Connection Machine® Model CM-2 Technical Summary

and - day

# **Thinking Machines Corporation**

Technical Report Series

\*

# Thinking Machines Technical Report HA87-4

# Connection Machine<sup>®</sup> Model CM-2 Technical Summary

April 1987

#### © 1987 Thinking Machines Corporation

Connection Machine is a registered trademark of Thinking Machines Corporation. DataVault, C\*, \*Lisp, CM-Lisp, and Paris are trademarks of Thinking Machines Corporation.

Symbolics 3600 is a trademark of Symbolics, Inc.

UNIX is a trademark of AT&T Bell Laboratories.

VAX, VAXBI, and ULTRIX are registered trademarks of Digital Equipment Corporation.

The information in this document is subject to change without notice and should not be construed as a commitment by Thinking Machines Corporation. Thinking Machines Corporation reserves the right to make changes to any products described herein to improve functioning or design. Although the information in this document has been reviewed and is believed to be reliable, Thinking Machines Corporation does not assume responsibility or liability for any errors that may appear in this document. Thinking Machines Corporation does not assume any liability arising from the application or use of any information or product described herein.

# Contents

٠

•

| 1  | Introduction                                             | 1    |

|----|----------------------------------------------------------|------|

|    | 1.1 The Connection Machine System                        | . 1  |

|    | 1.2 Data Parallel Hardware                               | . 2  |

|    | 1.3 Data Parallel Software                               | . 3  |

| 2  | System Organization                                      | 4    |

| 3  | The Paris Language                                       | 8    |

|    | 3.1 Overview                                             |      |

|    | 3.2 Virtual Machine Model                                | . 9  |

|    | 3.3 Organization of the Instruction Set                  | . 10 |

|    | 3.4 Instruction Set Summary                              | . 11 |

| 4  | Processor Architecture                                   | 19   |

|    | 4.1 Data Processors                                      | . 19 |

|    | 4.2 The Router                                           | . 20 |

|    | 4.3 The Floating Point Accelerator                       | . 22 |

| 5  | The Role of the Front End                                | 23   |

|    | 5.1 Applications Development                             | . 23 |

|    | 5.2 Running Connection Machine Applications              | . 24 |

|    | 5.3 Maintenance and Operations Utilities                 | . 24 |

|    | 5.4 The Digital Equipment Corporation VAX As a Front End | . 25 |

|    | 5.5 The Symbolics Lisp Machine As a Front End            | . 25 |

| 6  | Connection Machine I/O Structure                         | 27   |

| 7  | The Connection Machine DataVault                         | 28   |

|    | 7.1 The File Server                                      | . 28 |

|    | 7.2 Off-line Loading and Backup                          | . 29 |

|    | 7.3 Writing and Reading Data                             | . 29 |

|    | 7.4 Drive Failure and Data Base Healing                  | . 30 |

| 8  | High-Resolution Graphics Display                         | 31   |

| 9  | Languages                                                | 33   |

| 10 | The C* Language                                          | 35   |

|    | 10.1 Data Parallel Machine Model                         | . 35 |

|    | 10.2 Parallel Expressions                                | . 37 |

|    | 10.3 Parallel Statements                                 | . 39 |

|    | 10.4 Compiler Implementation                             |      |

| 1 | 1 Fortran                                                | 42 |

|---|----------------------------------------------------------|----|

|   | 11.1 The Environment                                     | 42 |

|   | 11.2 The Array Extensions of Fortran                     | 43 |

|   | 11.3 Fortran Statements for Controlling Context          | 43 |

|   | 11.4 Interprocessor Communication in Fortran             | 44 |

|   | 11.5 Fortran and the Data Parallel Approach              | 45 |

| 1 | 2 The *Lisp Language                                     | 46 |

|   | 12.1 Pvars: The Basic *Lisp Data Object                  | 46 |

|   | 12.2 Processor Addressing                                | 47 |

|   | 12.3 Reading and Writing Data from and to Pvars          | 47 |

|   | 12.4 Basic Parallel Operations                           | 47 |

|   | 12.5 Selection of Active Sets of Processors              | 48 |

|   | 12.6 Communication between Processors                    | 48 |

|   | 12.7 Global Reduction Operations                         | 49 |

|   | 12.8 Summary                                             | 49 |

| 1 | 3 The CM-Lisp Language                                   | 50 |

|   | 13.1 Xappings, Xets, and Xectors                         | 50 |

|   | 13.2 Parallel Computation: $\alpha$ Syntax               |    |

|   | 13.3 Interprocessor Communication: $\beta$ Syntax        |    |

|   | 13.4 Library Functions                                   |    |

| 1 | 4 An Example Program                                     | 56 |

|   | 14.1 The Example Program in C*                           | 56 |

|   | 14.2 The Example Program in Fortran                      |    |

|   | 14.3 The Example Program in *Lisp                        |    |

|   | 14.4 The Example Program in CM-Lisp                      |    |

| 1 | 5 Performance Specifications                             | 58 |

|   | 15.1 General Specifications                              | 58 |

|   | 15.2 Input/Output Channels                               | 58 |

|   | 15.3 Typical Application Performance (Fixed Point)       | 58 |

|   | 15.4 Interprocessor Communication                        |    |

|   | 15.5 Variable Precision Fixed Point                      | 59 |

|   | 15.6 Double Precision Floating Point                     |    |

|   | 15.7 Single Precision Floating Point                     |    |

|   | 15.8 Parallel Processing Unit Physical Dimensions        |    |

|   | 15.9 Parallel Processing Unit Environmental Requirements |    |

|   |                                                          |    |

÷

### **1** Introduction

The Connection Machine Model CM-2 is a data parallel computing system. Data parallel computing associates one processor with each data element. This computing style exploits the natural computational parallelism inherent in many data-intensive problems. It can significantly decrease the execution time of a problem, as well as simplify its programming. In the best cases, execution time can be reduced in proportion to the number of data elements in the computation; programming effort can be reduced in proportion to the complexity of expressing a naturally parallel problem statement in a serial manner. In order to fully exploit these potential benefits, a computing system consisting of both hardware and software that support this model of computing is required.

The Connection Machine Model CM-2 is an integrated system of hardware and software. The hardware elements of the system include front-end computers that provide the development and execution environments for the system software, a parallel processing unit of 64K processors that execute the data parallel operations, and a high-performance data parallel I/O system. The system software is based upon the operating system or environment of the front-end computer. The visible software extensions are minimal. Users can program using familiar languages and programming constructs, with all the development tools provided by the front end. Programs have normal sequential control flow; new synchronization structures are not needed. Thus, users can easily develop programs that exploit the power of the Connection Machine hardware.

#### **1.1** The Connection Machine System

At the heart of any large computational problem is the data set: some combination of interconnected data objects, such as numbers, characters, records, structures, and arrays. In any application this data must be selected, combined, and operated upon. Data level parallelism takes advantage of the parallelism inherent in large data sets.

At the heart of the Connection Machine Model CM-2 system is the parallel processing unit, which consists of thousands of processors, each with thousands of bits of memory. These processors can not only process the data stored in their memory, but also can be logically interconnected so that information can be exchanged among the processors. All these operations happen in parallel on all processors. Thus, the Connection Machine hardware directly supports the data parallel problem model.

One way to view the relationship of the CM-2 parallel processing unit to the other parts of the system is to consider it as an intelligent extension to the memory of the front-end computer. The data parallel data objects are stored by assigning each one to the memory of a processor. Then the operations on these objects can be specified to operate simultaneously on any or all data objects in this memory.

The Connection Machine processors are used whenever an operation can be performed simultaneously on many data objects. Data objects are left in the Connection Machine memory during execution of the program and are operated upon in parallel at the command of the front end. This model differs from the serial model of processing data objects from a computer's memory one at a time, by reading each one in turn, operating on it, and then storing the result back in memory before processing the next object.

The flow of control is handled entirely by the front end, including storage and execution of the program and all interaction with the user and/or programmer. The data set, for the most part, is stored in the Connection Machine memory. In this way, the entire data set can be operated upon in parallel through commands sent to the Connection Machine processors by the front end. The front end can also operate upon data stored in individual processors in the Connection Machine, treating them logically as memory locations in its virtual memory.

There are several direct benefits to maintaining program control only on the front end. First, programmers can work in an environment that is familiar. The front end interacts with the Connection Machine parallel processing unit using an integrated command set, and so the programming languages, debugging environment, and operating system of the front end remain relatively unchanged. Second, a large part of the program code for any application pertains to the interfaces between the program, the user, and the operating system. Since the control of the program remains on the front end, code developed for these purposes is useful with or without the Connection Machine parallel processing unit, and only the code that pertains specifically to the data residing on the Connection Machine processors needs to use the data parallel language extensions. Finally, parts of the program that are especially suited for the front end, such as file manipulation, user interface, and low-bandwidth I/O, can be done on the front end, while the parts of the program that run efficiently in parallel, namely the "inner loops" that operate on the data set, can be done on the Connection Machine. In this way, the individual strengths of both the serial front end and the Connection Machine processors can be exploited.

In general, the Connection Machine system appears to be a very powerful extension of the front-end system. The data parallel hardware looks like intelligent memory; the data parallel software extends the front end's capabilities to allow the direct execution of parallel operations.

#### **1.2 Data Parallel Hardware**

The Connection Machine system implements data parallel programming constructs directly in hardware. The system includes 65,536 physical processors, each with its own memory. Parallel data structures are spread across the data processors, with a single element stored in each processor's memory. When parallel data structures have more than 65,536 data elements (the normal case), the hardware operates in virtual processor mode, presenting the user with a larger number of processors, each with a correspondingly smaller memory.

Communication among elements of a parallel data structure is implemented by

#### Chapter 1 Introduction

a high-speed routing network. Processors that hold interrelated data elements store pointers to one another. When data is needed, it is passed over the routing network to the appropriate processors.

Scalar data is held in a front-end processor. The front end also controls execution of the overall data parallel program. Program steps that involve parallel data are passed over an interface to the Connection Machine parallel processing unit, where they are broadcast for execution by all the processors at once.

The Connection Machine front end provides the programming environment for the system. Programs can be stored on front-end disks. Network communications links are most effectively implemented on the front end as well.

High-speed transfers between peripheral devices and Connection Machine memory take place through the Connection Machine I/O system. All processors, in parallel, pass data to and from I/O buffers. The data is then moved between the buffers and the peripheral devices. Connection Machine high-speed peripherals include the DataVault mass storage system and the Connection Machine graphics display system.

#### **1.3 Data Parallel Software**

The Connection Machine system software is designed to utilize existing programming languages and environments as much as possible. The languages are based on wellknown standards; the extensions to support data parallel constructs are minimal so that a new programming style is not required. The CM-2 front-end operating system (either UNIX or Lisp) remains largely unchanged.

Fortran on the Connection Machine system uses the array extensions in the draft Fortran 8x standard (proposed by ANSI technical committee x3J3) to express data parallel operations. The remainder of the language is the standard Fortran 77. No extension is specific to the Connection Machine; the Fortran 8x array extensions map naturally onto the underlying data parallel hardware.

The \*Lisp and CM-Lisp languages are data parallel dialects of Common Lisp (a version of Lisp currently being standardized by ANSI technical committee X3J13). \*Lisp gives programmers fine control over the CM-2 hardware while maintaining the flexibility of Lisp. CM-Lisp is a higher-level language that adds small syntactic changes to the language interface and creates a very powerful data parallel programming language

The C\* language is a data parallel extension of the C programming language (as described in the draft C standard proposed by ANSI technical committee x3J11). C\* programs can be read and written like serial C programs; the extensions are unobtrusive and easy to learn.

The assembly language of the CM-2 is Paris. This is the target language of the high-level language compilers. This language logically extends the instruction set of the front end and masks the physical implementation of the CM-2 processing unit.

# 2 System Organization

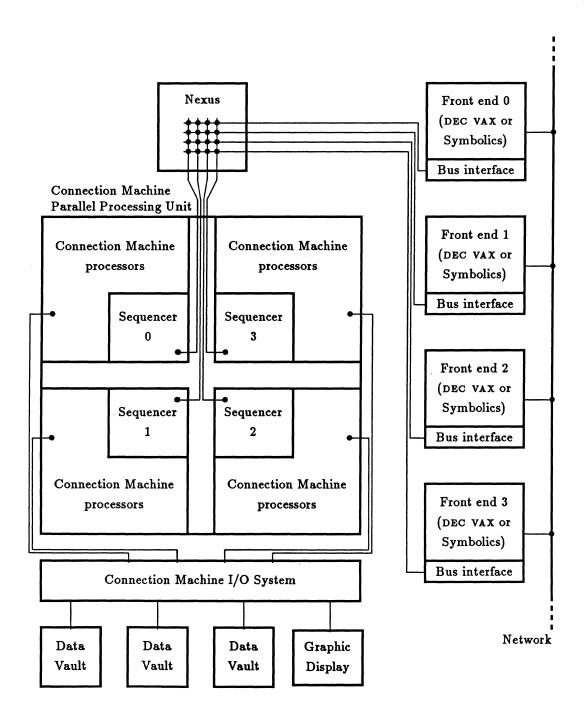

The Connection Machine Model CM-2 is a complete computing system that provides both development and execution facilities for data parallel programs. Its hardware consists of a parallel processing unit containing thousands of data processors, from one to four front-end computers, and an I/O system that supports mass storage and graphic display devices (see Figure 1). The user interacts with the front-end computer; all program development and execution takes place within the front end. Because the front-end computer runs standard serial software, the user sees a familar system environment with additional languages and utilities and some very powerful hardware.

The central element in the system is the CM-2 parallel processing unit, which contains:

- thousands of data processors

- an interprocessor communications network

- one or more sequencers

- an interface to one or more front-end computers

- zero or more I/O controllers and/or framebuffers

A parallel processing unit may contain 64K, 32K, or 16K data processors. (Here, and throughout this document, "K" stands for 1024. Thus 64K means 65,536; 32K means 32,768; 16K means 16,384; 8K means 8,192; and so on.) Each data processor has 64K bits (8 kilobytes) of bit-addressable local memory and an arithmetic-logic unit (ALU) that can operate on variable-length operands. Each data processor can access its memory at a rate of at least 5 megabits per second. A fully configured CM-2 thus has 512 megabytes of memory that can be read or written at about 300 gigabits per second. When 64K processors are operating in parallel, each performing a 32-bit integer addition, the CM-2 parallel processing unit operates at about 2500 Mips<sup>1</sup>. (This figure includes all overhead for instruction issuing and decoding.) In addition to the standard ALU, the CM-2 parallel processing unit has an optional parallel floating point accelerator that performs at 3500 MFlops<sup>2</sup> (single precision) or 2500 MFlops (double precision).

One of the most important requirements of general purpose data parallel computing is the ability of the data elements to communicate information among themselves in patterns that vary according to the problem and with time. The CM-2 system provides two forms of communication within the parallel processing unit. The more general mechanism is known as the *router*, which allows any processor to communicate with any other processor. One may think of the router as allowing every processor to send a message to any other processor, with all messages being sent and delivered at the same time. Alternatively, one may think of the router as allowing every processor to access

<sup>&</sup>lt;sup>1</sup>Mips = Millions of instructions per second

<sup>&</sup>lt;sup>2</sup>MFlops = Millions of floating point operations per second

Figure 1: Connection Machine Model CM-2 System Organization

any memory location within the parallel processing unit, with all processors making memory accesses at the same time; in effect, the router allows the local memories of the data processors to be treated as a single large shared memory. The messages (or accessed fields, if you will) may be of any length. The throughput of the router depends on the message length and on the pattern of accesses; typical values are 80 million to 250 million 32-bit accesses per second.

The CM-2 parallel processing unit also has a more structured, somewhat faster communication mechanism called the *NEWS grid*. In the CM-1 and some other fine grained parallel systems, communication can take place over a fixed two-dimensional grid. The CM-2, however, supports programmable grids with arbitrarily many dimensions. Possible grid configurations for 64K processors include  $256 \times 256$ ,  $1024 \times 64$ ,  $8 \times 8192$ ,  $64 \times 32 \times 32$ ,  $16 \times 16 \times 16 \times 16$ , and  $8 \times 8 \times 4 \times 8 \times 8 \times 4$ . The NEWS grid allows processors to pass data according to a regular rectangular pattern. For example, in a two-dimensional grid each processor could receive a data item from its neighbor to the east, thereby shifting the grid of data items one position to the left. The advantage of this mechanism over the router is merely that the overhead of explicitly specifying destination addresses is eliminated; for many applications this is a worthwhile optimization.

The parallel processing unit is designed to operate under the programmed control of a front-end computer, which may be either a Symbolics 3600 Lisp machine or a DEC VAX 8000 series computer with a BI bus. The front end provides the program development and execution environment. All Connection Machine programs execute on a front end; during the course of execution the front end issues instructions to the CM-2 parallel processing unit. In effect, the CM-2 parallel processing unit extends the instruction set and I/O capabilities of the front-end computer. The set of instructions that the front end may issue to the parallel processing unit is called Paris. It is designed for convenient use by front-end programs, and includes not only such operations as integer arithmetic, floating point arithmetic, and interprocessor communication, but also such powerful operations as vector summation, matrix multiplication, and sorting. The Paris instruction set is described further in Chapter 3.

The data processors do not handle Paris instructions directly. Instead, Paris instructions from the front end are processed by a *sequencer* in the parallel processing unit. The task of the sequencer is to break down each Paris instruction into a sequence of low-level data processor and memory operations. The sequencer broadcasts these low-level operations to the data processors, which execute them at a rate of several million per second. The low-level operations are described further in section 4.1.

To increase the flexibility of program development and execution, the CM-2 processing unit may be divided into as many as four sections. Depending on the configuration, a section will have either 8K or 16K data processors. For example, a parallel processing unit with 64K data processors will be divided into four sections of 16K data processors; a processing unit with 32K data processors could consist of either two 16K sections or four 8K sections.

Each section can be treated as a complete parallel processing unit in itself; in particular, each section contains its own sequencer, router, and NEWS grid. Sections may also be ganged; when this is done, their sequencers are also ganged and behave as a single sequencer, their routers cooperate as a single router, and their NEWS grids cooperate to form a single grid. A programmable, bidirectional switch called the Nexus allows up to four front-end computers to be attached to a single parallel processing unit. The front ends need not all be of the same type. Under front-end software control, the Nexus can connect any front end to any section or valid combination of sections in the CM-2 parallel processing unit. For example, in a CM-2 system with 32K data processors (in four 8K sections) and four front ends, one could assign one section to each front end for software testing; or one could gang all four sections to be controlled by any one front end for a production run; or one could assign 8K sections to each of two front ends, gang the other two sections to give 16K data processors to a third front end, and use the fourth front end for purposes unrelated to the parallel processing unit. The Nexus can be reconfigured in seconds; once this is done, data and instructions flow between the front end and the sequencers without visible intervention by the Nexus.

For every group of 8K data processors there is one I/O channel. (A section with 8K processors therefore has one channel; a section with 16K processors has two channels.) To each I/O channel may be connected either one high-resolution graphics display framebuffer module or one general I/O controller supporting an I/O bus to which several DataVault mass storage devices may be connected. The front end controls I/O transfers in exactly the same manner that it controls the data processors, by issuing Paris instructions to the sequencer. The sequencer can then send low-level commands to the I/O channels and interrogate channel status. Data is transferred directly and in parallel between the I/O devices and the data processors, without being funneled through the sequencers.

# **3** The Paris Language

The instructions that the front end may issue to the parallel processing unit constitute a language called Paris (from the phrase "parallel instruction set"). It is the lowest-level protocol by which the front-end computer directs the actions of Connection Machine processors.

#### 3.1 Overview

Paris is intended primarily as a base upon which to build higher-level languages for the Connection Machine system. It provides a large number of operations similar to the machine-level instruction set of an ordinary computer. Paris supports primitive operations on signed and unsigned integers and floating point numbers, as well as message-passing operations, I/O commands, and facilities for transferring data between the Connection Machine processors and the front-end computer.

Paris instructions direct the handling of data by the Connection Machine processors. Control instructions, such as subroutine calls, if-then-else conditionals, and while loops are not a part of the Paris instruction set. The control structure for an application is provided by the front-end computer. A program that is "written in Paris" must actually be written in some ordinary sequential language for the front end, such as C, Fortran, Pascal, or Lisp.

The Paris user interface consists of a set of functions, subroutines, and global variables. The functions and subroutines direct the actions of the Connection Machine processors, and the variables allow the user program to find out such information about the Connection Machine system as the number of processors available and the amount of memory per processor.

As a simple example, here is a bit of C code that repeatedly causes every processor whose floating point z field is greater than 1.0 to be divided by two; the loop is terminated when no processor has a z value greater than one.

The functions whose names begin with "CM\_" are Paris operations: CM\_f\_gt\_constant causes every processor to compare a field to a common, broadcast constant, storing a bit reflecting the result in its "test" flag; CM\_f\_divide\_constant similarly causes every processor to divide a floating point field by a common constant; and CM\_global\_logior takes a bit field (in this example, a one-bit field, namely the test flag) from every processor, and returns to the front end the result of a many-way bitwise inclusive-OR operation. The while construct is an ordinary C while loop, and is not a part of the Paris language proper.

8

#### Chapter 3 The Paris Language

Several different versions of the user interface are provided, one for each frontend programming language in which Paris is to be embedded. These interfaces are functionally identical; they differ only in conforming to the syntax and data types of one language or the other. Here is what the preceding example would look like if embedded in the Lisp language:

(do ()

This example of Lisp code uses a Lisp control structure, do, that is nearest in function to the C while statement. (It is actually a do-until statement, and the Lisp function zerop is used here to invert the sense of the result of CM:global-logior.) However, it would be appropriate to Lisp programming style to use a recursive function instead to express such a loop:

```

(defun loop ()

(CM:f-gt-constant z 1.0 23 8)

(unless (zerop (CM:global-logior CM:test-flag 1))

(CM:f-divide-constant-2 z 2.0 23 8)

(loop)))

```

This example underscores the point that the control structure of the program may be written in any programming language (even the assembly language of the front-end computer, if necessary), and in any style suitable to that programming language. Paris merely extends that language by providing for the parallel processing of data.

#### 3.2 Virtual Machine Model

Paris presents to the user an abstract machine architecture that is very much like the physical Connection Machine hardware architecture, but with two important extensions: the virtual processor abstraction and a much richer instruction set.

The virtual processor abstraction (on which most higher-level software depends) is supported at the Paris level. When the Connection Machine system is initialized for a particular application, the number of virtual processors required by the application may be specified. If this number exceeds the number of available physical processors, then the local memory of each processor is split up into as many regions as necessary, and for every Paris instruction the processors are automatically time-sliced among the regions. For example, if an application should need to process a million pieces of data, it might request  $V = 2^{20}$  virtual processors. Assume the available hardware to have  $P = 2^{16}$ physical processors each with  $M = 2^{16}$  bits of memory. Then each physical processor would support V/P = 16 virtual processors; this ratio V/P, usually denoted N, is called the virtual processor ratio, or VP-ratio. In this example each virtual processor would have  $M/N = 2^{12}$  bits of memory and would appear to execute code at about 1/N = 1/16 the speed of a physical processor.

The time taken to perform a move depends on the length of the field to be moved and also on the number of virtual processors in use. If each physical processor is simulating N virtual processors, then issuing a single move instruction causes each physical processor to execute N move operations. This will take N times as long as if virtual processors were not in use, but also does N times as much work, so the Mips measurement is about the same. Indeed, the use of virtual processors usually increases the measured Mips rate, because the instruction needs to be decoded by the sequencer only once for N executions, and so the decoding overhead may be amortized.

Each virtual processor has some local memory and also a number of 1-bit flags. Most of the flags are condition codes such as overflow and float-inexact. The context flag, however, controls conditional execution: for most Paris operations a processor executes the operation if its context flag is 1, but does not participate if its context flag is 0. Processors whose context flag is 1 are said to be *active*; the set of active processors is called the *current context*. A few operations are unconditional, being executed by all processors regardless of the values of their context flags. (It is important, for example, that there be a way to set all context flags to 1 unconditionally!)

#### **3.3** Organization of the Instruction Set

Most Paris operations deal with *fields* in the local memories of the Connection Machine processors. A field is specified by two quantities: the address of its first bit, and its length in bits. Uninterpreted bit fields (as processed by such operations as move, send, and logand) may be of any length. The length of an unsigned integer may range from 0 to 128 bits, and the length of a signed integer may range from 2 to 128 bits. (Some very simple arithmetic operations, such as addition, subtraction, and comparisons, are not limited to 128 bits.) Floating point operations are available in a variety of precisions, including 32-bit, 64-bit, and 80-bit formats.

Nearly all operations are memory-to-memory; for example, the signed integer addition operation can add the value of one memory field into another memory field (two-address mode) or can replace a memory field with the sum of two other fields (three-address mode). The flags are addressed as if they were 1-bit memory fields.

Many operations come in several forms, differing from each other in up to three categories:

• Addressing modes. The operations s-add-2 and s-add-3 both perform signed integer addition, but the one takes two addresses and a length and the other takes three addresses and a length. The operation s-add takes three addresses and three lengths, allowing the three fields involved to be of different sizes. Anything s-add-2 can do, s-add-3 can do by duplicating one address operand; anything s-add-3 can do, s-add can do by triplicating the length operand. The concise addressing modes improve performance by reducing total instruction size; the front end has fewer operands to send to the sequencer, and the sequencer has fewer operands to decode.

- Conditionalization. Most operations are executed only by active processors, but some are executed unconditionally by all processors. For example, the operation move copies one memory field to another for processors in the current context, but the operation move-always copies one memory field to another in all processors, regardless of the current context.

- Immediate operands. The operation s-add-2 adds one memory field into another in all active processors; the operation s-add-constant-2 adds an immediate quantity, sent from the front end as part of the instruction, into a memory field in all active processors. Note that the word "constant" in the instruction name is a relative term. The immediate operand is constant in being the same for all the data processors, but need not be constant within the front-end program; the front end may calculate the value to be sent to the sequencer.

#### **3.4 Instruction Set Summary**

The following sections list groups of related Paris instructions, with commentary, to illustrate the expressive power of the instruction set. This is not a complete list of Paris operations.

The names of the Paris operations are listed here in a compromise format. The name to be used in a Lisp program is derived by prefixing a name given below with "CM:"; the name to be used in a C program is derived by prefixing a name given below with "CM\_" and converting all hyphens to underscores. Thus the operation s-add-2 would be called CM:s-add-2 in Lisp code and CM\_s\_add\_2 in C code.

| move          | move-constant     | move-always     |

|---------------|-------------------|-----------------|

| logand        | logand-constant   | logand-always   |

| logior        | logior-constant   | logior-always   |

| logxor        | logxor-constant   | logxor-always   |

| logeqv        | logeqv-constant   | logeqv-always   |

| lognand       | lognand-constant  | lognand-always  |

| lognor        | lognor-constant   | lognor-always   |

| logandc1      | logandc1-constant | logandc1-always |

| logandc2      | logandc2-constant | logandc2-always |

| logorc1       | logorc1-constant  | logorc1-always  |

| logorc2       | logorc2-constant  | logorc2-always  |

| lognot        | array-fetch       | array-store     |

| load-context  | store-context     | set-context     |

| move-reversed | move-zero         | latch-leds      |

#### 3.4.1 Operations on Bit Fields

Every instruction in this group is executed by each data processor independently of the other data processors.

The move operations copy data from one memory field to another. Assuming only one virtual processor per physical processor and 32-bit fields, a move instruction, including all decoding overhead, takes about 21 microseconds; with 64K processors, this represents an aggregate execution rate of 3000 million individual 32-bit move operations per second.

All ten nontrivial binary bitwise boolean operations are provided. The array-fetch and array-store perform indexed load and store operations; every data processor has a small array of items within it, and each data processor may have a different index into its array. The load-context, store-context, and set-context operations are special cases of move optimized for use on the context flag.

The red lights on the CM-2 cabinet may be turned off and on by the latch-leds instruction; there is one light for every 16 processors.

| s-add<br>s-subtract<br>s-multiply | s-add-constant<br>s-subtract-constant<br>s-multiply-constant | s-add-carry<br>s-subtract-borrow<br>s-add-flags |

|-----------------------------------|--------------------------------------------------------------|-------------------------------------------------|

| s-divide                          | s-divide-constant                                            | s-mod                                           |

| s-max                             | s-max-constant                                               | s-rem                                           |

| s-min                             | s-min-constant                                               | s-random                                        |

| s-eq                              | s-eq-constant                                                | s-eq-zero                                       |

| s-ne                              | s-ne-constant                                                | s-ne-zero                                       |

| s-gt                              | s-gt-constant                                                | s-gt-zero                                       |

| s-ge                              | s-ge-constant                                                | s-ge-zero                                       |

| s-lt                              | s-lt-constant                                                | s-lt-zero                                       |

| s-le                              | s-le-constant                                                | s-le-zero                                       |

| s-shift                           | s-shift-constant                                             | s-integer-length                                |

| s-abs                             | s-signum                                                     | s-new-size                                      |

| s-negate                          | s-count-bits                                                 | <b>s</b> -isqrt                                 |

#### 3.4.2 Operations on Signed Integers

Every instruction in this group is executed by each active data processor independently of the other data processors. Most of these are operations familiar to any assembly language programmer: arithmetic operations, comparisons, absolute value, negate, and shift. The **s-new-size** operation copies a signed integer from one field to another of different size, performing sign extension or overflow checking as appropriate.

Assuming only one virtual processor per physical processor and 32-bit fields, an s-add instruction, including all decoding overhead, takes about 26 microseconds; with 64K processors, this represents an aggregate execution rate of 2500 million 32-bit additions per second.

#### Chapter 3 The Paris Language

| u-add      | u-add-constant      | u-add-carry              |

|------------|---------------------|--------------------------|

|            |                     | •                        |

| u-subtract | u-subtract-constant | u-subtract-borrow        |

| u-multiply | u-multiply-constant | u-add-flags              |

| u-divide   | u-divide-constant   | u-mod                    |

| u-max      | u-max-constant      | u-rem                    |

| u-min      | u-min-constant      | u-random                 |

| u-eq       | u-eq-constant       | u-eq-zero                |

| u-ne       | u-ne-constant       | u-ne-zero                |

| u-gt       | u-gt-constant       | u-gt-zero                |

| u-ge       | u-ge-constant       | u-ge-zero                |

| u-lt       | u-lt-constant       | u-integer-from-gray-code |

| u-le       | u-le-constant       | u-gray-code-from-integer |

| u-shift    | u-shift-constant    | u-integer-length         |

| u-abs      | u-signum            | u-new-size               |

| u-negate   | u-count-bits        | u-isqrt                  |

|            |                     |                          |

#### 3.4.3 Operations on Unsigned Integers

Every instruction in this group is executed by each active data processor independently of the other data processors. Most of these operations correspond to those listed in the preceding section, but operate on unsigned integers rather than signed integers. Unusual are two instructions that convert values between unsigned binary representation and a binary reflected Gray code representation; these have some utility in the Connection Machine architecture in performing low-level addressing calculations, because the processor addresses used by the router and those used by the NEWS grid are related by a Gray encoding.

#### 3.4.4 Operations on Floating Point Numbers

| f-move            | f-move-constant            | f-move-decoded-constant  |

|-------------------|----------------------------|--------------------------|

| f-add             | f-add-constant             | f-square                 |

| <b>f-subtract</b> | <b>f-subtract-constant</b> | f-integer-power          |

| f-multiply        | f-multiply-constant        | f-integer-power-constant |

| f-divide          | f-divide-constant          | f-mod                    |

| f-max             | f-max-constant             | f-rem                    |

| f-min             | f-min-constant             | f-random                 |

| f-eq              | f-eq-constant              | f-eq-zero                |

| f-ne              | f-ne-constant              | f-ne-zero                |

| f-gt              | f-gt-constant              | f-gt-zero                |

| f-ge              | f-ge-constant              | f-ge-zero                |

| f-lt              | f-lt-constant              | f-lt-zero                |

| f-le              | f-le-constant              | f-le-zero                |

| f-scale           | f-scale-constant           | f-logb                   |

| f-abs             | f-signum                   | f-new-size               |

| f-negate | f-float-signum  | <b>f-sqrt</b>    |

|----------|-----------------|------------------|

| f-sin    | <b>f-asin</b>   | float-exp        |

| f-cos    | f-acos          | float-log        |

| f-tan    | f-atan          | float-atan2      |

| f-sinh   | f-asinh         | float-power      |

| f-cosh   | <b>f-a</b> cosh | float-square     |

| f-tanh   | f-atanh         | float-polynomial |

Every instruction in this group is executed by each active data processor independently of the other data processors. Most of these are floating point operations familiar to any assembly language programmer: arithmetic operations, comparisons, absolute value, negate, scale, and the usual exponential, logarithm, and trigonometric functions.

#### 3.4.5 Type Conversions

| s-floor    | u-floor    | s-float |

|------------|------------|---------|

| s-ceiling  | u-ceiling  | u-float |

| s-truncate | u-truncate |         |

| s-round    | u-round    |         |

Every instruction in this group is executed by each active data processor independently of the other data processors. These operations convert between integer (signed or unsigned) and floating point representations.

#### 3.4.6 Intraprocessor Vector Operations

```

f-vector-dot-product

f-vector-3d-cross-product

f-vector-norm

f-matrix-multiply

```

There are two ways to represent vectors and matrices within the Connection Machine memory: one may represent a large vector or matrix by placing one element within each data processor, or one may represent many small vectors or matrices by placing an entire vector or matrix within each data processor.

The operations in this section assume the latter representation. As an example, f-matrix-multiply could be used to direct every active processor to multiply two  $4 \times 4$  matrices. These operations could be expressed in terms of the simple floating point instructions listed in the previous section; they are provided purely for reasons of convenience and performance.

Computing the single-precision dot product of two vectors of length n with the floating point accelerator takes approximately 13n - 5 microseconds. Assuming that this operation requires 2n - 1 "flops" (n multiplications and n - 1 additions), then the aggregate execution rate for 64K processors is 10,000 MFlops (that is, 10 gigaflops).

#### 3.4.7 Interprocessor Vector Operations

| global-count      | copy-scan       | segmented-copy-scan       |

|-------------------|-----------------|---------------------------|

| global-logand     | logand-scan     | segmented-logand-scan     |

| global-logior     | logior-scan     | segmented-logior-scan     |

| global-s-add      | s-add-scan      | segmented-s-add-scan      |

| global-s-multiply | s-multiply-scan | segmented-s-multiply-scan |

| global-s-max      | s-max-scan      | segmented-s-max-scan      |

| global-s-min      | s-min-scan      | segmented-s-min-scan      |

| global-u-add      | u-add-scan      | segmented-u-add-scan      |

| global-u-multiply | u-multiply-scan | segmented-u-multiply-scan |

| global-u-max      | u-max-scan      | segmented-u-max-scan      |

| global-u-min      | u-min-scan      | segmented-u-min-scan      |

| global-f-add      | f-add-scan      | segmented-f-add-scan      |

| global-f-multiply | f-multiply-scan | segmented-f-multiply-scan |

| global-f-max      | f-max-scan      | segmented-f-max-scan      |

| global-f-min      | f-min-scan      | segmented-f-min-scan      |

Each of these operations takes one datum from each active processor and combines them in some way.

The global- operations perform reduction; the set of values, one from each processor, is reduced to a single value through application of a binary combining function. This value is then returned to the front end. For example, global-s-add returns to the front end the signed integer sum of all the values, and global-f-max treats the items as floating point values and returns the largest one.

The -scan operations perform a scan (also called "parallel prefix"). This takes an array of values, one per virtual processor, and replaces each item with the reduction of all items occurring before (and possibly including) that item. For example, if there were eight processors, the argument and result fields might look like this for various operations:

| Argument                            | 3 | 2 | 6  | 4   | 5   | 11   | 0    | 9  |

|-------------------------------------|---|---|----|-----|-----|------|------|----|

| Result of exclusive u-add-scan      | 0 | 3 | 5  | 11  | 15  | 20   | 31   | 31 |

| Result of inclusive u-add-scan      | 3 | 5 | 11 | 15  | 20  | 31   | 31   | 40 |

| Result of exclusive u-multiply-scan | 1 | 3 | 6  | 36  | 144 | 720  | 7920 | 0  |

| Result of inclusive u-multiply-scan | 3 | 6 | 36 | 144 | 720 | 7920 | 0    | 0  |

| Result of exclusive u-max-scan      | 0 | 3 | 3  | 6   | 6   | 6    | 11   | 11 |

| Result of inclusive u-max-scan      | 3 | 3 | 6  | 6   | 6   | 11   | 11   | 11 |

On a CM-2 system with 64K physical processors, a u-add-scan operation on 64K 32-bit fields takes on the order of 300 microseconds.

The -scan operations come in many varieties. One set operates along the NEWS grid, so as to perform many scan operations, one for each row or column in the grid. Another set allows the processors to be segmented into subarrays of differing length,

performing a scan independently within each subarray. The copy-scan operation is particularly useful in these cases; within each row, column, or segment it copies a value from the first processor into all the other processors.

#### 3.4.8 General Interprocessor Communication

| send                 | store                 |

|----------------------|-----------------------|

| send-with-overwrite  | store-with-overwrite  |

| send-with-logior     | store-with-logior     |

| send-with-logand     | store-with-logand     |

| send-with-s-add      | store-with-s-add      |

| send-with-s-multiply | store-with-s-multiply |

| send-with-s-max      | store-with-s-max      |

| send-with-s-min      | store-with-s-min      |

| send-with-u-add      | store-with-u-add      |

| send-with-u-multiply | store-with-u-multiply |

| send-with-u-max      | store-with-u-max      |

| send-with-u-min      | store-with-u-min      |

| send-with-f-add      | store-with-f-add      |

| send-with-f-multiply | store-with-f-multiply |

| send-with-f-max      | store-with-f-max      |

| send-with-f-min      | store-with-f-min      |

| get                  | fetch                 |

Each of the send- operations takes two fields from each active processor, one containing message data and the other containing the address of a destination processor; each message is deposited into a third field within the memory of the processor specified as the destination for that message.

The plain send operation assumes that no processor will receive more than one message. The other send- operations cause multiple messages for the same destination to be combined in a specified way; they differ only in the combining operation to be used. Thus send-with-overwrite causes one message to be retained and the rest discarded; send-with-s-add causes the destination processor to receive the sum of all messages sent to it; and so on.

The send operation can process messages at rates varying typically from 80 million to 250 million per second, depending on the communication pattern. For example, if each of 64K processors sends a message to some other processor, the entire operation will take somewhere between 260 and 820 microseconds.

If send is viewed as a write into a global shared memory, then get is the corresponding read operation.

The store operation is like send, but the processor sending a message specifies not only which processor is to be the destination but also the memory location into which to deposit the message. This allows a processor to receive more than one message

#### Chapter 3 The Paris Language

without combining them; it also supports the abstraction of having completely general pointers into a global shared memory. The fetch operation is to store as get is to send.

3.4.9 Communication within a Cartesian Grid

| send-to-news         | get-from-news         |

|----------------------|-----------------------|

| send-to-news-bounded | get-from-news-bounded |

The send-to-news operation takes operands that specify a Cartesian coordinate system and a direction within that system, and causes every active processor to send a message to its neighbor in that direction. In the case of a two-dimensional grid the choices are North, East, West, or South, whence the name "NEWS grid." The get-from-news operation is complementary: each active processor fetches data from its neighbor. (There is no difference between sending to the West and getting from the East if all processors are active.)

The ordinary NEWS operations actually organize the grid as a hypertorus: the edges "wrap around" so that the West neighbor of a processor on the West edge of the grid is the processor at the East edge of the same row. The -bounded versions of the operations do not wrap around; data sent past the boundary of the grid is discarded, and a specified immediate operand is sent in from the opposite boundary. In other words, the plain operations perform a one-place circular shift of each row or column, while the bounded operations perform a one-place end-off shift with a specified value shifted in.

#### 3.4.10 Sorting

s-rank u-rank f-rank

A ranking operation takes one value from each active processor and calculates for each processor the rank of that processor's value in a sorted ordering of all the values. For example, if there were eight processors, the argument and result fields might look like this:

| Argument         | 3 | 2 | 6 | 4 | 5 | 11 | 0 | 9 |

|------------------|---|---|---|---|---|----|---|---|

| Result of u-rank | 2 | 1 | 5 | 3 | 4 | 7  | 0 | 6 |

If it is then desired to rearrange the values within the processors according to the sorted order, the result of the rank operation may be used as a processor address (or to calculate an address, say within the NEWS grid) for the send operation. An advantage of separating the ranking process from the actual rearrangement of the data is that one may perform the ranking step on a small key field and then use the result to reorder a much larger record. This is usually much faster than simply sorting the large records in one step.

On a CM-2 system with 64K physical processors, sorting 64K 32-bit fields (ranking them and then rearranging them) takes about 30 milliseconds.

```

3.4.11 Data Transfer between Processors and Front End

```

```

s-read-from-processor

s-write-to-processor

u-read-from-processor

u-write-to-processor

f-read-from-processor

f-write-to-processor

s-read-news-array

s-write-news-array

u-read-news-array

u-write-news-array

f-read-news-array

f-write-news-array

s-read-send-array

s-write-send-array

u-read-send-array

u-write-send-array

f-read-send-array

f-write-send-array

```

The -read-from-processor and -write-to-processor commands allow the front end to read or write a single field within a single data processor. The -array commands provide a fast block transfer of many data items, stored one per data processor in either NEWS-address order or send-address order, either to or from a block of memory in the front end.

#### 3.4.12 Housekeeping Operations

| get-stack-pointer | get-stack-limit | get-stack-upper-bound            |

|-------------------|-----------------|----------------------------------|

| set-stack-pointer | set-stack-limit | <pre>set-stack-upper-bound</pre> |

| push-space        | pop-and-discard | initialize-random                |

| cold-boot         | attach          | power-up                         |

| warm-boot         | detach          | set-system-leds-mode             |

A single global stack pointer is maintained that allows part of the local memory of each data processor to be treated as a stack, typically for the run-time allocation of automatic variables for a compiled high-level language. The operation push-space allocates stack space by adjusting the common stack pointer and performs a stack overflow check; the operation pop-and-discard deallocates stack space.

The initialize-random initializes the pseudo-random number generator used by the operations s-random, u-random, and f-random.

The operations cold-boot, warm-boot, attach, detach, and power-up are used to initialize the parallel processing unit and to assign sections for use by particular front-end computers.

The set-system-leds-mode operation determines whether the red lights on the CM-2 cabinet are to display internal status information or are to be controlled by the user program through the latch-leds instruction.

# **4 Processor Architecture**

This chapter describes details of the hardware in the CM-2 parallel processing unit. Most of these details are hidden from the user by the Paris interface and usually are of no concern to the Connection Machine application programmer. However, an understanding of these details is helpful in predicting program performance.

The Connection Machine Model CM-2 parallel processing unit contains thousands of data processors. Each data processor contains:

- an arithmetic-logic unit (ALU) and associated latches

- 64K bits of bit-addressable memory

- four 1-bit flag registers

- optional floating point accelerator

- router interface

- NEWS grid interface

- I/O interface

The data processors are implemented using four chip types. A proprietary custom chip contains the ALU, flag bits, router interface, NEWS grid interface, and I/O interface for 16 data processors, and also contains proportionate pieces of the router and NEWS grid network controllers. The memory consists of commercial RAM chips. The floating point accelerator consists of a custom floating point interface chip and a floating point execution chip; one of each is required for every 32 data processors. A fully configured parallel processing unit contains 64K data processors, and therefore contains 4096 processor chips, 2048 floating point interface chips, and 2048 floating point execution chips, and half a gigabyte of RAM.

#### 4.1 Data Processors

A CM-2 ALU consists of a 3-input, 2-output logic element and associated latches and memory interface. The basic conceptual ALU cycle first reads two data bits from memory and one data bit from a flag; the logic element then computes two result bits from the three input bits; finally, one of the two results is stored back into memory and the other result into a flag. One additional feature is that the entire operation is conditional on the value of a third flag; if the flag is zero, then the results for that data processor are not stored after all.

The logic element can compute *any* two boolean functions on three inputs; these functions are simply specified (by the sequencer) as two 8-bit bytes representing the truth tables for the two functions.

This simple ALU suffices to carry out, under control of the sequencer, all the operations of the Paris instruction set. Consider, for example, addition of two k-bit signed integers. First the virtual processor context flag is loaded into a hardware flag register (which is then used as the condition flag for all remaining ALU operations). Next a second hardware flag is cleared for use as a carry bit. Next come k iterations of an ALU cycle that reads one bit of each operand from memory and also the carry bit, computes the sum (a three-way exclusive OR) and carry-out (a three-input majority function), and stores the sum back into memory and the carry-out back into the carry flag. These cycles start with the least significant bits of the operands and proceed toward the most significant bits. The last of the k cycles stores the carry-out into a different hardware flag, so that the last two carry-outs may be compared to determine whether overflow has occurred. Arithmetic is therefore carried out in a bit-serial fashion; at about half a microsecond per bit, plus instruction decoding and other overhead, a 32-bit add takes about 21 microseconds. With 64K processors all computing in parallel, this produces an aggregate rate of 2500 Mips (that is, 2.5 billion 32-bit adds per second). All other Paris operations are carried out in like fashion.

The ALU cycle is broken down into subcycles. On each cycle the data processors can execute one low-level instruction (called a *nanoinstruction*) from the sequencer and the memories can perform one read or write operation. The basic ALU cycle for a two-operand integer add consists of three nanoinstructions:

LOADA: read memory operand A, read flag operand, latch one truth table LOADB: read memory operand B, read condition flag, latch other truth table STORE: store memory operand A, store result flag

Other nanoinstructions direct the router, NEWS grid, and floating point accelerator, initiate I/O operations, and perform diagnostic functions.

#### 4.2 The Router

Interprocessor communication is accomplished in the CM-2 parallel processing unit by special-purpose hardware. Message passing happens in a data parallel fashion; all processors can simultaneously send data into the local memories of other processors, or fetch data from the local memories of other processors into their own. The hardware supports certain message-combining operations: that is, the communication circuitry may be operated in such a way that processors to which multiple messages are sent receive the bitwise logical OR of all the messages, or the numerically largest, or the integer sum.

Each CM-2 processor chip contains one router node, which serves the 16 data processors on the chip. The router nodes on all the processor chips are wired together to form the complete router network. The topology of this network happens to be a boolean *n*-cube, but this fact is not apparent at the Paris level. For a fully configured CM-2 system, the network is a 12-cube connecting 4096 processor chips. Each router node is connected to 12 other router nodes; specifically, router node *i* (serving data processors 16*i* through 16i + 15) is connected to router node *j* if and only if  $|i-j| = 2^k$ for some integer *k*, in which case we say that routers *i* and *j* are connected along dimension *k*.

#### Chapter 4 Processor Architecture

Each message travels from one router node to another until it reaches the chip containing the destination processor. The router nodes automatically forward messages and perform some dynamic load balancing. For example, suppose that processor 117 (which is processor 5 on router node 7, because  $117 = 16 \times 7 + 5$ ) has a message M whose destination is processor 361 (which is processor 9 on router node 22). Since  $22 = 7+2^4-2^0$ , this message must traverse dimensions 0 and 4 to reach its destination. In the absence of congestion, router 7 forwards the message to router 6 ( $6 = 7 - 2^0$ ), which forwards it to router 22 ( $22 = 6 + 2^4$ ), which delivers the message to processor 361. On the other hand, if router 7 has another message that needs to use dimension 0, it may choose to send message M along dimension 4 first, to router 23 ( $23 = 7 + 2^4$ ), which then forwards the message to router 22, which then delivers it.

The algorithm used by the router can be broken into stages called *petit cycles*. The delivery of all the messages for a Paris send operation might require only one petit cycle if only a few processors are active, but if every processor is active then typically many petit cycles are required. It is possible for a message to traverse many dimensions, possibly all 12, in a single petit cycle, provided that congestion does not cause it to be blocked; the message data is forwarded through multiple router nodes in a pipelined fashion. A message that cannot be delivered by the end of a petit cycle is buffered in whatever router node it happens to have reached, and continues its journey during the next petit cycle. If petit cycles are regarded as atomic operations, then the router may be viewed as a store-and-forward packet-switched network. Within a petit cycle, however, the router is better regarded as a circuit-switched network, where dimension wires are assigned to particular messages whose contents are then pumped through the reserved circuits.

Each router node has a limited ALU, distinct from those for the data processors. During each petit cycle, each router node checks to see if its buffers hold several messages that are all going to the same processor. If so, the messages are combined. This may be done by taking the numerically greatest, summing them, taking the bitwise logical OR, or by arbitrarily discarding all but one. Other combining functions are implemented in terms of these. For example, combining with bitwise logical AND is performed by inverting the original message data, sending it with OR-combining, and re-inverting received messages. (Such tricks are implemented by the sequencer, transparently to the Paris user.) This hardware support for combining accelerates such Paris instructions as send-with-logand, send-with-s-add, and send-with-u-max. The combining hardware also combines read requests during execution of the Paris get instruction, so that a value fetched once from a processor can be returned to many requestors in a single petit cycle.

Each router node also contains specialized logic to support virtual processors. When a message is to be delivered by a router node, it is placed not only within the correct physical processor, but in the correct region of memory for the virtual processor originally specified as the message's destination.

#### 4.3 The Floating Point Accelerator

In addition to the bit-serial data processors described above, the CM-2 parallel processing unit has an optional floating point accelerator that is closely integrated with the processing unit. There are two possible options for this accelerator: Single Precision or Double Precision. Both options support IEEE standard floating point formats and operations. They each increase the rate of floating point calculations by more than a factor of 20 (see Chapter 15). Taking advantage of this speed increase requires no change in user software.

The hardware associated with each of these options consists of two special purpose VLSI chips, a memory interface unit and a floating point execution unit, for each pair of CM-2 processor chips.

As an example of the operation of the floating point accelerator, consider the execution of a two-operand floating point instruction such as f-add-2 or f-multiply-2. Execution proceeds in five stages; each stage is generally comprised of 32 nanoinstruction cycles (one cycle for each of the 32 data processors on the two CM-2 processor chips).

- 1. The first operand for each of 32 data processors is transferred from memory to the interface chip.

- 2. The first operand is transferred from the interface chip to the floating point execution chip. (The floating point execution chip is capable of storing 32 values of a given precision.) Simultaneously, the second operand is transferred from memory to the interface chip.

- 3. The second operand is transferred from the floating point interface chip to the floating point execution chip, where the operation is performed. At the end of this stage, the floating point execution chip contains the 32 results.

- 4. The results are transferred from the floating point execution chip to the interface chip.

- 5. The results are transferred from the interface chip to memory.

If the virtual processor ratio is N, this process is pipelined so as to require only 3N+2 stages instead of 5N stages.

# 5 The Role of the Front End

A front-end computer is a gateway to the Connection Machine system. It provides software development tools, software debugging tools, and a program execution environment familiar to the user. From the point of view of the user, the Connection Machine environment appears to be an extended version of the normal front-end environment. In addition to the usual suite of tools and languages provided by the front end, the environment includes at least one resident compiler or interpreter for a Connection Machine language. The front end also contains specialized hardware, called a Front-End Bus Interface (or FEBI), which allows communication with the Connection Machine.

A front end can be any computer system for which a FEBI exists. At the present time, a FEBI is available for most Digital Equipment Corporation VAX 8000 series minicomputers and for Symbolics 3600 series Lisp machines. The choice of which computer to use as a Connection Machine system front end depends on the nature of the application and on the preferences of the intended users. For example, an artificial intelligence application such as visual object recognition may be most naturally implemented in CM-Lisp, and would therefore work best with a Symbolics front end, whereas scientific applications normally implemented in Fortran would require a VAX front-end computer. Different types of front-end computers may be attached to the same Connection Machine and be running applications simultaneously. In addition, a single front-end computer may contain more than one FEBI to support up to four time-sharing users running Connection Machine applications simultaneously.

The front-end computer serves three primary functions in the Connection Machine system:

- It provides an applications development and debugging environment.

- It runs applications and transmits instructions and associated data to the Connection Machine parallel processing unit.

- It provides maintenance and operations utilities for controlling the Connection Machine and diagnosing problems.

#### 5.1 Applications Development

Users create Connection Machine programs in the development environment provided by the front end. The editors, file systems, and debugging tools are those that are part of the front end's normal environment. The resident Connection Machine language, which contains parallel extensions to a language already familiar to the user, is used to express algorithms exploiting the data parallel structure of a problem. Thus, users with very little experience in data parallel programming may begin to use the Connection Machine immediately. The native debugging facilities of the front end are augmented by simulators provided as part of the Connection Machine software system. The use of simulators can enhance productivity of users by allowing them to debug application programs, at least in part, without tying up the Connection Machine hardware.

#### 5.2 **Running Connection Machine Applications**

Once a Connection Machine program has been written, it is executed on the frontend computer. Most statements are translated directly to the native machine code of the front end. Those source-level constructs that correspond to Connection Machine (data parallel) operations are translated to a mix of native machine code and memory operations addressing the FEBI. These are totally transparent to the user.

Data that resides in the Connection Machine need not be returned to the front end immediately. In typical programs, data structures are created in the Connection Machine memory and are used in precisely the same manner as structures in front-end memory. The difference is that operations on the Connection Machine structures can be carried out on many data items in parallel.

Facilities are provided for users to run their programs in interactive or batched mode. Typically the interactive mode will be used during initial program debug, where the user will run the same program repeatedly under control of a debugger, or when the program requires user intervention. Programs that do not require interaction may be placed on a batch queue and run in the background.

#### 5.3 Maintenance and Operations Utilities

The front-end computer also provides utilities to support these functions:

- Allocating and deallocating Connection Machine resources

- Querying Connection Machine system status

- Diagnosing hardware problems

These tools are designed to be compatible with the style and operation of similar tools in the front-end environment.

Information on what segments of the Connection Machine system are in use is made available through status-querying functions. "Attach" and "detach" utilities are provided to allocate and deallocate all or a legal subset of Connection Machine processors to a user logged into a front-end computer. The minimum unit of allocation is whatever is attached to a single sequencer. See Chapter 2 for a description of hardware associated with a sequencer. The following table lists permitted configurations.

| Total number of Number of |            | Processors per | Permitted attachable |  |  |

|---------------------------|------------|----------------|----------------------|--|--|

| processors                | sequencers | sequencer      | subsets              |  |  |

| 16K                       | 2          | 8K             | 8K, 16K              |  |  |

| <b>32</b> K               | 2          | 16K            | 16K, 32K             |  |  |

| <b>32K</b>                | 4          | 8K             | 8K, 16K, 32K         |  |  |

| 64K                       | 4          | 16K            | 16K, 32K, 64K        |  |  |

Tools are provided for initializing an allocated sequencer, a procedure known as "booting" the Connection Machine system. There are two levels of initialization provided. The more drastic is "cold boot," which initializes the state of the attached sequencer (including downloading fresh microcode to the sequencer's writable control store) and also initializes the associated Connection Machine data processors (including clearing all memory and initializing per-processor memory-resident global data). The milder form of initialization is called "warm boot," which resets only the state of the sequencer without touching Connection Machine processor memory. When debugging programs, "warm boot" can be used to get the sequencer to a known state in order to be able to examine Connection Machine memory after a program crash. Note that neither of these procedures will affect other users running at the same time on other segments of the Connection Machine, nor will they affect unallocated processors.

A complete set of diagnostics is provided with the Connection Machine software. Facilities are also provided to make it easy to send error reports and details of diagnostic failures through an electronic message network to the Customer Support Group at Thinking Machines Corporation.

#### 5.4 The Digital Equipment Corporation VAX As a Front End

Currently any Digital Equipment Corporation VAX that contains a VAXBI I/O bus and runs the ULTRIX operating system may be used as a Connection Machine system front end. The VAXBI bus FEBI board provided by Thinking Machines Corporation is designed to allow the user program access to the Connection Machine system sequencer and Nexus registers with minimum system overhead. To accomplish this, the ULTRIX device driver for the FEBI maps the FEBI registers into the address space of the Connection Machine applications program, which then reads and writes the registers as if they were VAX processor memory. Thus, no system overhead at all is incurred in performing Connection Machine I/O. This scheme works especially well with the two-processor VAX computers in the 8000 series, as one processor can be dedicated to running the Connection Machine while the other performs normal time-sharing duties.

All Connection Machine languages are supported in the VAX environment. A VAX front end may contain more than one FEBI (up to four).

#### 5.5 The Symbolics Lisp Machine As a Front End

Any Symbolics 3600 series Lisp machine can be used as a Connection Machine system front end. The FEBI board provided by Thinking Machines Corporation is designed to allow the user program access to the Connection Machine system sequencer and Nexus registers with minimum system overhead. To accomplish this, the FEBI registers are mapped into into the Lisp address space; a Connection Machine applications program can then read and write the registers as if they were 3600 processor memory. Since Lisp machines are single user workstations, only one FEBI per front end is supported.

The languages currently supported for the Symbolics Lisp machine front end are CM-Lisp, \*Lisp, and Paris.

## 6 Connection Machine I/O Structure

The Connection Machine I/O structure allows data to be moved into or out of the parallel processing unit at aggregate peak rates as high as 320 megabytes per second for a system with multiple I/O controllers. Input/output is done in parallel, with as many as 2K data processors able to send or receive data at a time. All transfers are parity checked on a byte-by-byte basis.

The data processors send and receive data via I/O controllers, which interface through an I/O channel to Connection Machine data lines. These I/O controllers, in turn, operate under the control of the parallel processing unit sequencers. There may be as many as four sequencers in a fully configured system. A maximum I/O configuration for a 64K processor Connection Machine system includes eight I/O channels, each of which permits input and output operations for a set of 8K data physical processors.

An I/O controller treats its 8K physical processors as two banks of 4K. Each CM-2 processor chip contains 16 data processors and has one I/O line, so each bank of 4K processors is implemented on 256 chips and has 256 I/O lines. A bank can therefore pass 256 bits in parallel at a time to its associated I/O controller. Each sequencer controls a bank switch that determines which bank is active.

I/O controllers store data internally in 288-bit chunks (256 data bits plus 32 parity bits). Parity is checked each time data is transferred between a controller and the data processors. Each controller has the ability to store 512 of these 288-bit chunks in its own internal memory. Data transfers between I/O controllers and data processors proceed under control of a Connection Machine sequencer. Two I/O controllers may be active simultaneously on each sequencer.

A Connection Machine I/O bus runs from each I/O controller to the devices it controls. This bus is 80 bits wide (64 data bits, 8 parity bits, and 8 control bits). The I/O controller multiplexes and demultiplexes between 256-bit processor chunks and 64-bit I/O bus chunks. The controller also acts as arbitrator, allocating bus access to the various devices on the bus.

Since standard peripheral devices do not operate at the speeds that the Connection Machine system itself can sustain, it is often desirable to place multiple devices on multiple buses. For example, each of eight disk units could interface to several sections of data processors via several I/O controllers, each disk reading and writing data in parallel with the others. In this way, up to eight times the aggregate transfer rate of a single disk unit is achieved. Alternatively, devices may be interfaced to a single bus, interfaced in turn to I/O controllers in all sections of the parallel processing unit, allowing data to be moved directly between that device and any part of the processing unit. Typical configurations use a mix of these techniques. Some devices are connected to multiple controllers. Others connect to just one controller, and the Conection Machine router is used as necessary to move data to its final destination in the parallel processing unit.

# 7 The Connection Machine DataVault