Akhmetov B.S., Lakhno V.A., Malikova F.U.

# COMPUTER ARCHITECTURE

**Tutorial**

# MINISTRY OF EDUCATION AND SCIENCE OF THE REPUBLIC OF KAZAKHSTAN Almaty University of Power Engineering and Telecommunication

Akhmetov B.S., Lakhno V.A., Malikova F.U.

# **COMPUTER ARCHITECTURE**

#### UDC 004.031 LBC 32.973.202 A 27

Reviewers: Utepbergenov I.T. - Doctor of technical sciences, professor; Kartbaev T.S. - Dr. PhD; Alibieva Zh.M. - Dr. PhD;

#### Akhmetov B.S.

A 27 Computer architecture. *Tutorial/ B.S.Akhmetov, V.A.Lakhno, F.U.Malikova* - Almaty: AUPET, 2019. - 288 p. Fig. 109. Tab. 25. Bibliography - 23 titles.

#### ISBN 978-601-7307-74-5

The study of the discipline "Computer Architecture" is one of the important components of the professional training of modern specialists in the field of information technology. The rapid development of computers and other digital electronics leads to the saturation of almost all spheres of human activity.

In these conditions, for a specialist in computer or software engineering, knowledge of the basics of the computer hardware, its basic technical characteristics and functional capabilities is necessary.

This textbook on the discipline "Computer Architecture" is intended to help students in gaining knowledge about the functional components of modern computers, their purpose, types and characteristics, as well as forms of representing information in computers, the basics of machine mathematics and logic.

The training manual is intended for the preparation of bachelors and masters of the following educational programs of the field of information and communication technologies, as well as for all specialists who are interested in computer architecture.

#### ISBN 978-601-7307-74-5

Considered and approved at the Scientific Council of the AUPET (protocol No.3, 17.09.2019) Recommended by the Educational-methodical association of the Republican educational-methodical council(protocol No.1, 23.10.2019)

> UDC 004.031 LBC 32.973.202

C Akhmetov B.S., Lakhno V.A., Malikova F.U. 2019

C AUPET, 2019

C IE Balausa, 2019

# CONTENT

| INTRODUCTION                                                           | 5   |

|------------------------------------------------------------------------|-----|

| CHAPTER 1. THE CONCEPT OF COMPUTER ARCHITECTURE.                       | 5   |

| CLASSIFICATIONS OF COMPUTER ARCHITECTURE                               | 6   |

| 1.1. History of computer engineering                                   | 7   |

| 1.2. Computer architecture classification systems                      | 18  |

| 1.3. The concept of information. Information measurement               | 22  |

| CHAPTER 2. FUNCTIONAL NODES OF A COMPUTER                              | 30  |

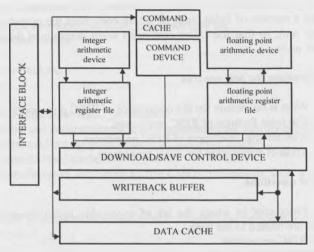

| 2.1. Arithmetic and logical device.                                    | 31  |

| 2.2. Control device.                                                   | 34  |

| 2.3. Input-Output devices.                                             | 37  |

| CHAPTER 3. ARITHMETIC FOUNDATIONS OF A COMPUTER                        |     |

|                                                                        | 41  |

| 3.1 Number systems and code concept                                    | 41  |

| 3.2. Arithmetic computer basics.                                       | 46  |

| 3.2.1 Fixed point number representation form                           | 47  |

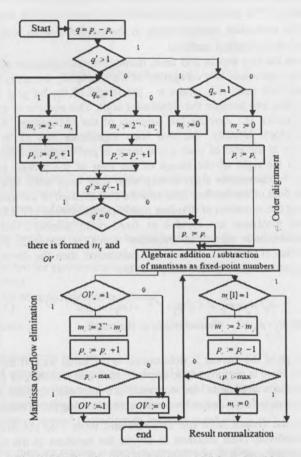

| 3.2.2. Floating point number representation form                       | 63  |

| CHAPTER 4. LOGICAL FOUNDATIONS OF A COMPUTER                           | 73  |

| 4.1. The logical basis for the construction and operation of computers | 73  |

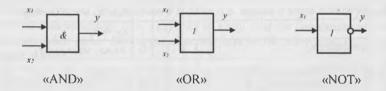

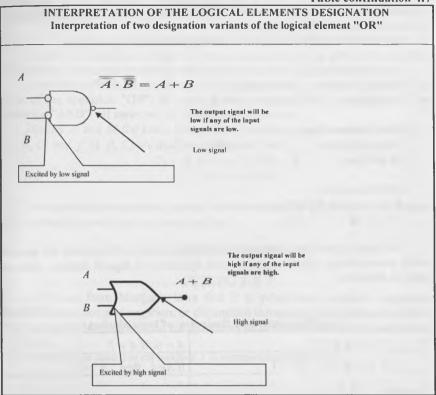

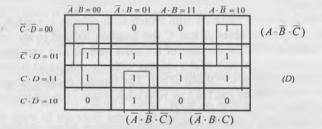

| 4.2. Electronic technology of computer logic elements                  | 88  |

| CHAPTER 5. MICROPROCESSOR SOFTWARE MODEL                               | 101 |

| CHAPTER 6. IA-32 PROCESSOR STRUCTURE                                   | 120 |

| CHAPTER 7. AMD PROCESSOR ARCHITECTURE                                  | 138 |

| CHAPTER 8. PROCESSOR OPERATING MODES                                   | 144 |

| CHAPTER 9. MULTI-CORE PROCESSORS                                       | 158 |

| CHAPTER 10. CO-PROCESSORS. METHODS FOR INFORMATION                     |     |

| EXCHANGE BETWEEN CPU AND CO-PROCESSOR                                  | 170 |

| CHAPTER 11. ORGANIZATION OF A MEMORY SUBSYSTEM IN A                    |     |

| COMPUTER                                                               | 179 |

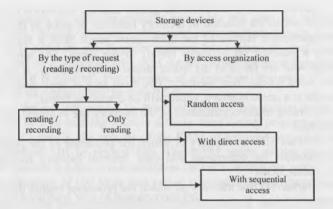

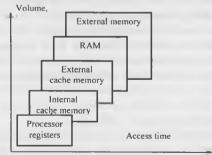

| 11.1. Key parameters and characteristics of the storage devices        | 179 |

| 11.2. Storage devices classification                                   | 182 |

| 11.3. Cache memory                                                     | 188 |

| 11.4. Random access memory (RAM)                                       | 192 |

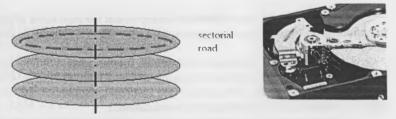

| 11.5. External computer memory                                         | 195 |

| CHAPTER 12. RISC PROCESSORS                                            | 202 |

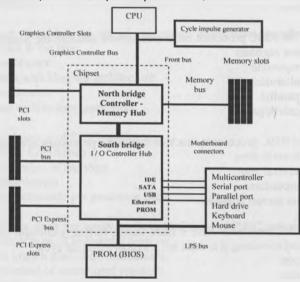

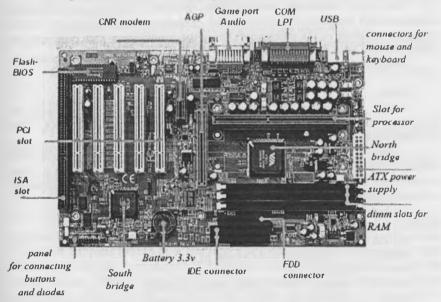

| CHAPTER 13. MOTHERBOARDS AND CHIPSETS                                  | 208 |

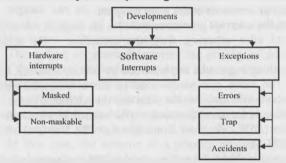

| CHAPTER 14. INTERRUPT AND EXCEPTION SYSTEM IN THE IA-32                |     |

| ARCHITECTURE.                                                          | 215 |

| 14.1. Interrupt and exception system of the processor                  | 215 |

| 14.2. Advanced Programmable Interrupt Controller (APIC)                | 220 |

| 14.3. Interrupt Handling Based on 8259A Controller                     | 221 |

| CHAPTER 15. TYPES AND CHARACTERISTICS OF INTERFACES                    | 225 |

| 15.1. System interfaces                                                | 225 |

| 15.2. Storage device interface                                         | 229 |

|                                                                        | /   |

| 15.3. Interfaces SCSI, RS-232C, IEEE 1284, USB, FireWire | 231 |

|----------------------------------------------------------|-----|

| 15.4. Wireless Interfaces                                | 237 |

| CHAPTER 16. INPUT-OUTPUT DEVICES                         | 243 |

|                                                          | 254 |

|                                                          | 265 |

|                                                          | 265 |

|                                                          | 268 |

|                                                          | 268 |

|                                                          | 277 |

| REFERENCES                                               | 284 |

#### **INTRODUCTION**

On the modern computer market there is a wide variety of different types of computers. Therefore, it is possible to assume that the consumer has a question - how to assess the capabilities of a particular type (or model) of a computer and its distinguishing features from computers of other types (models). Consideration of only the structural diagram of a computer for this is not enough, since it fundamentally differs little from different machines: all computers have RAM, a processor, and external devices. There are various ways, means and resources using which the computer operates as a single mechanism. In order to put together all the concepts that characterize a computer in terms of its functional program-controlled properties, there is a special term - computer architecture. For the first time, the concept of computer architecture began to be mentioned with the advent of the 3rd generation machines for their comparative evaluation.

This tutorial, consisting of 2 parts, discusses the basic elements of the modern computers architecture, as well as the fundamentals of machine mathematics and logic.

The first part includes sections devoted to the mathematical and logical fundamentals of computer operation, as well as a description of the software model and microprocessors structure of the IA-32 and AMD architecture.

In the second part of the tutorial, the following topics are discussed: processor operating modes, multi-core processor architecture, organization of the input-output subsystem, the basics of assembly language programming, etc.

# CHAPTER 1. THE CONCEPT OF COMPUTER ARCHITECTURE. CLASSIFICATIONS OF COMPUTER ARCHITECTURE

Computer architecture covers a wide range of problems associated with the construction of a complex of hardware and software means and many other factors. Among these components, the most important are: cost, sphere of application, functionality, ease of use.

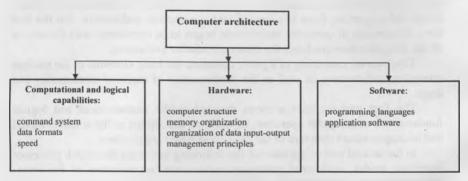

The main components of the computer architecture can be represented in the form of the circuit shown in Fig. 1.1.

Fig. 1.1. Key components of computer architecture

The architecture of a computing tool should be distinguished from its structure. The structure of a computing tool determines its specific composition at a certain level of detailization (devices, blocks, nodes, etc.) and describes the connections within the tool in its entirety. Architecture, however, defines the rules for the interaction of the components of a computing tool, the description of which is carried out to the extent necessary for the formation of the rules for their interaction. It regulates not all communications, but the most important ones that should be known for the most competent use of this tool.

So the computer user does not care on which elements the electronic circuits are executed, how the commands are implemented, etc. Another thing is important: what features are provided to the user, how these features are related to the structural features of the computer, how the characteristics of the individual devices that make up the computer are related, and what effect they have on the general characteristics of the machine. In other words, the computer architecture really reflects a range of issues related to the general design and construction of computers and their software.

Therefore, during the study the subject, we will, whenever possible, consider all components of the computer, including the structure of the computer, memory organization, organization of data input-output, principles of computer control, command systems, and the software composition. Before starting t study directly computers, firstly, we will study when and why they appeared, and in order to understand the basics of computers better, we will briefly dwell on what they work with and what they process, i.e. - information and methods for its presentation in computers.

#### 1.1. History of computer engineering

The beginning of technology development is considered to be from Blaise Pascal, who in 1642 invented a device that mechanically performs the addition of numbers. His machine was designed to work with 6-8 bit numbers and could only add and subtract, and also had a better way than everything else before, to fix the result [1, 5, 10]. Pascal's ideas had a huge impact on many other inventions in the field of computer technology.

The next stage in the development of computer technology and information theory is associated with the outstanding German mathematician and philosopher Gottfried Wilhelm Leibniz, who in 1672 expressed the idea of mechanical multiplication without sequential addition. A year later, at the Paris Academy, he introduced a machine that made it possible to perform mechanically four arithmetic operations [1, 10].

In 1812, the English mathematician Charles Babbage began working on the so-called difference machine, which was supposed to calculate any functions, including trigonometric ones, as well as make tables. However, due to lack of funds, this machine was not finished, and its mechanical part was handed over to the Royal College Museum in London, where it is stored as an exhibit. However, this failure did not stop Babbage. In 1834, he embarked on a new project to create an analytical machine that was supposed to perform calculations without human intervention. According to experts [1, 5, 6, 10, etc.], Babbage's merit lies in the fact that he first proposed, and partially realized, the idea of software-controlled computing.

In 1818, Thomas K. designed a calculating machine, focusing on the manufacturability of the mechanism, and called it an arithmometer. Within three years, 16 arithmometers were manufactured in Thomas' workshops. Thus, Thomas laid the foundation for counting engineering. His arithmometers were produced for a hundred years, constantly improving and changing the name from time to time [1, 10].

Since the 19th century, arithmometers have been very widely used. They performed even very complex calculations, for example, calculations of ballistic tables for artillery firing. By 1914, in the Russian Empire there were more than 22 thousand arithmometers [1].

Previously, when mankind did not know about electric and magnetic phenomena or did not yet know how to use them, the most accessible, and, therefore, convenient, was the mechanical form of representing information in computing devices. In arithmometers, operations on numbers were performed with the help of wheels, which at adding a unit rotated  $36^{\circ}$  and with the help of a pin set in motion the next wheel according to seniority each time when the number 9 went to the number 0 (a dozen accumulated). However, mechanical devices are bulky,

expensive and inertial (with their help it is impossible to create universal and highspeed computers). Therefore, now in all computers, electrical signals (most often DC voltage) are used as the main form of information representation. Computers were invented long time ago. In those days, electronics was not even mentioned. The first computers were vacuum tubes and took up a lot of space. However, at that time the basic principles of computer operation were laid down, which are still valid. Their essence is as follows. Data is transmitted using some kind of a signal by the method "there is a signal or not" or, in other words, "on or off." Due to this, there was appeared a *"bit"*. A bit is a unit of information that can take the value 0 or 1, that is, "on or off". Eight bits are combined into bytes, one byte is 8 bits. Why exactly 8? Yes, because the first computers were eight-bit and could only work with 8 bits at a time, for example, 010000111. All the first zeros can be deleted, so the number 010000111 can be written as - 10000111. This is the same as in the usual decimal number system, where each digit can take values from 0 to 9. Here, too, no one will write the number 6743 as 00006743.

In 1 byte, you can write any number from 0 to 255. The specified range of numbers is quite small. Therefore, there are often used larger gradations:

- two bytes = a word;

- two words = a double word.

In the first decades of the 20th century, designers paid attention to the possibility of using new elements in electromagnetic devices — electromagnetic relays. In 1941, a German engineer Konrad Zuse, created a computing device that runs on such relays.

Almost simultaneously, in 1943, American Howard Aiken, using Babbage's works based on 20th-century technology - electromechanical relays - created the legendary Harvard Mark -1 (Mark-1, and later Mark-2) at one of IBM's enterprises. Mark-1 had a length of 15 meters and a height of 2.5 meters, contained 800 thousand parts, had 60 registers for constants, 72 memory registers for addition, a central unit of multiplication and division, could calculate elementary transcendental functions. The machine worked with 23-digit decimal numbers and performed addition operations in 0.3 seconds, and multiplication in 3 seconds. However, Aiken made two mistakes: the first was that both of these machines were more electromechanical than electronic; the second is that Aiken did not adhere to the concept that programs should be stored in the computer's memory, like the data obtained [10].

At the same time, in England, the first relay computer began to work, which was used to decrypt messages transmitted by a German encoded transmitter. By the middle of the 20th century, the need for automation of computing (including for military purposes - ballistics, cryptography, etc.) became so great that several groups of researchers worked on the creation of machines like Mark-1 and Mark-2 in different countries.

Work on the creation of the first electronic computer was apparently begun in 1937 in the USA by professor John Atanasov, a Bulgarian by birth. This machine was specialized and intended for solving problems of mathematical physics. During the development, Atanasov created and patented the first electronic devices, which were subsequently used quite widely in the first computers. The full project of Atanasov was not completed, but after three decades, as a result of the trial, the professors were recognized as the founder of electronic computer technology [1, 5, 10].

Beginning from 1943, a group of specialists led by Howard Aiken, J. Mauchly, and P. Eckert in the USA began to design a computer based on electron tubes, rather than electromagnetic relays [1, 10]. This machine was named ENIAC (Electronic Numeral Integrator And Computer) and it operates a thousand times faster than the Mark-1. ENIAC contained 18 thousand vacuum tubes, occupied an area of 9-15 meters, weighed 30 tons and consumed a capacity of 150 kilowatts. ENIAC also had a significant disadvantage - it was controlled using a patch panel, it had no memory, and in order to set up a program, it was necessary to connect the wires in the right way for several hours or even days. The worst of all the disadvantages was the terrifying unreliability of the computer, since about a dozen vacuum tubes could fail during the day of work.

In order to simplify the process of setting programs, Mauchly and Eckert began to design a new machine that could store the program in its memory. In 1945, the famous mathematician John von Neumann was involved in the work, who prepared a report on this machine. In this report, von Neumann clearly and simply formulated the general principles of functioning of universal computing devices, i.e. computers. This is the first operating machine, created on vacuum tubes, was officially put into operation on February 15, 1946. They tried to use this machine to solve some problems prepared by von Neumann and related to the atomic bomb project. Then it was transported to the Aberdeen Proving Ground, where it worked until 1955.

ENIAC became the first representative of the 1st generation of computers. Any classification is conditional, but most experts agreed that the generation should be distinguished on the basis of the elemental base on which the machines were created.

The report of von Neumann and his colleagues G. Goldstein and A. Berks (June 1946) formulated requirements for the computer structure. Let note the most important of them [1, 6, 10, 12, 16]:

• machines on electronic elements should work not in decimal, but in binary number system;

• the program, like the initial data, must be located in the machine's memory;

• the program, like numbers, should be written in binary code;

• difficulties in the physical implementation of the storage device, whose speed corresponds to the speed of logical circuits, require a hierarchical organization of memory (that is, allocation of operational, intermediate and longterm memory);

• an arithmetic device (processor) is constructed on the basis of circuits that perform the addition operation; the creation of special devices for performing other arithmetic and other operations is impractical;

• the machine uses the parallel principle of organization of the computational process (operations on numbers are performed simultaneously for all digits).

Almost all the von Neumann recommendations were subsequently used in the machines of the first three generations, their combination was called "von Neumann architecture". The first computer in which von Neumann principles were embodied was created in 1949 by the English researcher Maurice Wilkes. Since then, computers have become much more powerful, but the vast majority of them were made in accordance with the principles that John von Neumann set forth in his report in 1945.

New first-generation machines replaced each other pretty quickly. In 1951, there was launched the first Soviet electronic computer MESM, with an area of about 50 square meters. MESM had 2 types of memory: random access memory, in the form of 4 panels 3 meters high and 1 meter wide; and long-term memory in the form of a magnetic drum with a volume of 5000 numbers. In total, MESM had 6000 electronic tubes, and it was possible to work with them only after 1.5-2 hours after turning on the machine. Data input was carried out using magnetic tape, and output – by digital printing device, conjugate with memory. MESM could perform 50 mathematical operations per second, memorize 31 numbers and 63 commands in RAM (there were 12 different commands in total), and consumed power equal to 25 kilowatts.

In 1952, the American EDWAC machine appeared. It is also worth noting the English computer EDSAC (Electronic Delay Storage Automatic Calculator) created earlier in 1949, the first machine with a stored program. In 1952, Soviet designers put into operation the BESM, the fastest machine in Europe, and in the following year in the USSR there began operating "Strela" - the first high-class production machine in Europe. Among the creators of domestic machines, the names of S.A. Lebedeva, B.Ya. Bazilevsky, I.S. Brooke, B.I. Rameeva, V.A. Melnikova, M.A. Kartseva, A.N. Mamlina. In the 1950s, other computers appeared: Ural, M-2, M-3, BESM 2, and Minsk 1, which embodied increasingly progressive engineering solutions.

Projects and implementation of Mark-1, EDSAC and EDVAC machines in England and in the USA, MESM in the USSR laid the foundation for the development of work on the creation of vacuum tube technology computers - first-generation serial computers. The development of the first electronic serial machine UNIVAC (Universal Automatic Computer) was started around 1947 by Eckert and Mauchly. The first model of the machine (UNIVAC-1) was created for the US Census Bureau and put into operation in spring of 1951. The synchronous, sequential computer UNIVAC-1 was created on the basis of the ENIAC and EDVAC computers. It worked with a frequency of 2.25 MHz and contained about 5000 electronic tubes.

Compared with the USA, the USSR and England the development of electronic computers in Japan, in the Federal Republic of Germany and Italy was delayed. The first Japanese "Fujik" machine was put into operation in 1956, mass production of computers in Germany began only in 1958.

The capabilities of the machines of the first generation were quite modest. So, their performance according to current concepts was small: from 100 (Ural-1) to 20,000 operations per second (M-20 in 1959). These figures were determined

primarily by the inertia of vacuum tubes and by the imperfection of storage devices. The amount of RAM was extremely small - an average of 2,048 numbers (words), this was not enough even to accommodate complex programs, even data. Intermediate memory was organized on bulky and slow-moving magnetic drums of relatively small capacity (5,120 words on BESM-1). Printing devices, as well as data input units, worked slowly. If we dwell on input-output devices in more detail, then we can say that since the beginning of the first computers, there has been revealed a contradiction between the high speed of central devices and the low speed of external devices. In addition, the imperfection and inconvenience of these devices was also revealed. The first data carrier in computers, as you know, was a punch card. Then came punching paper tapes or just punched tapes. They came from telegraph technology after in the beginning of the 19th century the father and son from Chicago, Charles and Howard Krama, invented teletype.

First-generation computers quickly left the stage because they did not find wide commercial application due to unreliability, high cost, and programming difficulties.

Semiconductors became the elemental base of the second generation. Without a doubt, transistors can be considered one of the most impressive miracles of the XX century.

A patent for opening a transistor was issued in 1948 to Americans D. Bardin and U. Brattein, and eight years later they, together with theorist W. Shockley, became Nobel Prize winners. Speed switching of the first transistor elements turned out to be hundreds of times higher than of tube ones, as its reliability and economy too. For the first time, memory on ferrite cores and thin magnetic films began to be widely used; there were tested inductive elements – parametrons.

The first onboard computer for installation on an intercontinental rocket – "Atlas" - was put into operation in the United States in 1955. The machine used 20 thousand transistors and diodes, it consumed 4 kilowatts. In 1961, the "Burrows" ground-based "STRETCH" computers controlled the spaceflight of "Atlas" rockets, and IBM's machines controlled the flight of astronaut Gordon Cooper. Under the control of the computer, there took place flights of unmanned vehicles of the "Ranger" type to the Moon in 1964, as well as the "Mariner" vehicle to the Mars. Similar functions were performed by Soviet computers.

In 1956, IBM company developed floating magnetic air cushion heads. Their invention made it possible to create a new type of memory - disk storage devices, the significance of which was fully appreciated in the following decades of the development of computer technology. The first disk storage devices appeared in the IBM-305 and RAMAC machines. The last one had a package consisting of 50 magnetically coated metal disks that rotated at a speed of 12,000 rpm. On the surface of the disc there were 100 tracks for recording data, for 10,000 signs each [1].

The first serial universal transistor computers were released in 1958 simultaneously in the USA, Germany and Japan.

In the Soviet Union, the first lampless machines "Setun", "Razdan" and "Razdan 2" were created in 1959 1961. In the 60s, Soviet designers developed

about 30 models of transistor computers, most of which began to be massproduced. The most powerful of them - "Minsk 32" performed 65 thousand operations per second. Entire families of machines appeared: Ural, Minsk, BESM [10].

The record holder among second-generation computers was BESM 6, which had a speed of about a million operations per second - one of the most productive in the world. The architecture and many technical solutions of this computer were so advanced and ahead of their time that it was successfully used almost until our time.

Especially for the automation of engineering calculations at the Institute of Cybernetics of the Academy of Sciences of the Ukrainian SSR under the leadership of Academician V.M. Glushkov there were developed computers MIR (1966) and MIR-2 (1969). An important feature of the MIR-2 machine was the use of a television screen for visual control of information and a light pen, with the help of which it was possible to correct data directly on the screen.

The construction of computer systems, which included about 100 thousand switching elements, would be simply impossible on the basis of lamp technology. The priority in the invention of integrated circuits, which became the elemental base of third-generation computers, belongs to the American scientists D. Kilby and R. Neuss, who made this discovery independently of each other. Mass production of integrated circuits began in 1962, and in 1964 the transition from discrete to integrated elements began to take place rapidly.

Despite the successes of integrated technology and the emergence of minicomputers, large machines continued to dominate in the 60s. Thus, the third generation of computers, originating inside the second generation, gradually grew out of it.

The first mass series of machines on integrated elements began to be produced in 1964 by IBM. This series, known as IBM-360, had a significant impact on the development of computer technology in the second half of the 60s. It combined a whole family of computers with a wide range of performance, moreover, compatible with each other. The last one meant that it became possible to connect machines into complexes, and also without any alterations to transfer programs written for one computer to any other in this series. Thus, there was identified for the first time a commercially viable requirement for standardizing computer hardware and software.

In the USSR, the first serial computer on integrated circuits was the "Nairi-3" machine, which appeared in 1970. In the second half of the 60s, the Soviet Union, together with the CMEA countries, began developing a family of universal machines similar to the IBM-360 system. In 1972, mass production began of the starting, least powerful model of the Unified System - the EC-1010 computer, and a year later - five other models. Their performance ranged from ten thousand (EC-1010) to two million (EC-1060) operations per second.

Within the framework of the third generation in the USA, a unique machine "ILLIAK-4" was created, in the structure of which in the initial version it was planned to use 256 data processing devices made on monolithic integrated circuits.

Later, the project was changed due to a rather high cost (more than \$ 16 million). The number of processors had to be reduced to 64, and also to switch to integrated circuits with a small degree of integration. A shortened version of the project was completed in 1972, the nominal speed of "ILLIAK-4" amounted to 200 million operations per second. For almost a year, this computer has been a champion in computing speed.

During the development of the third generation an extremely powerful computing industry arose, which began to produce computers for mass commercial use in large quantities. Computers are increasingly being incorporated into information systems or production management systems. They acted as an obvious lever of the modern industrial revolution.

The beginning of the 70s marks the transition to the fourth-generation computers - on ultra-large integrated circuits (ULIC). Another sign of a new generation of computers is a sharp change in architecture.

The equipment of the fourth generation gave rise to a qualitatively new computer element - a microprocessor. In 1971, they came up with the idea of limiting the capabilities of the processor by laying in it a small set of operations, the microprograms of which must be previously entered into the permanent memory. Estimates have shown that the use of a 16 kilobit read-only memory will eliminate 100,200 conventional integrated circuits. So the idea of a microprocessor arose, which can be implemented even on a single chip, and the program is written to its memory forever. At that time, in an ordinary microprocessor, the integration level corresponded to a density of about 500 transistors per square millimeter, and there was achieved very good reliability.

By the mid-70s, the situation in the computer market began to change abruptly and unexpectedly. Two concepts of computer development were clearly distinguished. Supercomputers became the embodiment of the first concept, and personal computers became the second one.

Beyond the fourth-generation large computers on ultra-large integrated circuits, American machines "Cray-1" and "Cray-2", as well as Soviet models "Elbrus-1" and "Elbrus-2" were especially distinguished. Their first samples appeared at about the same time - in 1976. All of them belong to the category of supercomputers, as they have extremely achievable characteristics for their time and a very high cost.

The fourth-generation machines made a departure from von Neumann architecture, which was the leading sign of the vast majority of all previous computers.

Multiprocessor computers, due to their enormous speed and architectural features, are used to solve a number of unique problems in hydrodynamics, aerodynamics, long-term weather forecasting, etc. Along with supercomputers, the fourth generation includes many types of mini-computers, which also rely on the elemental base of ultra-large integrated circuits.

Although personal computers belong to the fourth generation of computers, the possibility of their wide distribution, despite the achievements of ULIC technology, would remain very small.

In 1970, an important step was taken towards a personal computer - Marchian Edward Hoff, who worked at Intel, designed an integrated circuit that was similar in function to the central processor of a large computer. So there was the first Intel 4004 microprocessor, which was put on sale in 1971. This was a real breakthrough, because the Intel 4004 microprocessor less than 3 cm in size was more productive than the giant machines of the 1st generation. But the Intel 4004 capabilities were much more modest than that of the central processor of large computers of that time — it worked much slower and could only process 4 bits of information at a time (large computer processors processed 16 or 32 bits at a time), but its cost was in tens of thousands of times cheaper.

In 1972, the Intel 800 8-bit microprocessor appeared. The size of its registers corresponded to the standard unit of digital information - byte. The Intel 8008 processor was a simple development of the Intel 4004.

But in 1974, a much more interesting Intel 8080 microprocessor was created. From the very beginning of development, it was laid down as an 8-bit chip. He had a wider array of microcommands (the multitude of microcommands 8008 was expanded). In addition, it was the first microprocessor which could divide numbers. And until the end of the 70s, the Intel 8008 microprocessor became the standard for the microcomputer industry.

Several engineers of the company had ideas for improving the 8080. They left Intel to implement them. They organized Zilog Corporation, which presented the world with the Z80 microprocessor. In fact, the Z80 was a further development of the 8080 microprocessor. The number of its commands was simply increased, which made it possible to create and to use standard operating systems on personal computers.

Between 1970 and 1975, computer lovers' clubs sprang up throughout the United States. The most noteworthy was the Homebrew Computer Club, formed in March 1975 in Menlo Park, California. Its first members included Steve Jobs and Steve Wozniak, who later founded Apple Macintosh company.

Therefore, when the first microcomputer appeared, there was immediately a huge demand for it among thousands of fans. The first microcomputer was the "Altair-8800" created in 1974 by a small company in Albuquerque, New Mexico. This computer was sold for about \$500. And although its capabilities was very limited (RAM was only 256 bytes, there was no keyboard and screen), and there were also serious operational disadvantages, the Altair-8800 became a bestseller. Later, buyers themselves supplied this computer with additional devices: a monitor for outputting information, a keyboard, memory expansion units, etc. Soon, these devices began to be produced by other companies.

At the end of 1975, Paul Allen and Bill Gates (future founders of Microsoft) created the Basic language - interpreter for the "Altair" computer, which allowed users to simply communicate with the computer and easily write programs for it. It also contributed to the popularity of personal computers.

The success of the "Altair-8800" forced many companies also to engage in the production of personal computers. Personal computers began to be sold fully equipped, with a keyboard and a monitor, the demand for them amounted to tens, and then hundreds of thousands of pieces per year.

In 1979, Intel released the new Intel 8086/8088 microprocessor. Then the first Intel 8087 co-processor appeared. The frequencies at which the Intel-8086/8088 microprocessor could work were 4.77, 8 and 10 MHz.

In the late 70s, the spread of personal computers even led to some decrease in demand for large computers and mini-computers. This became a matter of serious concern for IBM, and in 1979, IBM decided to try its hand at the personal computer market.

First of all, Intel 8088, the then latest 16-bit microprocessor, was chosen as the main microprocessor of the computer. Its use significantly increased the potential of the computer, since the new microprocessor made it possible to work with 1 MB of memory, and then all available computers were limited to 64 KB. Other components of various companies were used in the computer, and its software was entrusted to be developed by small Microsoft company. And thus, in 1981, the first version of the operating system for the IBM PC computer appeared - MS DOS 1.0.

In August 1981, a new computer called "IBM Personal Computer" was officially presented to the public and shortly thereafter, it gained great popularity among users. The IBM PC had 64 Kb of RAM, a tape recorder for loading / saving programs and data, a drive and an integrated version of the BASIC language.

After one or two years, the IBM PC took a leading position on the market, displacing 8-bit computers.

IBM did not make its computer a single integral device and did not protect it with patents. On the contrary, it assembled a computer from independently manufactured parts and did not keep the specifications of these parts and how to connect them in secret. On the contrary, the design principles of IBM PC were available to everybody. This approach, called the "*principle of open architecture*", ensured tremendous success for the IBM PC, although it deprived IBM of the opportunity to use the benefits of this success alone.

A new generation of microprocessors replaces the previous one every two years and becomes obsolete in 3-4 years. The microprocessor, along with other microelectronic devices, allows to create fairly economical information systems.

The reason for the popularity of the microprocessor is that with their appearance there is no longer any need for special information processing schemes, it is enough to program its function and enter the microprocessor into the read-only memory (ROM).

After a short period of time, the IBM PC model was improved. The new modification was called the "expanded" IBM PC/XT (*Personal Computer/eXTended version*). In this modification, manufacturers abandoned the use of a tape recorder as a storage device, added a second floppy drive, as well as the ability to use a hard disk with a capacity of 10-30 MB. Nowadays, having a hard drive in an PC/XT is almost mandatory. The model was based on the use of the same microprocessor - Intel 8088.

In 1982, Intel launched the new Intel 80286 microprocessor, which had 134 thousand transistors and was developed using 1.5 micron technology (microns - micrometers or microns). He could work with 16 MB of RAM at frequencies: 8, 12 and 16 MHz. Its fundamental innovation - protected mode and virtual memory up to 1 GB in size - did not find mass application, the processor was mostly used as a very fast 8088.

In the same year, a new computer model was released under the name IBM PC/AT (*Personal Computer/Advanced Technolog* - "Advanced Technology PC"). Due to the use of the new microprocessor with the 80287 co-processor, the system performance increased more than in two times. It is equipped with floppy drives of a new type (with integrated volume of stored information), a hard disk of 40 MB or more. The bus of the PC motherboard is expanded to 16 bits.

The heat of competition forced IBM developers ultimately to abandon the principle of "open architecture". The new family of IBM PC models is called PS/2 ("Personal System/2"). It was absolutely incompatible with the first generation at the hardware level, but retains compatibility at the software level. The first models of the PS/2 family used the Intel 80286 microprocessor and actually copied the PC AT, but were based on a different architecture.

In 1985 there were appeared Intel 80386SX and Intel 80386DX. It discovered a class of 32-bit processors. The Intel 80386 microprocessor had 275 thousand transistors and was manufactured using 1.5 micron technology.

In 1987, Microsoft developed version 3.3 (3.30) of the MS DOS operating system, which became the standard for the next 3-4 years.

In 1989, Intel released a new microprocessor 80486SX/DX/DX2, which had 1.2 million transistors on a chip, and manufactured using 1 micron technology.

In June 1991, Microsoft released MS-DOS 5.0, which has its own characteristics: it has improved shell menu interfaces, a full-screen editor, utilities on disk and the ability to change tasks. The subsequent versions of MS-DOS 6.0, MS-DOS 6.21 and MS-DOS 6.22, in addition to the standard set of programs, include backup programs, an antivirus program, and other improvements in the operating system.

In 1992, the Intel 80486DX4 processor appeared with a frequency up to 100 MHz.

The following major development dates for Microsoft operating systems went along with the development of the personal computer hardware.

April 6, 1992 - Windows 3.1 OS released, which became the most popular in the USA (by the number of installations).

October 27, 1992 - Windows for Workgroups 3.1 released. It integrates features aimed at serving network users and workgroups, including email delivery, file and printer sharing, and scheduling. Version 3.1 was the forerunner of the small LAN boom, but failed commercially, receiving the offensive nickname "Windows for Warehouse".

November 8, 1993 - Windows for Workgrounds 3.11 released.

In 1993, the first Pentium processors with a frequency of 60 and 66 MHz appeared - these were 32-bit processors with a 64-bit data bus. In 1995, processors

for 120 and 133 MHz appeared, made using 0.35 micron technology, 1996 is called the year of Pentium - 150, 166 and 200 MHz processors appeared, and Pentium became an ordinary processor for PCs of wide application.

On August 24, 1995, Windows 95 was released.

July 25, 1998 Microsoft launches Windows 98, the latest version of Windows based on the old kernel, which runs on the foundation of DOS. Windows 98 is integrated with Internet Explorer 4 and is compatible with many, from USB to ACPI power management specifications.

On October 6, 1998, Intel announced a 450 MHz Pentium® II Xeon ™ processor for dual-processor (dual-channel) servers and workstations.

The last decade is characterized not only by the rapid growth of computer productivity, but also by the emergence of new approaches to increase their productivity. The main characteristics of computers of different generations are presented in table 1.1 [1, 5, 10, 16, 22].

#### Table 1.1

| The main characteristics of computers of various generations |                                                                  |                                                                                                                            |                                                                                        |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| generation                                                   | 1                                                                | 2                                                                                                                          | 3                                                                                      | 4                                                                                                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Period of<br>development,<br>yaers                           | 1946-1960                                                        | 1955-1970                                                                                                                  | 1965-1980                                                                              | 1980 – p.t.                                                                                                       | from 1990 r.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Elementary<br>base                                           | Vacuum<br>electronic<br>lamps                                    | Semiconductor<br>diodes and<br>transistors                                                                                 | Integrated<br>circuits                                                                 | Extra Large<br>Integrated<br>Circuits                                                                             | Nowadays, several<br>fundamentally different<br>directions are being                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Architecture                                                 | Von<br>Neumann<br>architecture                                   | Multiprogram<br>mode                                                                                                       | Local area<br>networks of<br>computers,<br>computer<br>systems for<br>collective use   | Multiprocessor<br>systems,<br>personal<br>computers,<br>global networks                                           | developed:<br>1) an optical computer in<br>which all components<br>will be replaced by their<br>optical counterparts<br>(optical repeaters, fiber-<br>optic communication<br>lines, memory based on<br>the principles of<br>holography;<br>2) a molecular computer,<br>the principle of which<br>will be based on the<br>ability of some molecules<br>to be in different states;<br>3) a quantum computer,<br>consisting of subatomic<br>sized components and<br>working on the principles<br>of quantum mechanics.<br>The fundamental<br>possibility of creating<br>such computers is<br>confirmed by both<br>theoretical work and the<br>existing components of<br>memory and logic<br>circuits. |  |  |

| Spess, op/c                                                  | 10 – 20 th.<br>op/c                                              | 100-500 - th.<br>op/c                                                                                                      | ≈1 mln. op/c                                                                           | Tens and<br>hundreds of<br>millions of op/c                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Software                                                     | Machine<br>languages                                             | Operating<br>Systems,<br>Algorithmic<br>Languages                                                                          | OS, interactive<br>systems,<br>computer<br>graphics<br>systems                         | Application<br>packages, data<br>and<br>knowledgebase<br>s, browsers                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| External devices                                             | Punch and<br>punched card<br>input devices                       | APD, teletypes,<br>MTD, MDD                                                                                                | Video<br>Terminals,<br>HDD                                                             | HDD, moderns,<br>scanners, laser<br>printers                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Application<br>areas                                         | Settlement<br>Tasks                                              | Engineering,<br>scientific,<br>economic<br>problems                                                                        | ACS, CADS,<br>scientific and<br>technical tasks                                        | Tasks of<br>management,<br>communication,<br>creation of<br>workstation,<br>word and<br>multimedia<br>processing, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| examples                                                     | ENIAC,<br>UNIVAC<br>(USA);<br>BESM - 1,2,<br>M-1, M-20<br>(USSR) | IBM         701/709           (USA)         BESM           BESM         -4, M-220, Minsk, BESM           -6         (USSR) | IBM 360/370,<br>PDP -11/20,<br>Cray-1 (USA);<br>EC 1050, 1066,<br>Elbrus 1,2<br>(USSR) | Cray T3 E, SGI                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

#### **1.2.** Computer architecture classification systems

In 1966, M. Flynn proposed an extremely convenient approach to the classification of computing system architectures [2, 5, 12, 16, 17, etc.]. It was based on the concept of a stream, which is understood as a sequence of elements, commands, or data processed by a processor. The corresponding classification system is based on the consideration of the number of instruction streams and data streams and describes four architectural classes [12, 13, 16, 18]:

**SISD** = Single Instruction Single Data;

**MISD** = Multiple Instruction Single Data;

SIMD = Single Instruction Multiple Data;

MIMD = Multiple Instruction Multiple Data.

Below are the decrypted notations of these architectural classes, respectively:

**SISD** – a single instruction stream / single data stream. The **SISD** class includes serial computer systems that have one central processor capable of processing only one stream of sequentially executed instructions. Nowadays, almost all high-performance systems have more than one central processor, however, each of them executes unrelated instruction streams, which makes such systems complexes of SISD-systems operating in different data spaces. In order to increase the speed of commands processing. In case of vector systems, a vector data stream should be considered as a stream of single indivisible vectors. Examples of computers with SISD architecture are the majority of Compaq, Hewlett-Packard, and Sun Microsystems workstations [16, 17];

MISD - a multiple instruction stream / single data stream. Theoretically, in this type of machine, many instructions should be executed on a single data stream. So far, not a single real machine falling into this class has been created;

**SIMD** – a single instruction stream / multiple data stream. These systems usually have a large number of processors, from 1024 to 16384, which can execute the same instruction regarding different data in a hard configuration. A single instruction is executed in parallel on many data elements. Examples of **SIMD** machines are CPP DAP, Gamma II, and Quadrics Apemille [16, 17, 20]. Another subclass of **SIMD** systems is vector computers. Vector computers manipulate arrays of similar data similar to how scalar machines process individual elements of such arrays. This is done through the use of specially designed vector central processing units. When data is processed by means of vector modules, the results can be output on one, two or three cycles of the frequency generator (cycle of the frequency generator is the main parameter of the system). Working in vector mode, vector processors process data almost in parallel, which makes them several times faster than at working in scalar mode. Examples of systems of this type are, for example, Hitachi S3600 computers [16, 18];

**MIMD** – a multiple instruction stream / multiple data stream. These machines simultaneously execute multiple instruction streams on different data streams. Unlike multiprocessor SISD machines, commands and data are related because they represent different parts of the same task. For example, MIMD systems can simultaneously perform many sub-tasks in order to reduce the execution time of the main task. A wide variety of systems falling into this class makes Flynn's classification not entirely adequate. Indeed, both the NEC fourprocessor SX-5 and the thousand-processor Cray T3E fall into this class. This forces us to use a different classification approach, which otherwise describes the classes of computer systems. The main idea of this approach may consist, for example, in the following. We assume that a multiple command stream can be processed in two ways: either by a single conveyor processing device operating in time-sharing mode for individual threads, or each stream is processed by its own device. The first feature is used in MIMD computers. They are usually called conveyor or vector, the second - in parallel computers. Vector computers are based on the concept of conveyor, i.e. explicitly segmenting the arithmetic device into separate parts, each of which performs its own subtask for a pair of operands. A parallel computer is based on the idea of using several processors working together to solve a single problem, and processors can be either scalar or vector.

For parallel computer systems, there is a classification.

# I. Vector-Conveyor Computers (PVP).

They have a MIMD architecture (a lot of instructions on a lot of data). Kev features:

- conveyor functional devices:

- a set of vector instructions in the command system:

- command engagement (used as a means of speeding up calculations).

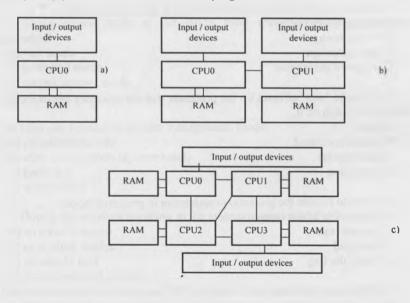

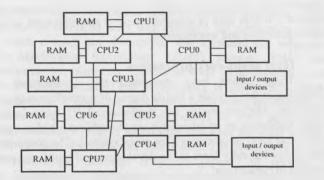

### II. Massively parallel computers with distributed memory.

There are combined several serial microprocessors, each with its own local memory, through some communication environment.

Such architecture has many advantages: if you need high performance, you can add more processors; if finances are limited or the required computing power is known in advance, then it is easy to choose the optimal configuration, etc.

Each processor has access only to its local memory, and if the program needs to know the value of a variable located in the memory of another processor, then the message transfer mechanism is activated. This approach allows to create computers that include thousands of processors.

But this architecture has two significant disadvantages:

• there is required a high-speed communication equipment that provides a messaging environment;

· during the creation of programs, it is necessary to take into account the topology of the system and to distribute data between processors in a special way in order to minimize the number of transfers and the amount of transferred data.

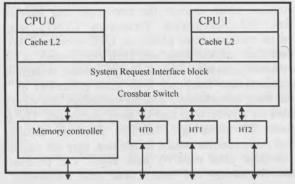

The last circumstance prevents the widespread adoption of such architectures. III. Parallel computers with shared memory (SMP).

All RAM is shared between several identical processors. This removes the problems of the previous class, but adds new ones - the amount of processors with access to shared memory cannot be large.

The main advantage of such computers is the relative ease of programming. In a situation where all processors have equally fast access to shared memory, the question which processor will perform which calculations will not be so crucial, and a significant part of the computational algorithms developed for serial computers can be accelerated using parallelizing and vectorizing translators. SMP computers are the most common parallel computers today. However, the total amount of processors in SMP systems, as a rule, does not exceed 16, and their further increase does not give a gain due to conflicts at accessing memory.

#### IV. Cluster architecture.

Cluster architecture is a combination of the previous three types. A computing node is formed from several processors (traditional or vector-conveyor) and a common memory for them. If the received computing power is not enough, then several nodes are combined with high-speed channels.

Let consider a few more common criteria for classifying computers.

- Classification by purpose [2, 5, 6, 8, 13, 15]:

- · large electronic computers or Main Frame;

- mini-computers;

- microcomputers;

- personal computers.

Classification by level of specialization [2, 5, 6, 8, 13, 15, 18]:

- universal;

- specialized.

- Classification by the size:

- desktop;

- portable (notebook);

- pocket (palmtop).

- Classification by compatibility:

- hardware compatibility (IBM PC platform and Apple Macintosh);

- compatibility at the operating system level;

- software compatibility;

- data level compatibility.

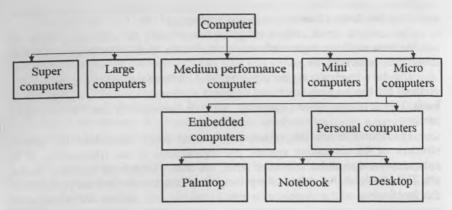

Therefore, choosing the above listed characteristics as the classification criteria, first of all, computing power and dimensions, we obtain the following scheme, see Fig. 1.2.

It should be noted that any classification is conditional, since the development of computer science and technology is so rapid that, for example, today's microcomputers are not inferior in power to mini computers, to supercomputers of the recent past. In addition, the assignment of computers to a certain class is rather arbitrary through the fuzziness of the separation of groups, and as a result of the implementation of custom assembly of computers, where the nomenclature of nodes and specific models are adapted to customer requirements.

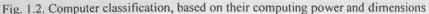

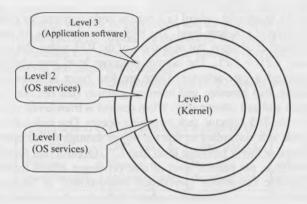

In the organization of a digital computing system, there can be distinguished nine levels of the hierarchy, shown on Fig. 1.3.

| 1. High level languages      |

|------------------------------|

| 2. Assembler Language Level  |

| 3. Operating system level    |

| 4. Machine Instruction Level |

| 5. Microarchitectural level  |

| 6. System Engineering Level  |

| 7. Digital Circuitry Level   |

| 8. Analog Circuitry Level    |

| 9. Physical level            |

Fig. 1.3. Levels of hierarchy in the organization of a digital computing system

The first level, *physical*, combines the physical laws, phenomena and effects that underlie the creation and functioning of the hardware component of a

computing system. This is the level of integrated and functional microelectronics, providing the element base of computing equipment.

The second level, *the analog circuitry level*, is associated with the construction of basic logic elements (gates) from analog components (diodes, transistors, capacitors, etc.).

The third level, *the digital circuitry level*, defines the principles, models and methods for constructing functional units and equipment devices in a given logical basis. This level has its own hierarchy, which is presented in detail in the chapter section.

The fourth level, *the system engineering level*, determines the general structure of the computing system, the organization of the relationships of its subsystems and modules with each other, the choice of optimal operating modes, etc. This is a level that reflects the principles of construction and the principles of the functioning of the system as a whole, taking into account the influence of external factors, technical, economic and other indicators. At this level, to a first approximation, the functions are distributed between the hardware and software components of the architecture of the computing system.

The fifth level, *microarchitectural*, is associated with the organization of computer hardware management in the language of microcommands. This is the level of interpretation of machine instructions at which effective instruction execution technologies are implemented (hardware or firmware) using instruction prefetching, conveyor method, parallelization, caching, dynamic branch prediction, renaming registers and other techniques that contribute to increasing the efficiency of the computing process.

The sixth level, *the machine instructions level*, represents a set of commands (instructions) executed by hardware or an interpreter firmware. This is a connecting link between hardware and software, therefore, its organization should be rational both from the point of view of hardware developers and from the point of view of creators of translator programs from high-level languages.

The seventh level, *the operating system level*, differs from the previous one by the presence of additional commands, its memory organization, multiprogram mode and other extensions implemented by a special interpreter created on the basis of the sixth and possibly fifth levels and which is called *the operating system*.

The last three of the considered levels are initially planned as a tool environment for system software creation (translators, operating systems shells and other extensions supporting higher level languages). In contrast, the means of the eighth and ninth levels are oriented on the applied programmers.

# 1.3. The concept of information. Information measurement

Information is always presented as a message. The basic unit of a message is a symbol. Symbols are grouped together - words.

A message in the form of words or individual characters is always transmitted in the material-energy form (electrical signal, light, etc.).

There is distinguished continuous and discrete information.

The function x(t) can be represented in a continuous and discrete form. In continuous form, this function can take any real values in a given range of changes of the argument t, i.e. the set of values of a continuous function is infinite. In a discrete form, the function x(t) can take real values only for certain values of the argument. No matter how small a discrete interval t is chosen, the set of values of the discrete function for a given range of argument changes will be finite. A structural approach distinguishes between geometric, combinatorial and additive measures of information. A geometric measure involves measuring a parameter of the geometric model of an information message (length, area, volume) in discrete units.

The maximum possible amount of information in the given structures determines the information capacity of the model (system), which is defined as the sum of discrete values for all dimensions (coordinates). In a combinatorial measure, the amount of information is defined as the number of combinations (elements). The possible amount of information coincides with the number of possible combinations, permutations and placements of elements. Additive measure (Hartley measure). In accordance with this measure, the amount of information is measured in binary units - bits. There are introduced the concepts of the depth "q" of the number and the length "n" of the number. The depth of the number "q" - the number of characters (elements) adopted to represent the information (this is the basis of the number system). At any moment of time, one symbol is realized. The length of the number "n" - the number of positions necessary and sufficient to represent numbers of a given value. At a given "q" and "n", the number of all possible displayed states is  $N=a^n$ . The value of N is not convenient for assessing information capacity. We introduce a logarithmic measure that allows to calculate the amount of information - bit [11]:

# I(q) = log N = nlog q.

Therefore, 1 bit of information corresponds to one elementary event, which may or may not occur. This allows to operate with a measure as with a number. The amount of information is equivalent to the amount of binary characters "0" or "1".

If there are several sources of information, the total amount of information is [9, 11]:

$$I(q, q, ..., q) = I(q) + I(q) + ... + I(q).$$

The transmission of information is a random process, because the content of the transmitted message is not known in advance. Interferences affecting the process of transmitting information are also of a random nature.

Therefore, the study of the laws of transmission and transformation of information is carried out by methods of probability theory, and information theory is sometimes called the statistical theory of message transmission.

At the same time, the theory of information is often and narrowly regarded as a theory of a measure of the amount of information and coding. The introduction of a numerical measure of the amount of information allows:

• to compare different messages according to their content;

• to evaluate the speed of information transfer in various systems;

• to compare these systems for effectiveness;

• to determine the maximum amount of information that can be transmitted in these specific conditions.

The need for information transfer arises only when the system may have a number of random states. It is assumed that the probabilities of the system in these states are known a priori.

About the system state we learn by message. A message about an event whose occurrence is known in advance does not contain information.

From two messages, one of which contains the results of two possible outcomes (throwing a coin), and the other results of six possible outcomes (throwing a dice), the second contains more information.

In the first case, the uncertainty of the outcome was relatively small, therefore, even before receiving the message that, for example, there is an "eagle" with a probability of P=1/2, it is possible to predict the occurrence of the outcome.

In the second case, P=1/6, the uncertainty was much greater, and, therefore, the receipt message to a greater extent contains an element of surprise, of novelty.

Therefore, the amount of information contained in a message can be quantified by the probability of occurrence of this message.

This evaluation criterion allows to establish an objective numerical measure of the amount of information contained in any possible messages, regardless of their specific meaning.

In accordance with the above mentioned, the requirements that must be met by the measure of the amount of information can be formulated as follows:

1. The amount of information contained in this message should not be determined by its specific meaning, but only by the degree of uncertainty removed upon receipt of this message.

2. The amount of information should be zero if the event of interest has only one outcome.

3. The principle of additivity should be observed, i.e. the amount of information contained in this message should be proportional to its length.

In case of equally probable events (messages), the logarithm of the inverse probability of each of them is taken as a numerical measure of the amount of information. If we use the binary logarithm and get N=2, then I=log2=1.

As a unit of information quantity, it is customary to consider such a quantity of information that removes uncertainty at choosing one of two equally probable outcomes. This unit is called a binary unit or bit. In the general case of receiving unequal messages, the uncertainty of the appearance of a particular (*i*-th) message is characterized by its probability  $P_i$ .

Information processed by the computer is represented by the corresponding symbols. Information is diverse - from numbers to music.

The semantic measures of information are considered:

- content;

- logical amount;

- expediency.

The content of the event *i* through the measure function m(i) is the content of its negation.

The logical functions of truth m(i) and false m(i)=1-m(i) have formal similarities with the probability functions of the events P(i) and q(i)=1-P(i). The logical amount of information I is calculated by the formula:

I = log(1/m(i)) = -log m(i).

The difference between a statistical estimate and a logical one is that in the first case the probabilities of the implementation of certain events are taken into account, that brings us closer to information meaning assessment. The measure of the expediency of information is defined as the change in the probability of achieving a goal when additional information is obtained

$$I_{uen} = log P_n - log P_\kappa = log P_n / P_\kappa$$

.

where  $P_{\mu}$ ,  $P_{\kappa}$  - initial and final probabilities of achieving the goal.

Electronic computers, i.e. computers, are designed to process digital information.

A computing machine - a physical system designed to automate the process of algorithmic information processing. Thus, the concept of "computing machine" (CM) is most closely related to the concepts of "information" and "algorithmic processing" [2, 5, 6].

The object of transmission and conversion in computing systems (machines) is information. In this sense, a CM (system) can be called informational.

Information is presented in the form of drawings, text, sound and light signals, energy pulses, etc. and transmitted by signals of any physical nature along the lines of communication of the source with the receiver.

Algorithmic processing - the information processing in accordance with a previously developed algorithm.

An algorithm - a rule (rules) formulated in a certain language that defines actions whose sequential execution leads from the initial data to some result.

Therefore, the specificity of information processes consists not only in the transmission of information messages through a given physical environment, but also in the transformation, processing and storage of information.

Information defines many processes in a CM. In the most general form, the process of solving a problem on a CM goes through the following steps:

1 - input of information or initial data set;

2 - processing or conversion of the input information;

3 - determination of results and processed information output.

Modern computers can solve a wide variety of problems. In order to do this, you just need to use the program to "train" the computer the algorithm for solving a particular problem and to set initial data into it. The program is written in an algorithmic language (for example, Pascal, C ++ or BASIC), which is quite close to the natural language (especially English).

However, the computer does not understand not only natural language, but also algorithmic. In order to decrypt the text of a program written in Pascal or C  $^{++}$ , the machine must have a special program - a compiler (translator), which translates the text of the original program from C  $^{++}$  or Pascal to the computer language. Therefore, a computing machine - a technical device in which information about the initial data of the problem, the rules for its solution (algorithm) and the results of the calculations must be set in the form of a change in any physical quantities:

- the magnetization of the material (such as, for example, to play a melody using a tape recorder or to save data on certification of students in the curriculum disciplines on a magnetic disk);

- screen illumination (display), etc.

#### Questions for self-control

- 1. What are the generations of computers?

- 2. By what criteria are computers classified?

- 3. What are the levels of hierarchy in the organization of a digital computing system?

- 4. What is the structural diagram of the computer?

- 5. Define the concept of information. What is an algorithm?

#### **Test questions**

1. What is the peculiarity of von Neumann architecture?

A) Separate areas of physical memory for storing data and commands (instructions).

B) A single area of physical memory for storing data and commands (instructions).

C) The CISC command system is used.

D) All answers are incorrect.

2. In what year was the first serial microprocessor released?

- A) 1971

- B) 1968

- C) 1945

- D) 1956

3. What modifications in the development of the IA-32 architecture appeared in the i486 microprocessor?

A) 32-bit external data bus

B) SIMD floating point number processing

C) SIMD fixed point number processing

D) embedded floating point number processor.

4. What was the very first Intel processor called?

A) intel 1001

B) intel 2201

C) intel 8008

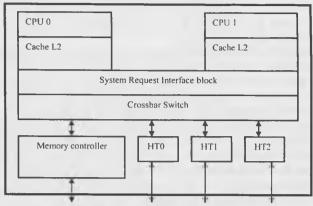

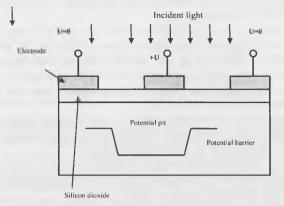

D) intel 4004