Yan Li Deepak Goyal *Editors*

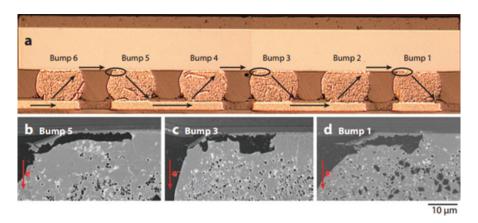

# Microelectronic Packaging

From Fundamentals to Applications

#### **Springer Series in Advanced Microelectronics**

#### Volume 57

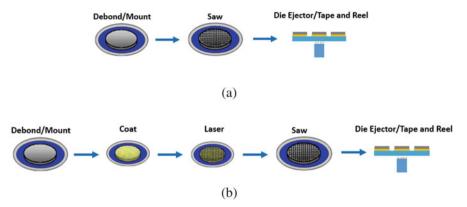

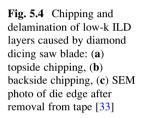

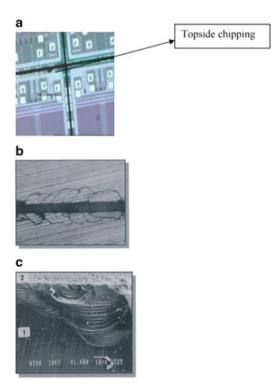

#### **Series Editors:**

Kukjin Chun, Seoul, Korea, Republic of (South Korea) Kiyoo Itoh, Tokyo, Japan Thomas H. Lee, Stanford, CA, USA Rino Micheloni, Vimercate (MB), Italy Takayasu Sakurai, Tokyo, Japan Willy M.C. Sansen, Leuven, Belgium Doris Schmitt-Landsiedel, München, Germany The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists.

Yan Li • Deepak Goyal Editors

# 3D Microelectronic Packaging

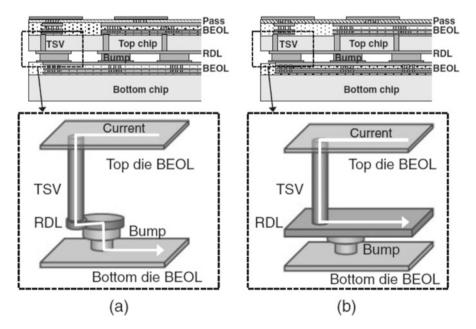

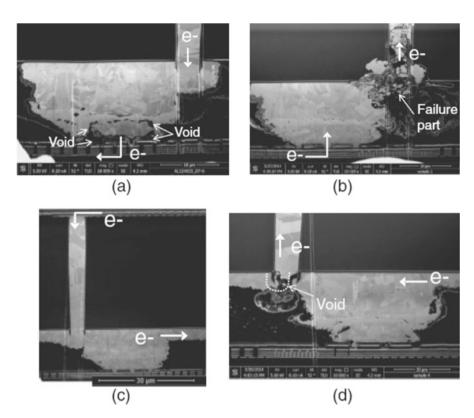

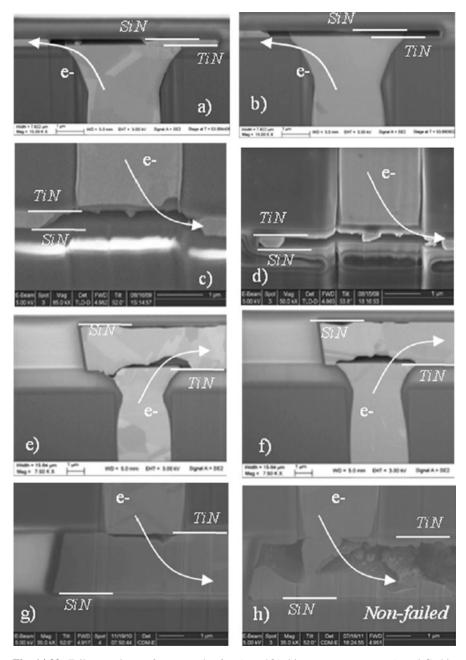

From Fundamentals to Applications

Editors

Yan Li

Intel Corporation

Chandler, AZ, USA

Deepak Goyal Intel Corporation Chandler, AZ, USA

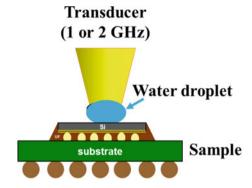

ISSN 1437-0387 ISSN 2197-6643 (electronic) Springer Series in Advanced Microelectronics ISBN 978-3-319-44584-7 ISBN 978-3-319-44586-1 (eBook) DOI 10.1007/978-3-319-44586-1

Library of Congress Control Number: 2016954441

#### © Springer International Publishing Switzerland 2017

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper

This Springer imprint is published by Springer Nature

The registered company is Springer International Publishing AG

The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

## **Contents**

| 1 | Yan Li and Deepak Goyal                                                                                                                       | 1   |  |  |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 2 | <b>3D Packaging Architectures and Assembly Process Design</b> Ravi Mahajan and Bob Sankman                                                    | 17  |  |  |  |

| 3 | Materials and Processing of TSV                                                                                                               | 47  |  |  |  |

| 4 | Microstructural and Reliability Issues of TSV                                                                                                 |     |  |  |  |

| 5 | Fundamentals and Failures in Die Preparation for 3D Packaging                                                                                 | 101 |  |  |  |

| 6 | Direct Cu to Cu Bonding and Other Alternative Bonding Techniques in 3D Packaging  Tadatomo Suga, Ran He, George Vakanas, and Antonio La Manna | 129 |  |  |  |

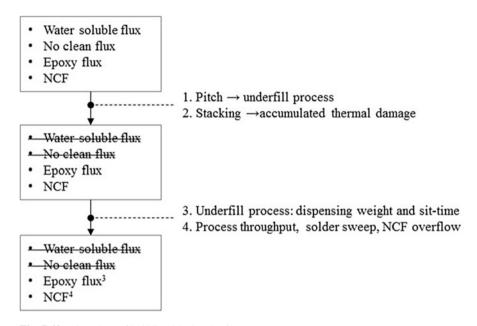

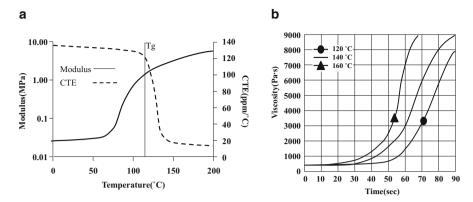

| 7 | Fundamentals of Thermal Compression Bonding Technology and Process Materials for 2.5/3D Packages                                              | 157 |  |  |  |

| 8 | Fundamentals of Solder Alloys in 3D Packaging                                                                                                 | 205 |  |  |  |

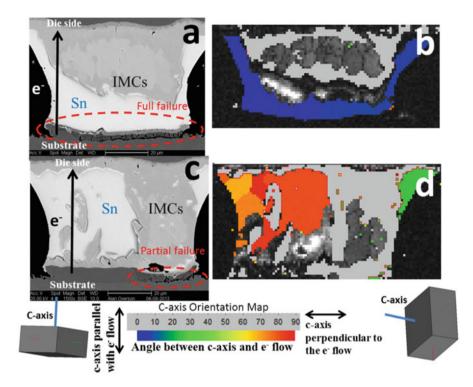

| 9 | Fundamentals of Electromigration in Interconnects of 3D Packaging                                                                             | 223 |  |  |  |

vi Contents

| 10  | Fundamentals of Heat Dissipation in 3D IC Packaging Satish G. Kandlikar and Amlan Ganguly                                                                      | 245 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11  | Fundamentals of Advanced Materials and Processes in Organic Substrate Technology                                                                               | 261 |

| 12  | Die and Package Level Thermal and Thermal/Moisture<br>Stresses in 3D Packaging: Modeling and Characterization<br>Liangbiao Chen, Tengfei Jiang, and Xuejun Fan | 293 |

| 13  | Processing and Reliability of Solder Interconnections in Stacked Packaging                                                                                     | 333 |

| 14  | Interconnect Quality and Reliability of 3D Packaging Yaodong Wang, Yingxia Liu, Menglu Li, K.N. Tu, and Luhua Xu                                               | 375 |

| 15  | Fault Isolation and Failure Analysis of 3D Packaging Yan Li and Deepak Goyal                                                                                   | 421 |

| Ind | lex                                                                                                                                                            | 461 |

#### **Contributors**

**Liangbiao Chen** Department of Mechanical Engineering, Lamar University, Beaumont, TX, USA

**Paul Conway** The Wolfson School of Mechanical, Electrical and Manufacturing Engineering, Loughborough University, Loughborough, Leicestershire, UK

**Indranath Dutta** School of Mechanical and Materials Engineering, Washington State University, Pullman, WA, USA

**Xuejun Fan** Department of Mechanical Engineering, Lamar University, Beaumont, TX, USA

**Amlan Ganguly** Computer Engineering Department, Rochester Institute of Technology, Rochester, NY, USA

Deepak Goyal Intel Corporation, Chandler, AZ, USA

Ran He The University of Tokyo, Tokyo, Japan

**Zhiheng Huang** School of Materials Science and Engineering, Sun Yat-sen University, Guangzhou, China

**Tengfei Jiang** Department of Material Science and Engineering, University of Central Florida, Orlando, FL, USA

**Satish G. Kandlikar** Mechanical Engineering Department, Rochester Institute of Technology, Rochester, NY, USA

**Praveen Kumar** Department of Materials Engineering, Indian Institute of Science, Bangalore, India

Sangil Lee, Ph.D. Invensas Corporation, San Jose, CA, USA

**Menglu Li** Department of Materials Science and Engineering, University of California, Los Angeles (UCLA), Los Angeles, CA, USA

Yan Li Intel Corporation, Chandler, AZ, USA

viii Contributors

**Kwang-Lung Lin** Department of Materials Science and Engineering, National Cheng Kung University, Tainan, Taiwan, R.O.C.

Pilin Liu Intel Corporation, Chandler, AZ, USA

**Yingxia Liu** Department of Materials Science and Engineering, University of California, Los Angeles (UCLA), Los Angeles, CA, USA

**Ravi Mahajan** High Density Interconnect Pathfinding, Assembly Technology, Intel Corporation, Chandler, AZ, USA

Antonio La Manna IMEC Consortium, Leuven, Belgium

Erasenthiran Poonjolai Intel Corporation, Chandler, AZ, USA

**Bob Sankman** High Density Interconnect Pathfinding, Assembly Technology, Intel Corporation, Chandler, AZ, USA

Hualiang Shi Intel Corporation, Chandler, AZ, USA

Songhua Shi Medtronic, Tempe, AZ, USA

Tadatomo Suga The University of Tokyo, Tokyo, Japan

Peter Tortorici Medtronic, Tempe, AZ, USA

**K. N. Tu** Department of Materials Science and Engineering, University of California, Los Angeles (UCLA), Los Angeles, CA, USA

George Vakanas Intel Corporation, Chandler, AZ, USA

Paul Vianco Sandia National Laboratories, Albuquerque, NM, USA

**Yaodong Wang** Department of Materials Science and Engineering, University of California, Los Angeles (UCLA), Los Angeles, CA, USA

Luhua Xu Intel Corporation, Chandler, AZ, USA

#### **About the Authors**

**Deepak Goyal** graduated (Ph.D.) from State University of New York, Stony Brook, and joined Intel as a Failure Analysis Engineer. He is currently the Technical Leader of the Assembly and Test Technology Development (ATTD) Failure Analysis Labs at Intel, supporting the materials and failure analysis of all assembly technology development at Intel and developing the next generation of analytical tools and techniques. He is an expert in the failure analysis of packages and has taught Professional Development courses on Package FA/FI and failure mechanisms at the ECTC from 2003 to present. He has won two Intel Achievement Awards and around 25 Division Recognition Awards at Intel. He has around 50 publications and has been awarded three patents and has ten patents filed. He was the chair of the Package and Interconnect Failure Analysis Forum sponsored by the International Sematech. He is a senior member of the IEEE. He has coauthored a chapter titled "Applications of terahertz technology in the semiconductor industry" in the Handbook of Terahertz Technology for Imaging, Sensing and Communications, 2013. He has also coauthored and edited two chapters for a book titled Characterization and Metrology for Nanoelectronics and *Nanostructures*, which will be published in November 2016.

Yan Li is currently a senior staff packaging engineer in the Assembly Test and Technology Development Failure Analysis Lab of Intel Corporation located in Chandler, Arizona. She joined Intel in 2006, and her work focuses on the quality and reliability of electronic packages, fundamental understanding of failure modes and failure mechanisms of electronic packages, and developing new tools and techniques for fault isolation and failure analysis of electronic packages. Yan received her Ph.D. in materials science and engineering from Northwestern University in 2006 on studies related to the synthesis and characterization of boron-based nanowires and nanotubes. She is actively involved in professional associations, such as Minerals, Metals and Materials Society (TMS), American Society for Metals (ASM) International, and Electronic Device Failure Analysis Society (EDFAS), serving as conference organizers and session chairs for more than 5 years.

# **Chapter 1 Introduction to 3D Microelectronic Packaging**

Yan Li and Deepak Goyal

#### 1.1 Introduction

Microelectronic packaging is the bridge between the Integrated Circuit (IC) and the electronic system, which incorporates all technologies used between them [1]. Advanced 3D microelectronic packaging technology is the industry trend to meet portable electronics demand of ultra-thin, ultra-light, high performance with low power consumption. It also opens up a new dimension for the semiconductor industry to maintain Moore's law with a much lower cost [1–3].

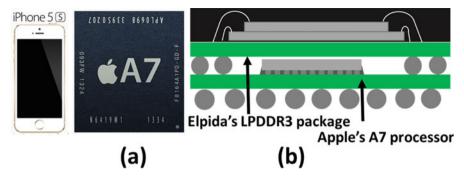

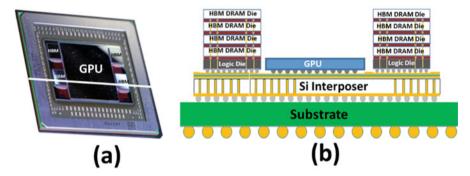

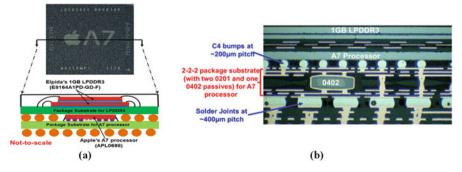

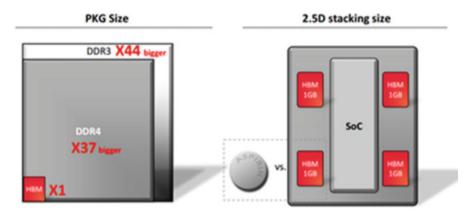

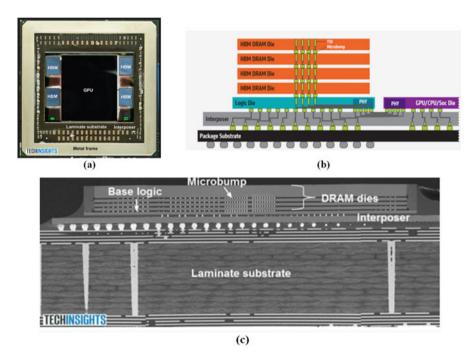

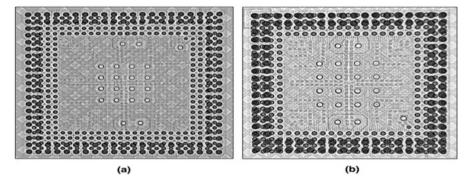

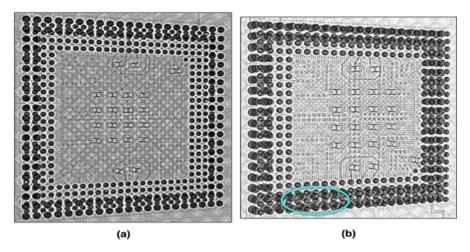

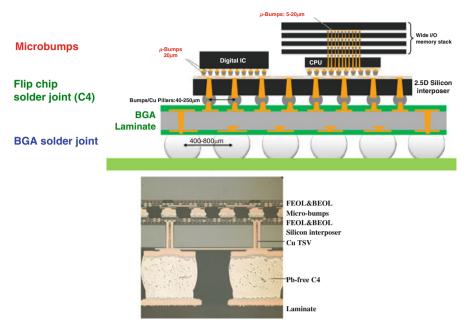

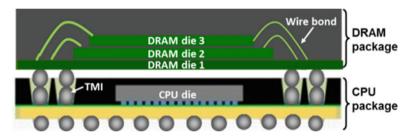

A wide variety of real products assembled by the advanced 3D packaging technology have been unveiled in the recent years. For example, the Apple A7 inside the iPhone 5S, introduced in September 2013, is a 3D package with Package on Package (POP) configuration [4]. As displayed in Fig. 1.1, the wire bond Elpida (now Micron) memory (low power double data rate type-3 (LPDDR3) mobile random access memory (RAM)) package is stacked on top of the Apple A7 flipchip package to achieve better performance with smaller form factor. In early 2014, SK Hynix announced its high bandwidth memory (HBM) products having higher bandwidth, less power consumption, and substantially small form factor, achieved by stacking up to eight DRAM dice interconnected through Through Silicon Vias (TSV) and micro-bumps [5]. In July of 2015, AMD introduced the AMD Radeon<sup>TM</sup> Fury graphics cards, the first Graphic Processing Unit (GPU) to implement HBM by TSVs and micro-bumps [6]. Figure 1.2 shows a top-down and schematic crosssectional view of the advanced 3D package. The big GPU die is integrated into the Si interposer along with four HBM memory stacks by micro-bumps and TSVs to ensure faster and shorter connection between chips [6]. These real products bring

Y. Li (⋈) • D. Goyal Intel Corporation, Chandler, AZ, USA e-mail: yan.a.li@intel.com

1

Fig. 1.1 POP inside iPhone 5s. (a) Top view of the Apple A7 package, (b) schematic of the cross-sectional view (not in scale), (adapted from Ref. [4])

**Fig. 1.2** Top view (a) and schematic cross-sectional view (not in scale), (b) of the AMD Radeon<sup>TM</sup> Fury. The big GPU die is integrated into the Si interposer along with four HBM memory stacks by micro-bumps and TSVs (adapted from Ref. [6])

the 3D packaging techniques from paper to reality and indicate the extensive applications of 3D packaging technology to microelectronics.

3D packaging technology involves multiple disciplines, for example, materials science, mechanical engineering, physics, chemistry, and electrical engineering. A technical book, which could provide a comprehensive scope of 3D microelectronic packaging technology is desirable for graduate students and professionals in both academic and industry area. Current available books on 3D integration typically focus on processing of wafers, especially TSV fabrication, and do not cover other key elements in 3D packaging. This book is proposed to fill in the gap. It presents a thorough extent of 3D packaging, covering the fundamentals of interconnects, bonding process, advanced packaging materials, thermal management, thermal mechanical modeling, architecture design, quality and reliability, and failure analysis of 3D packages, which are critical for the success of advanced 3D packaging.

This chapter provides detailed illustration of motivations as well as various architectures of 3D packaging. Challenges in 3D packaging, including fabrication,

assembly, cost, design, modeling, thermal management, material, substrate, quality, reliability, and failure analysis, are reviewed with brief introduction to the chapters addressing these challenges.

#### 1.2 Why 3D Packaging

#### 1.2.1 Moore's Law

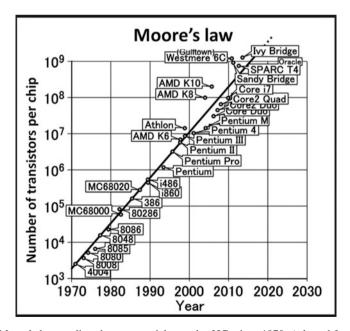

Since Intel introduced the world's first single-chip microprocessor, the Intel 4004, in 1971, an exponential growth of ICs has been observed following Moore's law in terms of transistor number per chip [7]. As illustrated in Fig. 1.3, the number of transistors per Si chip doubles approximately every 18 months, resulting in a straight line on a log scale [7, 8]. In 1990, the bipolar transistor technology switched to CMOS in order to reduce thermal power, circuit size, and manufacturing costs, at the same time increase the operating speed and energy efficiency [3]. In the early 2000s, multi-core processors were developed to address the challenging thermal power issue in conventional single-core processors [3]. Since multi-core processors require enormous cache capacity and memory bandwidth to achieve the designed performance, 3D packaging becomes one of the viable solutions to provide the required cache and bandwidth with a relatively low cost [3].

Fig. 1.3 Moore's law predicts the exponential growth of ICs since 1970s (adapted from Ref. [8])

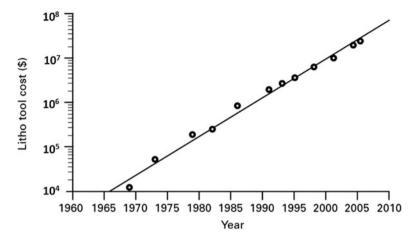

Fig. 1.4 The exponential growth of lithography equipment cost since 1970s (adapted from Ref. [8])

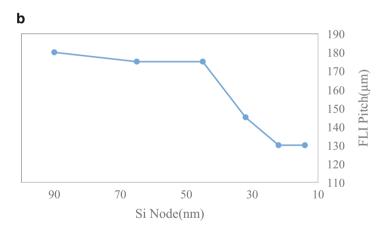

The conventional method to maintain Moore's law is to decrease the dimensions of components by lithography, which is becoming more and more sophisticated and expensive [8]. Figure 1.4 illustrates the exponential growth of lithography equipment cost since 1970s, which presents an economic challenge as the capital cost rises faster than semiconductor industry revenue [8]. 3D integration technology, which has been recognized as an enabling technology for future low cost ICs, provides the third dimension to extend Moore's law to ever higher density, more functionality, better performance with lower cost [3].

#### 1.2.2 Small Form Factor Requires 3D Packaging

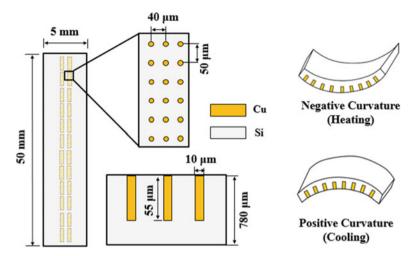

Market demands of small form factor microelectronics head to 3D packages, which are ultra-light, ultra-thin, and with small chip footprint. Si chips in 3D packages are typically  $50-100~\mu m$  thick, about 90~% thinner compared with those in conventional packages. Substrate core thickness of 3D packaging is about  $0-100~\mu m$ , more than 90~% thinner than that of traditional packaging. High density interconnects in 3D packaging are on the order of  $5-20~\mu m$  in diameter, more than 90~% smaller than those in 2D packaging. Thus, tremendous reduction in size and weight could be achieved by replacing conventional packaging with 3D technology [2].

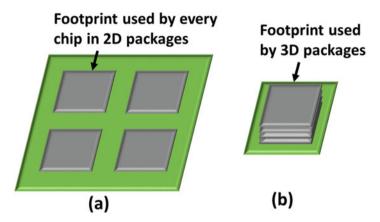

Small form factor requires small chip footprint, which is defined as the printed circuit board area occupied by the Si chip, as illustrated in Fig. 1.5 [2]. By stacking multiple dice on top of each other using 3D packaging techniques, the chip footprint could be reduced dramatically. Figure 1.5 schematically demonstrates the difference between conventional 2D packages and 3D packages

**Fig. 1.5** (a) Schematic illustration of the footprint difference between conventional 2D packages (a) and 3D packages (b) (adapted from Ref. [2])

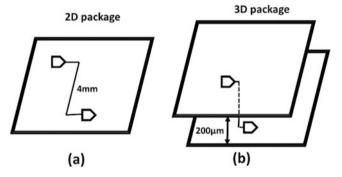

**Fig. 1.6** Schematic comparison between the wiring length in 2D packages (a) and 3D packages (b) (adapted from Ref. [2])

#### 1.2.3 Improved System Performance with Reduced Power

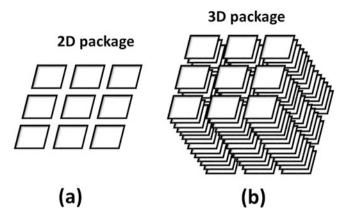

Interconnect length in 3D packages can be significantly reduced compared with conventional 2D packaging [2]. Figure 1.6a shows a typical interconnect length of 4 mm in a 2D package. The interconnect length could be reduced to 200 µm in a 3D package as demonstrated in Fig. 1.6b. Additionally, 3D packaging can also greatly improve the interconnect usability and accessibility [2]. Figure 1.7 shows a comparison between 2D and 3D packaging in terms of the accessibility and usability of interconnection. In contrast to eight neighbors to the center element in the case of 2D packaging technology, the utilization of a 3D packaging configuration provides access to 116 neighbors within an equal interconnect length to a center element in the stack.

The significant decrease in interconnect length as well as dramatic improvement in interconnect usability and accessibility result in much less delay in 3D devices, which is primarily limited by the time taken for the signal to travel along the

Fig. 1.7 Schematic comparison between 2D packages (a) and 3D packages (b) in terms of the interconnect accessibility and usability (adapted from Ref. [2])

interconnects [2]. Low latency and wide buses in 3D microelectronic systems lead to significant improvement to the system bandwidth [2]. Noise in well-designed 3D microelectronic systems, including reflection noise, crosstalk noise, simultaneous switching noise, and electromagnetic interference, can be reduced as a result of the reduction of interconnection length [2]. Additionally, as the parasitic capacitance in microelectronic packages is proportional to the interconnection length, the total power consumption in 3D packages is also reduced because of the reduced parasitic capacitance [2]. The power saving achieved by 3D technology enables 3D devices to perform at a faster rate or transition per second (frequency) with less power consumption. The overall system performance is greatly improved by applying 3D packaging technology [2].

#### 1.3 3D Microelectronic Packaging Architectures

The various 3D packaging architectures could be divided into the following three categories: die-to-die 3D integration, package-to-package 3D integration, and heterogeneous 3D integration combining both package and die stacking [3, 9, 10]. Chapter 2 discusses different 3D packaging architectures in detail along with assembly and test flows.

#### 1.3.1 Die-to-Die 3D Integration

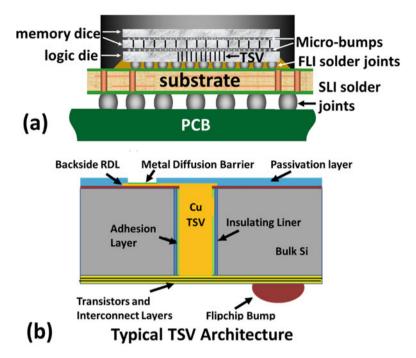

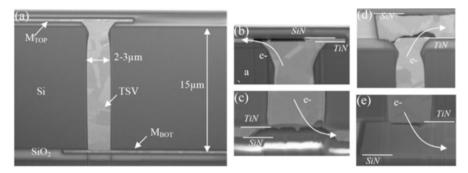

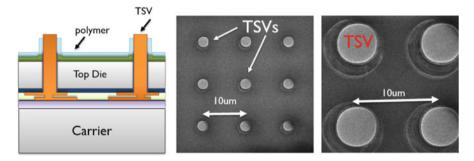

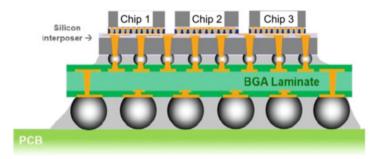

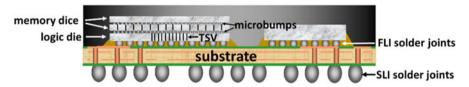

Die-to-die 3D integration is enabled by through silicon via (TSV) interconnections and thinned die-to-die bonding [3]. As illustrated in Fig. 1.8, two memory dice are stacked on top of a logic die with TSVs and micro-bumps. First Level Interconnect

Fig. 1.8 Schematic illustration of die-to-die 3D integration enabled by TSV and thinned die-to-die bonding (adapted from Ref. [10])

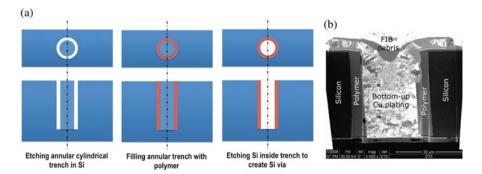

(FLI) solder joints connects the logic die with the substrate, while Second Level Interconnect (SLI) solder joints provides the connection between this 3D package to the Printed Circuit Board (PCB) [10]. The TSVs are formed by laser drilling or deep reactive ion etching, followed by liner deposition and copper fill. There are three typical manufacturing processes for TSVs, Via First, Via Middle, and Via Last [11–13]. The detailed process flow of each process as well as the Pros and Cons of each process are discussed in Chaps. 2 and 3.

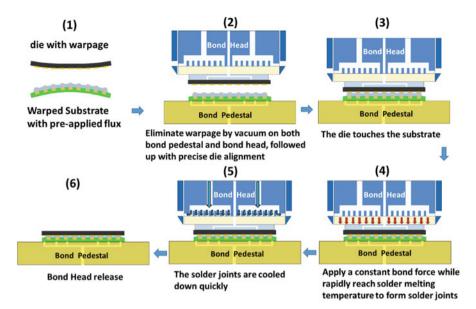

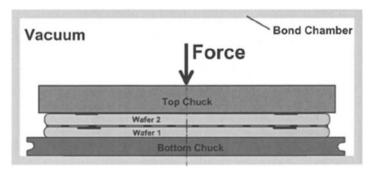

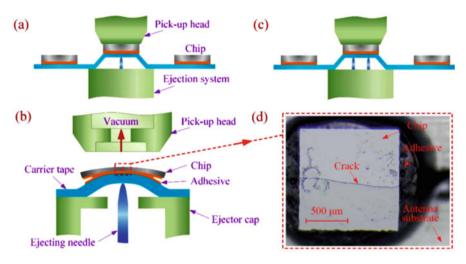

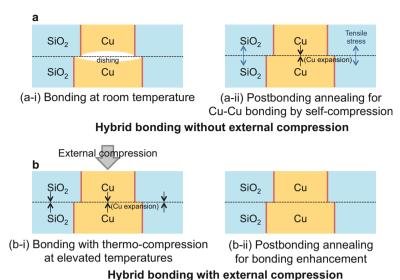

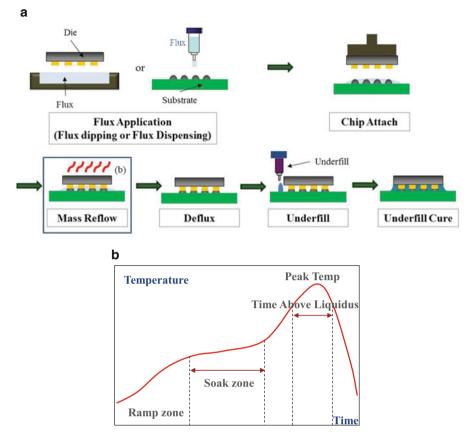

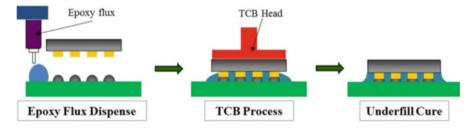

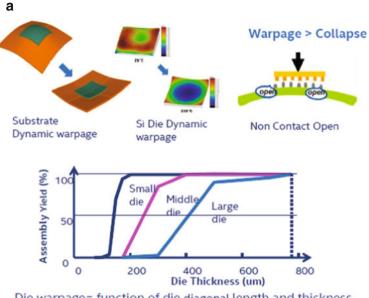

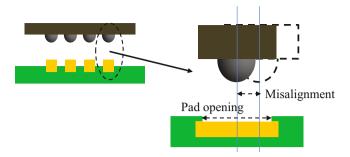

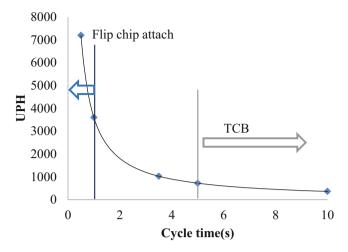

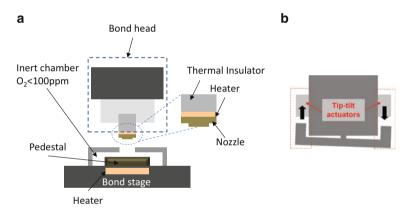

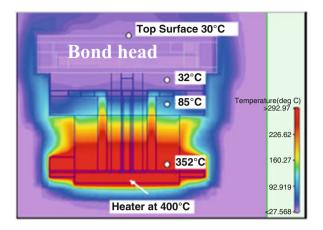

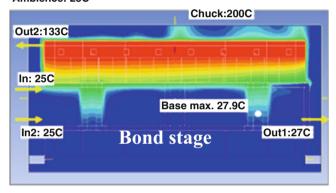

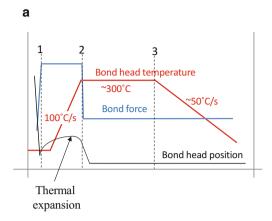

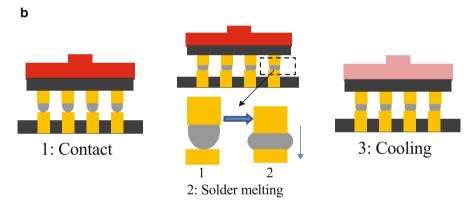

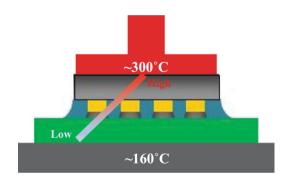

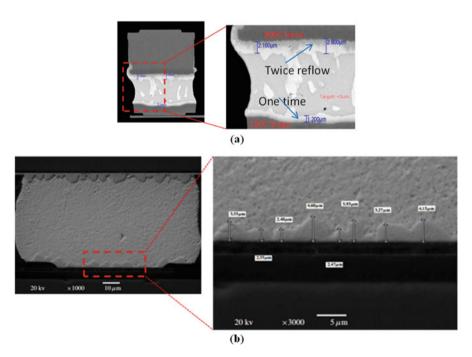

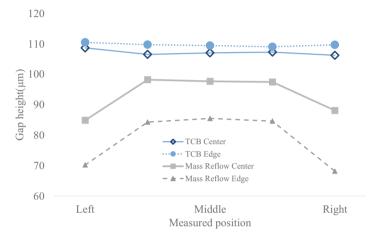

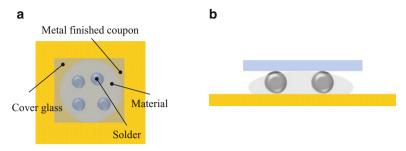

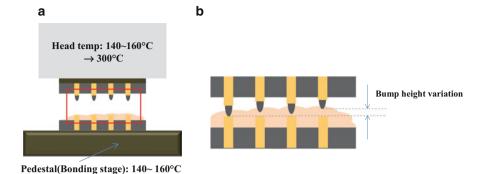

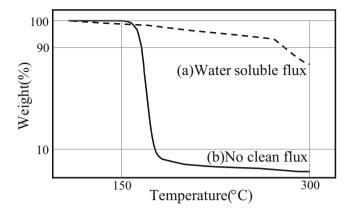

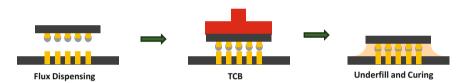

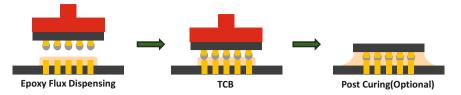

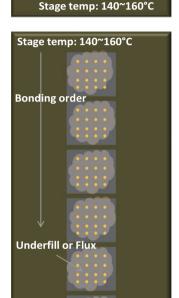

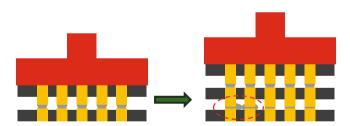

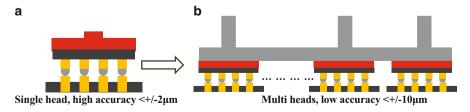

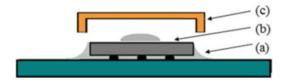

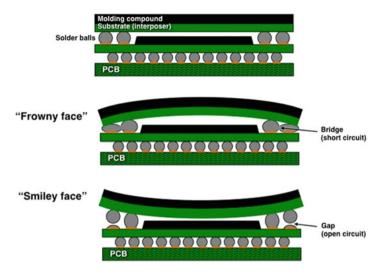

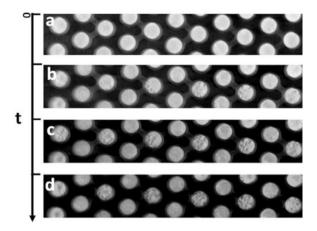

Die-to-die bonding is implemented by either Thermal Compression Bonding (TCB) process for solder micro-bumps or other alternative bonding process, for example, Cu-Cu bonding. Conventional solder mass reflow process in 2D packages, which includes flux dispensing, die attaching, and solder reflow in ovens, is not able to assemble advanced 3D packages having much thinner dice and organic packages, along with much smaller and denser interconnects. As the extent of warpage from both dice and substrates at the reflow temperature overcomes solder surface tension, leading to die misalignment, and results in die tilting, solder joint non-contact opens, and solder bump bridging [14]. TCB bonding process is developed to replace the conventional solder mass reflow process for solder-based micro-bump assembly in 3D packages. As illustrated schematically in Fig. 1.9, the substrate with pre-applied flux is kept flat on hot pedestal under vacuum to eliminate the substrate warpage. The die is picked up by the bond head, secured and kept flat with vacuum

Fig. 1.9 Schematic illustration of a typical thermal compression bonding process (adapted from Ref. [14])

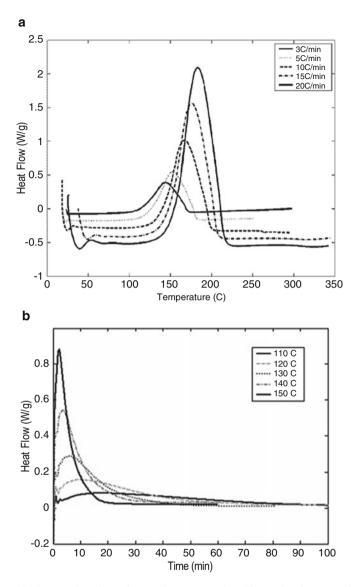

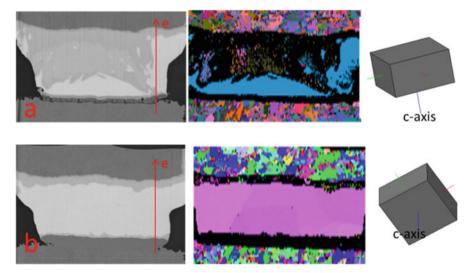

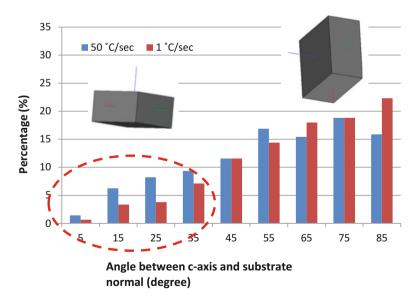

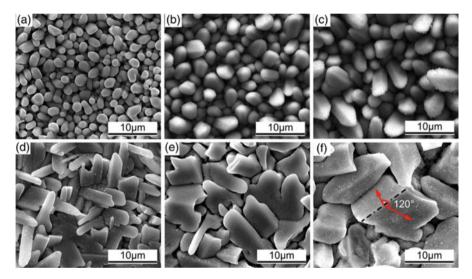

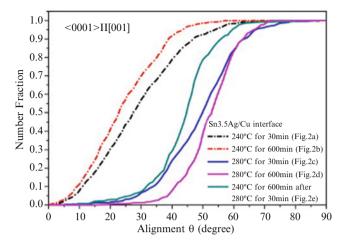

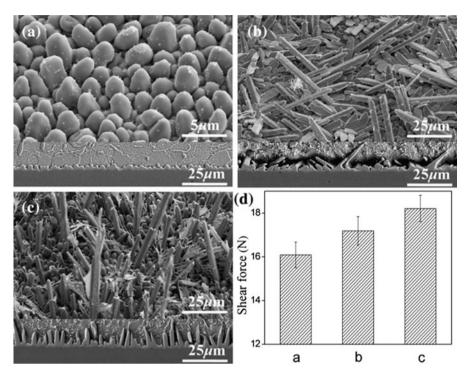

to remove any incoming die warpage. After the die is precisely aligned to the substrate, the bond head with die touches the substrate. A constant bond force is then applied on the die through the bond head, while the die is heated up rapidly beyond the solder melting temperature, with a ramping rate higher than 100 °C/s. As soon as the solder joints melt, the die is moved further down to ensure all the solder joints are at the same height. The die is held in this position long enough so that the solder joint forms between the die and the substrate. While the solder is still in the molten state, the bond head with die could retract upwards to control the solder joint height. Subsequently, the solder joints are cooled abruptly below the solidus temperature, with a cooling rate of more than 50 °C/s, followed up with die release from the bond head [14]. Unlike the traditional solder mass reflow process, with up to 10 min of process time for units in batches, the TCB bonding process assemble units one by one with about a couple of seconds per unit [14]. Additionally, thermal ramping rates during both the heating and cooling cycles are much higher than the conventional method. These higher rates result in solder grain size and orientation differences that can affect mechanical properties as detailed in Chap. 7.

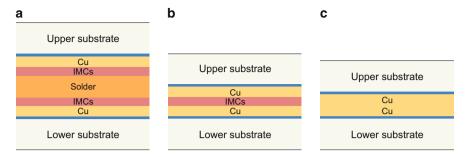

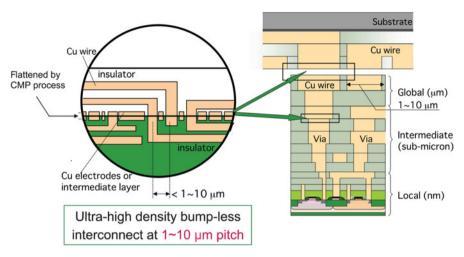

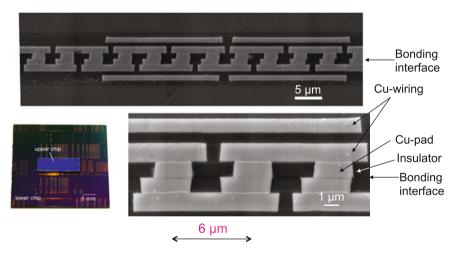

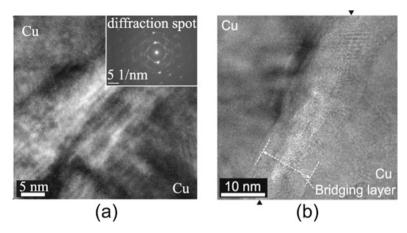

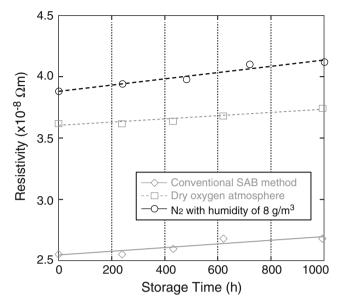

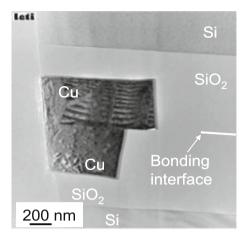

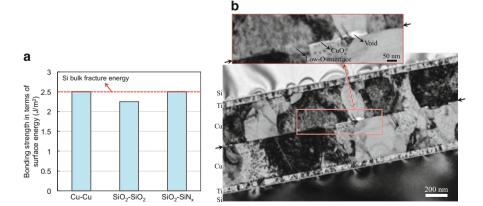

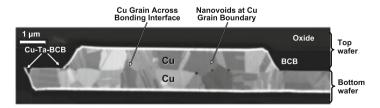

Solder-based micro-bumps are more compliant, thus could compensate bump height variations, lack of co-planarity, and misalignment issues during high volume manufacture. However, the TCB process peak temperature needs to be higher than the melting point of solder material, typically in the range of 250–300 °C, which brings more assembly and reliability challenges. Additionally, solder bridging risk gets much higher as bump pitch shrinks from more than 100  $\mu m$  to less than 40  $\mu m$ . Alternative bonding process, like direct Cu to Cu bonding, which could address interconnects with

Fig. 1.10 Schematic illustration of package-to-package 3D integration (adapted from Ref. [3])

less than 5 µm bump pitch, and assemble at relatively lower temperature is very promising. Various types of alternative bonding process is reviewed in Chap. 6 as well as Pros and Cons comparing with solder-based TCB process.

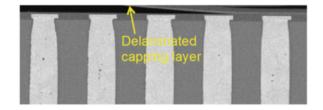

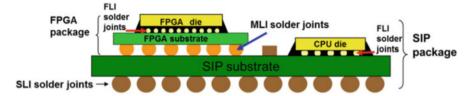

#### 1.3.2 Package-to-Package 3D Integration

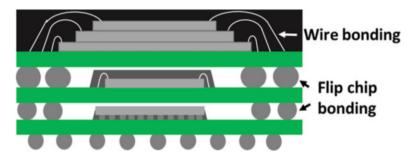

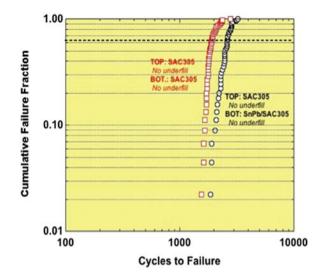

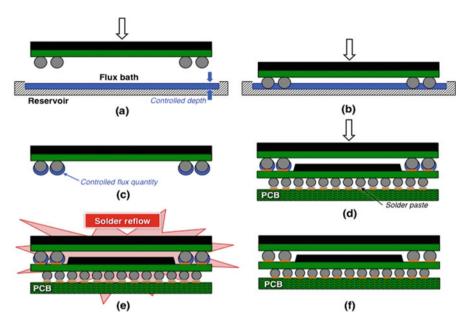

System in Package (SIP) and Package on Package (POP) are typical configurations of package-to-package 3D integration, which is enabled by stacking packages through wire bonding or flip-chip bonding [3]. Comparing to die-to-die stacking, package-to-package stacking technique has a shorter development cycle, thus help bring products to market faster with a low price. As displayed in Fig. 1.10, a wire bonding package is stacked on top of the other wire bonding package by flip-chip bonding. The two packages are then stacked on a flip-chip package to form a POP. The conventional solder mass reflow process could still be used in package-topackage stacking if the package warpages are within control, and the interconnect size and density is comparable with traditional 2D packages. However, market demands require packages to be ultra-thin, which limit the number of packages that could be stacked together. Additionally, solder joints and package materials in SIP and POP need to go through multiple cycles of reflow, bringing process and reliability challenges, like solder joint open, delamination between multiple layers in packages, and moisture control between each reflow process. Chapter 13 discusses in detail the processing and reliability of stacked packaging technique, as well as the Pros and Cons comparing with die stacking.

#### 1.3.3 Heterogeneous 3D Integration

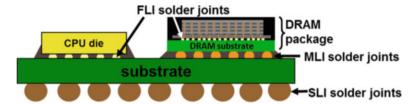

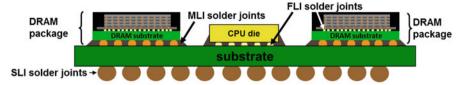

Depending on product needs, complex 3D packages can have the combination of both die stacking and package stacking [10]. As shown in Fig. 1.11, a 3D Dynamic Random Access Memory (DRAM) package formed by stacking four memory dice

Fig. 1.11 Schematic illustration of 3D packaging architectures having the combination of both die stacking and package stacking (adapted from Ref. [10])

Fig. 1.12 Schematic illustration of Silicon interposer technology providing connection between chips and stacked dice through TSVs (adapted from Ref. [10])

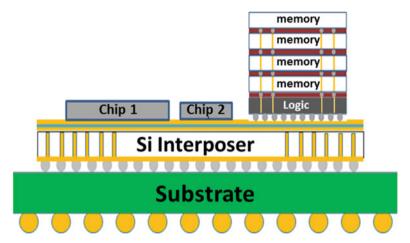

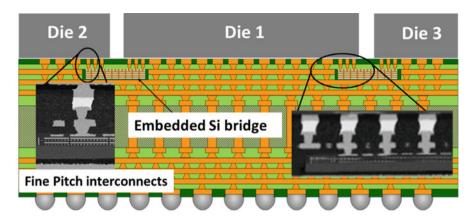

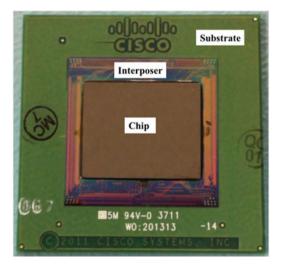

on top of the logic die through TSVs and micro-bumps is integrated along with a flip CPU chip by package stacking. FLIs between the CPU chip and the 3D package, MLIs between the DRAM package and the 3D package, as well as interconnects in the substrate provide connection between the CPU chip and the DRAM package [10]. Smaller and denser interconnects between chips and packages are highly desired for better performance, higher bandwidth, and lower power consumption. Figure 1.12 demonstrates the Silicon interposer technology, which could provide better connection between chips and stacked dice through TSVs [10, 15]. Embedded Multi-Die Interconnect Bridge (EMIB) technology is an alternative approach to provide localized high density interconnects between dice without TSVs [16]. As illustrated in Fig. 1.13, the link between dice is provided by fine Cu interconnects in Si bridges embedded in the organic substrate and confined denser FLIs between Si bridges and chips. Comparing with Si interposer technology, EMIB technology is able to provide similar performance with a much lower cost, thus opens up new opportunities for heterogeneous 3D packaging [16].

**Fig. 1.13** Schematic illustration of Embedded Multi-Die Interconnect Bridge (EMIB) technology providing localized high density interconnects between chips without TSVs (adapted from Ref. [16])

#### 1.4 3D Microelectronic Packaging Challenges

#### 1.4.1 Assembly Process, Yield, Test, and Cost Challenges

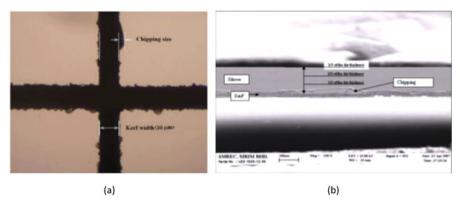

3D packaging involves more challenging assembly steps than conventional packaging, such as TSV wafer fabrication and die singulation process (reviewed in Chap. 5), TCB of micro-bumps (discussed in Chap. 7), and multiple solder reflow process for POP (refer to Chap. 13). The complicated process results in yield, test, and cost challenges [2], which could be addressed by redundancy or fault-tolerant designs, throughput time (TPT) improvement of assembly process, and minimize process steps based on product quality and reliability requirement [2], [3].

## 1.4.2 Thermal Management, Package Design, and Modeling Challenges

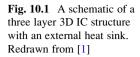

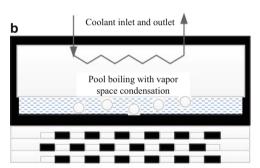

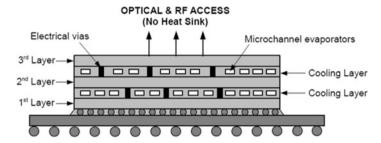

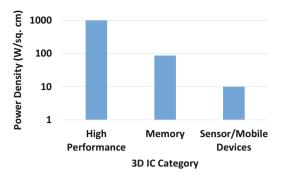

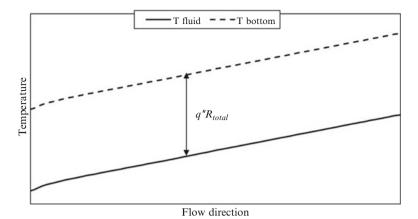

The 3D integration of heat generation components in close vicinity increases the heat flux density as well as complexity of coolant routing, thus leads to big challenges to the thermal management of 3D packaging [2, 3]. Chapter 10 presents the fundamentals of heat transfer along with advanced guidelines helpful to address the issue.

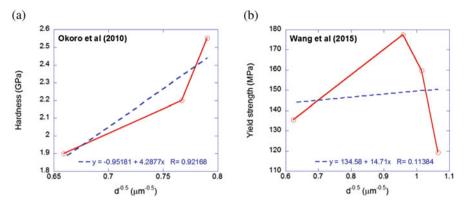

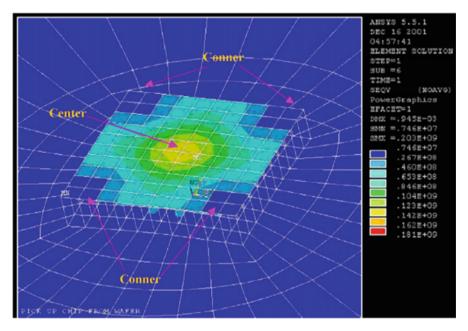

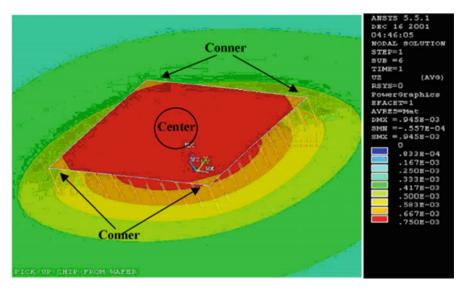

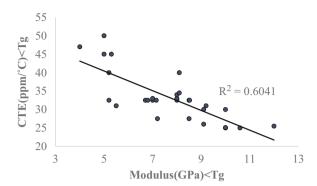

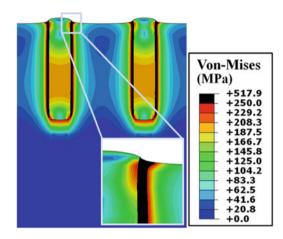

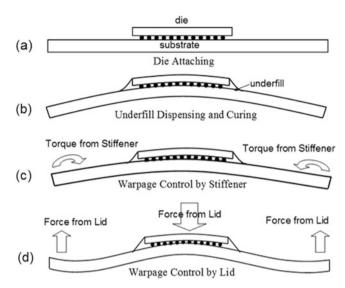

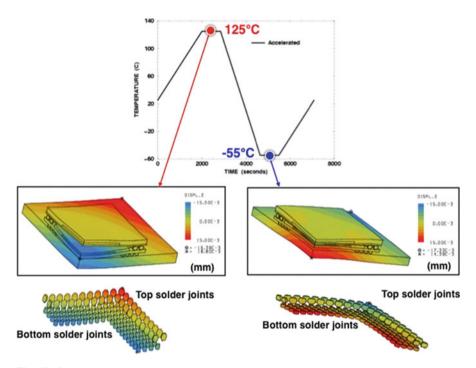

Due to the increased system complexity, designing 3D packages could be very challenging, but could be addressed by designing and developing design software [2]. In addition to increased system complexity, 3D packaging involves multilevels of solder joints, underfill, and molding compounds. Thermal stress due to the

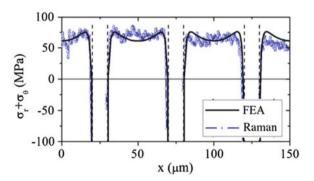

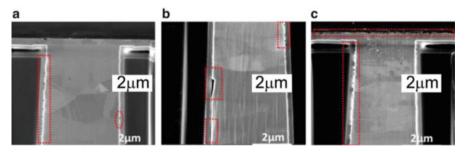

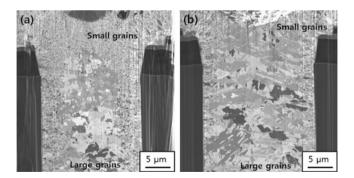

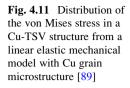

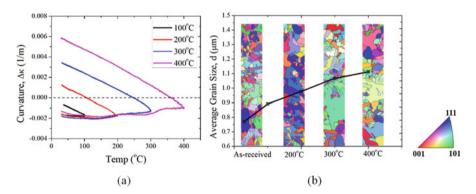

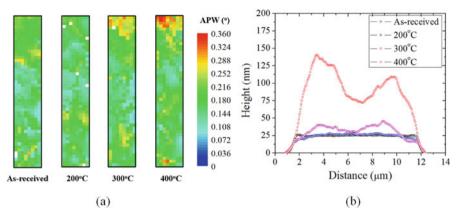

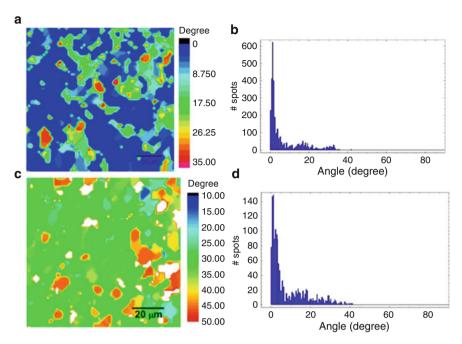

mismatch in coefficients of thermal expansion (CTE) and hygroscopic stress caused by excessive moisture absorption are often combined together, which complicates the stress modeling in 3D packaging [17, 18]. For interconnects with a couple of micrometer in diameter, like TSVs, it is found that microstructure, anisotropy of material properties, recrystallization, and time-dependent phase morphological evolution need to be considered during stress modeling [19]. Chapters 4 and 10 provide through discussions on the modeling of thermal mechanical and moisture stresses in 3D packaging.

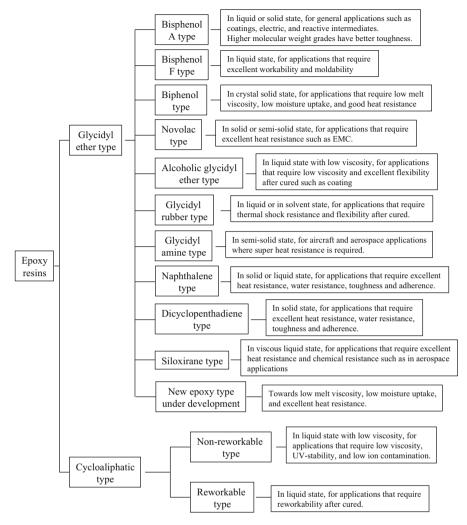

#### 1.4.3 Material and Substrate Challenges

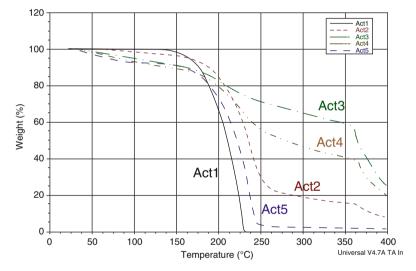

3D packages typically have smaller interconnect size, tighter bump pitch, and reduced chip gap, which brings challenges to underfill, chip attachment, and deflux process. Additionally, the TCB process widely used in the chip attachment of 3D packages is very different from the conventional mass reflow process, as the whole bonding cycle completes in a few seconds rather than over 10 min [14]. Major modification of traditional underfill and flux material is essential to prevent underfill process, flux residue, and interconnect integrity-induced yield loss, such as underfill voids, delamination because of flux residue, solder bump bridging, or non-wets. Chapter 7 reviews the material challenges and provides guidelines for epoxy and flux material selection.

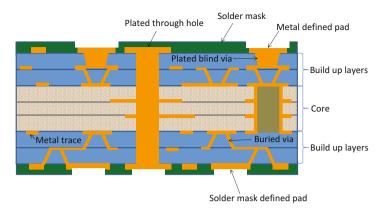

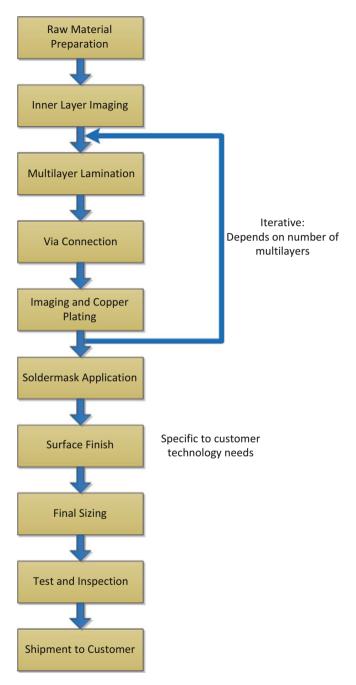

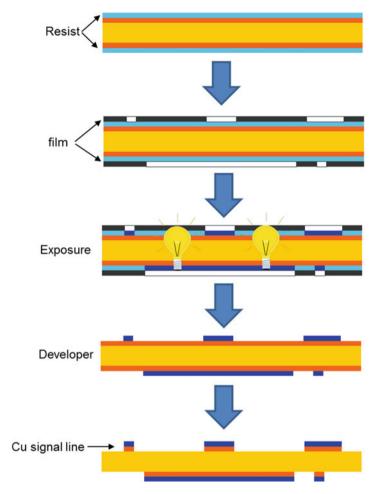

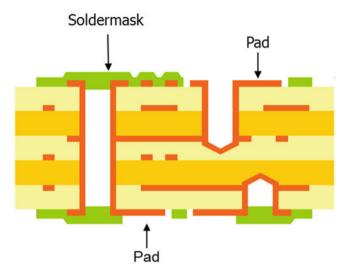

To enable the highly integrated 3D packaging, both substrate and PCB need to fulfill the much higher signal and power density requirements. Smaller substrate vias, through holes (TH), and traces, along with much tighter pitches are desired. Furthermore embedded components, including both Si chip and packages, integrating into substrates or PCB is one of the approaches to achieve the product miniaturization with higher performance and lower power consumption goal. These results in significant challenges in substrate warpage control and flawless fabrication process to enable much finer interconnect size and pitch. Chapter 11 reviews the substrate material and fabrication technology evolution, along with general recommendations in selecting and applying appropriate material and process technologies for 3D packaging.

#### 1.4.4 Quality, Reliability, and Failure Analysis Challenges

Complex 3D packages have multiscale interconnects ranging from a few to 1000 micrometers. For instance, TSVs and micro-bumps are about a couple of micron in diameters, while the SLI connecting packages to the PCB could be up to 1000  $\mu m$  in diameter. During 3D integration, interconnects need to go through multiple solder reflow process, defects generated during fabrication and assembly, CTE mismatch between different materials, and microstructure evolution in

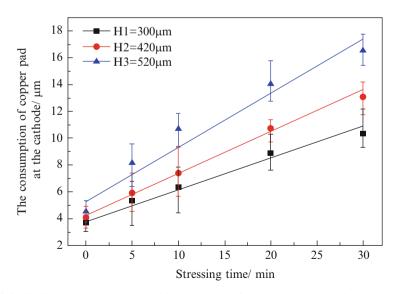

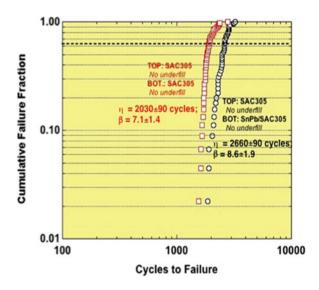

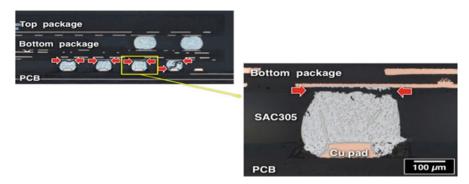

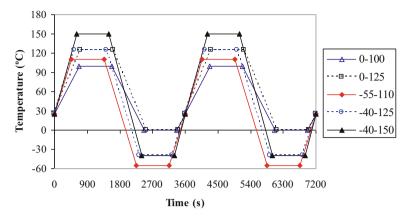

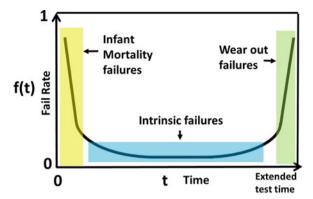

interconnects could lead to new quality and reliability issues. Additionally, the extended application of 3D packaging in products requiring much higher reliability, for instance, Advanced Driver Assistance Systems (ADAS), avionics, and high-end servers brings extra challenges to the quality and reliability of 3D packages. Chapters 3 and 4 review the quality and reliability of TSVs. Chapter 9 reviews the electro migration concerns in interconnects of 3D packages. Focusing on the reliability of multilevel solder joints in stacked packages, Chap. 13 explains the different reliability requirements between consumer electronics and high-reliability electronics. It also provides detailed discussions of use conditions, the roles of encapsulants and underfills, reliability tests and modeling to address complex reliability concerns in 3D packages. Chapter 14 provides an overview of quality and reliability of 3D packaging and demonstrates with case studies, along with field performance prediction.

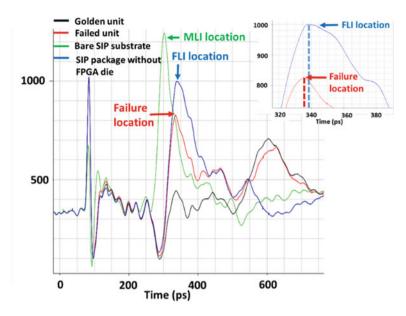

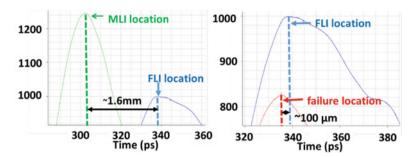

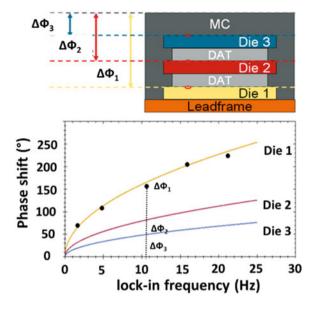

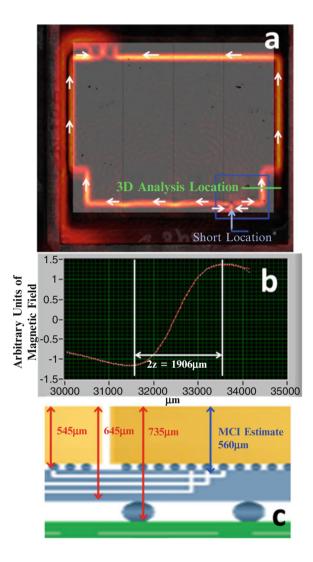

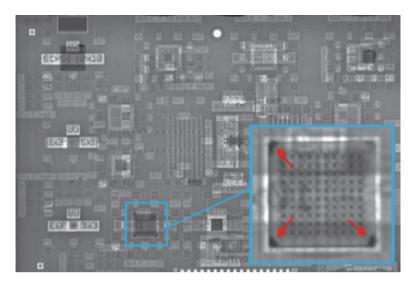

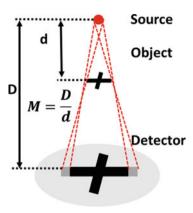

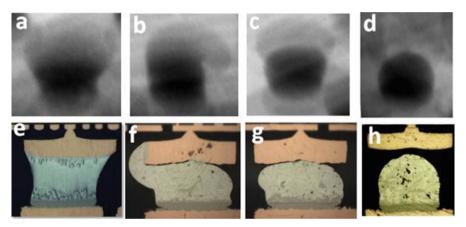

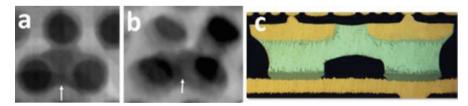

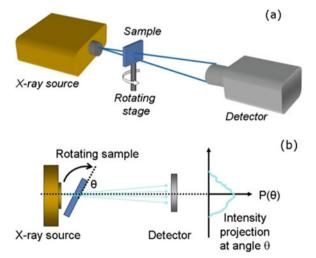

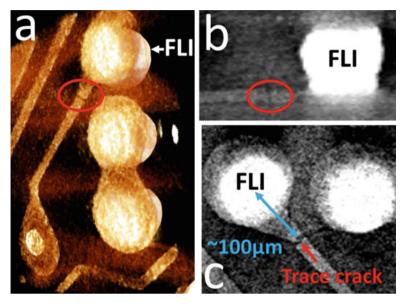

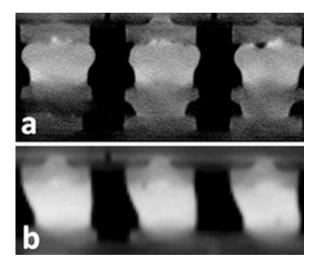

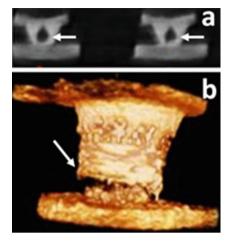

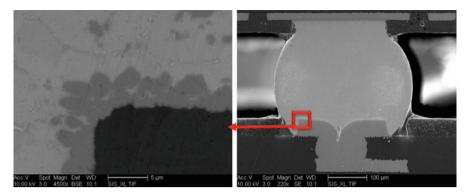

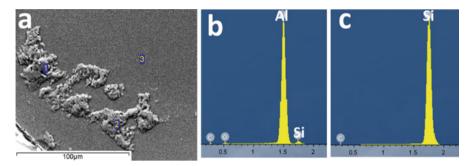

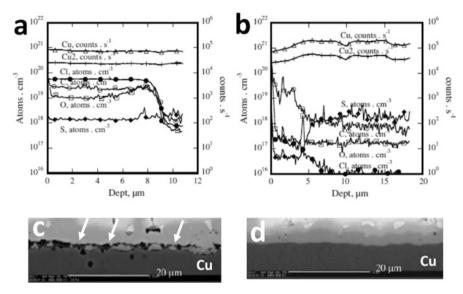

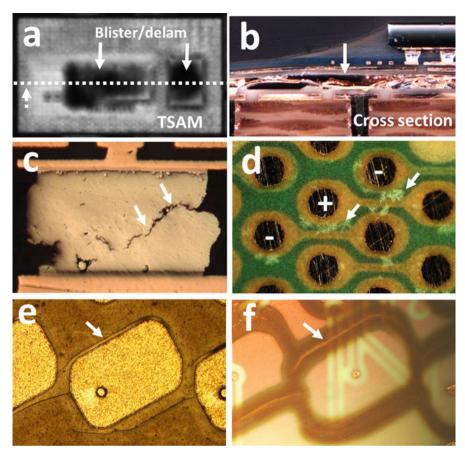

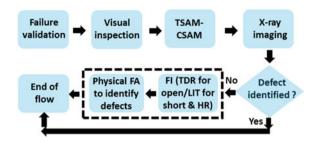

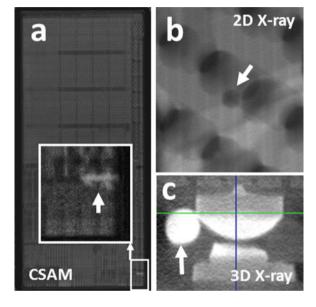

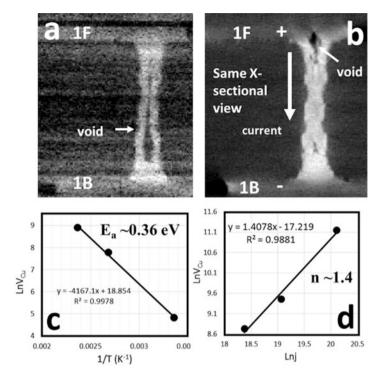

Failure analysis is critical for the technology development of 3D packaging, as in-depth root cause analysis of failures provides solution paths for resolving quality and reliability issues. Due to the complexity of 3D packages, Fault Isolation (FI) and Failure analysis (FA) become very challenging. First of all, multiple failures could exist in one unit post-reliability tests, flawless failure analysis on each failure requires nondestructive high-resolution techniques, including fault isolation, imaging, and material analysis. Additionally, each electrical failure in a 3D package could come from various dice, assembly layers or interconnects, highresolution fault isolation techniques, which could provide 3D information of defects are highly desired. After the identification of defects, physical failure analysis needs to be performed for the root cause study. However interconnects in 3D packages, like TSVs, have small diameters (2–10 μm) and long lengths (40–200 μm), artifact free cross-sectional techniques with short throughput time is critical for characterizing small defects in a relatively large cross-sectional plane. Chapter 15 reviews advanced high-resolution nondestructive FI and FA techniques, such as Electro Optic Terahertz Pulse Reflectometry (EOTPR), 3D X-ray Computed Tomography (CT), Lock-in Thermography (LIT), and acoustic microscopy. The applications of novel physical sample preparation techniques and various material analysis methods in 3D packaging failure analysis are also discussed. It also provides guidelines for building up efficient 3D packaging FI-FA flow and performing in-depth root cause studies, along with case study demonstration.

#### 1.4.5 Summary

3D packaging has provided a new dimension for semiconductor industry to maintain Moore's law with much lower cost and has been adopted as an effective approach to provide portable microelectronics with better performance, smaller power consumption, and less cost. There has been numerous novel technological innovations invented for the development of advanced 3D packaging in the recent years. However, due to the much smaller and denser interconnects, complicated

assembly process, unique TSV and micro-bump TCB process, and the extended application in high-reliability products, there are tremendous challenges in highly integrated 3D packaging.

Chapters in this book are written by experts from both academia and semiconductor industry. Chapter 2 provides an insightful overview of 3D packaging architecture and assembly process design. Chapters 3, 4, and 5 focus on the fundamentals of TSV processing, reliability, and mechanical properties. Chapters 6 and 7 discuss the fundamentals of thermal compression bonding of micro-bumps, process materials, direct Cu to Cu bonding, and other alternative interconnects in 3D packaging. Chapters 8 and 9 provide fundamentals of solder alloys and electro migration in interconnects of 3D packages. Chapter 10 presents a thorough review of thermal management in 3D packaging. Chapter 11 displays in great details the fundamentals of substrate materials and manufacture process. Chapter 12 covers the thermal mechanical and moisture modeling in 3D packaging. Chapters 13, 14, and 15 illustrate a comprehensive overview of quality, reliability, fault isolation, and failure analysis of advanced 3D packages. Readers could obtain all-around knowledge about 3D packaging, including the fundamentals, developing areas, technique gaps, and guidelines for future research and development.

**Acknowledgement** The editors would like to thank John Elmer from Lawrence Livermore National Laboratory for his critical review of this chapter.

#### References

- 1. I. Szendiuch, Radioengineering. **20**(1), 214 (2011)

- S.F. Al-sarawi, D. Abbott, P.D. Franzon, IEEE Trans. Comp. Packag. Manufact. Technol. 21 (1), 2 (1998)

- 3. J.Q. Lu, Proc. IEEE 97(1), 18 (2009)

- 4. J.H. Lau, Chip Scale Rev. **18**(1), 32 (2014)

- L. Li, P. Chia, P. Ton, M. Nagar, S. Patil, J. Xue, J. DeLaCruz, M. Voicu, J. Hellings, B. Isaacson, M. Coor, R. Havens, in *Conference Proceedings from the 66th Electronic Components and Technology Conference*. (ECTC), Las Vegas, 31 May–3 June 2016, p. 1445

- C. Lee, C. Hung, C. Cheung, P. Yang, C. Kao, D. Chen, M. Shih, C. C. Chien, Y. Hsiao, L. Chen, M. Su, M. Alfano, J. Siegel, J. Din, B. Black, in *Conference Proceedings from the* 66th Electronic Components and Technology Conference. (ECTC), Las Vegas, 31 May–3 June 2016, p. 1439

- R.R. Tummala, Fundamentals of Microsystems Packaging (McGraw-Hill, New York, 2001), pp. 4–41

- 8. D.C. Brock, *Understanding Moore's Law: Four Decades of Innovation* (Chemical Heritage Foundation, Philadelphia, 2006), pp. 67–84

- 9. Y. Li, P.K. Muthur Srinath, D. Goyal, J. Electron. Mater. 45(1), 116 (2016)

- 10. Zhiyong Ma and David G. Seiler, "Metrology and Diagnostic Techniques for Nanoelectronics", Pan Stanford Publishing, (2016), pp. 1089-1119. (To be published).

- T.M. Bauer, S.L. Shinde, J.E. Massad, D.L. Hetherington, in Conference Proceedings from the 59th Electronic Components and Technology Conference. (ECTC), San Diego, 26–29 May 2009, p. 1165

- 12. G. Pares, N. Bresson, S. Minoret, V. Lapras, P. Brianceau, J.F. Lugand, R. Anciant, N. Sillon, in *Conference Proceedings from the 11th Electronics Packaging Technology Conference (EPTC)*, Singapore, 9–11 Dec. 2009, p. 772

- 13. K-W Lee, H. Hashimoto, M. Onishi, Y. Sato, M. Murugesan, J.-C. Bea, T. Fukushima, T. Tananka, M. Koyanagi, in *Conference Proceedings from the 64th Electronic Components and Technology Conference (ECTC)*, Orlando, 27–30 May 2014, p. 304

- 14. A. Eitan, K. Hung, in Conference Proceedings from the 65th Electronic Components and Technology Conference (ECTC), San Diego, 26–29 May 2015, p. 460

- K. Zoschke, M. Wegner, M. Wilke, N. Jürgensen, C. Lopper, I. Kuna, V. Glaw, J. Röder1,

O. Wünsch1, M.J. Wolf, O. Ehrmann, H. Reichl, in Conference Proceedings from the 60th Electronic Components and Technology Conference (ECTC), Las Vegas, 1–4 June 2010,

p. 1385

- R. Mahajan, R. Sankman, N. Patel, D. Kim, K. Aygun, Z. Qian, Y. Mekonnen, I. Salama,

S. Sharan, D. Iyengar, D. Mallik, in Conference Proceedings from the 66th Electronic Components and Technology Conference (ECTC), Las Vegas, 31 May–3 June 2016, p. 558

- C.-H. Liu, J.-L. Tsai, C. Hung-Hsien, C.-L. Lu, S.-C. Chen, in Conference Proceedings from the 64th Electronic Components and Technology Conference (ECTC), Orlando, 27–30 May 2014, p. 1628

- 18. C.-H. Liu, Y.-H. Liao, W.-T. Chen, C.-L. Lu, S.-C. Chen, in *Conference Proceedings from the 65th Electronic Components and Technology Conference (ECTC)*, San Diego, 26–29 May 2015, p. 1502

- N. Nabiollahi, N. Moelans, M. Gonzalez, J.D. Messemaeker, C.J. Wilson, K. Croes, E. Beyne, I.D. Wolf, Microelectron. Reliab. 55(5), 765–770 (2015)

# Chapter 2 3D Packaging Architectures and Assembly Process Design

#### Ravi Mahajan and Bob Sankman

#### Acronyms

| 2D   | Two dimensional   |

|------|-------------------|

| 3D   | Three dimensional |

| BEOL | Back end of line  |

BI Burn-In

CMP Chemical mechanical polishing

D2D Die-to-die D2W Die-to-wafer

ECD Electro-chemical deposition

ECG Deleted in chapter

EMIB Embedded multi-die interconnect bridge

**FEOL** Front end of line ΙP Intellectual property KGD Known good die KOZ Keep out zone MCM Multi chip module MCP Multi chip package Middle end of line MEOL **MPM** Multi package module

PECVD Plasma enhanced chemical vapor deposition

PVD Plasma vapor deposition

Rx Receiver SBS Side by side

High Density Interconnect Pathfinding, Assembly Technology, Intel Corporation, MS CH5-157, 5000 West Chandler Blvd., Chandler, AZ 85226, USA e-mail: ravi.v.mahajan@intel.com; bob.sankman@intel.com

R. Mahajan (🖂) • B. Sankman

SIP System in package SOC System on chip

TDP Thermal design power

TIM Thermal interface material

TSV Through silicon via

Tx Transmitter W2W Wafer-to-wafer

#### 2.1 Introduction

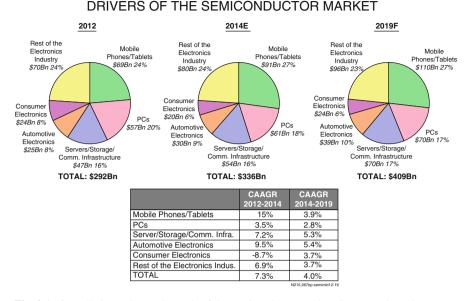

Increasing transistor density enabled by Moore's Law [1, 2] has led to increasingly powerful and pervasive computer systems that enable multiple personal and business applications (see Fig. 2.1 for an estimate of the overall size and growth trends of the semiconductor market). The trend in increased compute capabilities has been fueled by increased wired and wireless connectivity [3] which has led to powerful interconnected computer networks. These computers and associated networks utilize a myriad of computing and communication functions that are implemented within digital circuits (e.g., Microprocessors, Field Programmable Gate Arrays), memory circuits (e.g., SRAM, DRAM), and analog circuits (e.g., power supplies, clocks, RF front end modules, amplifiers, SERDES, USB, PCIe, DDR). Different computing and communication functions can be integrated on a monolithic silicon chip (typically referred to as System On Chip or SOC integration) or on a package (typically referred to as System In Package or SIP integration 1). Integration on chip has the advantages of improved signal transmission fidelity due to reduced interconnect lengths, lower system power due to efficient on-chip connections between IP blocks, and overall reduced silicon resulting from Moore's Law scaling. Thus, on-chip integration is usually preferred when:

(a) The integrated functions can easily be implemented on the same silicon fabrication process. For example, digital logic and SRAM can be built using compatible silicon processes. Conversely, high performance digital logic and DRAM are rarely fabricated on similar silicon manufacturing processes, and hence are not commonly included in the same chip.

<sup>&</sup>lt;sup>1</sup> As a general definition, SIP refers to the on-package integration of multiple heterogeneous and/or homogenous ICs each of which may be in the form of unpackaged die, individually packaged die, or packaged modules. iNEMI (International Electronics Manufacturing Initiative) defines SIP as: System in Package is characterized by any combination of more than one active electronic component of different functionality plus optionally passives and other devices like MEMS or optical components assembled preferred into a single standard package that provides multiple functions associated with a system or subsystem. SIP is considered to be subset of the broader concept of System On Package (SOP) [4] where an entire computer system is built on a package.

## Fig. 2.1 Overall size and growth trends of the semiconductor market (Source: Prismark Partners LLC)

(b) The IP<sup>2</sup> blocks desired for the SOC are available in the same silicon fabrication process and the resulting chip meets the cost target required to make the product economically viable.

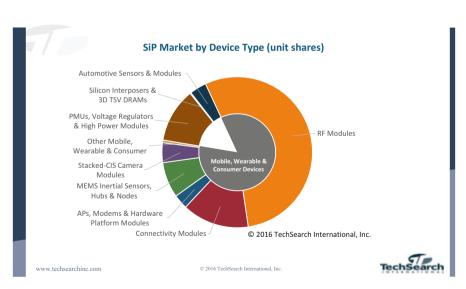

SIP is preferred for the integration of heterogeneous functions [5] (i.e., functions manufactured using disparate semiconductor technologies) and to help bring products to market quicker when technical and/or business reasons prevent timely SOC integration. As seen in Table 2.1 and Fig. 2.2, there continues to be significant interest in SIP configurations. SIP architectures can be broadly classed in three categories:

- (a) Planar configurations where two or more die or packages are placed side by side and connected to each other through lateral interconnects in a multilayer substrate.

- (b) Stacked configurations where two or more die, or packages, are stacked one on top of the others and connected through a combination of both lateral and vertical interconnects. The value of implementing stacking in a product

<sup>&</sup>lt;sup>2</sup> An IP (Intellectual Property) block is reusable circuit block that performs a certain specialized functions and serves as a building block for constructing the SOC.

Total

| SiP/MCP forecast                                |      |        |                                                                                                     |  |  |  |

|-------------------------------------------------|------|--------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Product/package type volume (Bn units)          | 2014 | 2019 F | Leading suppliers/players                                                                           |  |  |  |

| Stacked die in package and memory card          | 8.3  | 10.5   | Samsung, Micron, SKHynix, Toshiba, SanDisk<br>PTI, ASE, SPIL, Amkor, STATS ChipPAC                  |  |  |  |

| Stacked package on package: bottom package only | 0.95 | 1.2    | Samsung, Apple, Qualcomm, MediaTek<br>Amkor, STATS ChipPAC, ASE, SPIL                               |  |  |  |

| PA centric RF module                            | 4.5  | 5.9    | Qorvo, Skyworks, Anadigics, Avago, Amkor, ASE, Inari, HEG, JCET. Unisem, ShunSin                    |  |  |  |

| Connectivity module (bluetooth/WLAN)            | 0.6  | 0.9    | Murata, Taiyo Yuden, Samsung, ACSIP, ALPS, USI                                                      |  |  |  |

| Graphics/CPU or ASIC MCP                        | 0.2  | 0.2    | Intel, AMD, Nvidia, Xilinx, Altera                                                                  |  |  |  |

| Leadframe module (power SiP)                    | 3.2  | 4.7    | NXP, STMicro, TI, Freescale, Toshiba,<br>Infineon/IR, Renesas, ON Semi                              |  |  |  |

| MEMS and controller                             | 5 4  | 8.2    | ST, Analog, Bosch, Freescale, Knowles,<br>InvenSense, Denso                                         |  |  |  |

| Camera module                                   | 3.7  | 5.3    | LG Innotek, SEMCO, Hon Hai, Lite-on,<br>Toshiba, Sunny Optical, Sharp, Cowell                       |  |  |  |

| Fingerprint sensor                              | 0.35 | 1.5    | Apple, Synaptics, Fingerprint Cards, Cypress/<br>IDEX, Silead, Goodix, NEXT Biometrics,<br>Qualcomm |  |  |  |

Table 2.1

Volume forecast of different SIP configurations (Source: Prismark Partners LLC)

Fig. 2.2 2015 SIP Market by device type (Source: TechSearch International)

27.2

38.4

design, and thus leveraging the vertical dimension in a package, has been discussed in detail in [6].

(c) Hybrid configurations that combine both the planar and stacked configurations.

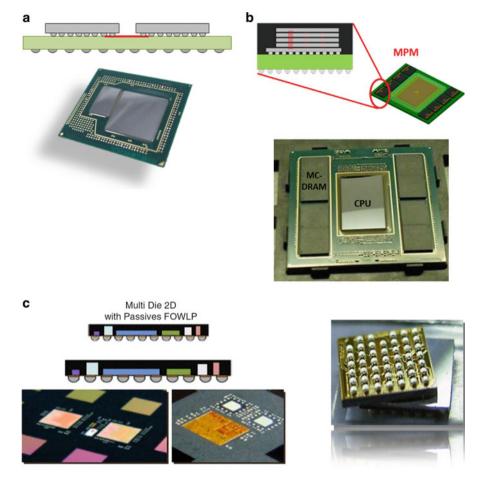

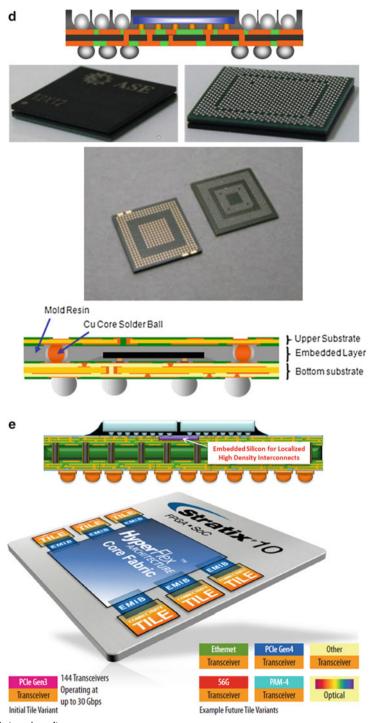

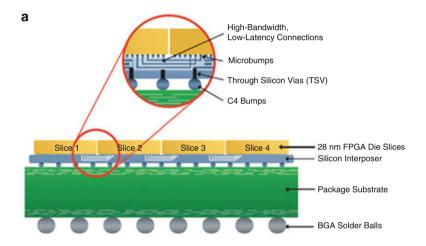

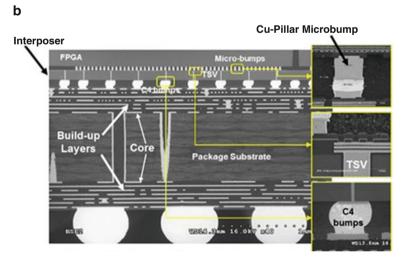

There are a number of innovative ways to construct SIP architectures using planar and stacked structures. Some of the more well-known SIP architectures are shown in Fig. 2.3. Figure 2.3 illustrates how different architectures have evolved to meet specific needs for different markets. Figure 2.3 is not intended to be a complete list of all the possible architectures. It is clear from the configurations shown in Fig. 2.3a–f that a number of SIP combinations are possible, offering feature, size, configuration, and cost flexibility.

One class of SIP configurations that has driven the most significant technology changes is through silicon vias (TSV)-based SIP. This chapter focuses on 3D stacks that are enabled by TSV technology. TSV-based SIPs have been the subject of considerable research for more than two decades and numerous papers have explored applications, architecture and design opportunities, as well as process, material, and equipment complexities [11–14]. Since it is difficult to comprehensively discuss all these aspects in a general overview, this chapter will attempt to provide a broad perspective of the architectural and process opportunities and complexities. The process of TSV formation has been previously discussed in depth in Chap. 3 and will not be repeated here, except for a brief reference in Sect. 2.3.

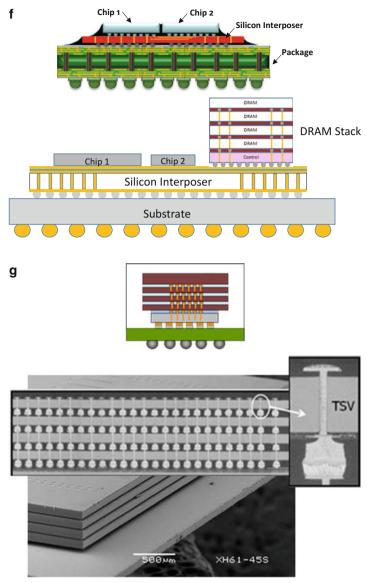

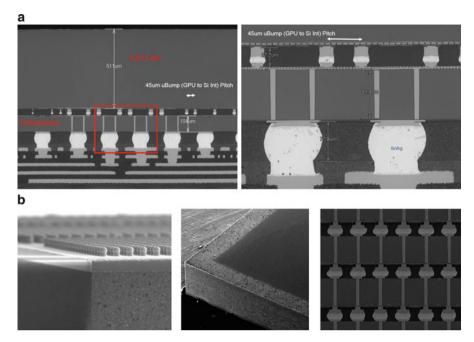

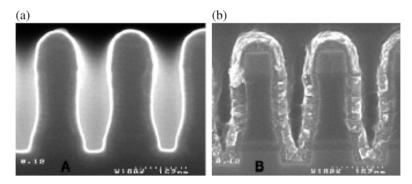

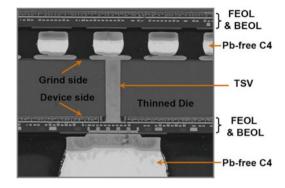

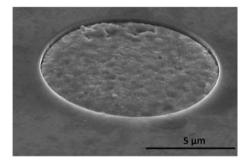

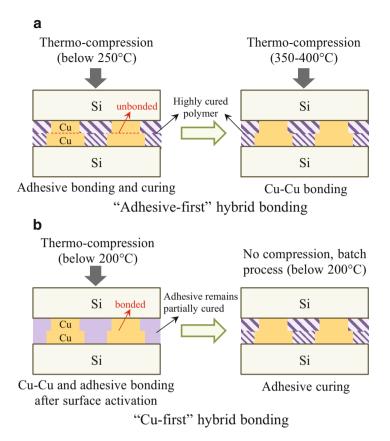

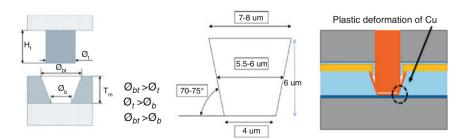

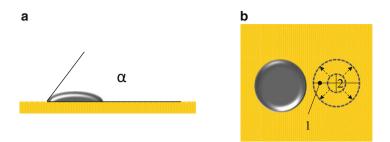

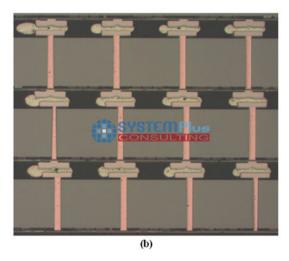

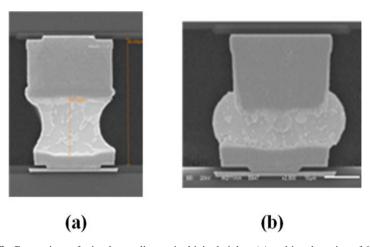

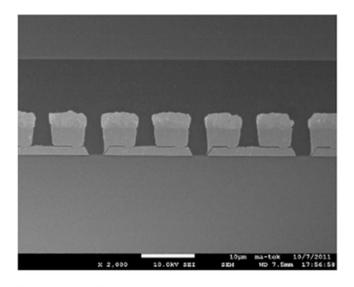

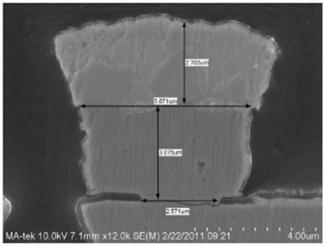

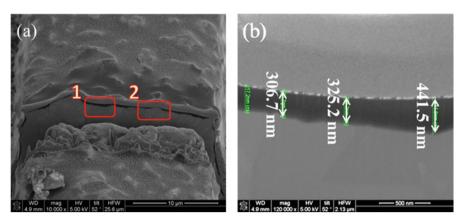

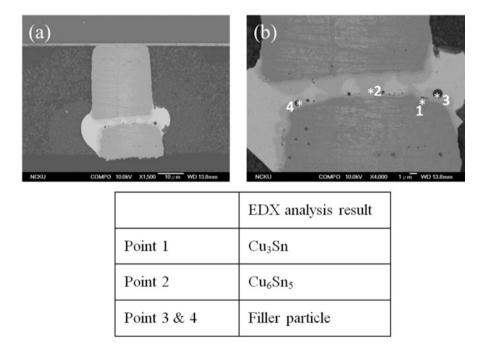

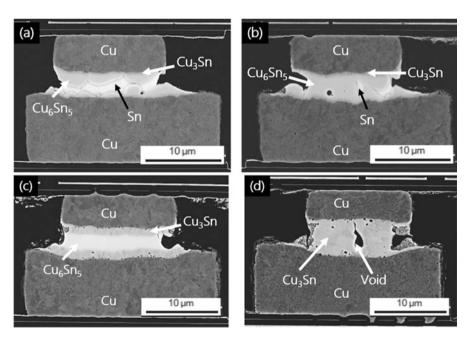

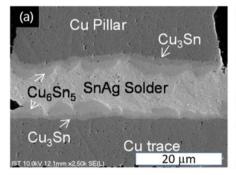

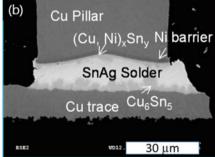

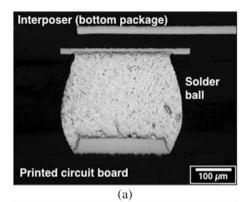

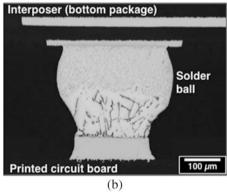

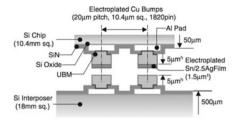

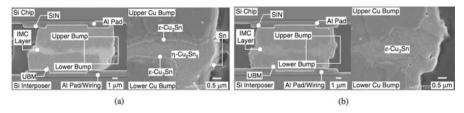

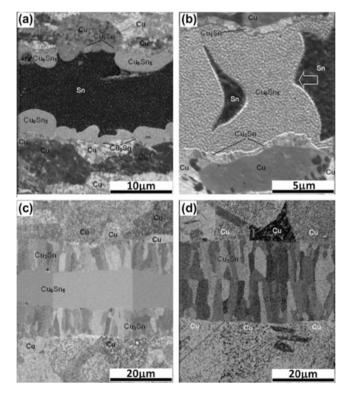

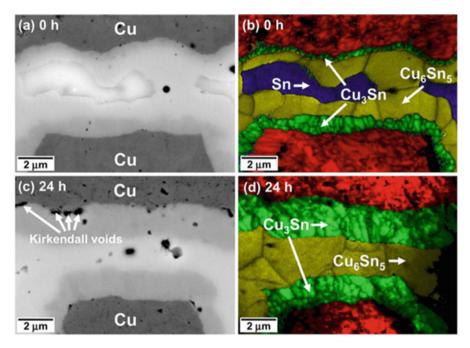

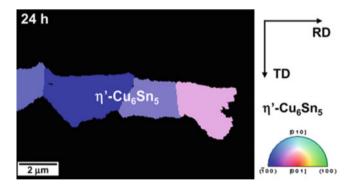

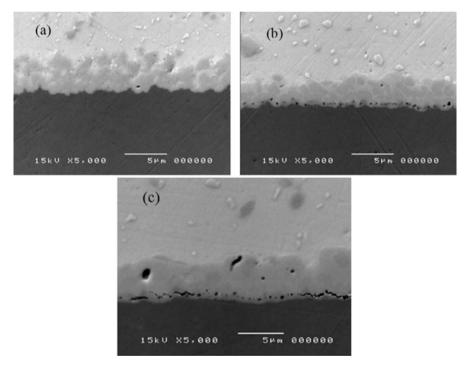

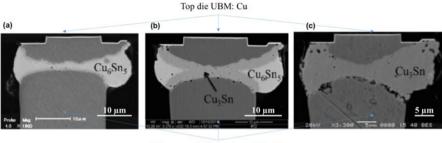

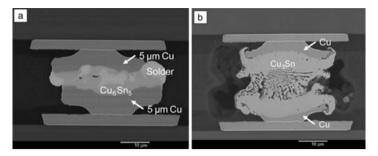

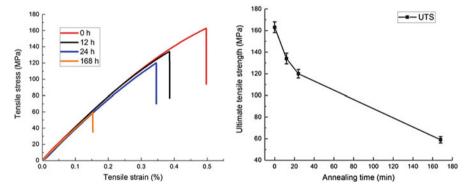

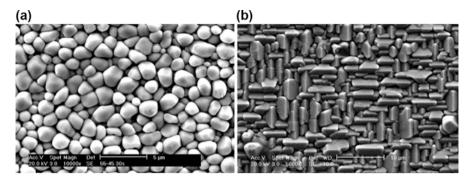

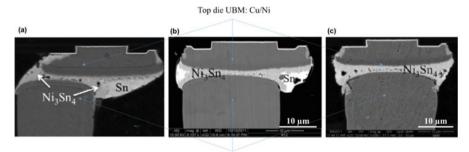

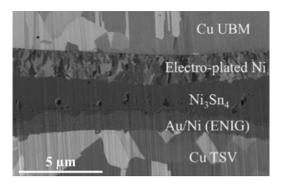

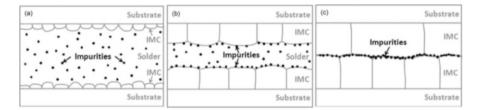

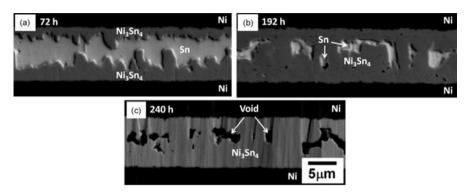

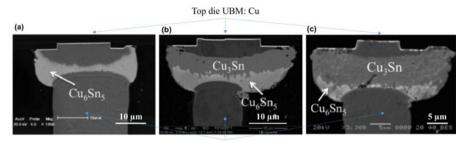

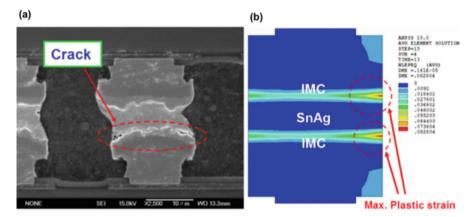

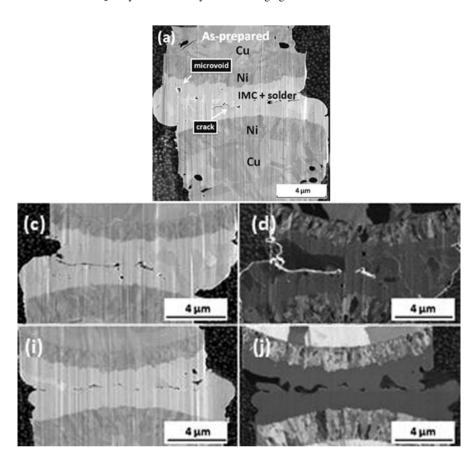

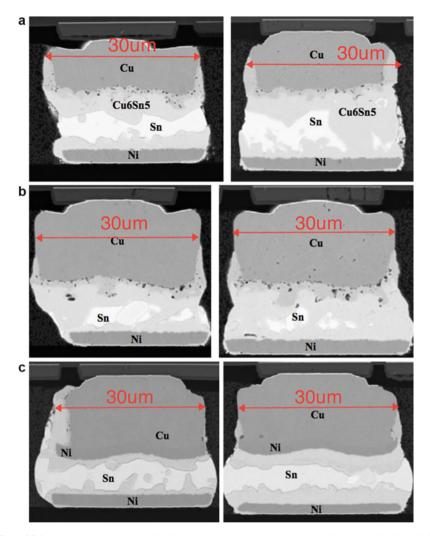

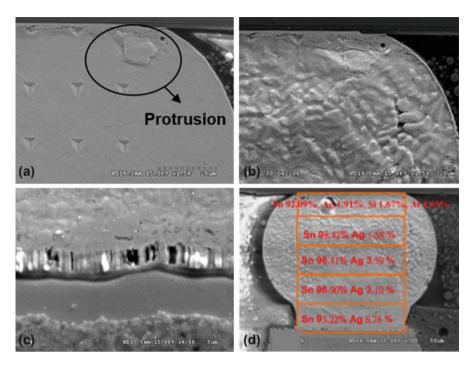

The most commonly used interconnect between stacked die for currently available products with TSVs is solder based (Fig. 2.4a, b) with interconnect pitches as low as 40 µm. Solder-based interconnects have an advantage of being compliant and hence they are more tolerant to misalignment and lack of coplanarity between bonded surfaces during assembly<sup>3</sup>. However as the joints become increasingly small, with decreasing interconnect pitches projected below 40 µm for future 3D stacks, the available solder volume will be reduced and a greater proportion of the solder joint will become intermetallic compounds [15], thus decreasing its compliance. Additionally, with shrinking interconnect pitch, there is an increasing risk of solder bridging during the assembly process since the joints are closer to each other. Various research groups have suggested the need for alternate interconnects; the most common among these are Cu-Cu bonding [17–21], a subject covered in detail in Chap. 6. In 2016, there are two types of widely available products with TSVs. These are DRAM memory stacks [7, 22, 23] and image sensors [24–26].

<sup>&</sup>lt;sup>3</sup> In most applications, Thermo-Compression Bonding (TCB) is used to create the fine pitch interconnect typically needed between two stacked die because of its superior alignment capability over reflow based flip-chip bonding [16].

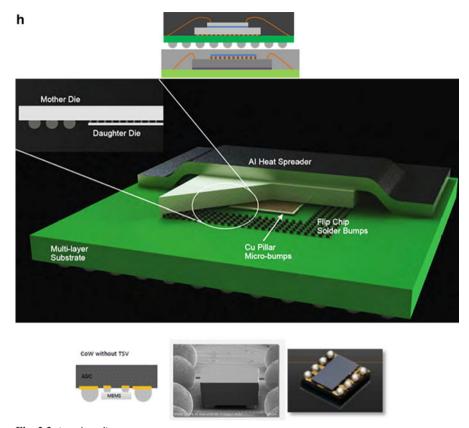

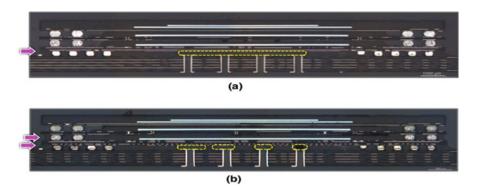

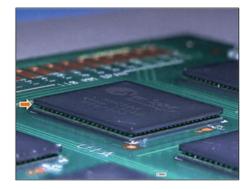

Fig. 2.3 (a) Multi Chip Module (MCP)—Two or more die are attached in a planar configuration to a package substrate (red line in schematic drawing indicates that the two or more die are electrically connected using lateral on-package interconnects). Image shows the Intel Iris Pro processor with a CPU (larger of the two die) and a DRAM chip. (b) Multi Package Module (MPM)—One or more die are packaged before being attached to the final package. Image above shows the Intel's Knights Landing Processor which uses the MC-DRAM Memory Module. The MC-DRAM memory module (a memory stack that conforms to the Hybrid Memory Cube specification [6]) has four stacked memory die connected using TSVs, placed on top of a logic chip). (c) Embedded SIP modules-Embedded SIP modules have solder-less die-to-package interconnects and are usually built using reconstituted wafer level or panel level processes [7, 8]. (d) Package-on-Package (POP) SIP module—Two packages are stacked on top of each other and connected using peripheral interconnects. The peripheral interconnects can be made using solder balls, Cu posts, or solder-coated Cu balls. Example of an MCeP® (Molded Core embedded Package) is shown above. MCeP® is the registered trademark of SHINKO Electric Industries CO., Ltd. (e) EMIB (Embedded Multi-Die Interconnect Bridge) [9]—EMIB-based SIPs use embedded silicon for localized high-density interconnects. Figure above shows a Stratix-10 part from Altera [5]. (f) Silicon interposer-based SIP Module—A silicon interposer is used to for fine feature interconnects between the different chips or chip stacks. The interposer has TSVs to connect the chips to the package substrate. See [10] for a product implementation. (g) 3D TSV-Stacked module-Multiple die are stacked using TSV-based interconnects. Image above shows a HMC memory stack from Micron. (h) SIP Variants that include combinations of wirebond and flip-chip interconnects. The Possum die is from AMKOR

Fig. 2.3 (continued)

Fig. 2.3 (continued)

Fig. 2.3 (continued)

## 2.2 3D TSV-Based Architectures: Advantages and Limitations

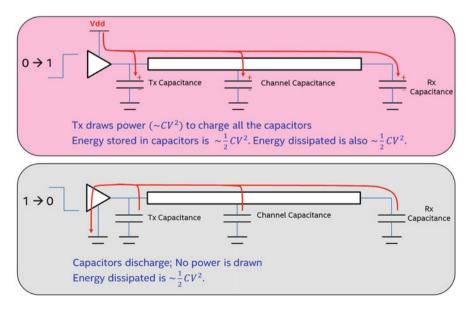

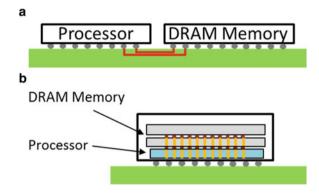

In the past few decades, there has been considerable interest in 3D TSV-based SIP architectures [27–30] because of their compact construction and electrical advantages. The advantages include reduced signal latency, and lower signaling power dissipation due to reduced interconnect lengths. Figure 2.5 shows the energy consumption and dissipation during a  $0 \rightarrow 1$  and a  $1 \rightarrow 0$  bit transition based on a simple capacitance model. Assuming the same Tx and Rx capacitance, energy draw, and dissipation is directly proportional to the capacitance of the interconnect, and this is where TSVs have an advantage over traditional planar wire connections. Since TSVs are short length interconnects, they can exhibit a significantly lower (typically 4–20 times lower [31]) interconnect capacitance compared to a side-byside or planar interconnect. In Fig. 2.6a, a memory is connected to the processor

Fig. 2.4 (a) Solder joints @ 45  $\mu$ m pitch at the GPU to silicon interposer (AMD Fury [10]). (b) HBM Stacks. Leftmost image shows solder bumps on the HBM stack, center image shows the top view of a HBM package with side mold. Image on the right shows the *M*emory–*M*emory *I*nterconnect (MMI) and the TSVs in the memory die. The MMI pitch is 55  $\mu$ m

**Fig. 2.5** Simple capacitance model describing the energy consumption in a Tx (Transmitter)—Rx (Receiver) interconnect link

Fig. 2.6 (a) Schematic illustrating a side-by-side Processor–DRAM interconnect. (b) Schematic illustrating a side-by-side Processor–DRAM interconnect

through a planar on-package interconnect and in Fig. 2.6b the connection uses TSVs. A comprehensive calculation [32] shows that the interconnect power efficiency (mW/Gbps) dropped from 15.65 mW/Gbps (for a bounding case where a DDR memory in a DIMM slot was accessed by the CPU) to 0.55 mW/Gbps when the CPU accessed a WIO<sup>4</sup> memory through TSVs). This is more than a 28× improvement<sup>5</sup>. This power efficiency, multiplied by the number of wires in the interface, combined with reduced data latency due to reduced interconnect lengths is what has motivated designers to consider TSV-based architectures [33]. The power efficiency advantage is appealing across the application spectrum from handheld devices where longer usage times between battery recharging can be enabled to servers where lower energy costs make 3D TSV stacks attractive.

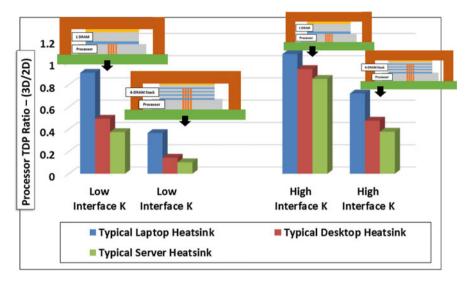

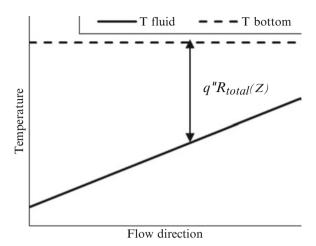

While energy efficiency and latency are the significant advantages for 3D TSV-based architectures, a key limitation is that the maximum *Thermal Design Power* (TDP) can be significantly lower than with comparable 2D configurations. This is due to the thermal resistances in a 3D stack which are in series and hence additive (Fig. 2.7). Consider the case where a DRAM memory is stacked on top of a logic processor<sup>6</sup>. The Processor–DRAM interface, the bulk DRAM silicon, and in the case of multiple DRAM die, the DRAM-DRAM interfaces all add thermal resistances to the heat flow. This compares to a planar case where heat from the processor has to only flow through the silicon of a single chip and a *Thermal Interface Material* (TIM) before reaching a Heat Spreader or the base of a heatsink. Thus, the thermal impact of stacking is that it reduces the total Thermal Design Power (TDP) available for the system designer to utilize for the processor. This is

<sup>&</sup>lt;sup>4</sup> WIO, i.e., Wide IO is a JEDEC standard memory, where the memory die are connected by TSVs [22].

<sup>&</sup>lt;sup>5</sup> Power efficiency quoted for the ESD case. See [*Ref Hazkazemi paper*] for a detailed review of power and performance differences between LPDDR and Wide-IO.

<sup>&</sup>lt;sup>6</sup> This is architecturally a more likely scenario for CPU-DRAM 3D stacks, since the CPU typically needs more bump interconnects than a DRAM and power delivery to a DRAM would require fewer TSVs compared to the converse case, where power is delivered to the CPU through the DRAM.

Fig. 2.7 Schematic showing heat paths in a 2D vs. 3D stack

Fig. 2.8 TDP Impact of 3D stacking

quantitatively shown in Fig. 2.8 using a simple case study comparing TDP between the 3D case (where 1 and 4 DRAMs are stacked on top of a processor) and the 2D case where 1 DRAM or a 4 DRAM stack is placed side-by-side to the processor. In this case study, the following assumptions are made:

- 1. The processor and DRAM silicon are both 100 µm thick.

- 2. Processor power is uniform across the processor die and is time independent.

- 3. Junction temperature limits for both the processor and DRAM are 105 °C.

- 4. Three different system cooling solutions are considered, i.e.,

- (a) High thermal resistance cooling solutions which depend mainly on conduction (Typically encountered in laptop environments where active airflow is not possible)

- (b) Medium thermal resistance cooling solutions which use both conductive and convective heat transfer (Typically encountered in desktop environments that use cost-performance optimized cooling solutions)

<sup>&</sup>lt;sup>7</sup> System cooling refers to the cooling solution attached to the SIP.

- (c) Low thermal resistance cooling solutions which use both conductive and convective heat transfer (Typically encountered in server environments that use performance optimized solutions to manage high TDP envelopes).

- 5. The Processor–DRAM and DRAM–DRAM interfaces, comprising metallic interconnects and protective underfill, are key interfaces that limit heat transport since the effective thermal conductivity (K) across that interface tends to be in the approximate range (0.3–3.0 W/m  $^{\circ}$ C), which is significantly lower than the thermal conductivity of silicon (110 W/m  $^{\circ}$ C) or Cu (390 W/m  $^{\circ}$ C). Two different interface conditions are considered for the analysis including a low interface with K=0.3 W/m  $^{\circ}$ C and high interface with K=3.0 W/m  $^{\circ}$ C

In cases where the system thermal resistance is high relative to the package resistances, the impact of changes in package resistance has a lesser influence on the overall TDP. In these cases, a system designer can increase memory capacity and still take advantage of improved memory capacity and power savings. As the performance of the system thermal cooling solution improves, increasing package resistance (with increasing number of stacks) will have a greater influence on the product's TDP capability. In this scenario, the TDP degradation and increasing the number of stacks is more significant. It can be seen from Fig. 2.8 that since the bulk of the heat transfer in the package is conduction based. For this case, improvements in the effective thermal conductivity of the interfaces between the stacked silicon chips are critical to improving the overall TDP capability. The effective thermal conductivity of the interface can also be improved by increasing the number of micro-bumps between the die, and by increasing the effective thermal conductivity of the underfill, or polymeric encapsulant, used to increase the reliability of the micro-bumps. Additionally, there is a need to improve the quality of system thermal solutions. Chapter 10 summarizes the various thermal solution strategies developed to address the thermal management problem in 3D stacking.

It should also be noted that the assumption of uniform power distribution in the processor is simplistic. In most cases, the processor power distribution is nonuniform. The presence of the additional thermal interfaces from the DRAM stack will exacerbate the hot spots compared to a side-by-side configuration. Design approaches that minimize the thermal burden on the package have been shown to be capable of achieving thermal equivalence with 2D configurations [34].

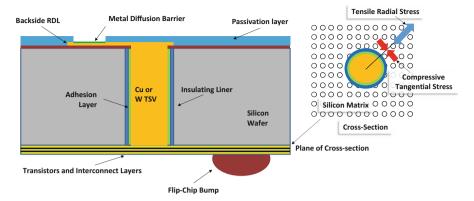

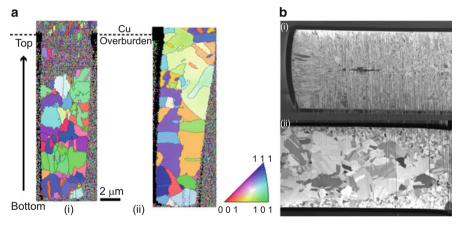

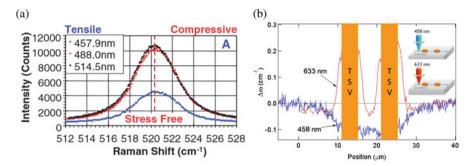

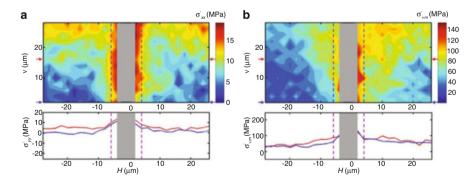

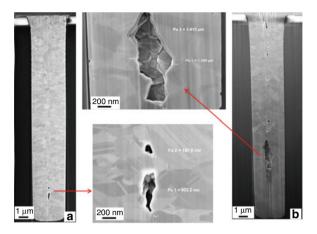

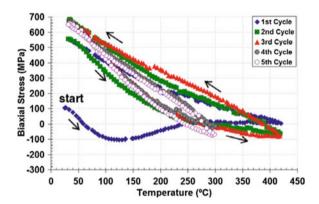

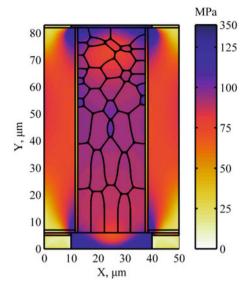

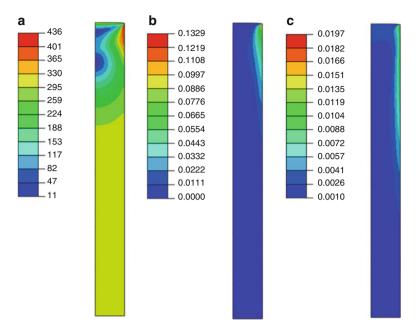

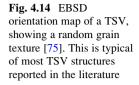

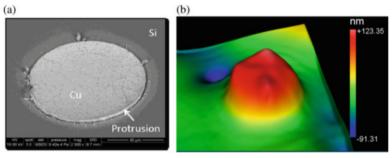

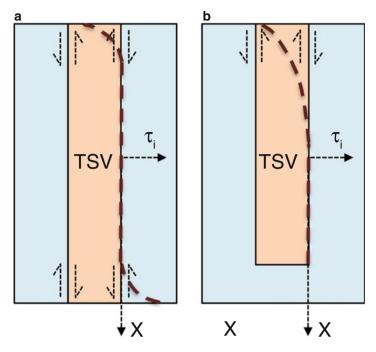

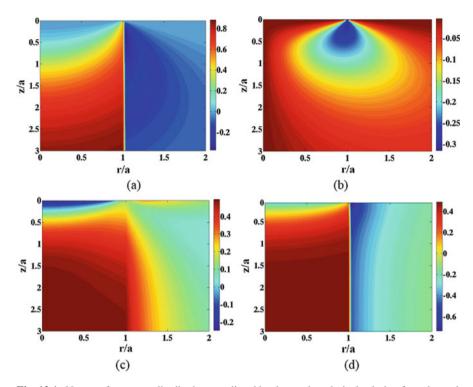

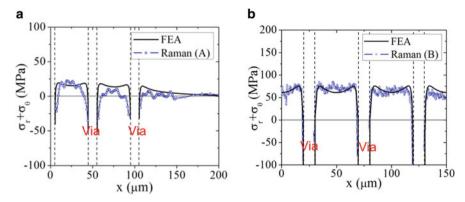

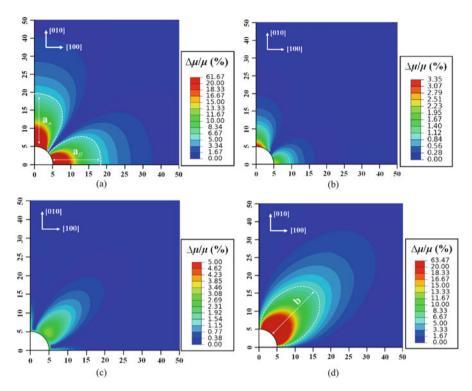

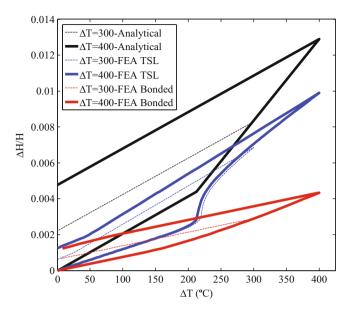

Another key consideration is the impact of TSVs on the stress state in silicon. Cu and W are typical materials used for TSVs and polysilicon TSVs have also been mentioned in literature [35]. TSVs are typically filled using *E*lectro-*C*hemical *D*eposition (ECD) at temperatures greater than 200 °C<sup>8</sup>. The ECD temperatures are significantly higher than the typical operation temperature of a processor or a memory device which tend to be in the (90 °C–110 °C) range. At the deposition temperature, the TSV is in an equilibrium (i.e., stress-free) state with the

$<sup>^8</sup>$  200 °C quoted as a typical lower temperature bound. A number of FEOL and MEOL processes have deposition temperatures significantly higher than 200 °C.

Fig. 2.9 Stresses in silicon due to TSV integration

surrounding silicon, however at operating temperatures, the TSV induces radially tensile and tangentially compressive stresses in the surrounding silicon (see Fig. 2.9 for a schematic illustration) resulting from the CTE differential between the Cu/W fill and the surrounding silicon. These stresses have an impact on the electron and hole mobility in the transistors and hence an impact on transistor performance and reliability [36–38]. Keep out zones (KOZ), i.e., regions in the silicon surrounding the TSVs where transistors cannot be placed, are specified for silicon designers so that performance and reliability impact is reduced to an acceptable level. The consequence is that there is a silicon area increase due to both the TSV and its associated KOZ.

In summary, the power efficiency advantage due to short TSV interconnects must be balanced against the disadvantages in TDP reduction and increased chip area due to the TSV integration. A designer must ensure that the disadvantages don't adversely affect the overall performance or value of the product being designed.

#### 2.3 Methods of Fabrication and Other TSV Attributes

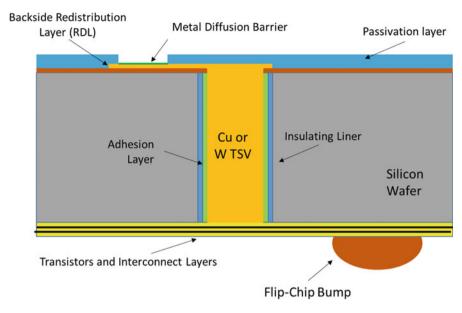

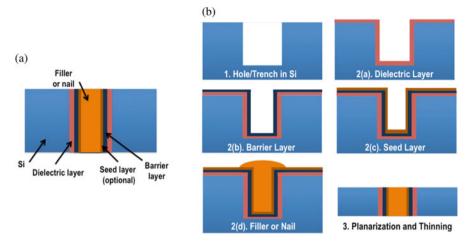

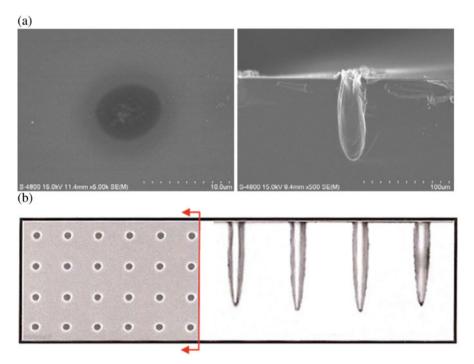

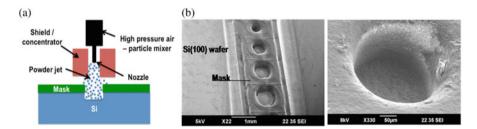

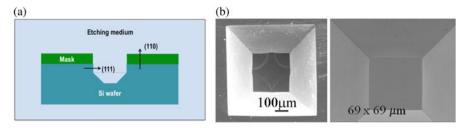

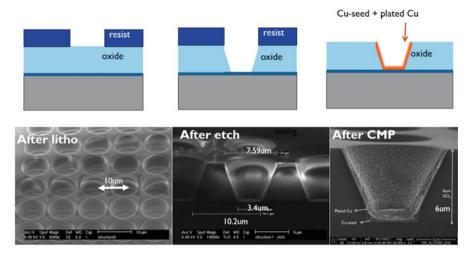

The structure and location of a TSV with reference to the transistors and back-end interconnect stack in a typical wafer is shown schematically in Fig. 2.10. TSVs are typically created using a process with the following steps:

- A photoresist is coated on the silicon wafer and lithographic exposure is used to define the TSV locations.

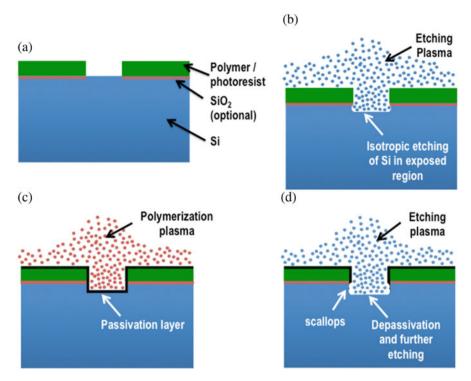

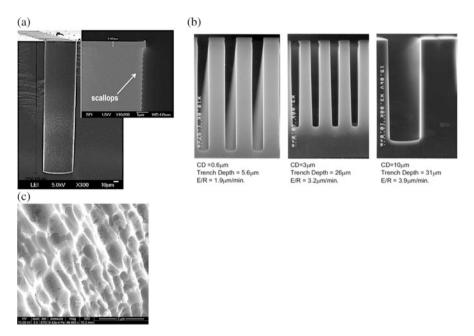

- The silicon is etched, typically using the Bosch process [39], which uses multiple sequences of *etch and coat* to create the via holes.

- The photoresist is then stripped and the wafer surface is cleaned.

Fig. 2.10 Schematic showing the structure of a TSV in the silicon back-end interconnect stack

- The inner walls of the TSV are coated with a dielectric liner (typically SiO<sub>2</sub> though Si<sub>3</sub>N<sub>4</sub> has also been reported [40] using thermal oxidation or PECVD (Plasma Enhanced Chemical Vapor Deposition). The liner electrically isolates the TSV from the bulk silicon.

- Next an adhesion layer, typically Ti or Ta, is added on the inner lining of the TSV using PVD (Physical Vapor Deposition).

- A seed layer is deposited in the via hole next and the vias are ready for deposition

of the TSV metal.

- Electro-Chemical Deposition (ECD) is used to fill the via holes with Cu or W.

- Vias are annealed to stabilize the TSV microstructure and to relieve stresses within the TSV.

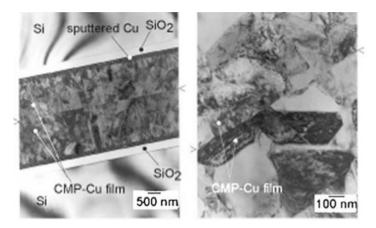

- Finally, Chemical Mechanical Polish (CMP) is used to planarize the wafer.

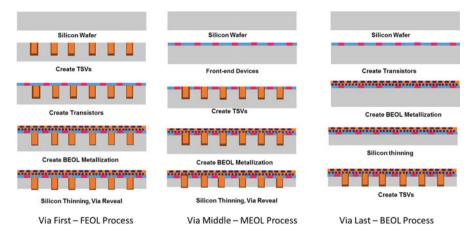

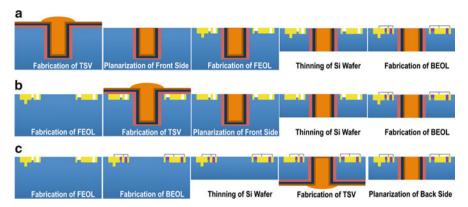

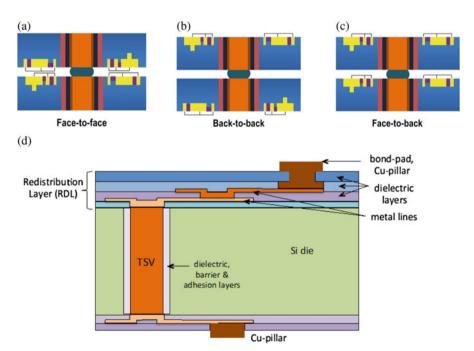

- TSVs are typically manufactured using three different processes (Fig. 2.11)

- 1. Via First Process (Also referred to as the Front End Of Line (FEOL) Via Process): In this process, the TSVs are created before the transistors [40, 41]. Key steps in this process are

- (a) The wafer surface is patterned and TSVs are etched and filled on the transistor side (front or active side) of the wafer.

- (b) After the TSV formation, the wafer is planarized and readied for transistor creation.

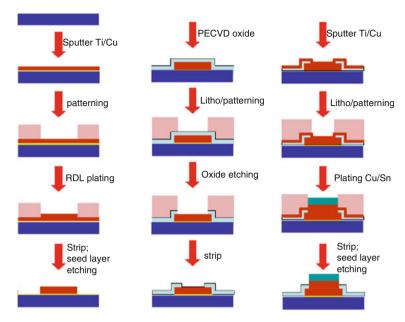

Fig. 2.11 High-level process flow for the three processes of creating TSVs

- (c) Transistor creation is followed by the Back End of Line (BEOL) process which creates the multiple metal/insulator layers on the silicon wafer.

- (d) Finally, the wafer backside is thinned to reveal the vias and creates a Redistribution Layer (RDL) (Fig. 2.12).

An important advantage of the Via First approach is that since the vias are created before transistor creation, only known good wafers with defect-free TSVs can be used for subsequent steps. Additionally, some authors [40] have claimed that the Via First process allows for a fewer design constraints and a higher density of vias compared to the Via Middle and Via Last processes<sup>9</sup>. A key limitation of the Via First approach is that all the TSV materials and processes need to be compatible with CMOS processes and temperatures (~1200 °C). Polysilicon vias are mostly used in the Via First process [41]. Bauer et al. [40] discuss a process where high density vias are created in a Via First process using a silicon as a sacrificial material during the initial via formation step. The silicon is replaced with W after the transistor formation processes are completed.

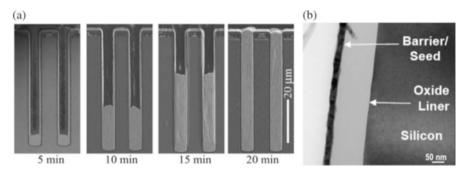

- 2. Via Middle (Also referred to as Mid End of Line (MEOL) Via Process: In this process, TSV formation is after front-end device creation and before the creation of all the back-end metal layers [41–47]. Key steps in this process are as follows:

- (a) Front-end devices are fabricated including transistors and several lower metal layers.

- (b) Next, TSVs are created from the active device side typically at temperatures in the 400  $^{\circ}$ C-450  $^{\circ}$ C.

- (c) The TSV is then plated with Cu or W.

<sup>&</sup>lt;sup>9</sup> While this statement seems intuitively feasible, the authors are not aware of an authoritative study that establishes the design advantages of the Via First process over the Via Middle or Via Last options.

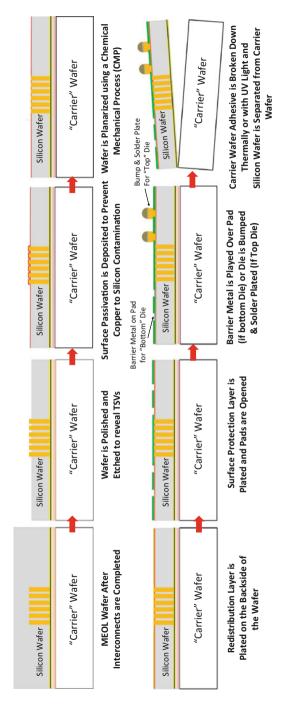

Fig. 2.12 Bumping process flow post TSV formation, shown for the MEOL/FEOL TSV process

- (d) The wafer is then annealed at  $\sim$ 400 °C to relieve stresses in the TSV and to stabilize the TSV metal structure.

- (e) Next, the wafer is planarized with a typical damascene process and readied for the remaining BEOL metallization.

- (f) After BEOL metallization is complete, the wafer is mounted on a carrier and thinned to reveal the TSVs on the inactive (backside) of the wafer. Via reveal is usually (optionally) followed by creation of a Re-Distribution Layer (RDL) and backside bump formation processes that is a critical structure for die stacking (See Fig. 2.12).

An advantage of the Via Middle process is that subsequent chip fabrication processing temperatures are lower than for the Via First process, and hence the thermal stresses induced in silicon due to the CTE mismatch between the silicon and TSV metal are lower.

- 3. Via Last (Also referred to as Back End Of Line (BEOL) Via Process: In this process, TSVs are created after the transistors and interconnects are created [41, 48]. Key steps in this process are as follows:

- (a) The transistors and the entire BEOL process is first completed.

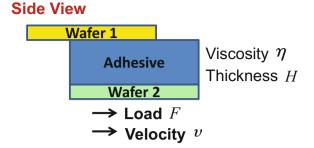

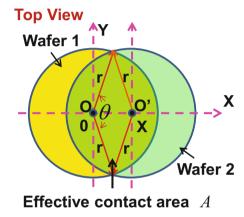

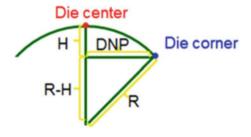

- (b) The wafer is then temporarily attached to a carrier using an adhesive (usually referred to as a wafer bond/debond adhesive) on the active (front side).

- (c) The wafer is thinned and the TSVs are formed using a similar process to the Via Mid described earlier. This is followed by manufacturing of the RDL and backside bumping. The backside RDL and bumping process are essentially the same as described in Fig. 2.12.

In the Via Last process, TSV processing temperatures are typically lower than 200 °C. This is important since the fully formed wafer is mounted on a carrier using a low temperature adhesive. An advantage of this approach is that the thermal stress issues are lower than with the Via First and Via Middle process options. However, there are two significant concerns with the Via Last process. First since TSVs are created after the BEOL, the TSVs need to land at the right metal layer in the chip metal wiring. Special landing surfaces, also called catch cups, are included in silicon metal layers to precisely locate the TSVs. Special care needs to be taken that the TSVs land on catch cups and don't accidentally punch through the catch cups. Integration of catch cups requires careful design and restricts the placement of the TSVs. Secondly since the TSVs are formed after complete wafer processing, yield loss due to TSV formation could result in loss of valuable silicon.

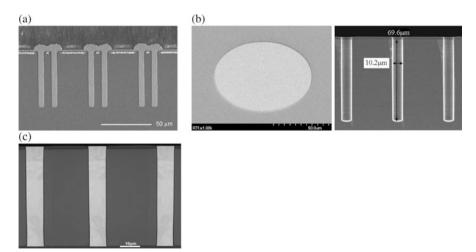

Some of the key design attributes of TSVs are their diameter, pitch, aspect ratio (i.e., the ratio of TSV diameter to its depth), electrical characteristics (including resistivity, inductance, and frequency dependent capacitance), and stress-related KOZs. TSV aspect ratios are influenced by a few key parameters such as the ability to get good insulation coverage as a function of via depth and the ability

|           | TSV      | Silicon   |                  |              |               |

|-----------|----------|-----------|------------------|--------------|---------------|

|           | diameter | thickness | Aspect ratio     | TSV          |               |

| Reference | (µm)     | (µm)      | (diameter:depth) | material     | Process       |

| [40]      | 2        | 45        | 1:22.5           | W            | FEOL          |

| [41]      | 5        | 150       | 1:30             | Poly-silicon | FEOL          |

| [42]      | 3        | 100       | 1:33.3           | W            | MEOL          |

| [48]      | 10       | 50        | 1:5              | Cu           | BEOL          |

| [43]      | 6        | 55        | 1:9              | Cu           | MEOL          |

| [44]      | 10       | 50        | 1:5              | Cu           | MEOL          |

| [49]      | 5        | 50        | 1:10             | Cu           | MEOL/BEOL     |

| [50]      | 20       | 50        | 1:2.5            | Cu           | BEOL          |

| [51]      | 2        | 30        | 1:15             | Cu           | Not specified |

| [46]      | 3        | 50        | 1:17             | Cu           | MEOL          |

Table 2.2 Some recent TSV dimensions reported in the literature

to get void-free via filling. Table 2.2 shows some of the published data on TSV diameters and depth. Electrical and stress characteristics are determined by the TSV materials choices (including via metal, liner, and adhesion materials) and process choices (deposition and anneal temperatures).

### 2.4 Assembly Process Flows

3D stacks can be assembled using three different approaches. They are commonly referred to as Wafer-to-Wafer (W2W) attach [52, 53], Die-to-Wafer (D2W) attach [53–56], or Die-to-Die (D2D) attach.

#### (a) Wafer-to-Wafer Attach (W2W)

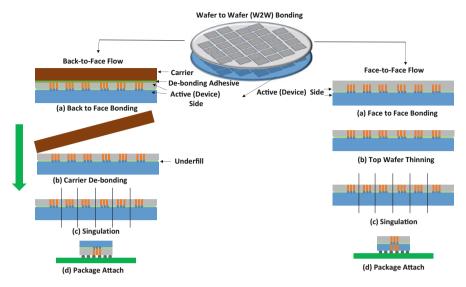

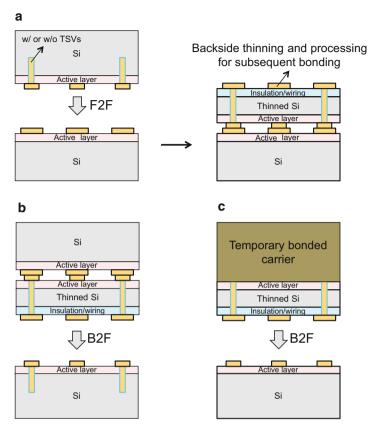

In this process, entire wafers are aligned and then bonded, followed by the singulation of individual die stacks. Two W2W flows are schematically illustrated in Fig. 2.13.

- Back-to-Face Flow: where the inactive side (back) of the top wafer is bonded to the active (front) side of the bottom wafer. This approach can enable multiple wafers with TSVs to be bonded one after the other, while retaining the back-to-face connectivity between the die.

- Face-to-Face Flow: where the active side of the top wafer is attached to the

active side of the bottom wafer. This approach is less valued for stacking more

than 2 wafers.

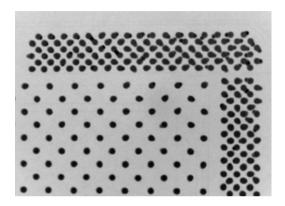

A significant advantage of a W2W process is that both bonding surfaces are extremely flat, and thus there can be excellent wafer-to-wafer alignment ( $<3~\mu m$  across the wafer) and hence very fine interconnect pitches can be achieved. In the case of solder-based interconnects, pitch scaling in W2W attach is limited by solder

Fig. 2.13 Schematic describing the key steps in a W2W attach process

bridging between interconnects and the implications of intermetallic compound formation. Another advantage of the W2W process is that it is a batch process and with high manufacturing throughput. Key limitations of the W2W process include: (1) all the die have to be of the same size; (2) the process precludes the ability to bond known good die together; (3) yield loss due to misalignment during this process can be significantly expensive, especially in the case where multiple wafers are stacked.

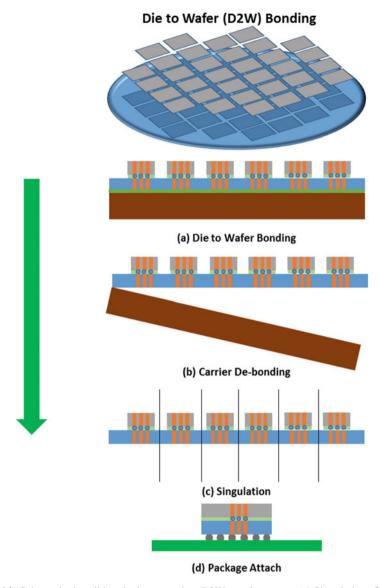

#### (b) Die-to-Wafer Attach (D2W)

In this process, individual die (with or without TSVs) are bonded on a base wafer incorporating TSVs mounted on a carrier (Fig. 2.14). This process has similar advantages of alignment as the W2W process, and it is not limited by the requirement for the die to be the same size. The top stacked die used in successive stacking steps can be the same size or smaller than the corresponding die below it. If only known good die are stacked, better yields than the W2W process can be expected. Additionally, top die with different functionality than the bottom die can be stacked, allowing for increased heterogeneous integration. Unlike the W2W flow, D2W is a sequential process which will have considerably slower process throughput times.

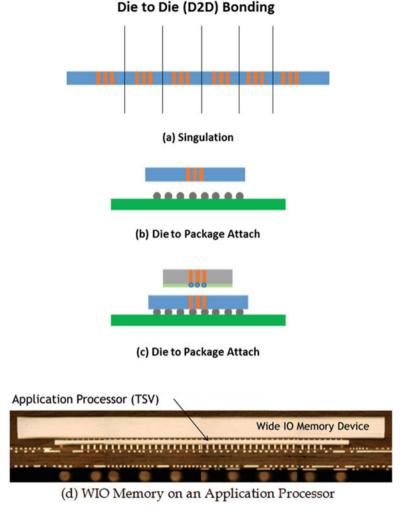

#### (c) Die-to-Die Attach (D2D)

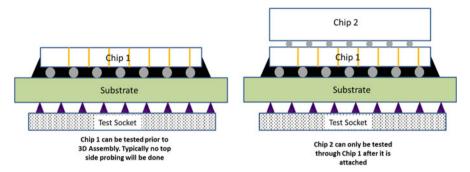

In this process flow, bottom die is first assembled to a package substrate and subsequently other die or die stacks are then stacked on the die connected to an assembled package (Fig. 2.15). This process resolves the die size limitations of

Fig. 2.14 Schematic describing the key steps in a D2W attach process. (a) Singulation; (b and c) die to package attach; (d) WIO Memory on an application processor

the W2W and D2W flows through careful alignment methods. In this way, die larger than the bottom die can be stacked on top. Since the bottom die can be fully tested prior to committing the top die, this process has best chance among the three process of creating known good stacks. However, a key disadvantage of this process is that since the bottom die is fully assembled to a package substrate

Fig. 2.15 Schematic describing the key steps in a D2D attach process

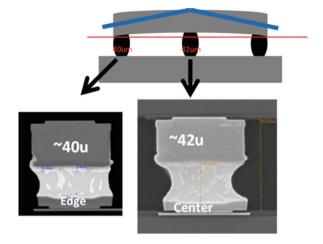

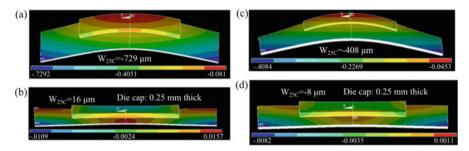

(typically to an organic package), it can become quite warped because of the CTE mismatch with the package. Hence during the attach of the top die to the bottom package, the die to package yield can be compromised due to the alignment challenges that are created. In general, the 3D stacking process is an exercise in precise tolerance and process control and requires very good characterization of the surfaces being assembled as a function of temperature. Some of this is schematically illustrated in Fig. 2.16.

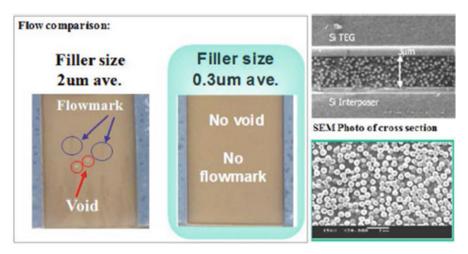

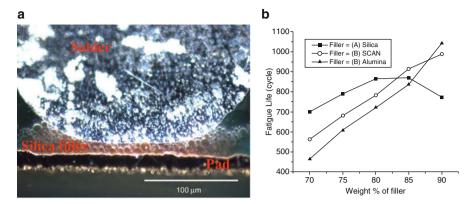

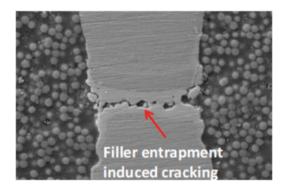

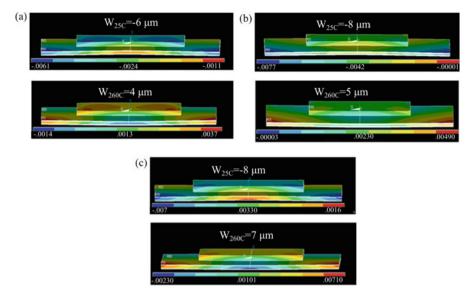

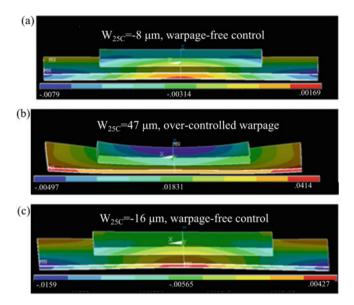

An important consideration in all three attach processes is the ability to successfully underfill the die–die interconnects which is especially challenging at very fine

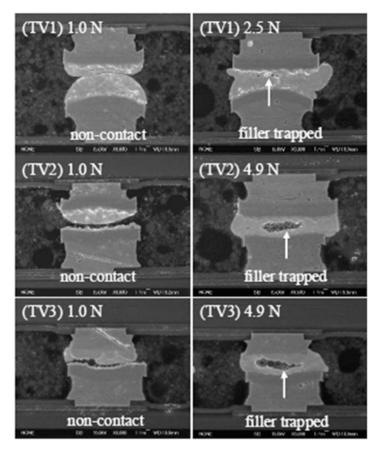

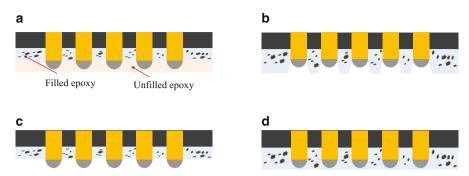

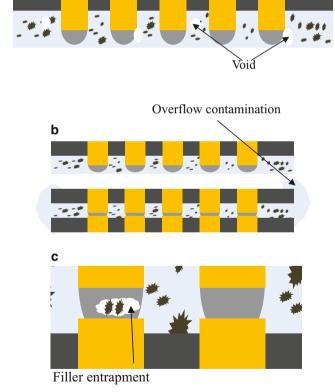

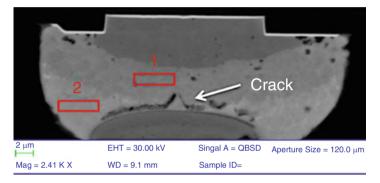

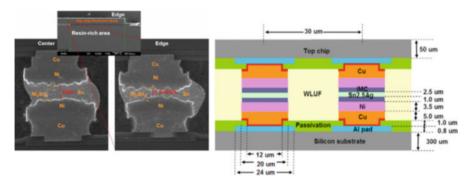

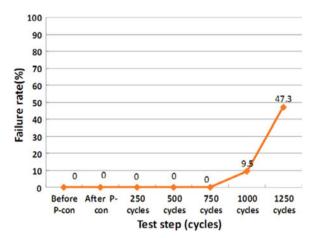

Fig. 2.16 Yield loss in SIPs as a function of individual process step yields

pitches. Underfill is needed to improve the reliability of the die-to-die and die-topackage interconnects. Since the die–die interconnect pitches are significantly lower (typically  $\leq 55~\mu m$ ) compared to typical die–package interconnect pitches (typically  $\geq 100~\mu m$ ) the gaps or empty space between bumps become smaller for die–die interconnects. This creates another disadvantage of the D2W process. Since it is a sequential stacking process, a dispense underfill process is possible, but underfill bleed-out and unintentional cure in adjacent unattached chip area is a concern. Dispense of underfill after all the die are attached is a possibility that needs to be carefully planned ahead to ensure there is a sufficient gap between the die for adequate underfill flow between the solder-based bump interconnects. Pre-applied film underfills are a better choice for D2W stacking, however if filled underfills are used to deliver the improved thermal performance (Sect. 2.2) filler entrapment in the solder joints during chip attach becomes an important concern.

## 2.5 Manufacturing Yields and the Role of Test

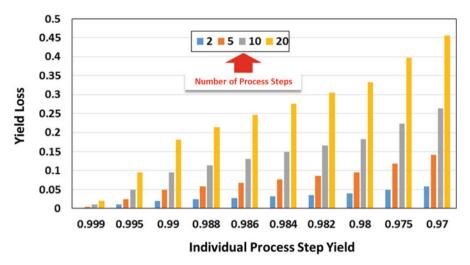

One of the key goals in manufacturing multi-die modules is to maximize manufacturing yields. Minimizing the number of good die scrapped in modules that fail when tested, has a large impact on average product cost. This proposition can be quantified using a simple example. Consider a module that has n number of die, each of which costs a, and is attached to a single package substrate that costs b. For simplicity, assume that each die is attached to the package in a single process step (i.e., the entire assembly process is a single integrated step), hence the overall SIP assembly process has n steps—one step for each die. If the yield in each

Fig. 2.17 Key steps in a package assembly process

assembly step is z, then the yield after n steps is  $z^n$ ; the yield loss is  $(1-z^n)$ . The yield loss is plotted as a function of number of steps and individual process step yield in Fig.  $2.16^{10}$ . The cost due to scrapped modules that fail due to a flaw in the assembly process is  $(na+b) \times (1-z^n)$ . There are two primary ways of reducing the cost of scrapped units.

#### (a) Increasing individual step yield

Increasing yield of each individual step in the assembly process is the main focus of packaging technology development. Process, materials, and design parameters for each assembly step, and the impact to upstream and downstream steps of the process are carefully studied and optimized for maximal yield.

#### (b) Ensuring each key component "Known Good"

If only known good components are assembled, the chances that the overall module will perform as intended is significantly increased. Components and subassemblies need to be fully tested prior to assembly to ensure that they are *known good*<sup>11</sup> and cause no yield loss when modules are tested. Designing an efficient test flow that maximizes quantity of known good components while minimizing any added test cost is a key focus area.

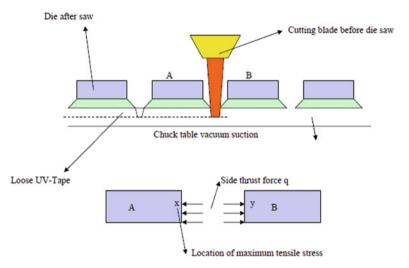

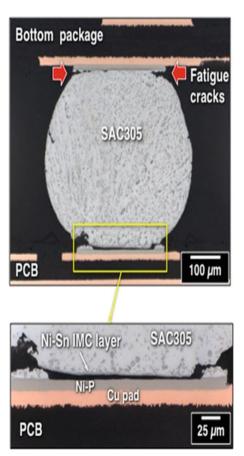

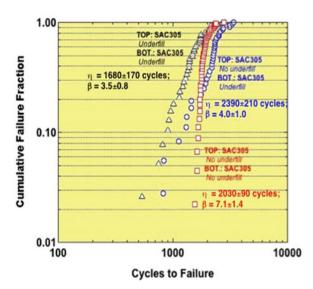

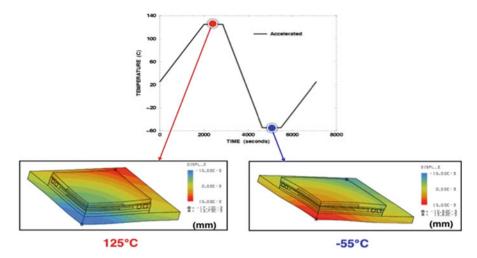

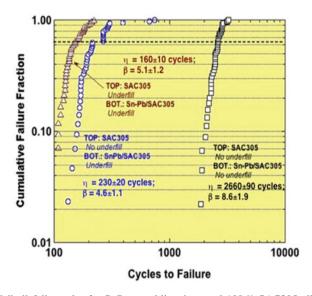

Before discussing the challenges involved in testing SIP modules with 3D TSV stacks, it is necessary to understand the different steps involved. A high-level assembly process flow for a single component is illustrated in Fig. 2.17 to show the typical points in the flow where the wafer, die, and assembled package are tested to check for manufacturing quality or performance. Key steps involved in testing products include: