Because Testing Matters

# Teradyne, Inc.

The Dynamic World of Semiconductors and Implications for Test

Mark Jagiela President, Semiconductor Test June, 2007

#### **Overall Semiconductor Industry Trends**

- Industry consolidation/partnerships/outsourcing growing

- Design is King, Manufacturing technology less of a differentiator

- Shared risks and costs of progress in face of complexity

- Test methods are still IP, test execution increasingly outsourced.

- Lithography migration "velocity" is slowing

- New nodes getting lower percentage of new designs

- Devices rely on "multi-core" designs to increase performance

- More testing complexity at protocol level, non-deterministic.

- Consumer Market is driving device roadmaps and volumes

- Time to market becomes a key differentiator

- Implies need for more streamlined design-to-test processes

- Is test cost keeping up?

Because

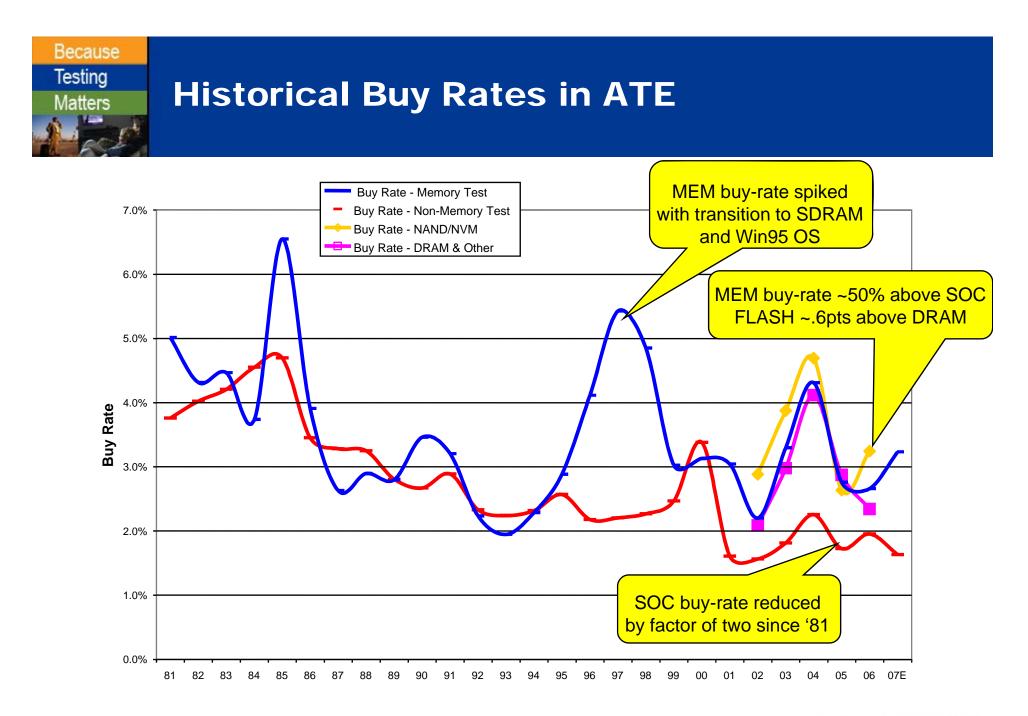

- ATE Buy Rate Measures Productivity of Capital Expense

Calculated as Yearly ATE CAPEX/Semi Revenue

- ATE Buy Rate has been trending down for 20+ years

Lets look at the historical data!

Korea Test Conference June 2007

#### **CAPEX Productivity Improvement in Memory**

#### SOC CAPEX is More Efficient by Nearly 50%

- ~2% vs ~3% buy rate

Current Trends in Memory to Improve CAPEX Productivity

- Reduced pin count test

- Increased wafer level testing

- Known Good Die test

- Single Touchdown wafer test

- $\rightarrow$  Lower capital cost per site

- $\rightarrow$  Increase package test yield

- $\rightarrow$  Eliminate final test insertions

- $\rightarrow$  Reduced test time per wafer

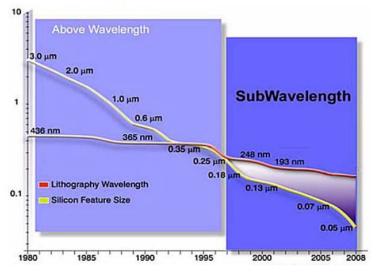

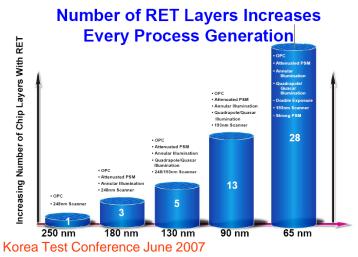

# Lithography is getting more complex

#### Growing Gap Between Lithography Wavelength and Feature Size

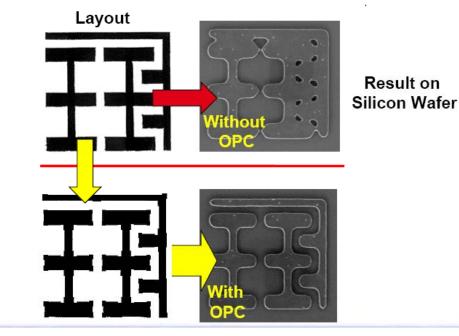

#### What You Design Is Not What's on the Photomask

## These techniques are called Reticule enhancement or RET.

Source: Mentor Graphics

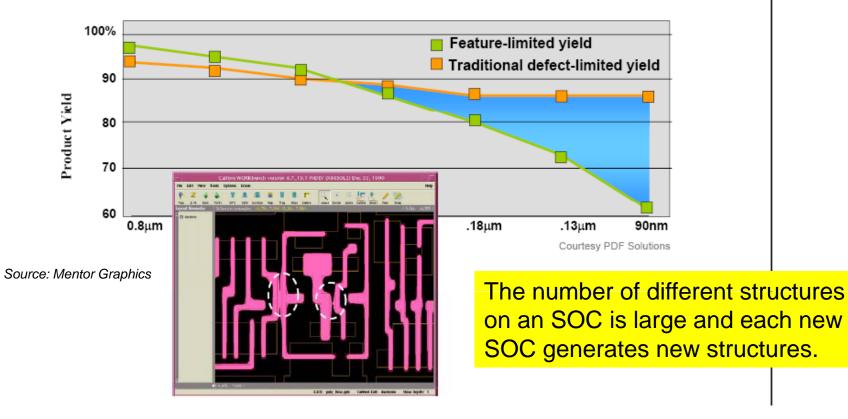

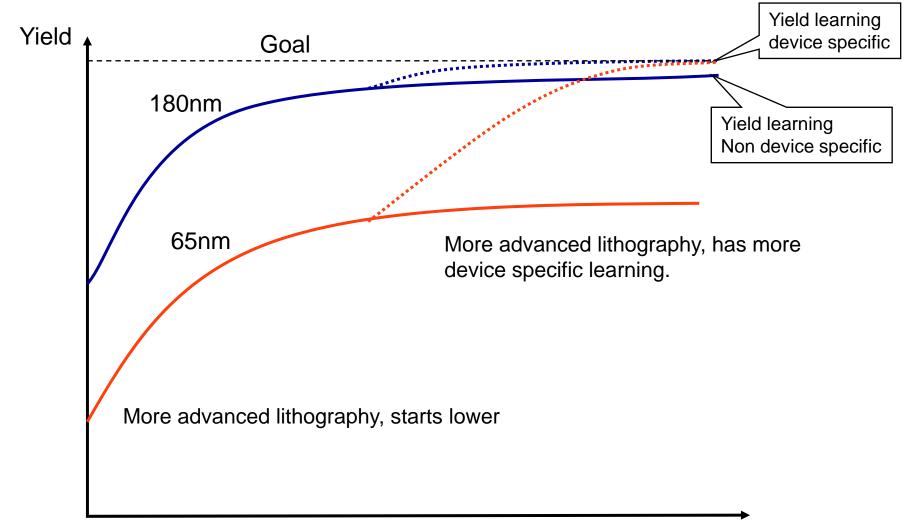

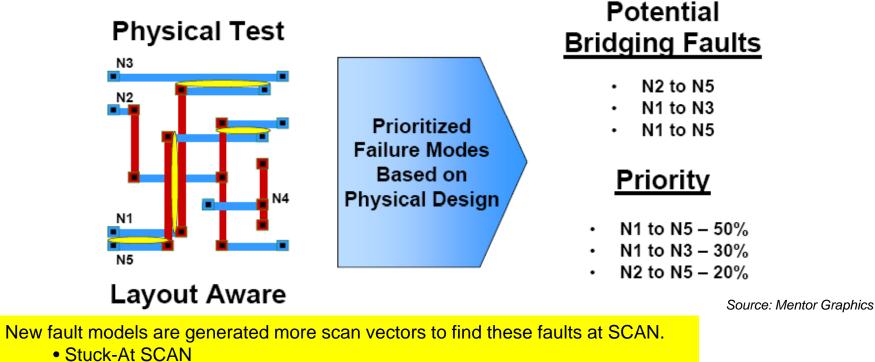

### Yield limited by Structures not Particles

#### Manufacturing Yields Increasingly Limited by Physical Features Instead of Particles

## Scan can isolate the failures for Yield Learning with new models

## Physical Layout Based Test

- AC SCAN (transition faults

- Bridging

- Opens

Capturing 250 failures allows unique isolation of a fault

Korea rest Conference June 2007

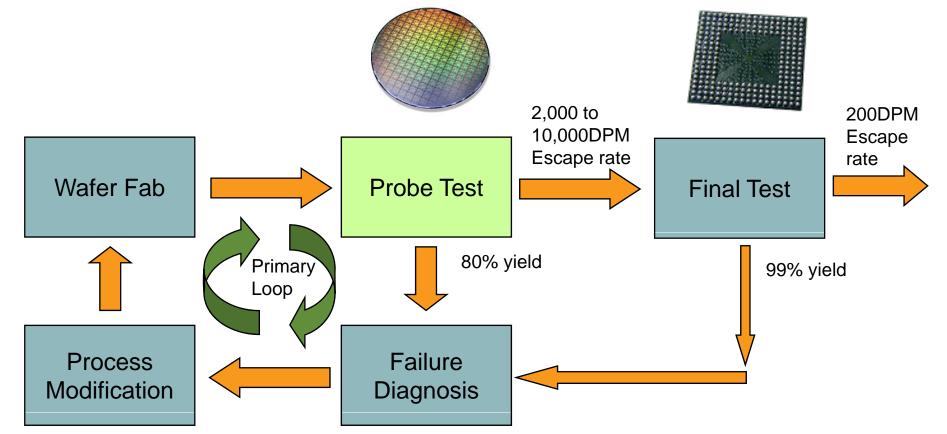

Probe results are primary path for yield learning.

- Tighter connection to the Wafer foundry

- Data is available sooner

- Lower cost insertion

SCAN results are the primary data used because they enable rapid fault isolation.

Korea Test Conference June 2007

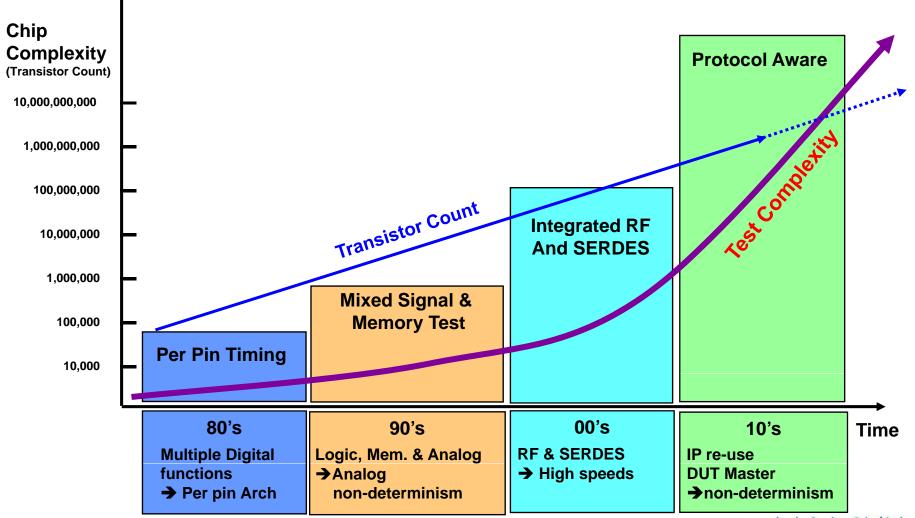

#### IP re-use: Design Engineers Heaven, Test Engineer's Hell

- Designers tape out full feature designs faster using Asynchronous IP that speeds design time and chip timing closure

- Designers work with <u>high level behavior simulations</u>, simplifying verification of complex bus protocols.

- Test Engineers do not have re-usable TEST IP

- Asynchronous I/F make test results non-deterministic, a tough test challenge

- Test Engineers work at a low level of abstraction, <u>dealing with every bit</u> in each complex protocol.

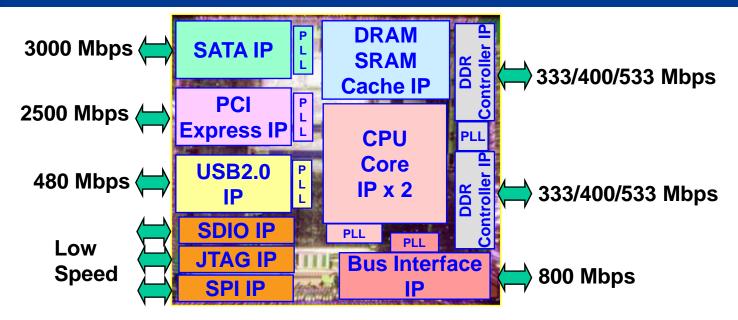

#### The Future of ATE is Protocol Aware

- Limited Protocol Aware ATE capability is available today

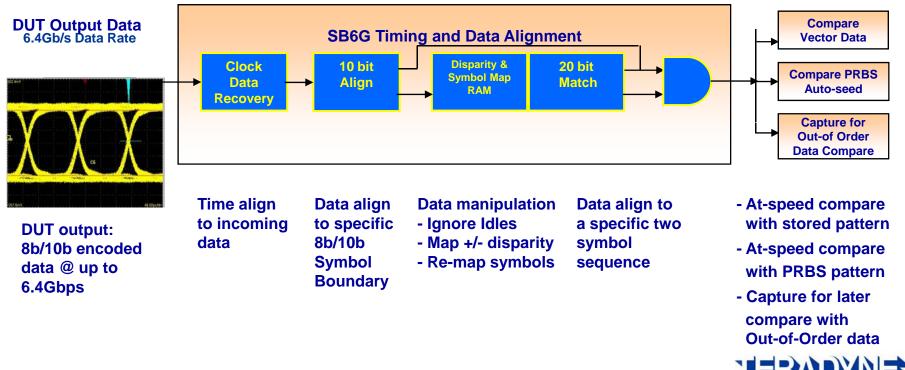

- A first generation Protocol Aware Instrument is the UltraFLEX SB6G

- Designed for at-speed test of High Speed Serial buses like PCI Express and SATA

- SB6G can recognize, manipulate, and compare 8b/10b encoded DUT output data

#### The Future of ATE is Protocol Aware

- ATE will become Protocol Aware rather than just stored-response patterns

- Future Protocol Aware ATE capabilities include:

- Transactional level software so <u>design</u> and test interact with the device at the same high level of abstraction. Faster time to yield and faster test development and debug.

- Low latency DUT<-> ATE handshaking to support higher level functions such as memory (RAM/Flash/ROM) emulation.

- Deal with non-deterministic DUT behavior such as timing shifts, idles, & out-of-order data.

- Support at-speed functional test in device native operating mode (Mission Mode) for lower DPM.

Testing Matters

# **Thank You**