# **PRESS KIT**2006

## ISSCC VISION STATEMENT

The International Solid-State Circuits Conference is the foremost global forum for presentation of advances in solid-state circuits and systems-on-a-chip. The Conference offers a unique opportunity for engineers working at the cutting edge of IC design and use to maintain technical currency, and to network with leading experts.

## TABLE OF CONTENTS

| ISSC | C 2006     |                                                                             | 1  |

|------|------------|-----------------------------------------------------------------------------|----|

|      | ACTIVITI   | ES AT ISSCC 2006                                                            |    |

|      |            |                                                                             |    |

|      |            | CANT RESULTS                                                                |    |

|      |            |                                                                             |    |

| ISSC | C 2006     |                                                                             | 9  |

|      | EVENTS     |                                                                             | 11 |

|      | PAPER S    | STATISTICS                                                                  | 12 |

|      | PLENAR     | Y SESSION                                                                   | 13 |

|      | TECHNIC    | CAL HIGHLIGHTS                                                              | 15 |

|      | EVENING    | G SESSIONS                                                                  | 19 |

|      | Short Cou  | urse                                                                        | 20 |

|      | Tutorials  |                                                                             | 21 |

|      | ADVANC     | ED CIRCUIT DESIGN FORUMS                                                    |    |

|      |            | CED WIRELESS CMOS TRANSCEIVERS                                              |    |

|      |            | DED-SRAM DESIGN                                                             |    |

|      |            | T DESIGN IN EMERGING TECHNOLOGIES                                           |    |

|      |            | IMAGING                                                                     |    |

|      |            | IIGH-SPEED INTERCONNECT                                                     |    |

|      | MULTI-C    | CORE ARCHITECTURES, DESIGNS, AND IMPLEMENTATION CHALLENGES                  | 26 |

| 1990 | C 2006     |                                                                             | 27 |

| 1330 |            |                                                                             |    |

|      |            | EW                                                                          |    |

|      |            |                                                                             | 31 |

|      | Panel      | PRESENT (AND FUTURE) CLASSIC CIRCUITS WITH                                  | 07 |

|      | Tutorial   | LESS THAN 25 TRANSISTORS<br>INTRODUCTION TO FRACTIONAL-N PHASE-LOCKED LOOPS |    |

|      | Tutorial   | INTRODUCTION TO FRACTIONAL-W PHASE-LOCKED LOOPS                             | 30 |

| ISSC | C 2006     |                                                                             | 39 |

|      | OVERVIE    | EW                                                                          | 41 |

|      |            | ED PAPERS                                                                   |    |

|      | Special-To | opic Session ANALOG SCALING                                                 | 46 |

|      | Tutorial   | DATA CONVERTERS INTERFACES:                                                 |    |

|      |            | THE ANALOG AND DIGITAL INS AND OUTS                                         | 48 |

|      |            |                                                                             |    |

| ISSC | C 2006     |                                                                             | 49 |

|      | OVERVIE    | EW                                                                          |    |

|      |            | ED PAPERS                                                                   |    |

|      | Panel      | IS THE DIGITAL-CIRCUIT DESIGNER DEAD?                                       |    |

|      | Tutorial   | INTRODUCTION TO STATISTICAL VARIATION                                       |    |

|      | ratorial   | AND TECHNIQUES FOR DESIGN OPTIMIZATION                                      | 64 |

|      | Forum      | MULTICORE ARCHITECTURES, DESIGN,                                            |    |

|      | i orani    | AND IMPLEMENTATION CHALLENGES                                               |    |

|      | Trends     |                                                                             |    |

|      |            |                                                                             |    |

| ISSC | C 2006     | - IMAGERS, MEMS, MEDICAL AND DISPLAY                                        | 69 |

|      |            | EW                                                                          |    |

|      |            | ED PAPERS                                                                   |    |

|      |            | opic Session WHAT IS DRIVING DISPLAYS?                                      |    |

|      |            | opic Session SENSORS ON THE MOVE                                            |    |

|      | Tutorial   | INTRODUCTION TO CMOS BIO SENSORS: ELECTRICAL                                |    |

|      |            | SPECIFICATIONS, CMOS PROCESSING, CIRCUIT AND SYSTEM DESIGN                  |    |

|      | Forum      | COLOR IMAGING                                                               | 84 |

|      | Trends     |                                                                             | 85 |

| ISSCC | 2006 – MEMO          | RY                                              | 89  |

|-------|----------------------|-------------------------------------------------|-----|

| 0     | VERVIEW              |                                                 | 91  |

| F     | EATURED PAPERS.      |                                                 | 92  |

| S     | pecial-Topic Session | EMERGING & DISRUPTIVE MEMORY TECHNOLOGIES       | 98  |

|       | utorial              | MULTI-LEVEL CELL DESIGN FOR FLASH MEMORY        |     |

| F     | orum                 | EMBEDDED-SRAM DESIGN                            | 101 |

| ISSCC | 2006 – SIGNA         |                                                 | 103 |

| 0     | VERVIEW              |                                                 | 105 |

| F     | EATURED PAPERS.      |                                                 | 106 |

| S     | pecial-Topic Session | POWER-AWARE SIGNAL PROCESSING                   | 109 |

| Т     |                      | LLULAR-PHONE APPLICATION;                       |     |

|       | TR                   | ENDS AND DSP TECHNOLOGY                         | 111 |

| ISSCC | 2006 - TECH          |                                                 | 113 |

|       |                      |                                                 |     |

|       |                      |                                                 | 117 |

| S     | pecial-Topic Session | HIGHLIGHTS OF 2005 A-SSCC                       |     |

|       |                      | AND SYMPOSIUM ON VLSI TECHNOLOGY                |     |

|       | utorial              | 3D INTEGRATION                                  |     |

| F     | orum                 | CIRCUIT DESIGN IN EMERGING TECHNOLOGIES         | 128 |

| ISSCC | 2006 – WIREL         | ESS COMMUNICATIONS                              | 129 |

|       |                      |                                                 |     |

|       |                      |                                                 |     |

|       |                      | CMOS RF DESIGN IN 90NM AND BEYOND               |     |

|       |                      |                                                 |     |

| F     | orum GIF             | RAFE Forum: ADVANCED WIRELESS CMOS TRANSCEIVERS | 144 |

|       |                      | INE COMMUNICATIONS                              |     |

|       |                      |                                                 |     |

|       |                      |                                                 | 148 |

| P     |                      | IAT IS NEXT TO BE OFF-SHORED,                   |     |

| -     |                      | C DESIGN JOBS OR IC DESIGN FUTURE ?             |     |

| _     |                      | BNAL INTEGRITY FOR HIGH-SPEED CIRCUIT DESIGNERS |     |

|       |                      | AC: HIGH-SPEED INTERCONNECT                     |     |

| I     | renus                |                                                 | 130 |

| ISSCC | 2006 - PRESS         | S-RELEASE SESSION OVERVIEWS                     | 157 |

|       |                      | BLICATION                                       |     |

|       |                      | S                                               |     |

|       |                      |                                                 |     |

|       |                      |                                                 |     |

|       |                      | BLICATION                                       |     |

|       |                      | ) PAPERS                                        |     |

| Р     | RESS COPY            |                                                 | 197 |

| ISSCC | 2006 – CONT/         |                                                 | 229 |

|       |                      | S                                               |     |

|       |                      | S                                               |     |

|       |                      |                                                 |     |

## ISSCC 2006 EXECUTIVE SUMMARY

- Activities

- Conference Theme

- Significant Results

## **EXECUTIVE SUMMARY**

### **ACTIVITIES AT ISSCC 2006**

#### • <u>Tutorials</u>, presented Sunday, February 5:

- Nine independent lectures presented by experts from each of the ISSCC 2006 Program Subcommittees: Analog & RF; Data Converters; Digital; Imagers, MEMS, Medical and Display; Memory; Signal Processing; Technology Directions; Wireless Communications; Wireline Communications.

- Advanced-Circuit-Design Forums, presented Sunday, February 5 and Thursday, February 9:

- Informal all-day linked interaction in which circuit experts exchange information on their current research.

- Evening Sessions, presented on Monday and Tuesday, February 6 and 8 evenings:

- Seven Special-Topic Sessions

- Three Panel-Discussion Session

- <u>Technical Paper Sessions</u>, presented Monday through Wednesday, February 6 through 8:

- o Three presentations in the Plenary Session on Monday morning

- **33** paper sessions, beginning Monday afternoon and continuing through Wednesday afternoon, including:

**255** regular-length papers

73 short papers

- <u>Social Hour</u> on Monday and Tuesday evenings after the paper sessions:

- o DAC/ISSCC and ASSCC Student-Design-Contest-winners poster session

- Technical-book display

- Short Course, presented Thursday, February 9:

- Four linked 90-minute lectures given by experts in the field

## **CONFERENCE THEME:**

#### "Multimedia for a Mobile World"

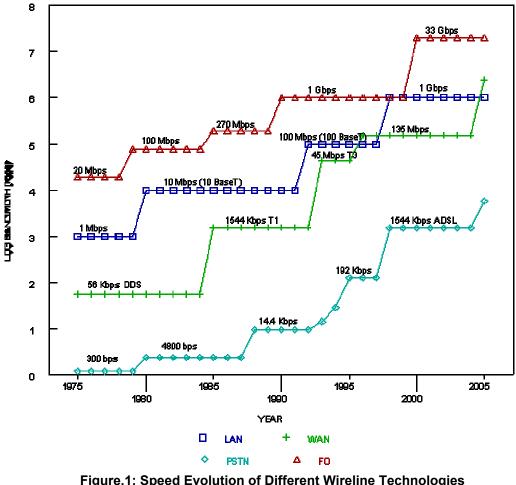

Today, electronic multimedia is an indispensable part of life. Broadband Internet with megabit-per-second capability on copper has replaced the kilobit-per-second modems of the past. Digital music and video, as well as industrial data, run at the speed of light around the globe, for ubiquitous use in new consumer and new professional products and applications. The enablers of this media-revolution have been ever-deeper deep submicron silicon circuits, shrinking to nanometer dimensions, now providing cheaply the gigascale integration of IP in system-on-a-chip multimedia equipment. To mark this major transition, this year's Conference will highlight papers on new circuit techniques and devices supporting this mobile and multimedia tour of triumph for semiconductors.

Advanced semiconductor technology, wireless and broadband interconnection, multimedia applications, and real-time entertainment, are driving the semiconductor business today. But, circuit research is facing new challenges in the deep nanometer regime: CMOS devices with high-leakage gates and low-linearity performance, but with plentiful bandwidth, open new opportunities: Thus, we see converters at 65nm, and even-smaller-featured silicon, along with other devices like carbon nanotubes and large-scale applications of organic materials.

In support of the Conference theme, there are:

#### Plenary Session, with three presentations :

- Where CMOS is Going: Trendy Hype versus Real Technology

- o ICs for Mobile Multimedia Communications

- The Future of Computing For Real-Time Entertainment

#### <u>Technical-paper sessions</u>, amongst which are included:

- 3 sessions describing high-performance high-frequency ADCs and DACs [Sessions 3, 12,31]

- 1 session on new microprocessor developments including single-chip many-multicore processors [Session 5]

- 4 sessions on diverse RF applications [Sessions 6, 11, 17, 25]

- o 3 sessions on DRAM, SRAM and non-volatile memory [Sessions 7, 8, 34]

- 4 sessions on low-power multimedia and mobile TV [Sessions 9, 14, 22, 33]

- o 3 sessions on cellular telephony and WLAN [Sessions 14, 20, 26]

- 1 session on large-scale flexible organic ICs [Session 15]

- o 2 sessions on concerns for power management and distribution [Sessions 24, 29]

#### Evening Sessions, amongst which sample topics include:

- What is Driving Displays? [SE1]

- Power-Aware Signal Processing [SE2]

- Analog Scaling [SE3]

- CMOS RF Design at 90nm and Beyond [SE5]

#### Advanced-Circuit-Design Forums, amongst which sample topics include:

- Wireless CMOS Transceivers [F1]

- Embedded-SRAM Design [F2]

- o Multicore Architectures, Designs, and Implementation Challenges [F6]

#### **Tutorials**, amongst which sample topics include:

- Data Converter: The Analog and Digital Ins and Outs [T2]

- Multi-Level Cell Design for Flash Memory [T5]

- Cellular-Phone Applications Trends and DSP Technology [T6]

- o 3D Integration [T7]

## SIGNIFICANT RESULTS

#### • ANALOG:

- High-efficiency class-D audio power amplifiers reach to new levels of fidelity at 100W+ power levels [19.1, 19.3]

- DC to 2.4 GHz power upconverter employs a multipath mostly-digital technique to cancel unwanted harmonics up to the 17<sup>th</sup>, without filtering [25.1]

- Divider circuit in CMOS operates at frequency beyond 70GHz [32.8]

#### • DATA CONVERTERS:

- Data converters for communication systems move closer to the antenna [3.2, 3.3, 31.7, 31.8]

- Nyquist ADCs achieve sub-pJ/conversion-step power efficiency [12.1, 12.2, 12.3, 12.5, 12.7, 31.3, 31.5, 31.6]

- o 1GS/s ADC with new sampling technique pushes resolution to 11-bits. [31.6]

#### • DIGITAL:

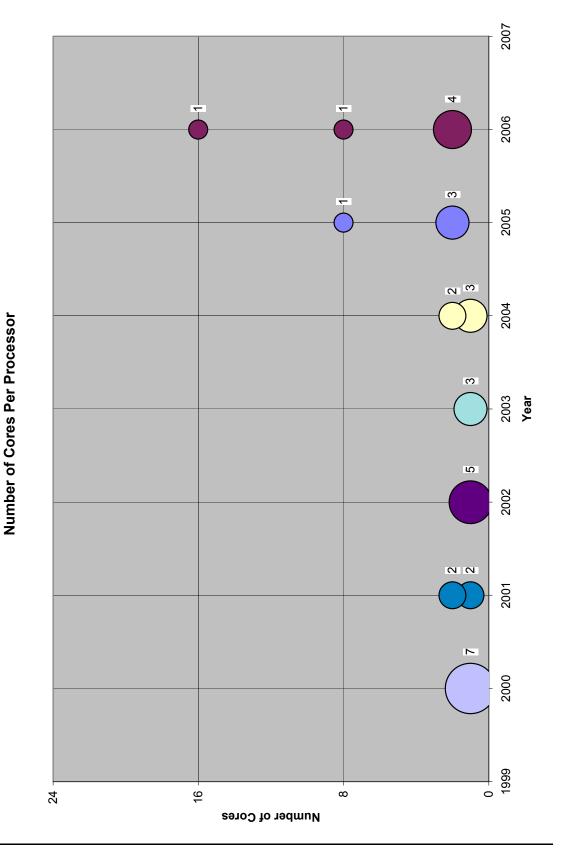

- Single-chip processors with up to 16 cores and 32-threads [5.1, 5.2]

- o 65nm processors and processor components [5.3, 5.7, 24.1, 24.7]

- 1.2Tb/s aggregate bandwidth from a single chip [5.6]

- o 9GHz processor components: 64-bit integer execution unit and register file [5.7,24.7]

- Circuit techniques for improved PVT tolerance [24.7, 24.4, 24.5, 29.6]

#### • IMAGERS, MEMS, MEDICAL AND DISPLAY:

- A 32-site 4-channel cochlear-implant microelectrode array with inductively-coupled wireless link and position-sensing capability. **[2.3]**

- Low-power implantable retinal prostheses include a digitally-programmable stimulation scheme with ESD protection, achieving a data rate of 100 kb/s at 1.3 mW. **[2.4, 2.5]**

- A micromechanical silicon-on-insulator accelerometer with low-noise CMOS, achieves micro-gravity resolution in a wide dynamic range of 95dB to enable inertial navigation at micro-scale [16.1]

- A thermal oscillator in standard CMOS used as a temperature sensor, achieving an accuracy better than ±0.5°C over the industrial temperature range of-40 to 105°C [16.5]

- A 128x128 pixel CMOS image sensor inspired by the human retina images over a wide range of light levels while responding to relative intensity changes in less than 100µs. [27.9]

#### • MEMORY:

- NROM-based flash memory achieves four bits of storage in a single memory cell [7.1]

- Smallest 8Gb multi-level NAND flash memory ever reported [7.7]

- 10MB/s program throughput achieved by a sub-60nm Multi-Level NAND flash memory.

[7.7]

- Powerful 5-bit error-correction scheme embedded into a monolithic Multi-Level NAND flash memory. [7.6]

- 5Ghz SRAM design for high-performance CPU [34.1]

- Thyristor-based volatile memory in nano-scale CMOS [34.6]

#### • SIGNAL PROCESSING:

- First-published DSSS UWB baseband transceiver for wireless ad-hoc networks. [14.5]

- 5mW MPEG4 video encoder and 160Kgate HDTV video decoder provide low-power and low-cost solutions. [22.3, 22.6]

- Vertex processor delivers 120Mvertices/s 3D-geometry performance which is 3x the performance and half the power of previous chips. **[22.4]**

#### • TECHNOLOGY DIRECTIONS:

- First demonstration of functional RFID tags built in organics, operating at 13.56MHz [15.2]

- Electronic "nose" detects spoilage of wine at levels of 10 parts per million [15.3]

- o Development of a Braille sheet allows e-books for the blind that update in 2 seconds [15.4

- Combination of 2.4GHz BAW resonators and 0.18µm CMOS radio front-end achieving 50dB image rejection with 1.8mW power consumption [17.7]

- Demonstrated generation of 1 microwatt of electrical power from a 1 milliCurie of benign Nickel-63 nuclear-energy source. [23.1]

- Demonstrated 1 Terabit per second data transfer between 3D integrated chips via inductive coupling over an area of 2 square millimeters and energy consumption of 3 picoJoules per bit. [23.4]

- Optical clocking of 5-to-10 GHz with a silicon nano-photodiode. [23.5]

- Neuro-interface chips locally process signals captured from 100 electrodes and radiotransmit them outside the body **[30.1, 30.2]**

- Realization of a MEMS-based reusable biosensor for identifying and monitoring cardiovascular-risk biomarkers (that is, C-Reactive proteins) [30.6]

#### • WIRELESS COMMUNICATIONS:

- Fully-integrated UWB transceivers in CMOS [6.4, 6.5]

- A frequency synthesizer covering all the 14 UWB bands in CMOS [6.7]

- A 77GHz phased-array system in silicon [10.1. 10.2]

- A 60GHz transmitter and receiver in silicon [10.3]

- The first single-chip 802.11a/b/g SoC that fully integrates RF front-end, baseband analog, digital baseband, and MAC in one die for embedded applications. **[20.2]**

- o A fully-integrated SoC for GSM/GPRS on 0.13μm CMOS [26.7]

- o RF tuners for all the worldwide mobile TV standards. [33.1 to 33.6]

#### • WIRELINE COMMUNICATIONS:

- o 10Gb/s photonic modulator and WDM Mux/Demux with electronics in 0.13μm SOIC [13.7]

- 25Gb/s CDR in 90nm CMOS for high-density interconnects [18.1]

- 104Gb/s 2<sup>11</sup>-1 and 110Gb/s 2<sup>9</sup>-1 PRBS generator in InP HBT technology [28.10]

# ISSCC 2006 CONFERENCE OVERVIEW

- Events

- Paper Statistics

- Plenary Session

- Technical Highlights

- Discussion Sessions

- Short Course

- Tutorials

- Advanced-Circuit-Design Forums

## **EVENTS**

#### **TUTORIALS** (SUNDAY, FEBRUARY 5, 2006)

• Nine 90-minute Tutorials, each taught two times, by individual circuit experts from the Program Committee, serve to meet attendees' needs for introductory material in circuit specialties.

#### ADVANCED-CIRCUIT-DESIGN FORUMS (SUN, FEB 5, AND THURS, FEB 9, 2006)

• In six circuit-design forums, circuit experts exchange information on their current research in an all-day informal linked-topic environment.

#### TECHNICAL SESSIONS (MON. TO WED., FEBRUARY 6 THROUGH 8, 2006)

• **Three invited talks** presented in the Plenary Session and **255 technical papers** presented in **33** Regular Sessions, highlight the latest circuit developments.

#### EVENING SESSIONS (SUN, MON. & TUES., FEBRUARY 5 THROUGH 7, 2006)

- Seven Special-Topic Presentations, in which multiple experts provide, linked insights and background on a subject of current importance.

- Three Panel Discussions in which experts debate a selected topic and field audience questions in a semi-formal atmosphere.

#### SOCIAL HOURS (MONDAY, FEBRUARY 6, AND TUESDAY, FEBRUARY 7, 2006)

• Opportunities to network with experts in a wide range of circuit specialties; to meet colleagues in an informal exchange; to view the Poster Session (see below); to browse the technical-book exhibits!

**POSTER SESSION** (MONDAY, FEBRUARY 6, AND TUESDAY, FEBRUARY 7, 2006)

• DAC/ISSCC and ASSCC Student-Design-Contest winners will provide poster presentations during the Social Hours.

#### SHORT COURSE (THURSDAY, FEBRUARY 9, 2006)

• Intensive all-day course on a single topic, taught by world-class instructors, can serve to "jump start" a change in an engineer's circuit specialty.

## PAPER STATISTICS

## OVERALL:

- **3** papers invited

- 680 papers submitted to ISSCC 2006

- **255** papers accepted, including:

- **119** papers from North America, including:

- 65 Industry papers

- **54** University papers

- **81** papers from the Far East, including:

- 47 Industry papers

- **34** University papers

- **55** papers from Europe, including:

- 26 Industry papers

- 29 University papers

- 34 Sessions, over 3 days

## **INTERNATIONAL SCOPE:**

| • | Americas: | 47% |

|---|-----------|-----|

| • | Far East: | 32% |

| • | Europe:   | 22% |

|   | <b>TECHNICAL COVERAGE:</b>       | <u>2006</u> | <u>2005</u> | <u>2004</u> |

|---|----------------------------------|-------------|-------------|-------------|

| • | Analog & RF                      | 13%         | 13%         | 13%         |

| • | Data Converters                  | 10%         | -           | -           |

| • | Digital                          | 11%         | 11%         | 12%         |

| • | Imagers, MEMS, Medical & Display | 11%         | 11%         | 9%          |

| • | Memory                           | 7%          | 10%         | 11%         |

| • | Signal Processing                | 7%          | 9%          | 9%          |

| • | Technology Directions            | 11%         | 12%         | 11%         |

| • | Wireless Communications          | 15%         | 18%         | 16%         |

| • | Wireline Communications          | 14%         | 16%         | 15%         |

## PLENARY SESSION

# [1.1] WHERE IS CMOS GOING: TRENDY HYPE VERSUS REAL TECHNOLOGY

#### **TZE-CHIANG (T.C.) CHEN**

IBM Fellow, VP of Science and Technology, T.J. Watson Research Center, Yorktown Heights, NY

- CMOS approach toward atomistic and quantum-mechanical boundaries has motivated industry pundits to profile Nanotechnology, Bio-electronics, or Quantum Computing as urgently-needed CMOS replacements.

- New materials, coupled with effective circuit design and architecture practices ensure at least another 10 years of CMOS service.

- Power dissipation and variability emerge as first-order concerns which must be addressed effectively in design.

- Stochastic threshold variation caused by dopant implant variation in ultra-small inversion regions will give rise to 3-digit threshold variation by the 25-nm generation in excess of 100mV threshold variation. At the architecture level, initiatives such as self-healing systems, self-biasing substrates, and simultaneous circuit and device diagnostics will extend a circuit's ability to survive and function given a wider range of sensitivities.

- The development of silicon technology has been, and will remain, driven by system needs.

#### [1.2] ICS FOR MOBILE MULTIMEDIA COMMUNICATIONS

#### Hermann Eul,

Member of the Management Board, Infineon Technologies, Munich, Germany

- At the current growth rate, the number of worldwide subscribers of cellular services is expected to exceed 1.5 billion by 2007. In 2004, 700 million mobile handsets were produced.

- High data-rates such as 7.2 Mb/s HSDPA and corresponding mobility trade-offs, along with different standards like 2G, 3G, Bluetooth, WLAN, GPS, UWB and digital video broadcasting, are leading to multimode requirements. Correspondingly, topics such as coexistence of different technologies must be solved. Beyond all of that, secure data transfer using technologies such as encryption is most important for the networked world.

- Parameters such as data-rate and algorithmic circuit complexity have changed exponentially with time, but there was not been, much improvement in battery capacity. For this reason, a key consideration for mobile products is energy management and power reduction.

- Wafer processes with low leakage and improved analog and RF capabilities are required to achieve the performance targets for ICs.

- Platform concepts, including analog and RF, to provide the most-practical costs powerlevels and form-factors, are key requirements for system-on-chip and system-in-package solutions for current and future mobile multimedia terminals.

#### [1.3] THE FUTURE OF COMPUTING FOR REAL-TIME ENTERTAINMENT

#### Ken Kutaragi,

President and CEO, SONY Computer Entertainment, Tokyo, Japan

- There are two elements in real-timeliness that a human being can intuitively sense. One is the continuity of motion that a human being can cognitively feel to be natural, and the other is response time between action and reaction.

- Lack of both processing power and data-transfer rate using general-purpose microprocessors in achieving this level of real-timeliness has motivated the development of a new breed of more-powerful processors built on a new architecture.

- Today, more than 40 million computer entertainment systems are shipped in a year, and are becoming a leading power in spearheading advancements in semiconductor technology, and in creating demand.

- In the future of real-time computing, massively "Parallel Computing Over the Network" to execute vast amounts of computation, and "Vision Systems" that recognize the real world in real-time from a vast number of sensors over the Network, will lead the next era in real-time computing.

## **TECHNICAL HIGHLIGHTS**

#### • ANALOG:

- RF preamplifier with lower noise figure, higher gain and smaller silicon area [11.5]

- High-efficiency Class-D Audio Power Amplifiers push to new levels of fidelity at 100W+ power levels [19.1, 19.3]

- Fully-integrated synchronous DC-to-DC converter with on-chip LC filter in 0.18µm SiGe technology [19.7]

- DC-to-2.4 GHz power upconverter employing a multipath mostly-digital technique to cancel unwanted harmonics up to the 17<sup>th</sup>, without filtering [25.1]

- New techniques for handling leakage currents in PLLs [32.5]

- Divider circuit in CMOS pushes operating frequency beyond 70GHz [32.8]

#### • DATA CONVERTERS:

- High-bandwidth Delta-Sigma ADCs increase dynamic range [3.1, 3.2]

- Data converters for communication systems move closer to the antenna [3.2, 3.3, 31.7, 31.8]

- Nyquist ADCs achieve sub-pJ/conversion-step power efficiency [12.1, 12.2, 12.3, 12.5, 12.7, 31.3, 31.5, 31.6]

- Advances in power-reduction and improved converter efficiency [12.1, 12.2, 12.3, 12.5, 12.7, 31.1, 31.5, 31.6]

- Offset-reduction techniques enable low-power and high-speed Nyquist ADCs [12.3, 12.5, 12.6, 31.1, 31.2, 31.3]

- o 1GS/s ADC with new sampling technique pushes resolution to 11-bits. [31.6]

#### • DIGITAL:

- Single-chip processors with up to 16 cores and 32-threads [5.1, 5.2]

- o 65nm processors and processor components **[5.3, 5.7, 24.1, 24.7]**

- o 1.2Tb/s aggregate bandwidth from a single chip [5.6]

- 9GHz processor components: 64-bit integer execution unit and register file [5.7,24.7]

- Next-generation research on clocking: low skew/jitter resonant techniques [21.1, 21.4, 21.5, 21.6]

©COPYRIGHT 2005 ISSCC-DO NOT REPRODUCE WITHOUT PERMISSION

## TECHNICAL HIGHLIGHTS (CONTINUED)

- o Advanced adder designs: 64-bit adders 4 to 6 fanout-of-4 (FO4) delay [24.2, 24.3]

- Circuit techniques for improved PVT tolerance [24.7, 24.4, 24.5, 29.6]

- Real-time high-spatial-resolution power monitoring of modern processor chips [29.2]

- Single chip with power management for 20 power domains [29.4, 29.5]

#### • IMAGERS, MEMS, MEDICAL AND DISPLAY:

- A 32-site 4-channel cochlear-implant microelectrode array with inductively-coupled wireless link and position-sensing capability. **[2.3]**

- Low-power implantable retinal prostheses include a digitally-programmable stimulation scheme with ESD protection, achieving a data rate of 100kb/s at 1.3mW. **[2.4, 2.5]**

- $\circ~$  A current-mode 6-bit AMOLED driver using the current-copier technique, achieving 2% accuracy at currents in the 10  $\mu$ A to 10 nA range. **[9.2]**

- A micromechanical silicon-on-insulator accelerometer with low-noise CMOS, achieves micro-gravity resolution in a wide dynamic range of 95dB to enable inertial navigation at micro-scale [16.1]

- $\circ~$  A thermal oscillator in standard CMOS used as a temperature sensor, achieving an accuracy better than  $\pm0.5^\circ\text{C}$  over the industrial temperature range of-40 to 105°C **[16.5]**

- A 1/1.8-inch 6.4M pixel CMOS image sensor for digital still cameras, achieving 60frames/s with photographic performance. **[27.1]**

- A 128x128 pixel CMOS image sensor inspired by the human retina images over a wide range of light levels while responding to relative intensity changes in less than 100µs. [27.9]

#### • MEMORY:

- NROM-based flash memory achieves four bits of storage in a single memory cell [7.1]

- Smallest 8Gb multi-level NAND flash memory ever reported [7.7]

- 10MB/s program throughput achieved by a sub-60nm multi-level NAND flash memory. **[7.7]**

- Powerful 5-bit error-correction scheme embedded into a monolithic multi-level NAND flash memory. [7.6]

- An 8Gb/s deca-data-rate SDRAM incorporates CRC I/O error-detection [8.1]

- A range-matching TCAM with 2.5x data-storage efficiency [8.6]

- 5Ghz SRAM design for high-performance CPU [34.1]

- Thyristor-based volatile memory in nano-scale CMOS [34.6]

## TECHNICAL HIGHLIGHTS (CONTINUED)

#### • SIGNAL PROCESSING:

- First-published DSSS UWB baseband transceiver for wireless ad-hoc networks. [14.5]

- 5mW MPEG4 video encoder and 160Kgate HDTV video decoder provide low-power and low-cost solutions. [22.3, 22.6]

- Vertex processor delivers 120Mvertices/s 3D-geometry performance which is 3x the performance and half the power of previous chips. **[22.4]**

#### • TECHNOLOGY DIRECTIONS:

- First demonstration of functional RFID tags built in organics, operating at 13.56MHz [15.2]

- Electronic "nose" detects spoilage of wine at levels of 10 parts per million [15.3]

- o Development of a Braille sheet allows e-books for the blind that update in 2 seconds [15.4]

- o 71,000 TFT devices integrated on plastic realize cryptographic security RFID [15.6]

- 0.15mm x 0.15mm RFID chip with 128-bit ROM and antenna contacts on top and bottom.

[17.1]

- o 3.4Mb/s data rate in a 13.56MHz RFID front-end [17.2]

- o 50-to-75 GHz 0.13µm CMOS LNA achieves > 20dB gain [17.8]

- Combination of 2.4 GHz BAW resonators and 0.18µm CMOS radio front-end achieving 50 dB image rejection with 1.8mW power consumption [17.7]

- Demonstrated generation of 1 microwatt of electrical power from a 1 milliCurie of benign Nickel-63 nuclear-energy source. [23.1]

- First experimental comparison of comprehensive building blocks in FinFET and Triple-Gate transistor technologies. **[23.2]**

- Demonstrated 1 Terabit-per-second data transfer between 3D integrated chips via inductive coupling over an area of 2 square millimeters and energy consumption of 3 picoJoules per bit. [23.4]

- Optical clocking at 5-to-10 GHz with a silicon nano-photodiode. [23.5]

- Neuro-interface chips locally process signals captured from 100 electrodes and radiotransmit them outside the body [30.1, 30.2]

- Realization of a MEMS-based reusable biosensor for identifying and monitoring cardiovascular-risk biomarkers (that is, C-Reactive proteins) [30.6]

## TECHNICAL HIGHLIGHTS (CONTINUED)

#### • WIRELESS COMMUNICATIONS:

- Fully-integrated UWB transceivers in CMOS [6.4, 6.5]

- A frequency synthesizer covering all the 14 UWB bands in CMOS [6.7]

- A 77GHz phased-array system in silicon [10.1. 10.2]

- A 60GHz transmitter and receiver in silicon [10.3]

- The first single-chip 802.11a/b/g SoC that fully integrates RF front-end, baseband analog, digital baseband, and MAC in one die for embedded applications. **[20.2]**

- A highly-integrated SoC for low-power ZigBee applications, which includes the radio and the PHY layers. **[20.6]**

- A fully-integrated SoC for GSM/GPRS on 0.13μm CMOS [26.7]

- A 1.9GHz single-chip CMOS PHS cellphone [26.8]

- RF tuners for all the worldwide mobile TV standards. [33.1 to 33.6]

#### • WIRELINE COMMUNICATIONS:

- o 10Gb/s 5-tap DFE / 4-Tap FFE transceivers in 90nm CMOS [4.1]

- o 12.5Gb/s single-chip transceiver for UTP Cable in 0.13μm CMOS [4.4]

- ο 9.95-to-11.1Gb/s XFP Transceiver in 0.13μm CMOS [13.1]

- o 10Gb/s photonic modulator and WDM Mux/Demux with electronics in 0.13μm SOI [13.7]

- o 10Gb/s burst-mode adaptive gain-select limiting amplifier in 0.13μm CMOS [13.9]

- o 25Gb/s CDR in 90nm CMOS for high-density interconnects [18.1]

- o Data recovery and retiming for 4.8Gb/s fully-buffered DIMM serial links [18.6]

- 104Gb/s 2<sup>11</sup>-1 and 110Gb/s 2<sup>9</sup>-1 PRBS Generator in InP HBT technology **[28.10]**

## **EVENING SESSIONS**

There are ten Evening Sessions in all, three on each of Sunday and Tuesday evenings and four on Monday evening. Of these, there are seven Special-Topic Sessions, providing insight and background in a topical area.

#### SUNDAY

- **SE1** What is Driving Displays?

- **SE2** Power-Aware Signal Processing

- SE3 Analog Scaling

#### MONDAY

- **E1** Is the Digital-Circuit Designer Dead?

- **SE4** Emerging & Disruptive Memory Technologies

- SE5 CMOS RF Design at 90nm and Beyond

- SE6 Highlights of A-SSCC 2005 and the 2005 Symposium on VLSI Technology

#### TUESDAY

- E2 Present (and Future) Classic Circuits with Less than 25 Transistors

- E3 What is Next to be Off-Shored, IC Design Jobs or IC Design Futures?

- **SE7** Sensors on the Move

## SHORT COURSE:

Thursday, February 9, 2006

## ANALOG-TO-DIGITAL CONVERTERS

#### COURSE OBJECTIVE:

This Short Course is intended to provide both entry-level and experienced engineers with practical approaches to the design of analog-to-digital converters. The course provides an overall perspective on the technology considerations, circuit-design issues, and detailed design strategies, for circuit building blocks in analog-to-digital converters. Topics covered address the challenges faced by analog designers in current and future technologies, with an emphasis on detailed circuit-design approaches, and methodologies for deep-submicron integration.

#### **OVERVIEW**:

- Fundamental Limits and Practical Design Issues in A/D Converters

Hae-Seung Lee, Massachusetts Institute of Technology

- Pipelined A/D Converters

Bang-Sup Song, University of California, San Diego

• ΔΣ ADCs

Richard Schreier, Analog Devices

Sub-1V Analog-to-Digital Converters

Un-Ku Moon, Oregon State University

#### **TUTORIALS:** Sunday, February 5, 2006

- T1 INTRODUCTION TO FRACTIONAL-N PHASE-LOCKED LOOPS Ian Galton, University of California, San Diego

- T2 DATA-CONVERTER INTERFACES: THE ANALOG AND DIGITAL INS AND OUTS David Robertson, Analog Devices

- T3 INTRODUCTION TO STATISTICAL VARIATION AND TECHNIQUES FOR DESIGN OPTIMIZATION Norman Rohrer, IBM

- T4 INTRODUCTION TO CMOS BIO-SENSORS: ELECTRICAL SPECIFICATIONS, CMOS PROCESSING, CIRCUIT AND SYSTEM DESIGN Roland Thewes, Infineon

- T5 MULTI-LEVEL CELL DESIGN FOR FLASH MEMORY Mark Bauer, Intel

- T6 CELLULAR-PHONE APPLICATIONS TRENDS AND DSP TECHNOLOGY Masafumi Takahashi, Toshiba

- T7 3D INTEGRATION Kerry Bernstein, IBM

- **T8** MILLIMETER-WAVE ICS IN SILICON **Ali Hajimiri**, California Institute of Technology

- **T9** SIGNAL INTEGRITY FOR HIGH-SPEED CIRCUIT DESIGNERS **Hong-June Park**, *Pohang University of Science and Technology (POSTECH)*

Sunday, February 5, 2006

#### F1 ADVANCED WIRELESS CMOS TRANSCEIVERS

- Introduction

**Rudolf Koch**, Infineon

- Cellular and Short-Range Standards, Key Challenges, and their Impact on Architecture

Chris Rudell, Intel

- Highly-Integrated Linear Transmitters

Tony Montalvo, Analog Devices

- Receivers for Traditional, MIMO, and Dynamic Bandwidth Radio Systems

Bill McFarland, Atheros

- System Design for Multi-Standard Radios

Aarno Pärssinen, Nokia

- Transceiver Integration into a Single-Chip Cellular Phone Andre Hanke, Infineon

- Digital RF Processor (DRP) for Cellular Phones Bogdan Staszewski, Texas Instruments,

- Software-Defined Radio

Asad Abidi, University of California, Los Angeles

#### F2 EMBEDDED-SRAM DESIGN

- Introduction

Don Weiss, Intel

- High-Performance Power-Aware SRAM Design

Kevin Zhang, Intel

- Low-Power Low-Voltage SRAM Design for Battery Operation

Masanao Yamaoka, *Hitachi*

- Design for Testability (DFT)

**R. Dean Adams**, *Magma Design Automation*

- Stability/Reliability/Manufacturability Factors in SRAM Design

Takayuki Kawahara, *Hitachi*

- Alternatives to 6T SRAM

Hyun-Geun Byun, Samsung

Sunday, February 5, 2006

#### F3 CIRCUIT DESIGN IN EMERGING TECHNOLOGIES

- Introduction

Eugenio Cantatore, Philips

- Regular Fabrics for Nano-Scaled CMOS Technologies

Larry Pileggi, Carnegie Mellon University

- Multigate MOSFET Design

Gerhard Knoblinger, Infineon

- Design with Organic TFTs

Eugenio Cantatore, Philips

- Technology Trends and Design with Silicon TFTs

Tatsuya Shimoda, Seiko-Epson

- Digital Circuits Using Carbon Nanotubes: Modeling, Design, and Architectures

Ali Keshavarzi, Intel

- Analog-Circuit Design with 1D Electronic Devices

Donhee Ham and Xiaofeng Li, Harvard University

- Spintronics: Past, Present, and Future

Stuart Parkin, IBM

Thursday, February 9, 2006

#### F4 COLOR IMAGING

- Introduction

Albert Theuwissen, DALSA

- Human Vision System

Brian Wandell, Stanford University

- Capturing Color Images

**Tetsuya Kuno,** *Mitsubishi*

- Color-Filter Technology

Katsumi Yamamoto, Toppan SMIC

- Color Matrixing

Gennady Agranov, Micron

- Color Interpolation

**Takashi Saito**, *Kanagawa University*

- White Balancing

Massimo Mancuso, ST Microelectronics

- Color Coding

Charles Poynton, ATI

Thursday, February 9, 2006

#### F5 ATAC: HIGH-SPEED INTERCONNECT

- Introduction

Wolfgang Pribyl, austriamicrosystems & CONPRI

- High-Speed Interconnect Techniques, Standards and Application Areas

Yuriy Greshishchev, PMC Sierra

- Implementing Chip- and Board-Level Protocols on Programmable Platforms

Christian Sauer, Infineon

- The Evolution of High-Speed Interfaces into Memory Applications

Antony Sanders, Infineon

- Receiver Decision-Feedback Equalization for Multi-Gigabit Server Links

**Evelina Yeung**, Intel

- Tradeoffs of Receive and Transmit Equalization Architectures in 10 to 20Gb/s I/O Systems

Bryan Casper, Intel

- A Study of FFE/DFE Performance for Application to 10Gb/s 802.3ap Ethernet over Backplane Channels Troy Beukema, IBM

- Multi-Gigabit Signaling Over UTP Cables

Scott Powell, Broadcom

- Silicon Photonics in High-Speed Interconnects Overview, Results, and Future Perspectives

Mario Paniccia, Intel

Thursday, February 9, 2006

#### F6 MULTI-CORE ARCHITECTURES, DESIGNS, AND IMPLEMENTATION CHALLENGES

- Introduction

**Peter Kogge**, University of Notre Dame,

- An Introduction to Multicore Chip Design

**Peter Kogge**, *University of Notre Dame*

- Niagara: Architecture and Physical Design of a 32-Threaded General-Purpose CPU

James Laudon, Sun Microsystems

- The Cell Processor's Multicore Architecture: Impact and Influence of Physical Design

James Kahle, IBM

- Low-Power Multicore Chips for Mobile Embedded Applications

Satoshi Matsushita, NEC

- Challenges of Multicore Processors for Embedded Infrastructure Requiring High-Bandwidth I/O, Memory Interfaces, and On-Chip Accelerators

Dan Bouvier, Freescale Semiconductor

- Circuit Technologies for Multicore Processor Design

Stefan Rusu, Intel

- Multicore-SoC Test and Yield Enhancement– Challenges and Advancements in a Complex Environment

Juan Rosal, Texas Instruments

- How Does Future Technology Scaling Affect a Multicore World?

Panel Discussion

# ANALOG & RF

- Overview

- Featured Papers

- Panel

- Tutorial

## **ISSCC 2006 – ANALOG & RF**

Subcommittee Chair: John R. Long, Delft University of Technology, The Netherlands

## **OVERVIEW**

#### **MOST-SIGNIFICANT RESULTS**

- RF preamplifier with lower noise figure, higher gain and smaller silicon area [11.5]

- High-Efficiency Class-D Audio Power Amplifiers push to new levels of fidelity at 100W+ power levels [19.1, 19.3]

- Fully-integrated synchronous DC to DC converter with on-chip LC filter in 0.18µm SiGe technology [19.7]

- DC to 2.4 GHz power upconverter employing a multipath mostly-digital technique to cancel unwanted harmonics up to the 17<sup>th</sup>, without filtering **[25.1]**

- New techniques for handling leakage currents in PLLs [32.5]

- Divider circuit in CMOS pushes operating frequency beyond 70GHz [32.8]

#### **APPLICATIONS AND ECONOMIC IMPACT**

- Wireless handheld devices with improved RX and TX efficiency to extend battery life and enable larger feature set [11.5]

- High-efficiency audio power amplifiers drive down the cost and size of home theater and automotive-entertainment systems [19.1, 19.3]

- Fully-integrated converter enables complete SoC solution for low-cost production [19.7]

- Digital correction techniques are simple and cost-effective ways to improve quality of analog signals in highly-integrated receiver ICs [25.1]

- Leakage-control technique opens up the design of PLLs in deep-submicron CMOS [32.5]

- CMOS at 70GHz leads to lower costs for millimeter-wave applications [32.8]

#### PANEL

Present (and Future) Classic Circuits with Less Than 25 Transistors [EP2]

#### TUTORIAL

Introduction to Fractional-N Phase-Locked Loops [T1]

# Art of RF Design

# A 5GHz Resistive-Feedback CMOS LNA for Low-Cost Multi-Standard Applications [11.5]

Intel

#### PRESENT STATE OF THE ART (THE PROBLEM)

• Need for wider tuning range, faster settling time, and lower power consumption, for mobile multi-standard radio

#### NOVEL CONTRIBUTIONS

• Inductorless LNA at 5Ghz occupies small silicon area [11.5]

#### CURRENT AND PROJECTED SIGNIFICANCE

• Highly-efficient and small-area circuits enable feature-packed wireless handheld devices [11.5]

# 200W+ Monolithic Class-D Audio PA Stage

# A 240W Monolithic Class-D Audio-Amplifier Output Stage [19.1]

Texas Instruments; *ø*rsted\*DTU

# **PRESENT STATE OF THE ART** (THE PROBLEM)

- High-power Class-D output stages typically suffer from high levels of distortion

- High levels of distortion necessitate complicated feedback structures

## NOVEL CONTRIBUTIONS

- An output switching stage with 0.1% THD at power levels up to 240W [19.1]

- Power amplifier operates "open-loop" in audio amplifiers, reducing complexity of the highest-fidelity applications **[19.1]**

- This optimization approach minimizes distortion caused by output-switch "dead-time" [19.1]

- Lowers cost and size of amplifiers for home theater and automotive-entertainment systems [19.1]

# Highest-Fidelity Class-D Audio Controller

# A Digital Input Controller for Audio Class-D Amplifiers with 100W 0.004% THD+N and 113dB DR [19.3]

Texas Instruments

# **PRESENT STATE OF THE ART** (THE PROBLEM)

• Available approaches have been analog with high distortion levels that require external DACs

## **NOVEL CONTRIBUTIONS**

- The controller accepts a digital-audio input and performs digital-to-analog conversion internal to the IC, while providing a novel analog-feedback architecture to correct distortion produced by the power stage. **[19.3]**

- The controller in concert with a suitable power stage achieves 0.004% distortion at the 100W output level. **[19.3]**

- Lower cost and size of amplifiers for home theater and automotive-entertainment systems [19.3]

- Development of a robust feedback architecture opens the door to high-fidelity audio at a very low cost **[19.3]**

# Integration of LC filter in a DC-DC converter in SiGe technology

# A Multi-Stage Interleaved Synchronous Buck Converter with Integrated Output Filter in a 0.18µm SiGe Process

[19.7]

Freescale Semiconductor; Arizona State University

## **PRESENT STATE OF THE ART** (THE PROBLEM)

- Large filter-inductor and capacitor size makes full integration impossible

- External filter increases the number of I/O pads and PCB interconnects which introduces system noise, delay and power loss

## NOVEL CONTRIBUTIONS

- High switching frequency, multiphase interleaved operation, and fast hysteretic control reduce the filter inductor and capacitor sizes enabling a fully-integrated converter **[19.7]**

- Utilizes a 10µm-thick electroplated copper layer to improve integrated inductor and gatecapacitor performance **[19.7]**

- Reduces board-level circuit complexity and provides a low-cost product [19.7]

- Decreases the size and weight of handheld devices through miniaturization of the power modules **[19.7]**

# **RF/IF CIRCUITS**

# A Multipath Technique for Cancelling Harmonics and Sidebands in a Wideband Power Upconverter [25.1]

University of Twente

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

• Complex analog techniques are not easily scalable to deep-submicron technologies

#### NOVEL CONTRIBUTIONS

• The polyphase multipath technique allows digital wideband and frequency up-conversion without a filter **[25.1]**

#### CURRENT AND PROJECTED SIGNIFICANCE

• A step forward to highly-reconfigurable and adaptive radio [25.1]

# PLLs, VCOs, and Dividers

#### A 6.25GHz 1V LC-PLL in 0.13µm CMOS [32.5]

Texas Instruments

#### 70GHz CMOS Harmonic-Injection-Locked Divider [32.8]

University of Tokyo

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

- Charge-pump leakage current in deep submicron processes increases jitter in PLLs

- Limited locking range in high-frequency dividers

#### NOVEL CONTRIBUTIONS

- Improved state-of-the-art in the charge pumps for PLLs [32.5]

- Record operating frequency with twice the locking range compared to the current state-of-theart **[32.8]**

- Enables very-low-voltage low-timing-jitter PLL operation [32.5]

- Step forward for millimeter-wave transceivers in CMOS [32.8]

# Panel

# Present (and Future) Classic Circuits with Less Than 25 Transistors

Organizer: **JoAnn Close**, Analog Devices Moderator: **Bill Redman-White**, Philips Semiconductors and Southampton University

#### OBJECTIVE

- To illustrate, with specific examples from the last twenty years, key innovations in "small" circuit design.

- To highlight the attributes of a "classic" circuit.

- To identify the pressures that keep circuit innovation going.

#### CHALLENGE

- What are the big drivers of innovation in the field of transistor-level design?

- o Demands of higher performance?

- o Meeting demands of new application areas?

- o Demands of shrinking CMOS technologies?

#### CONTROVERSY

- Have there been recent significant advances in the field of transistor-level circuit design? Have all the really-good small circuits already been invented?

- What makes a circuit a classic? Is it elegance of design? Is it everyday usefulness? Is it portability among processes and application areas?

- Can we guess which circuits will be classics in the future? Will the requirements be different for future classics?

#### PANEL DESCRIPTION:

Some circuits are easily forgotten like cheap wines, but others are instantly classic vintage. These are the sound choices of the past and present, and will be brought to the table for years to come. We ask some connoisseurs for their pick of circuits with fewer than 25 transistors from the last 20 years which best illustrate undiminished creativity in the field of transistor-level design.

Moderator:

Bill Redman-White, Philips Semiconductors and Southampton University, United Kingdom

Panelists:

Klaas Bult, Broadcom, The Netherlands Bob Dobkin, Linear Technology, CA Barrie Gilbert, Analog Devices, OR Tom Lee, Stanford University, CA, USA Takahiro Miki, Renesas Technology, Japan Yannis Tsividis, Columbia University, NY

# Tutorial

# INTRODUCTION TO FRACTIONAL-N PHASE-LOCKED LOOPS

Ian Galton, University of California at San Diego, CA

#### **OVERVIEW**

This tutorial begins with a brief review of integer-N PLLs, and then, presents a detailed explanation of the additional ideas and issues associated with the extension to fractional-N PLLs for frequency synthesis. Topics include a self-contained explanation of the relevant aspects of  $\Delta\Sigma$  modulation, an extension of the well-known integer-N PLL linearized model to fractional-N PLLs, the non-ideal effects of particular concern in fractional-N PLLs such as charge-pump nonlinearities and data-dependent divider delays, and techniques for wideband in-loop digital modulation of the VCO. Case studies of example circuits and applications are presented to illustrate the main concepts.

#### SPEAKER BIOGRAPHY

Ian Galton received his Sc.B. from Brown University, in 1984, and his M.S. and Ph.D. from the California Institute of Technology, in 1989 and 1992, respectively, all in electrical engineering. Since 1996, he has been a professor of electrical engineering at the University of California, San Diego, where he teaches and conducts research in the field of mixed-signal integrated circuits and systems for communications. Prior to 1996, he was with UC Irvine, the NASA Jet Propulsion Laboratory, Acuson, and Mead Data Central. His research involves the invention, analysis, and integrated-circuit implementation of critical communication-system building blocks, such as data converters, frequency synthesizers, and clock- recovery systems. In addition to his academic research, he regularly consults at several semiconductor companies, and teaches industry-oriented short courses on the design of mixed-signal integrated circuits. He has served as a member of a corporate Board of Directors, as a member of several corporate Technical Advisory Boards, and as the Editor-in-Chief of the IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing.

# **DATA CONVERTERS**

- Overview

- Featured Papers

- Special-Topic Session

- Tutorial

- Short Course

# **ISSCC 2006 – Data Converters**

Subcommittee Chair: David Robinson, Analog Devices, Wilmington, MA

# **OVERVIEW**

#### **MOST-SIGNIFICANT RESULTS**

- High-bandwidth Sigma-Delta ADCs increase dynamic range [3.1, 3.2]

- Data Converters for communication systems move closer to the antenna [3.2, 3.3, 31.7, 31.8]

- Nyquist ADCs achieve sub-pJ/conversion step power efficiency [12.1, 12.2, 12.3, 12.5, 12.7, 31.3, 31.5, 31.6]

- Strong emphasis on power-reduction and improved converter efficiency [12.1, 12.2, 12.3, 12.5, 12.7, 31.1, 31.5, 31.6]

- Offset-reduction techniques enable low-power and high-speed Nyquist ADCs [12.3, 12.5, 12.6, 31.1, 31.2, 31.3]

- 1GS/s ADC with new sampling technique pushes resolution to 11-bits. [31.6]

#### **APPLICATIONS AND ECONOMIC IMPACT**

- ADCs that can support higher input frequencies, and DACs that can synthesize higher output frequencies [3.2, 3.3, 31.7, 31.8]

- Wider bandwidths are required in data converters to support newer communications standards, including ADSL 2+, 3G, WLAN, and UWB. **[3.4, 3.5]**

- Lower power is critical for battery-powered portable applications, from cell phones to mobile TVs: Sometimes, power efficiency is improved by moving to more-advanced processes, but in many cases, it is realized through circuit innovation. **[12.1, 12.2, 12.3, 12.5, 12.7, 31.1, 31.5, 31.6]**

#### **SPECIAL-TOPIC SESSION**

Analog Scaling [SE3]

#### **TUTORIAL**

Data-Converter Interfaces: The Analog and Digital Ins and Outs [T2]

#### **Short Course**

This year's short course is on data-conversion techniques (refer to the Short-Course section of the Press Kit, page 20)

# Oversampling ADCs Push Dynamic Range at Higher Bandwidths

# A 14b 20mW 640MHz CMOS CT $\Delta\Sigma$ ADC with 20MHz Signal Bandwidth and 12b ENOB [3.1]

Xignal Technologies

# A 375mW Quadrature Bandpass $\Delta\Sigma$ ADC with 90dB DR and 8.5MHz BW at 44MHz [3.2]

Analog Devices

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

• Delta-Sigma converters are known to be very power-efficient. However, due to the required oversampling, they have typically been used on lower-frequency signals (audio, for example). Over the past few years, Delta-Sigma techniques are increasingly being applied to higher-frequency signals, offering a whole new set of challenges.

#### NOVEL CONTRIBUTIONS

- One way to push the bandwidth up is to run at high clock rates, but this had traditionally implied very-high power consumption, but newer techniques (and fine-line CMOS processes) allow high sample rate converters to deliver good power efficiency. **[3.1, 3.4, 3.5]**

- Bandpass Delta-Sigma ADCs are pushing to the IF frequencies of consumer RF applications, including Radio and Television [3.2, 3.3]

- Delta-Sigma topologies can provide increased dynamic range, allowing large (and expensive) analog filters to be moved into the digital domain. [3.1,3.2]

- Improving power efficiencies allow for longer-battery-life and smaller-form-factor in portable systems. [3.1]

# Data Conversion at ISSCC 2006: It's all about Power Efficiency

A 90nm CMOS 1.2V 10b Power and Speed-Programmable Pipelined ADC with 0.5pJ/Conversion-Step [12.1]

Philips

A 10b 50MS/s Pipeline ADC with Opamp-Current Reuse [12.2] University of California, San Diego; Conexant

# A 30mW 12b 40MS/s Subranging ADC with a High-Gain Offset-Canceling Positive-Feedback Amplifier in 90nm Digital CMOS [12.3]

Sony

# A 25 µW 100kS/s 12b ADC for Wireless Micro-Sensor Applications [12.5]

Massachusetts Institute of Technology

# A 0.16pJ/Conversion-Step 2.5mW 1.25GS/s 4b ADC in a 90nm Digital CMOS Process [31.1]

IMEC

A 6b 600MS/s 5.3mW Asynchronous ADC in 0.13µm CMOS [31.5] University of California, Berkeley

#### A 1GS/s 11b ADC Time-Interleaved ADC in 0.13µm CMOS [31.6] Teranetics

#### PRESENT STATE OF THE ART (THE PROBLEM)

- Power Efficiency of High-Speed ADCs is limited to about 1pJ/Conversion-step

- Offset Reduction Techniques primarily used for increasing the resolution

#### **NOVEL CONTRIBUTIONS**

- Offset Cancelation is used to reduce power consumption and increase speed [12.3, 12.5, 31.1]

- Offset Calibration by digital means is used to reduce power consumption [12.6, 31.2]

- Redundancy is used to select the lowest offset and reduce power consumption [31.3]

- Power saving enables higher levels of integration

- Power saving enables longer battery-life

- Power saving reduces size and weight

#### **SPECIAL-TOPIC SESSION**

# **Analog Scaling**

Organizer: Andrea Baschirotto, University of Lecce, Lecce, Italy Chair: Robert Neff, Agilent Labs, Palo Alto, CA

#### **OVERVIEW**

The ITRS provides a robust roadmap for technology scaling of digital circuits, while analog circuits strongly suffer from the same trend. This divergence is becoming a crucial bottleneck in the realization of SoCs in scaled technologies, those merging high-density digital parts with high-performance analog interfaces. This results primarily from the reduction in supply voltage, which reduction limits analog performance both in qualitative and quantitative terms. In other words qualitatively, "Is it possible to operate from a low voltage?" and, quantitatively "If it is possible to operate, what performance is achievable?" In fact, the reduced supply voltage and the modified analog performance of scaled devices imply a lower signal swing, and, hence, a reduced dynamic range for analog circuits. This reduction becomes more and more critical in advanced signal-processing systems which require large dynamic range at low supply voltages. Accordingly, analog designers must face challenging trade-offs between supply headroom, device matching, gain, and accuracy.

#### OBJECTIVE

This Special-Topic Session is organized as in three talks that deal with these critical issues, giving an overview of the present situation and a forecast of the future. Each talk will deal with one of the following open questions:

- How will the new scaled-technologies be affected by the power consumption of an analog system?

- Which analog topologies will be feasible in scaled technologies?

- What level of performance will be possible in scaled technologies?

#### CHALLENGE

To review and propose possible circuit techniques for various blocks in an analog signalprocessing unit (such as gain stages, filters, ADCs, etc) for maintaining performance quality in scaled technologies

#### STRUCTURE

# Klaas Bult, Broadcom: "The Effect of Technology Scaling on Power Dissipation in Analog CMOS Circuits"

A general approach to estimating power dissipation in analog CMOS circuits as a function of technology scaling is introduced. As technology progresses to smaller dimensions and lower supply voltages, matching-dominated circuits are expected to see a reduction in power dissipation, whereas noise-dominated circuits will see an increase. A prediction for future analog power scaling will be discussed, using the latest ITRS predictions on power-supply scaling.

#### Andrea Baschirotto, University of Lecce: "Analog-Circuit Solutions in Scaled Technologies"

Technology scaling leads to a reduction of the supply voltage available to analog devices, which can be compensated by a reduction in the MOS-device threshold voltage. However, the threshold-voltage reduction is proportionally less than the power-supply reduction. The effects of this slope difference on analog building blocks will be addressed for several situations.

#### Willy Sansen, KU Leuven: "Delta-Sigma Converters in Scaled CMOS Technologies"

In nanometer CMOS technologies, the supply voltage is reduced to below 1 volt. As a result, the dynamic range of analog blocks, and specifically of Delta-Sigma A/D Converters, is limited by lack of gain and by distortion. Moreover switches have become hard to realize. Specific circuit-design techniques are thus required to achieve high dynamic range, at low voltages for low power.

#### RECAP

This session will provide insights into the effects of technology scaling on analog-circuit performance, and into solutions that could guarantee a certain analog-circuit performance quality, even in scaled technologies.

# Tutorial

# DATA CONVERTER INTERFACES: THE ANALOG AND DIGITAL INS AND OUTS

David Robertson, Analog Devices, Wilmington, MA

#### **OVERVIEW**

- Data Converters form the critical gateway between "real world" analog signals and the digital signals used by computers

- New circuits, new architectures, and new applications, for converters create new challenges for interfacing to the converters on both the analog and digital sides.

- Higher digital speeds, faster analog signals, smaller supply voltages, and higher levels of integration, all have important implications for Data-Converter interfaces.

- Choices that the converter designer makes have fundamental implications for the "usability" of the data-converter design. Understanding these issues is important to interpreting how the state-of-the-art is advancing in converters.

#### **SPEAKER BIOGRAPHY**

**David Robertson** is a Product-Line Director of the High-Speed-Converter Group at Analog Devices. He received his B.A. and B.E. degrees from Dartmouth College, in 1984 and 1985, respectively, and since 1985 has worked at Analog Devices on a wide variety of D/A and A/D converters on complementary bipolar, BiCMOS, and CMOS processes. Dave currently holds 14 patents on converter and mixed-signal circuits, has participated in two "outstanding-panel" ISSCC evening panel sessions, and was co-author of the paper that received the IEEE Journal of Solid-State Circuits 1997 Best Paper Award.

# **ISSCC 2006 – DIGITAL**

Subcommittee Chair: Samuel Naffziger, Intel, Fort Collins, CO

# OVERVIEW

#### MOST-SIGNIFICANT RESULTS

- Single-chip processors with up to 16 cores and 32-threads [5.1, 5.2]

- 65nm processors and processor components [5.3, 5.7, 24.1, 24.7]

- 1.2Tb/s aggregate bandwidth from a single chip [5.6]

- 9GHz processor components: 64-bit integer execution unit and register file [5.7,24.7]

- Next-generation research on clocking: low skew/jitter resonant techniques [21.1, 21.4, 21.5, 21.6]

- Advanced adder designs: 64-bit adders 4 to 6 front of 4 (FO4 delay) [24.2, 24.3]

- Circuit techniques for improved PVT tolerance [24.7, 24.4, 24.5, 29.6]

- Real-time high-spatial-resolution power monitoring of modern processor chips [29.2]

- Single chip with power management for 20 power domains [29.4, 29.5]

#### **APPLICATIONS AND ECONOMIC IMPACT**

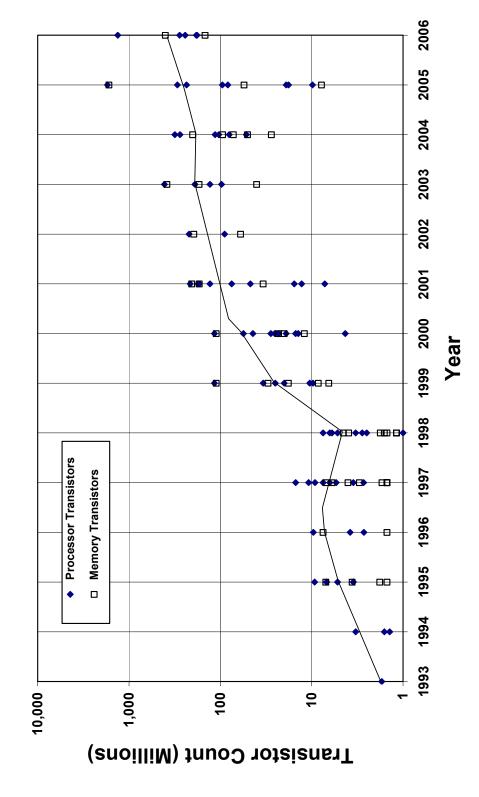

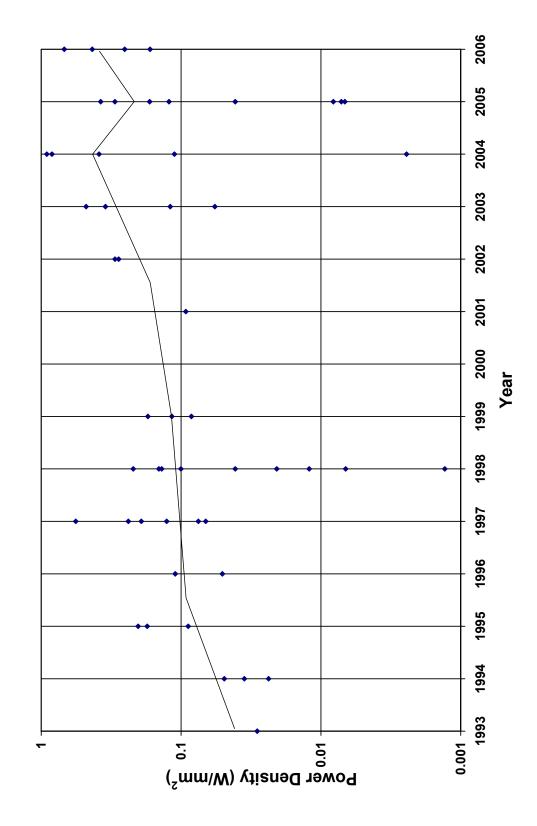

- Multicore multithreaded processors enable higher parallelism, and improved power-performance [5.1, 5.2, 5.3, 5.4, 5.5]

- Debut of 65nm processor technology marks the next level of integration and performance, cutting chip area and power consumption [5.3, 5.7, 24.1, 24.7]

- High-speed I/O links take system bandwidths to a higher level; allowng tight coupling of large numbers of powerful processors [5.6]

- Design for process, voltage and temperature (PVT) variation tolerance will improve manufacturability, reliability, cost [24.7, 24.4, 24.5, 29.6]

- Advances in power-delivery techniques for higher-performance server processors improve power efficiency [29.2, 29.3, 29.4, 29.7]

#### PANEL

Is the Digital Circuit Designer Dead? [E1]

#### TUTORIAL

Introduction to Fractional-*N* Phase-Locked Loops [T1]

#### FORUM

#### Multicore Architectures: Designs, and Implementation Challenges [F6]

©COPYRIGHT 2005 ISSCC—DO NOT REPRODUCE WITHOUT PERMISSION

# High-Performance Chips Integrate Multicore, Multithread Processors

#### A Power-Efficient High-Throughput 32-Thread SPARC Processor [5.1]

Sun Microsystems

#### A 16-Core RISC Microprocessor with Network Extensions [5.2] Cavium Networks

# A Dual-Core Multithreaded Xeon<sup>™</sup> Processor with 16MB L3 Cache [5.3]

Intel

# A 2.6GHz Dual-Core 64b x86 Microprocessor with DD2 Memory Support [5.4]

AMD

#### A 64b CPU Pair: Dual- and Single-Processor Chips [5.5] **IBM**

# **PRESENT STATE OF THE ART** (THE PROBLEM)

- Processors continue to struggle for additional performance within a given power budget.

- The drive for higher frequency for better performance is fading due to power constraints

#### NOVEL CONTRIBUTIONS

- 32 threads available within one chip. [5.1]

- 8 and 16 cores per chip enhance the overall power-performance design point [5.1, 5.2]

- Frequency is reduced to allow for additional cores per chip [5.1, 5.2]

- DDR2 usage becomes standard for high-throughput memory interfaces [5.1, 5.2, 5.4] •

- Four-thread and two-thread cores effectively use silicon area for increased performance [5.1, 5.3, 5.5] •

#### CURRENT AND PROJECTED SIGNIFICANCE

- Performance enhancements continue for existing architectures [5.1, 5.3, 5.4, 5.5]

- Dual-core chips becoming mainstream across many applications. [5.3,5.4,5.5] •

- Software adaptation will be required to use multicore chips effectively. •

©COPYRIGHT 2005 ISSCC—Do NOT REPRODUCE WITHOUT PERMISSION

# 65nm Processors and Processing Cores

A Dual-Core Multi-Threaded Xeon<sup>™</sup> Processor with 16MB L3 Cache [5.3]

Intel

## A 9GHz 65nm Pentium®-4 Processor Integer-Execution Core [5.7]

Intel.

#### 4GHz+ Low-Latency Fixed-Point and Binary Floating-Point **Execution Units for the POWER6 Processor** [24.1] **IBM**

# An 8.8GHz 198mW 16x64b 1R/1W Variation-Tolerant Register File in 65nm CMOS [24.7]

Intel

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

- Electronics consumers continue their demand for products that have more transistor density and • integration, higher performance, and greater mobility.

- Due to challenges in processing, the industry has been very concerned over a substantial slowing • of the rate of scaling, slower than 1 generation every 2 years.

- Power, in particular that due to leakage, is a critical concern. •

- More-deeply-scaled CMOS technologies are exhibiting greater PVT variation. •

#### NOVEL CONTRIBUTIONS

- Power-management techniques that power up less than 1% of the SRAM cache, and utilize • multiple sleep modes with virtual supplies that can be disconnected from all actual supplies. [5.3]

- First fully-demonstrated microprocessor and execution cores in 65nm CMOS technology [5.3, 5.7, • 24.1]

- 9GHz operation of processor functional units, i.e. registers, and integer execution cores, in 65nm. with 30% improvement in speed performance, and 50% reduction in switching power is demonstrated. **[24.1, 24.7]**

- Variation and leakage current compensation embedded in the circuits and architecture of functional blocks using split wordlines and added keeper compensation circuits. [24.7]

- The level of integration afforded by 65nm CMOS indicates an end to single-core processors. [5.3]

- The demonstration of a high-performance processor and execution cores indicates the ramp-up of 65nm production [5.3, 5.7, 24.1, 24.7].

- The continued power-speed-performance improvements for individual execution units enable greater functionality for both server and mobile applications. **[5.7, 24.1, 24. 7]**

# Green Computing: Charge-Recycling Logic Families Exceed 1 GHz Operation Frequencies

## A 1.1GHz Charge-Recovery Logic [21.5]

University of Michigan, Ann Arbor

# A 3.5GHz Rotary-Traveling-Wave-Oscillator Clocked Dynamic-Logic Family in 0.25µm CMOS [21.6]

Multigig

#### PRESENT STATE OF THE ART (THE PROBLEM)

- Power consumption in high-performance processors is already a critical design issue

- Power delivery, cooling, and compute density are important constraints/parameters for datacenters

- Conventional circuit techniques draw current from a supply to charge load capacitance, then dump charge to ground to discharge loads (in which process, charge flows from supply to ground, and is "lost").

- Circuits to recycle charge (storing energy in an inductor, rather than dumping it to ground) have been proposed in the past, but to-date, operating frequencies have been limited, and required external inductive clock generators.

#### NOVEL CONTRIBUTIONS

- Charge-recovery logic circuits fabricated and demonstrated to run at frequencies up to 1.3 GHz, with up to 60% of total energy recovered every cycle **[21.5]**

- 3.5 GHz operation for dynamic logic circuits powered by a charge-recycling oscillator clock [21.6]

- Due to process and frequency scaling, resonant clock generators can now be fully integrated onchip (LC oscillator, rotary wave) [21.5, 21.6]

- Large fractions of the switching energy can be recovered, even at high frequencies. Similar techniques may eventually be used in mainstream-processor design, which would enable significant power reduction [21.5, 21.6]

# On-Die Voltage Regulation for Fine-Grained Power Management and Delivery

#### A Linear Regulator with Fast Digital Control for Biasing Integrated DC-DC Converters [29.2]

Intel; Silicon Laboratories

# Hierarchical Power Distribution with Power Domains in 90nm Low-Power Multi-CPU Processor [29.4]

Hitachi; Renesas

#### A Power-Management Scheme Controlling 20 Power Domains for a Single-Chip Mobile Processor [29.5]

Renesas Technology; NTT DoCoMo

# A Signal-Integrity Self-Test Concept for Debugging Nanometer CMOS ICs [29.6]

Philips

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

- The increasing levels of integration of transistors on-chip results in high power dissipation and increased challenges in power delivery.

- Variation due to manufacturing-process effects on transistor features, supply voltage, and temperature, cause degradation of power consumption and frequency of high-performance processing circuits.

- Conventional power-gating schemes only allow for coarse-grained power-domain partitioning.

#### **NOVEL CONTRIBUTIONS**

- An on-die linear regulator achieves 3X speed-power performance by using digital control rather than conventional analog control **[29.2]**

- Fine-grained power gating in a 3G cellular processor is supported by a power tree distribution. Leakage current is reduced up to 4000X using a hierarchical power down scheme. **[29.4,29.5]**

- On-die voltage and temperature monitors are distributed across the chip to provide 10ps/20mV pulse power-supply noise resolution and 4b temperature resolution. **[29.6]**

- Improving the speed-power performance of the linear regulator improves the power effiiciency of the entire chip. **[29.2]**

- Leakage reduction enables lower overall energy consumption and improved product and battery lifetimes. **[29.4, 29.5]**

- High-resolution on-chip supply-noise and temperature monitors allow for adaptive self-control techniques to increase performance and reduce energy. **[29.6]**

# *Circuit Techniques for Power-Performance Optimization for Dynamic Logic*

# A Leakage-Current Replica Keeper for Dynamic Circuits [24.4]

#### PRESENT STATE OF THE ART (THE PROBLEM)

- Dynamic logic is a mainstay in high-performance processing blocks

- Because of the dynamically-held charge in the logic, leakage is a serious issue in the design of dynamic logic. Feedback "keepers", are commonly used to maintain the charge by injecting a compensating current.

- While over-designing the "keeper" ensures robust performance, performance is degraded.

#### **NOVEL CONTRIBUTIONS**

- A keeper device that has a well-controlled current is created by using a replica circuit that produces the optimal current. The technique provides the necessary robustness without excess degradation on performance.[24.4]

- The keeper design tracks process/voltage/temperature (PVT) variations. [24.4]

- The keeper design is applied to an SRAM. [24.4]

- The technique can be applied to any regular logical structures in addition to memories. [24.4]

- The replica-keeper technique provides up to 40% improvements in an SRAM with almost no area penalty. **[24.4]**

# Circuit and Architectural Improvements in Adder Design

#### A 250ps 64b Carry-Lookahead Adder in 90nm CMOS [24.2]

University of California, Berkeley; Xilinx

#### A 64b Adder Using Self-Calibrating Differential Output-Prediction Logic [24.3]

University of Washington; University of Texas, Dallas

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

- High-performance processors must maintain <100W ceilings. Speed and energy efficiency of execution cores (i.e. adders, multipliers, etc.) are critical for modern processing ICs.

- A wide range of circuit options and architectural options are available for design. Tradeoffs in the design space is not well understood.

#### NOVEL CONTRIBUTIONS

- An optimization framework is introduced to help designers converge to an architecture with optimal power/performance tradeoff. **[24.2]**

- 75pJ-per-addition in a 90nm CMOS technology at 4Goperations/sec and for 64 bits using the architectural optimization. **[24.2]**

- A prediction-based circuit technique using aggressive clock timing is introduced to improve both speed and performance. For improved robustness, a self-timing mechanism increases tolerance to process, voltage, and temperature (PVT) variations. **[24.3]**

- 30pJ-per-addition in a 130nm CMOS technology at 4Goperations/second for 64 bits using a novel circuit technique. **[24.3]**

- Power-performance tradeoffs in the architecture of an adder are explored via an optimization. The framework which can be applied to future technologies as well as to execution units beyond adders [24.2]

- 30 to 75pJ/addition enables the next generation of low-power computing engines for both servers and mobile units. **[24.2, 24.3]**

# High-Performance Processor Modules

# A 9GHz 65nm Intel Pentium<sup>®</sup>-4 Processor Integer-Execution Core [5.7]

Intel

## An 8.8GHz 198mW 16x64b 1R/1W Variation-Tolerant Register File in 65nm CMOS [24.7]

Intel

#### **PRESENT STATE OF THE ART** (THE PROBLEM)

- High-speed processor modules, such as the integer-execution core and register file, are key components of current high-performance processors.

- Power dissipation of the processor modules must go hand-in-hand with high-speed design.

#### NOVEL CONTRIBUTIONS

- Domino circuits enable 2X frequency operation replacing previous Low-Voltage-Swing technology which did not scale frequency in the reduction to 65nm. **[5.7]**

- Optimized design of arithmetic units and register files leads to 50% reduction in dynamic power. **[5.7]**

- First demonstration of 65nm processor modules. [5.7, 24.7]

- Variation-tolerant register files achieve frequencies up to 10GHz, while reducing active leakage to 25mW over a wide range of process, voltage and temperature (PVT) conditions. **[24.7]**

#### CURRENT AND PROJECTED SIGNIFICANCE

• Significant power and performance improvements are being achieved on scaled process technologies through choice of logic families, architectural innovation, and power reduction techniques. **[5.7, 24.7]**

# SPARC Processor expands to a 32-thread chip

# A Power-Efficient High-Throughput 32-Thread SPARC Processor [5.1]

Sun Microsystems

#### **RESENT STATE OF THE ART** (THE PROBLEM)

- General-purpose processors are limited in performance by power at high frequency.

- Dual-core chips share I/O infrastructure similar to that used in single-core predecessors.

- For performance, two threads per core are used on high-end chips.

#### **NOVEL CONTRIBUTIONS**

- Eight 64-bit cores, each with four threads, enhance overall performance [5.1]

- Increased memory bandwidth is achieved with four dedicated DDR2 interfaces [5.1]

- 3MB L2 cache is shared by eight cores [5.1]

- New performance level obtained for a single chip with 32 threads [5.1]

- Multicore, multithreaded chips running at a lower frequency obtain better performance [5.1]

# Panel

#### Is the Digital-Circuit Designer Dead?

Organizer: **Shannon Morto**n, Icera Moderator: **Dennis Fischette**, AMD

#### OBJECTIVE

- To determine the future of the digital-circuit designer

- To query whether technology trends will provide more, or less, challenges for digital design

- To question whether CAD tools are evolved enough to replace the digital designer

#### CHALLENGE

- CAD tools have improved their design capabilities, and are arguably competent-enough to replace the digital designer for more and more applications and building blocks.

- Increasing leakage and variability issues demand more time and manpower for the design of highperformance and high-reliable circuits; Therefore simple structures with low innovation are proliferating.