## Freie Universität Berlin 4.1.1 Evaluation of CPU Performance The response time of a program A can be split into: User CPU time of A System CPU time of A

## Freie Universität Berlin 4.1.1 Evaluation of CPU Performance The response time of a program A can be split into: User CPU time of A System CPU time of A Waiting time of A

## Freie Universität Berlin 4.1.1 Evaluation of CPU Performance The response time of a program A can be split into: User CPU time of A System CPU time of A Waiting time of A

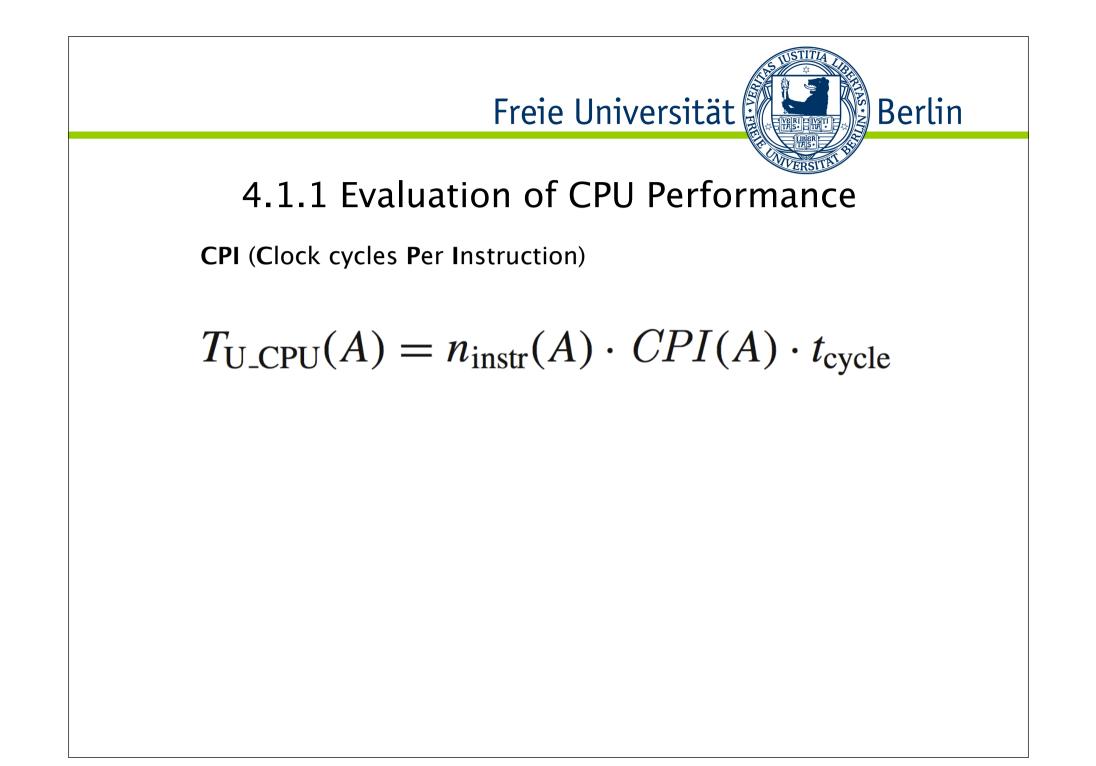

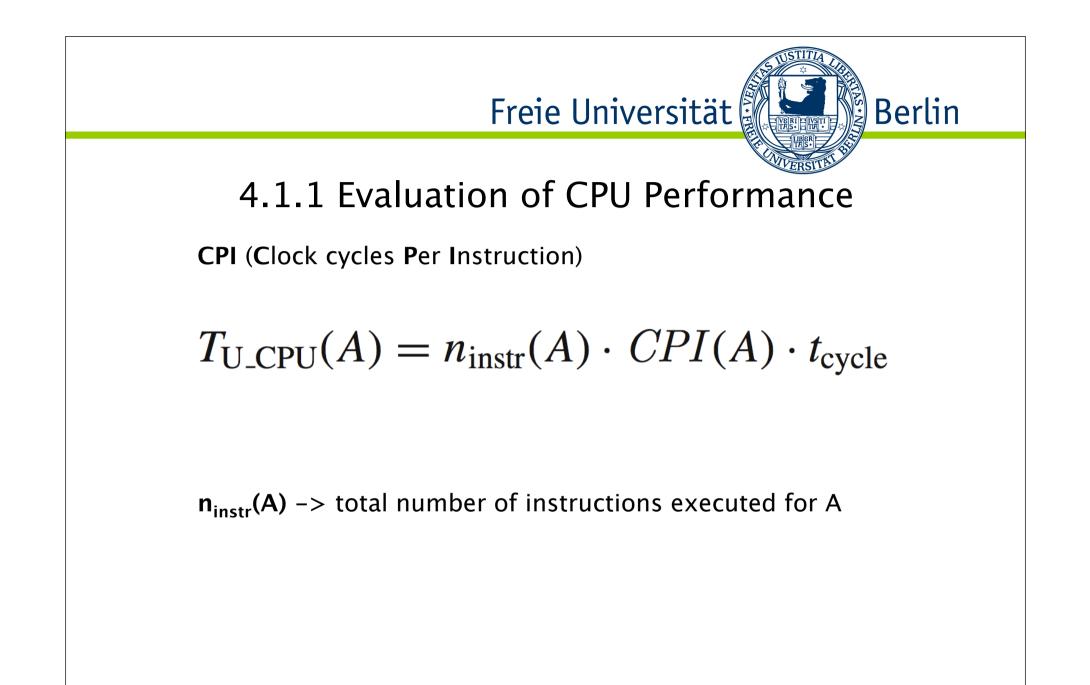

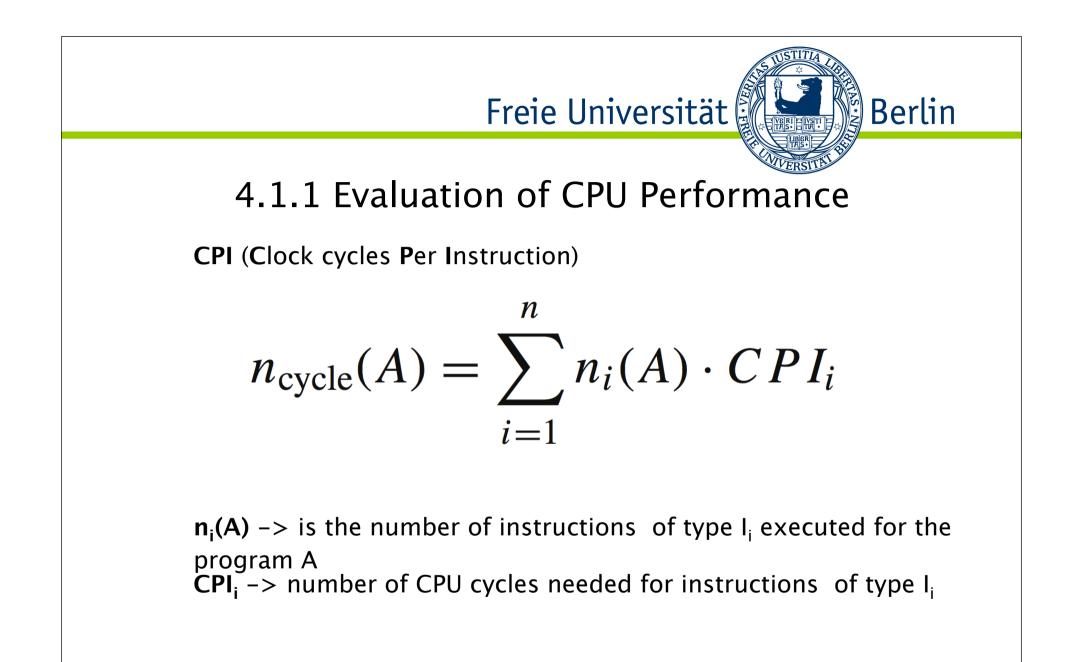

## Freie Universität Berlin 4.1.1 Evaluation of CPU Performance **CPI** (Clock cycles **P**er Instruction) Example: We consider a processor with three instruction classes $I_1$ , $I_2$ , $I_3$ containing instructions which require 1, 2, or 3 cycles for their execution. We assume that there are two different possibilities for the translation of a Instruction classes Programmi structions. Sum of the Translation instructions $\mathcal{I}_1$ $\mathcal{I}_2$ $\mathcal{I}_3$ $n_{\rm cycle}$ 2 1 2 10 5 1 2 4 1 9 1 6 $CPI_1 = 10/5 = 2$ $CPI_2 = 9/6 = 1,5$ $CPI_i = n_{\text{cycle}}(A) / \sum_{i=1}^n n_i(A)$

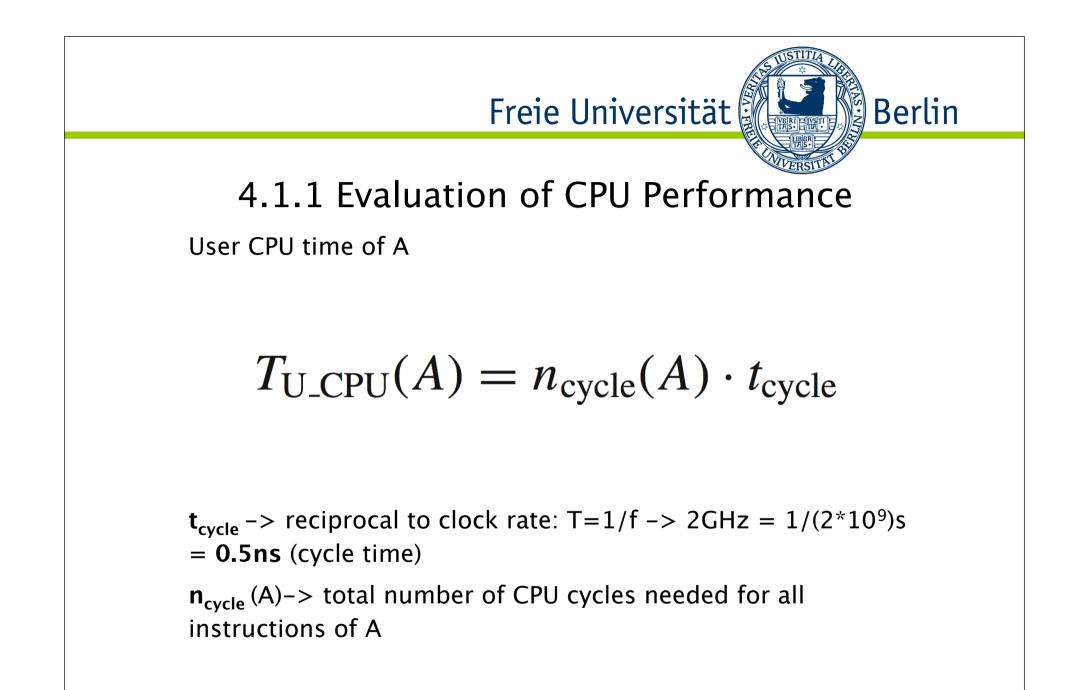

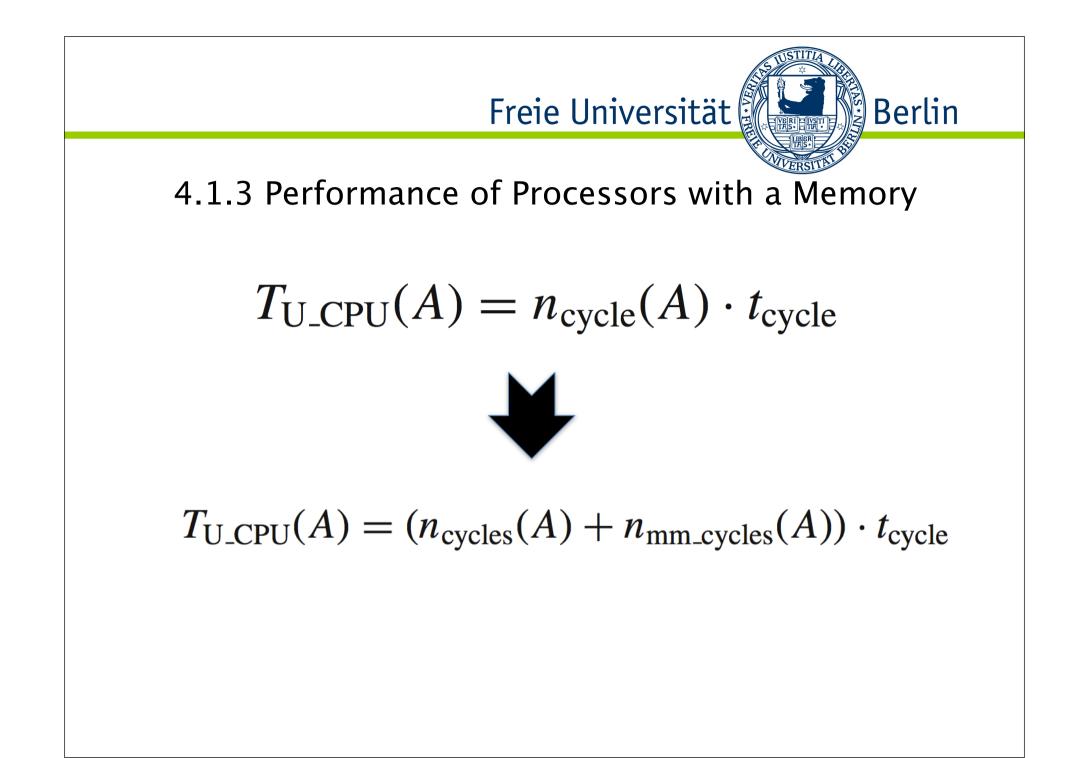

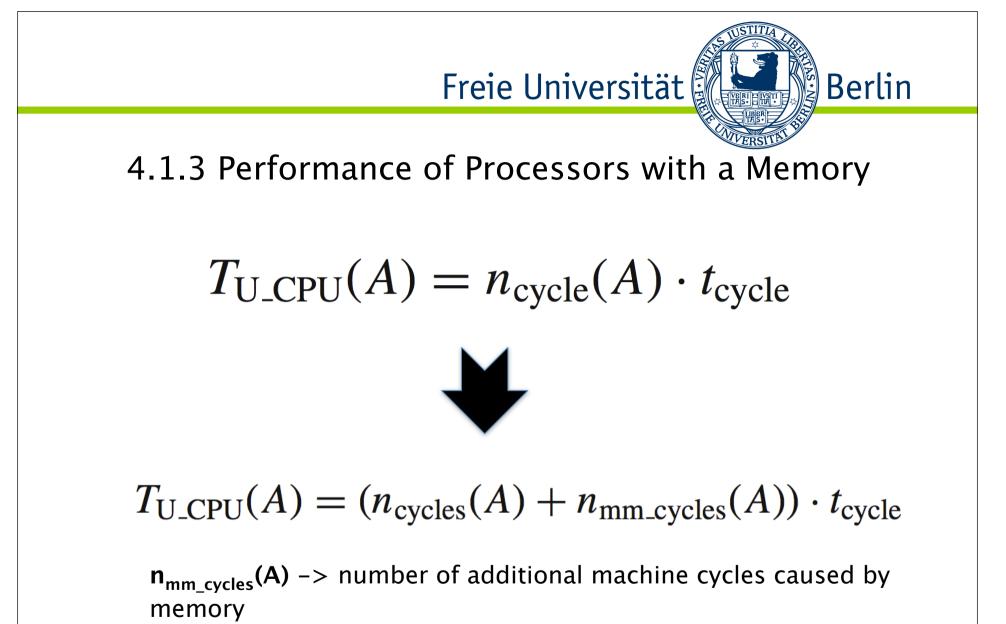

accesses of A