#### Memory Locations, Address, Instructions and Instruction Sequencing

Read pages 28-40

#### Memory locations and addresses

- The simple computer is a good start to understand computer organizations

- We need to study

- how data/instructions are organized in the main memory?

- how is memory addressed? addressing mode

#### Memory

Address

- Holds both instructions and data

- With *k* address bits and *n* bits per location

|    |                             | Audicss                                                 |

|----|-----------------------------|---------------------------------------------------------|

| k  | Number of locations         | $0  \boxed{\mathbf{n-1}  \bullet \bullet \bullet  1 0}$ |

| 10 | $2^{10} = 1024 = 1$ K       | 1                                                       |

| 16 | $2^{16} = 65,536 = 64K$     | 2                                                       |

| 20 | $2^{20} = 1,048,576 = 1$ M  | •                                                       |

| 24 | $2^{24} = 16,777,216 = 16M$ | •                                                       |

|    |                             | $2^{\kappa}$ -1                                         |

• n is typically 8 (byte), 16 (word), 32 (long word), ....

#### Memory stores both data and instructions

- Consider 32-bit long word in each location which can store

- 32-bit 2's complement number (integer):

$(-2^{n-1}) - (2^{n-1} - 1)$

• If

$$n = 32$$

:  $-2G - 2G-1$  (recall that  $G = 2^{30}$ )

- 4 ASCII characters

| byte byte byt | e byte |

|---------------|--------|

|---------------|--------|

- It is often convenient to address operands which are as short as 1 byte

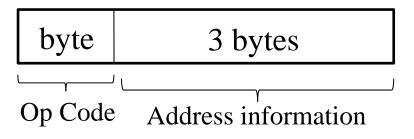

– A machine instruction

#### Dealing with strings of characters

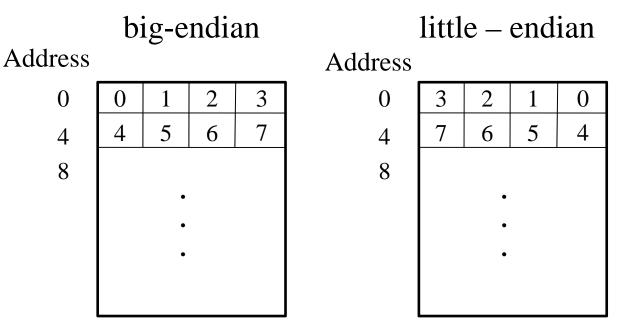

- Byte addressable machine is almost universal

- Successive addresses refer to successive byte locations

- There are two different schemes for addressing byte:

- Also bit can be numbered the other way around: bit 0 is the MSB

# Memory addressing Example – for a Computer

- Word = 16 bits

- Byte addressable uses big-endian

- Long word = 4 bytes

- 24 bits used for address  $\longrightarrow$  16 M bytes or 8 M words

#### Instructions and instruction sequencing

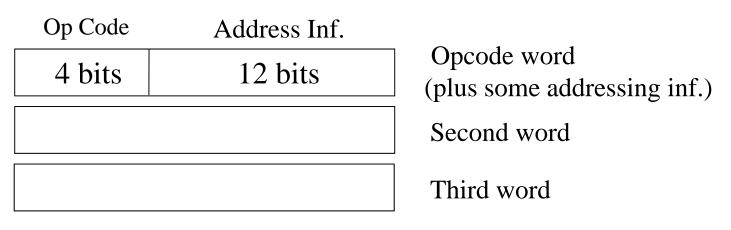

- Example computer instruction format:

- Uses multiple words of 16 bits

- Typical instruction is Add: C = A+B

- Most general instruction is to add 2 numbers in memory and store in a 3<sup>rd</sup> location

Add A, B, C  $[A]+[B] \rightarrow C$

## Problems for instructions with multiple memory locations

- 1. Long instructions

- Address of an operand = 24 bits

- Instruction length = 3 x 24 bits + opcode (4 bits) = 76 bits

too much memory space

- Solutions: a) Use one- or two-address instruction:

Add A, B:  $[A]+[B] \rightarrow B$

Add A:  $[A]+[AC] \rightarrow AC$

b) Use general-purpose CPU register

Often 8-64 bits of them

- 8 registers  $\rightarrow$  use only 3 bits to select a CPU reg.

#### Problems for instructions with multiple memory locations (continued)

- 2. Memory access time is too long

- Recall that memory access is always slow

- Multiple memory access consumes a lot of time

- Solutions: use CPU registers to store operands and temporary results

- Minimizing the frequency with which data moved back and forth between main memory

### Modern CPUs are designed with the above two issues in mind

e.g. ADD A, D1  $[A]+[D1] \rightarrow D1$

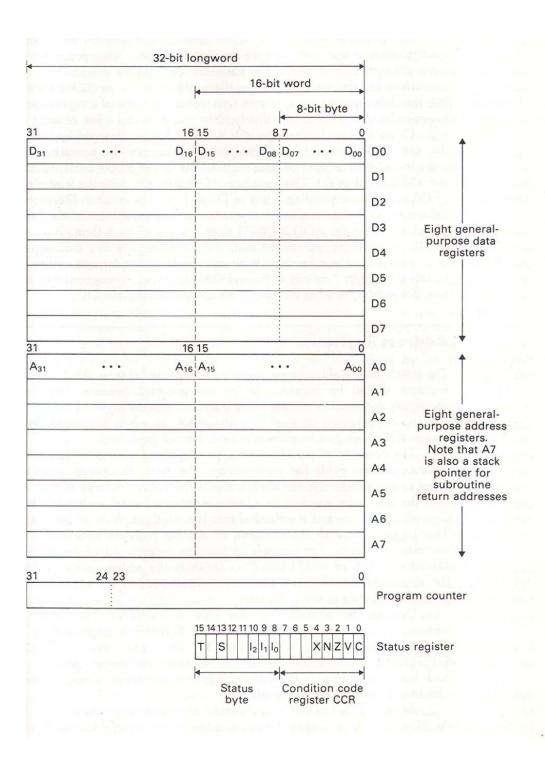

# Registers on CPU

### All are visible to programmer.

#### Compare with our simple computer

- 1. D7 D0 are equivalent to AC (accumulator)

- 2. A7 A0 are equivalent to ? none in our simple computer

- 3. PC (program counter) is the same as PC

- 4. SR (status register) none in our simple computer

- 5. Where are X, MDR, MAR, and IR?

- 6. Those are not visible to the programmer

- 7. Guess how many invisible registers in the CPU?

#### Some instructions for illustration

• ADD -- 2 operand instruction

- e.g. ADD B, D0  $[B]+[D0] \rightarrow D0$

Memory location, data register 0

R

- Either source or destination must be one of the 8 data registers

- Both can be data register

- MOVE similar to ADD

| <b>D</b> 0 |

|------------|

| 0          |

| С          |

|            |

#### Some instructions for illustration (continued)

- SUB (subtract)

- e.g. SUB B, D0  $[D0] - [B] \rightarrow D0$

- CMP (compare)

- e.g. CMP B, D0 [D0] - [B] and set/reset N, Z, V, C

- MOVEA (move address)

- e.g. MOVEA ADDR, A3 [ADDR]  $\rightarrow$  A3

- CLR A  $0 \rightarrow A$  (clear data register or

- Can use .B, .W, or .L

- TST A lacksquare- Can use .B, .W, or .L

- ADDQ #2, D5

- SUBQ #1, D4 •

memory location)

[A] - 0 and set/reset N, Z; make V, C=0

$[D5] + 2 \rightarrow D5$  quick addition

$[D4] - 1 \rightarrow D4$  quick subtraction