# UNCLASSIFIED

| AD NUMBER:                                                               | AD0818377                             |

|--------------------------------------------------------------------------|---------------------------------------|

| LIMITATION                                                               | I CHANGES                             |

| TO:                                                                      |                                       |

| Approved for public release; distribution                                | on is unlimited.                      |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

| FROM:                                                                    |                                       |

| Distribution authorized to U.S. Gov't. a                                 | -                                     |

| Export Control; 1 Jun 1967. Other required to the Air Force Rome Air Dev |                                       |

| 13440.                                                                   | elopment center, Leivil, Griniss Arb, |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

| AUTHO                                                                    | ORITY                                 |

| RADC, USAF LTR, 22 JUN 1973                                              |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

|                                                                          |                                       |

RADC-TR-66-791 Final Report

2

81837

AD

Ð

#### INVESTIGATION OF RELIABILITY TESTING AND PREDICTION TECHNIQUES FOR INTEGRATED CIRCUITS

D. R. Fewer W. L. Gill

Texas Instruments, Incorporated

TECHNICAL REPORT NO. RADC-TR-66-791 June 1967

> This document is subject to special export controls and oach transmittal to foreign governments, foreign nationals or representatives thereto may be made only with prior approval of RADC (EBLI), GAFB, N.Y. 13440

Rome Air Development Center Air Force Systems Command Griffias Air Force Base, New York

When US Government drawings, specifications, or other data are used for any purpose other than a definitely related government procurement operation, the government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specific tions, or other data is not to be regarded, by implication or otherwise, as in any manner 1 tensing the holder or any other person or corporation, or conveying any rights or permission to manufacturer, use, or sell any patented invention that may in any way be related thereto.

Do not return this copy. Retain or destroy.

# INVESTIGATION OF RELIABILITY TESTING AND PREDICTION TECHNIQUES FOR INTEGRATED CIRCUITS

1776.077

## D. R. Fewer W. L. Gill

Texas Instruments, Incorporated

This document is subject to special export controls and each transmittal to foreign governments, foreign netionals or representatives thereto may be made only with prior approval of RADC (EMLI), GAFE, N.Y. 13440

AFLC, GAFB, N.Y., 14 Jul 67-249

and the second

24

75

ant.

#### FOREWORD

This final report was prepared by Texas Instruments, Incorporated, P. O. Box 5012, Dallas, Texas, under Contract AF30(602)-3723, Project 5519, Task 551902, System 760E, Contractor Report Number 03-66-131. The period of time covered was from 19 April 1965 through 19 October 1966. Authors were D. R. Fewer, W. L. Gill, S. F. Musket and W. L. Workman.

RADC Project Engineer was Mr. Regis Hilow (EMERR). Technical Advisors were Mr. John Carroll (EMERP) and Mr. Edward O'Connell (EMERM).

The information contained in this report pertains to the reliability, performance and evaluation of state-of-the-art components.

This technical report has been reviewed by the Foreign Disclosure Policy Office (EMLI). Release of subject report to the general public is prohibited by the Strategic Trade Control Program, Mutual Defense Assistance Control List (revised 6 Jan 65) published by the Department of State.

This technical report has been reviewed and is approved.

Approved: Sugic. 2

REGIS C. HILOW Reliability Engineering Section Reliability Branch

mil R. Louto Approved

Chief, Engineering Division

|         | COMMANDER THIN Solder                              |

|---------|----------------------------------------------------|

| FOR THE | COMMANDER NAME COLORING                            |

|         | IRVINGEL GABELMAN<br>Chief, Advanced Studies Group |

|         | Chief, Xdvanced Studies Group                      |

#### ABSTRACT

This report is the last in a series of three reports relating to the work performed by Texas Instruments under this contract. The work is divided into four parts: (1) Data analysis and preliminary tests to determine failure mechanisms for early direction in the study; (2) a physics of failure program consisting of fundamental oxide studies, metal contact and interconnection evaluations, and circuit analysis; (3) a test program including data and failure analysis and consisting of two major segments; and (4) the development of a reliability screening procedure for integrated circuits. Three computer programs, SERF, LINDA 1 and LINDA 2 were written to assist in the analysis of data.

The physics of failure program consisted of fundamental surface studies to produce stable metal-oxide-silicon (MOS) systems, circuit analysis of the SN5420 integrated circuit, and a study of the molybdenumgold expanded contact system.

D. R. Fewer Program Manager

C. gordon Rottie

C. Gordon Peattie Manager, Quality and Reliability Assurance Department, Semiconductor-Components Division

## TABLE OF CONTENTS

| SECTION | TITLE                                                | PAG |

|---------|------------------------------------------------------|-----|

| I.      | INTRODUCTION                                         | 1   |

|         | 1. Summary of Reports                                | 1   |

|         | 2. Program Summary                                   | 1   |

|         | a. Data Analysis and Preliminary Tests               | 1   |

|         | b. Physics of Failure Program                        | 2   |

|         | c. Test Program                                      | 3   |

|         | d. Nondestructive Reliability Screening              | 3   |

|         | e. Computer Programs                                 | 5   |

|         | f. Publications                                      | 7   |

| II.     | PROGRAM REVIEW                                       | 9   |

|         | 1. Introduction                                      | 9   |

|         | 2. Test Venicle                                      | 9   |

|         | 3. Circuit Analysis                                  | 9   |

|         | a. Objective                                         | 9   |

|         | b. DC Analysis                                       | 9   |

|         | c. Small Signal Analysis                             | 10  |

|         | d. Transient Analysis                                | 10  |

|         | 4. Failure Definition and Stress Circuit Analysis    | 10  |

|         | 5. Data Analysis and Preliminary Tests               | 10  |

|         | 6. Test Program                                      | 11  |

|         | a. Step Stress Series                                | 11  |

|         | b. Fixed and Step Stress Series                      | 11  |

|         | 7. Computer Programs                                 | 12  |

| ш.      | TEST RESULTS AND ANALYSIS                            | 13  |

|         | 1. Introduction                                      | 13  |

|         | 2. Measurement Error Detection and Control           | 13  |

|         | 3. SERF Screening Results                            | 14  |

|         | 4. Analysis of Nonfunctional Measurements            | 17  |

|         | a. Voltage Gain                                      | 17  |

|         | b. Output Impedance                                  | 24  |

|         | 5. Analysis of Stress Failures                       | 24  |

|         | 6. Component Evaluation                              | 30  |

| IV.     | RELIABILITY SCREENING                                | 31  |

|         | 1. Introduction                                      | 31  |

|         | 2. Precapsulation Lot Acceptance for Metal Adherence | 31  |

|         | 3. Die and Wire Dress                                | .32 |

# TABLE OF CONTENTS (Continued)

## SECTION

## TITLE

|           | 4.      | Die I | nspec  | tion . | •      |      | •         | •    | •      | •   | •   | • |   |   |   | • | • | 33             |

|-----------|---------|-------|--------|--------|--------|------|-----------|------|--------|-----|-----|---|---|---|---|---|---|----------------|

|           | 5.      | Ther  | mal-e  | lectri | ical H | Bur  | n-in      |      | •      | •   | •   | • |   |   |   | • | • | 36             |

|           |         | a.    | Elec   | trical | Burn   | n-in | L         |      |        |     |     |   |   |   | • | • |   | 36             |

|           |         | b.    | High   | Tem    | perat  | ure  | Sto       | rag  | e      | •   | •   | • | • |   |   | • |   | 40             |

|           | 6.      | Hern  |        |        |        |      |           |      |        | •   | •   | • |   |   |   | • |   | 41             |

|           | 7.      | Cost  | of Sci | reenin | g.     | •    | •         |      |        | •   |     |   |   | • |   |   | • | 41             |

|           | 8.      | Contr |        |        | -      | •    | •         |      |        | •   |     | • |   | • |   | • | • | 45             |

| v.        | CONT    | ACTS  |        |        |        | NN   | ECT       | ΓΙΟ  | NS     | •   | •   | • | • | • | • | • | • | 47             |

|           | 1.      | Intro |        |        |        |      |           |      |        | •   | •   | • | • | • | • | • | • | 47             |

|           | 2.      | Test  | Vehic  | le .   |        |      |           | •    | •      | •   | •   | • | • | • | • | • | • | 47             |

|           | 3.      | Sumn  |        | •      | ulta   |      | •         | •    | •      | •   | •   | • | • | • | • | • | • | 49             |

|           | 4.      | Tech  | •      |        |        | •    | •         | •    | •      | •   | •   | • | • | • | • | ٠ | • | <del>4</del> 9 |

|           |         | a.    |        | on $-$ |        |      | •<br>tarf | •    | •      | ٠   | •   | ٠ | ٠ | • | • | • | • |                |

|           |         | b.    |        | l Top  |        |      |           |      | -      | •   | •   | • | • | • | • | • | • | <b>49</b>      |

|           |         | с.    |        |        | - +    |      | -         |      | •<br>• | •   | •   | • | ٠ | ٠ | • | • | • | 50             |

|           | ~ ~ ~ ~ |       |        | Strei  | igui a | Ind  | Me        |      | Adn    | ere | nce | ; | ٠ | • | • | • | • | 59             |

| VI.       | CRIT    | IQUE  | • •    | • •    | •      | •    | •         | •    | •      | •   | ٠   | • | • | • | • | • | • | 73             |

|           | 1.      | Intro | ductio | n.     | •      | •    | •         | •    | •      | •   | •   | • | • | • | • | • | • | 73             |

|           | 2.      | Reco  | mmen   | dation | ns for | · Fi | ıtur      | e Si | udi    | es  | •   | • | • | • | ٠ | • | • | 75             |

| REFERENC  | ידפ     |       |        |        |        |      |           |      |        |     |     |   |   |   |   |   |   |                |

| ALF ERENC | - EO    | •     | • •    | • •    | •      | •    | •         | •    | •      | •   | •   | • | • | • | ٠ | • | • | 77             |

## APPENDICES

## TITLE

| <b>A.</b> | FIXED AND STEP STRESS SERIES            |

|-----------|-----------------------------------------|

| в.        | COMPONENT EVALUATION                    |

| C.        | COMPUTER PROGRAMS - SERF AND LINDA      |

| D.        | FAILURE ANALYSIS                        |

| E.        | THEORY OF FIXED AND STEP STRESS TESTING |

|           |                                         |

# LIST OF ILLUSTRATIONS

FIGURE

## TITLE

.

14

л÷,

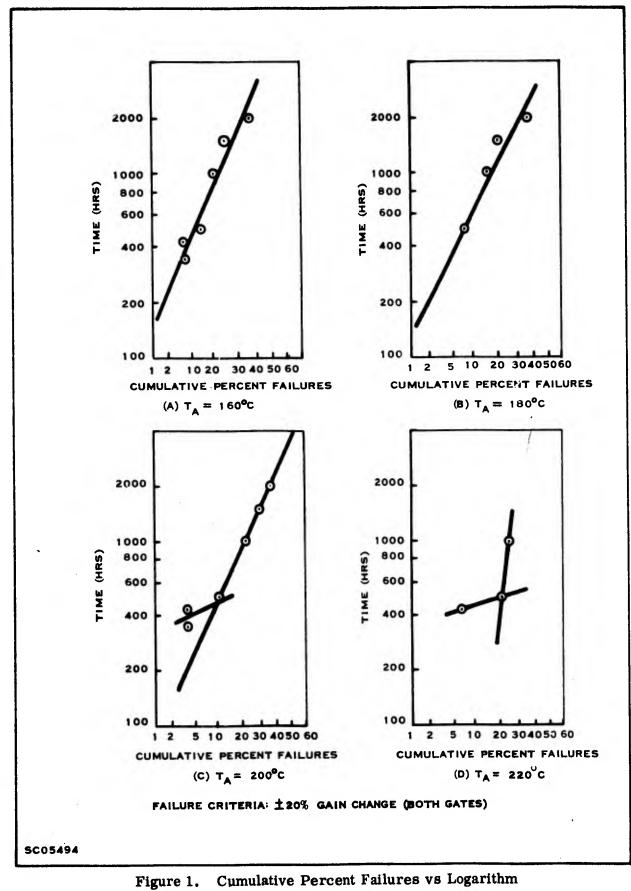

| 1.  | Cumulative Percent Failures vs Logarithm of Time      |                  |

|-----|-------------------------------------------------------|------------------|

|     | for Forward Bias Life                                 | 18               |

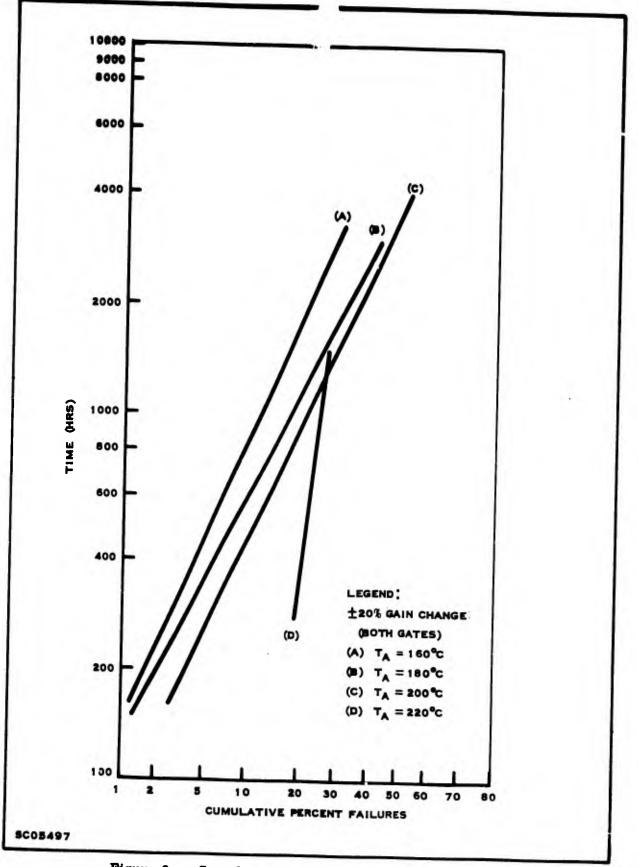

| 2.  | Cumulative Percent Failure vs Logarithm of Time       | 10               |

|     | for Forward Bias Life (Summary of Figure 1)           | 19               |

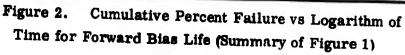

| 3.  | Cumulative Percent Failures vs Logarithm of Time      | 13               |

|     | for Ring Counter Life                                 | 20               |

| 4.  | Cumulative Percent Failure vs 1000/T(°K) for          | 20               |

|     | Ring Counter Step Stress                              | 21               |

| 5.  | Ring-counter Acceleration Curve                       |                  |

| 6.  | Plots of Output Impedance vs Time for Ring            | 22               |

|     | Counter Life Test                                     | 26               |

| 7.  | Plots of Outrut Impedance vs Time for Ring            | 20               |

|     | Counter Life Test                                     | 27               |

| 8.  | Plots of Output Impedance vs Time for Ring            | 21               |

|     | Counter Life Test                                     | 28               |

| 9.  | Plots of Output Impedance vs Time for High            | 20               |

|     | Temperature Storage Life                              | 29               |

| 10. | 20X Visual Package Inspection                         | 2 <i>3</i><br>33 |

| 11. | Visual Inspection for Cracked Dice                    | 36               |

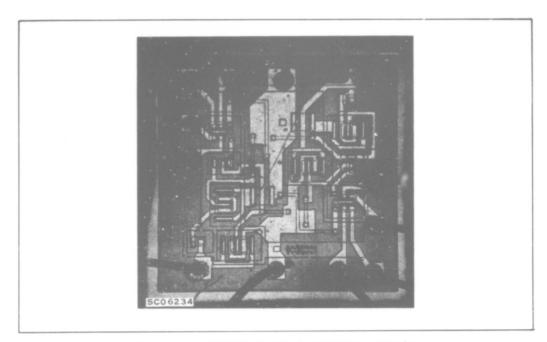

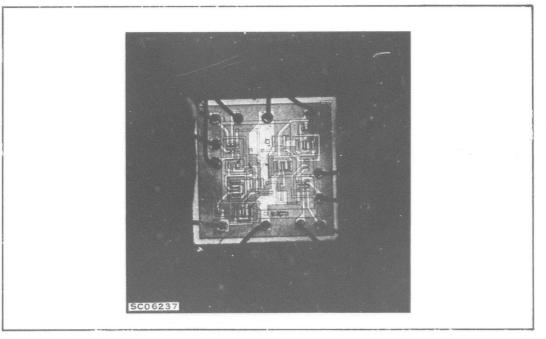

| 12. | SN5420 Die Photo-70X Direct Light                     | 38               |

| 13. | SN5420 Die Photo-40X Diffused Light                   | 38<br>38         |

| 14. | SN5420 Die-Photo-40X Oblique Light .                  | 39               |

| 15. | SN5420 Die-Photo-40X Direct Light                     | 39<br>39         |

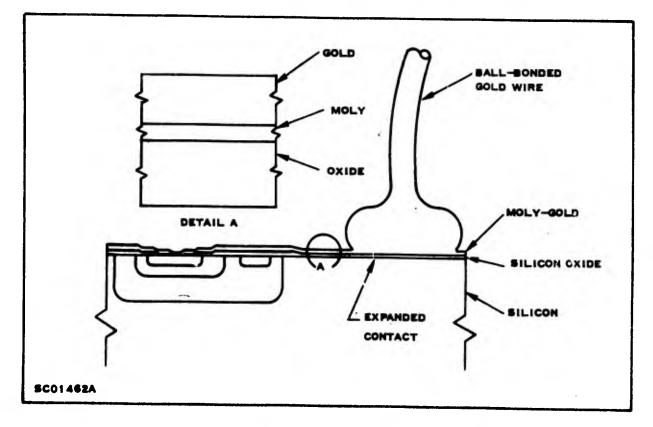

| 16. | Sectional View of Moly-gold Interconnect System       | 39               |

|     | Used for Monolithic Integrated Circuits               | 48               |

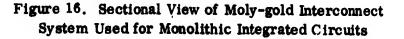

| 17. | Percent Change $\Delta V_{BE}$ (Forward Bias)         | 40               |

|     | versus Stress                                         | 51               |

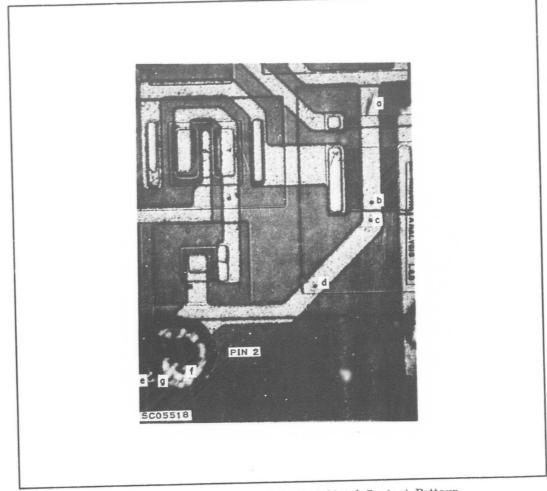

| 18. | Diagram of SN5420 Metal Contact Pattern               | 53               |

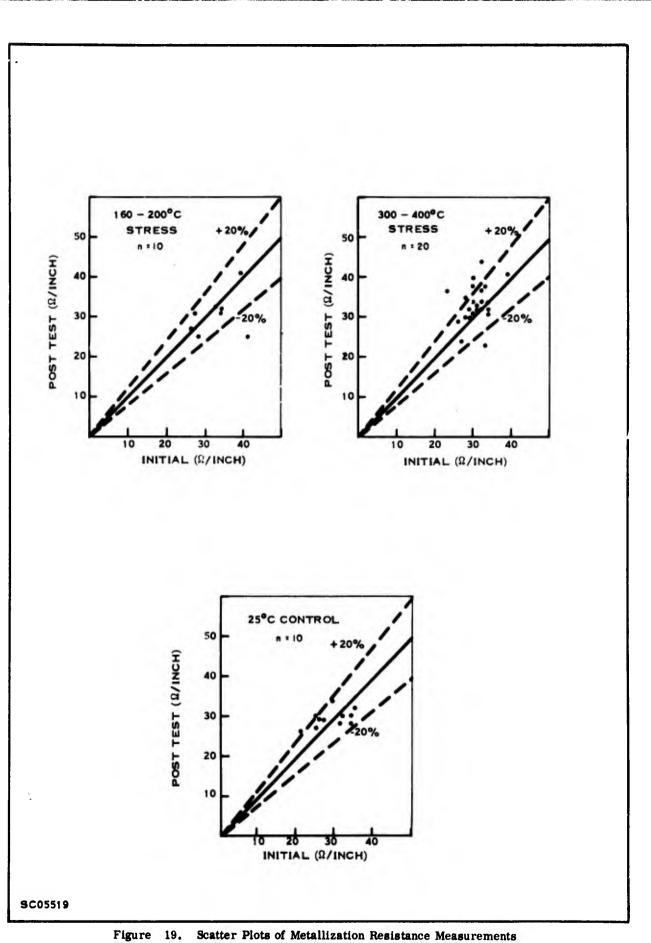

| 19. | Scatter Plots of Metalization Resistance Measurements | 53               |

|     | Initial Versus Post Stress for Metal Length           | <b></b>          |

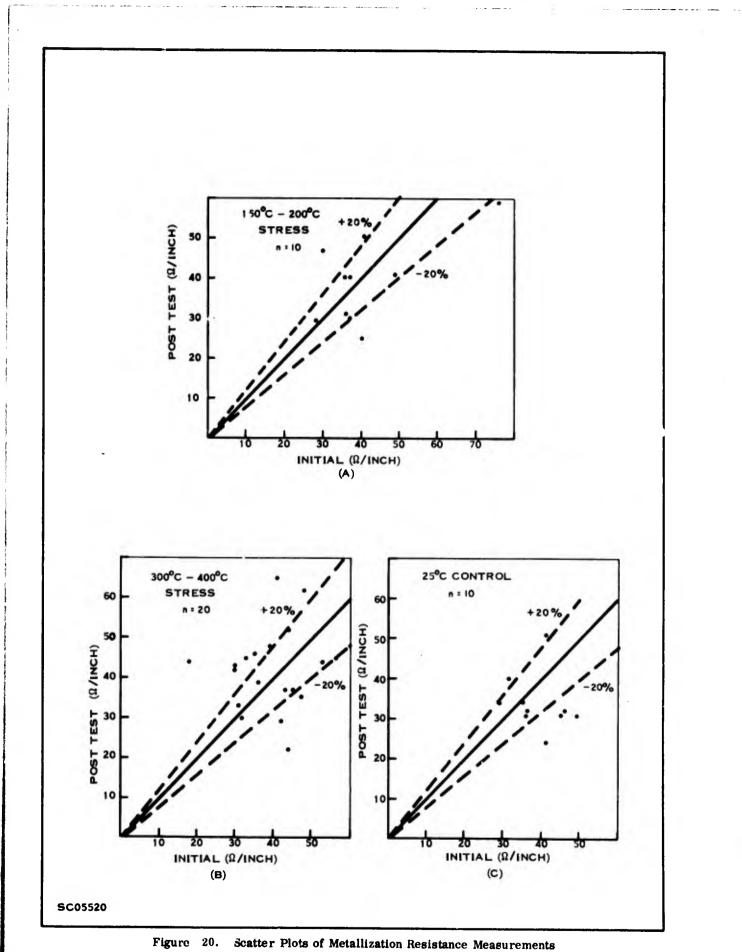

| 20. | Scatter Plots of Metalization Resistance Measurements | 55               |

|     | Initial Varaus Doct Strang for Out 1 of               | EC               |

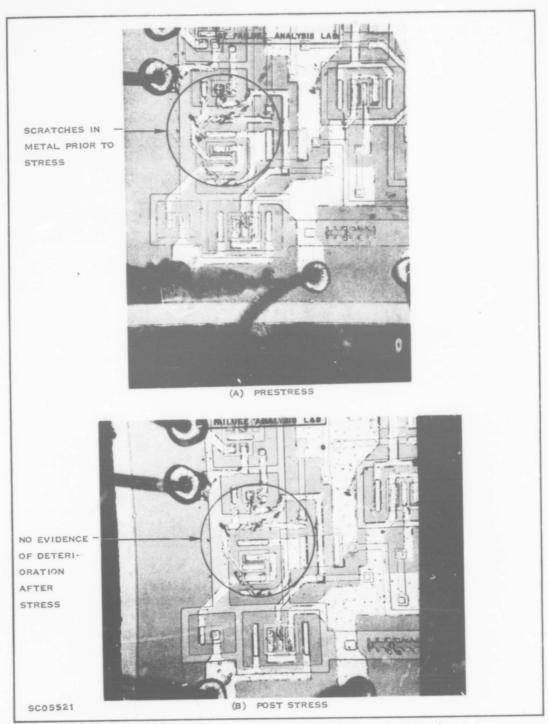

| 21. | Photographs (200x) of Scratched Lead Before and       | 56               |

|     | After 375° Stress for 1000 Har                        | = 0              |

|     |                                                       | 58               |

## LIST OF ILLUSTRATIONS (Continued)

#### FIGURE

#### TITLE

PAGE

54

•

| 22.  | Contact Metal to Oxide Cross Section for Samples           |

|------|------------------------------------------------------------|

|      | Subjected to High Temperature Storage 60                   |

| 23.  | Cross Section of Gold Ball Bond to Metallization Interface |

|      | Following 400°C Storage for 540 Hours 61                   |

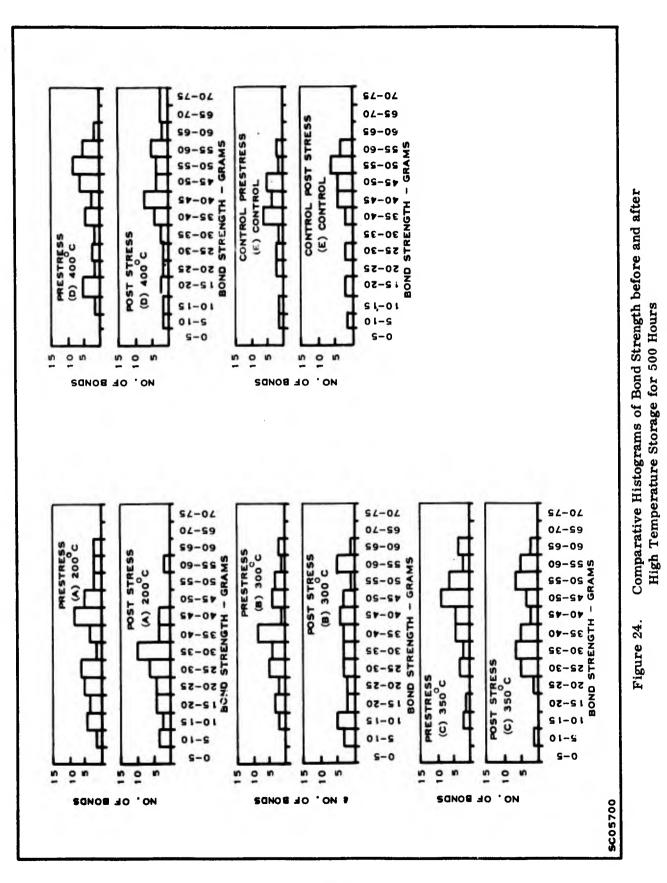

| 24.  | Comparative Histograms of Bond Strength Before and         |

|      | After High Temperature Storage for 500 Hours 64            |

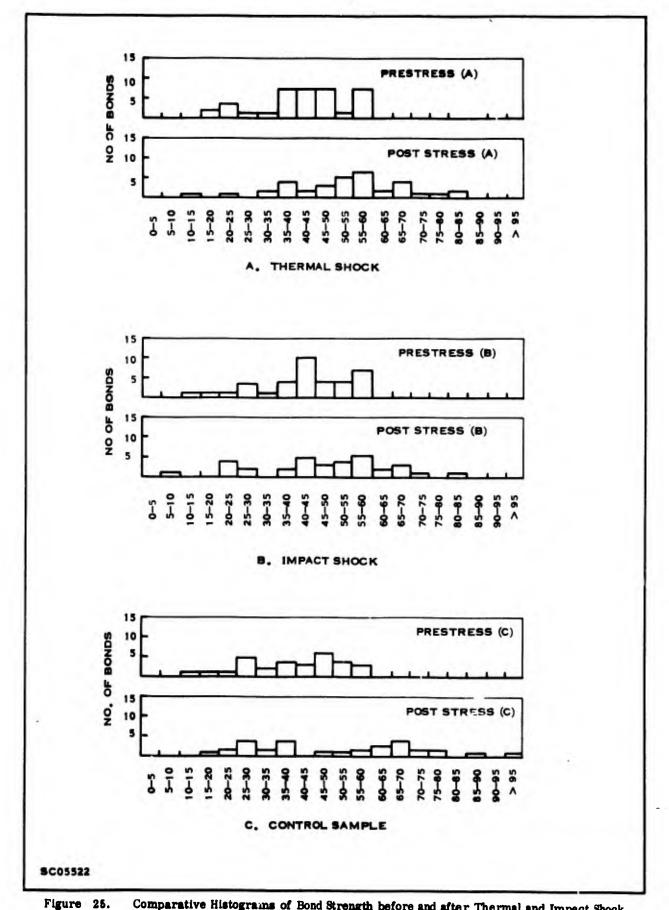

| 25.  | Comparative Histograms of Bond Strength Before and         |

|      | After Thermal and Impact Shock 65                          |

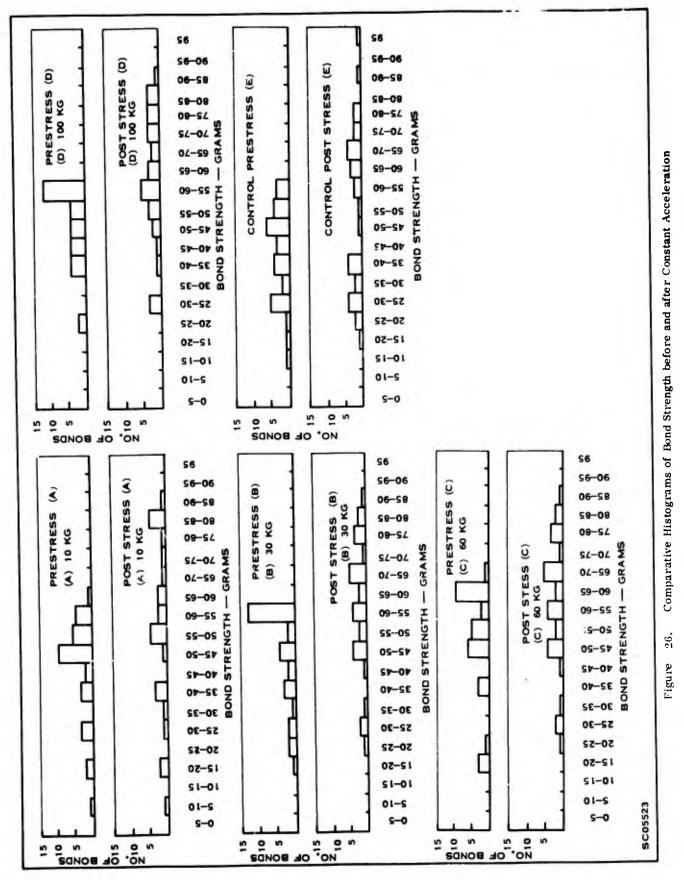

| 26.  | Comparative Histograms of Bond Strength Before and         |

|      | After Constant Acceleration                                |

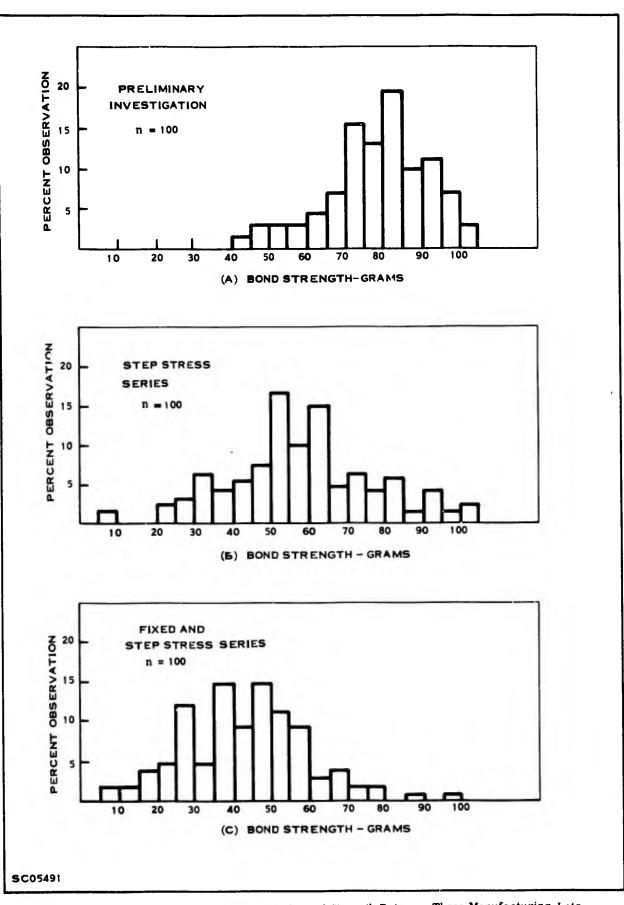

| 27.  | Comparative Histograms of Bond Strength Between Three      |

|      | Manufacturing Lots                                         |

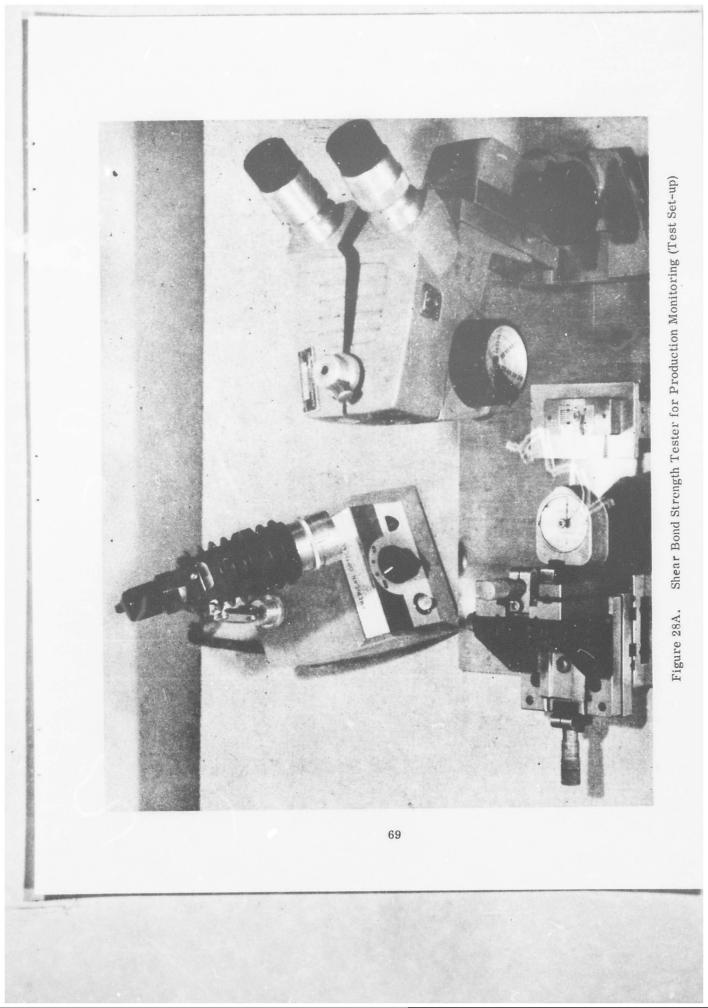

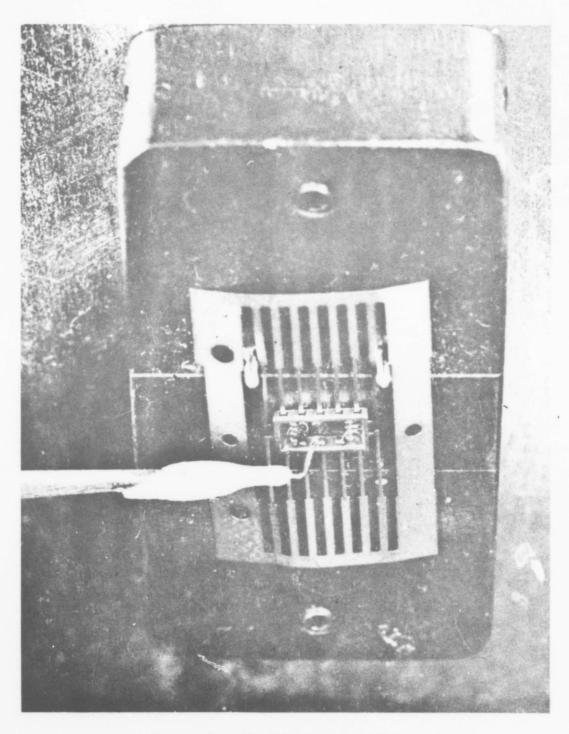

| 28A. | Shear Bond Strength Tester for Production                  |

|      | Monitoring (Test Set-up)                                   |

| 28B. | Detail for Device and Shear Probe                          |

|      |                                                            |

## LIST OF TABLES

## NUMBER

S. Inter-

#### TITLE

| 1.  | Reliability Screening Procedure for SN5420                |  |

|-----|-----------------------------------------------------------|--|

| 2.  | SERF Screening Results                                    |  |

| 3.  | Test and Failure Analysis Results                         |  |

| 4.  | Precap Visual Screening Procedure for Integrated Circuits |  |

|     | (70X Direct Lighting Recommended)                         |  |

| 5.  | Cracked Dice Failure Modes                                |  |

| 6.  | Oxide Defects                                             |  |

| 7.  | SERF Screening Results                                    |  |

| 8.  | Cost of Screening                                         |  |

| 9.  | Requirements for Testing, Data Analysis and Reporting 44  |  |

| 10. | Contact Resistance Measurement Study Conducted on         |  |

|     | Devices from Fixed and Step Stress Series                 |  |

11. Analysis of Metal Resistance Measurements . . . . .

viii

AN CONTRACT

Sale Parts of Sale

## LIST OF TABLES (Continued)

PAGE

#### TITLE NUMBER Variance in Metal Resistance Measurements as a 12. 57 Function of Metal Length • Test Plan for Bond Strength Evaluation 62 13. Comparison of Pre and Post Stress Strength Distributions 14. Using Kolmogorov -Smirnov Two-sample Test 68 Comparison of Post Stress Bond Strength Distributions 15. Between Stress Samples and Control Samples 71 Relating Shear Bond Strength to Modes of Bond 16. Separation and Incidence of Stress Failures 72

#### EVALUATION

1. The objectives of this effort were to comprehensively define, through physics-of-failure studies and a test program, all of the pertinent factors that affect silicon microcircuit reliability. The end items sought in this effort were a nondestructive reliability screening procedure for failure rate improvement and acceleration factors for rapid reliability prediction for a given class of silicon monolithic microcircuits.

2. The physics-of-failure studies were concerned with oxide stability, contact and interconnect studies, and circuit analysis. The main test vehicles used in the oxide studies were MOS capacitors and MOS transistors, whereas the SN5420 was utilized in the circuit and metalization studies. Concurrent with these studies, a detailed test program was conducted to determine the operating failure modes of the SN5420 and their dependence on various electrical and environmental stresses.

3. The significant achievements resulting from this effort are specified as follows:

a. A complete nondestructive screening procedure including real cost of each screen was developed. Included in this procedure are detailed visual criteria for accepting or rejecting precapped microcircuits.

b. The bond study clearly demonstrated that bond strength varies from lot-to-lot. A shear bond test was developed to measure this variance and is presently employed by Texas Instruments as a quality control procedure.

c. Substantial proof is provided to show that the development of universal acceleration factors for monolithic microcircuits is virtually impossible.

d. A detailed circuit analysis of the SN5420 resulted in two nonconventional (not called for in manufacturer's electrical specifications) a-c tests and proved to be more sensitive preindicators of device degradation than the standard on-off d-c tests.

e. Demonstrated that a silicon monolithic microcircuit can be more reliable than the discrete transistors that make up the circuit.

f. Developed two computer programs to aid in developing screening tests for any electronic part.

g. Definition of work elements that need further investigation.

47.

Fish

Although the results of this effort were obtained from the study and testing of the SN5420, TTL dual nand gate, the major portion of the resulting techniques and definitions is applicable to any silicon microcircuit.

4. Two follow-on efforts are presently underway to optimize the screening procedure mentioned in 3.a with respect to cost and efficiency and to generalize the circuit techniques. The techniques developed in this report have been utilized in the preparation of RADC Exhibit 2867A, "Quality and Reliability Assurance Procedures for Monolithic Microcircuits," and are being utilized in preparation of the Joint DOD/NASA Standards for silicon monolithic microcircuits.

REGIS C. HILOW

Reliability Engineering Section Reliability Branch

#### SECTION I

#### **INTRODUCTION**

#### 1. SUMMARY OF REPORTS

This report is published in two volumes and is the last in a series of three reports on United States Air Force Contract No. AF30(602)-3723, prepared for Air Force Systems Command Research and Technology Division, Rome Air Development Center, Griffiss Air Force Base, New York.

One volume titled "Surface Studies"  $(RADC-TR-66-776)^{1/2}$  reports results of the fundamental oxide studies performed as a part of the physics of failure program. This volume contains results of other physics of failure studies, test programs, failure and data analysis and the integration of these studies to determine reliability screening and prediction methods for integrated circuits.

This report covers progress made during the calendar period 20 April 1966 through 19 October 1966. The work discussed in two previously published interim reports  $\frac{2}{3}$ ,  $\frac{3}{10}$  is summarized in Section II.

2. PROGRAM SUMMARY

The contract was an eighteen-month program consisting of four r for interrelated work elements.

Data Analysis and Preliminary Tests

Physics of Failure Program

Accelerated Reliability Tests

Nondestructive Reliability Screening

a. Data Analysis and Preliminary Tests

A study was conducted to analyze the reliability of the SN5420 to actermine failure mechanisms for early direction in the study.<sup>2</sup>/The analysis was supplemented by a series of short-term high-stress tests to provide additional information on failure mechanisms and gross time stress relationships. Data acquired from these studies provided information for the design of the test program.

#### b. Physics of Failure Program

The physics of failure program consisted of surface studies, contact and interconnection studies, and circuit analysis.

<u>Surface Studies</u>. Surface studies, reported in a separate volume,  $\frac{1}{}$  were primarily concerned with sodium contamination of thermal oxide on silicon. The work was concerned with linking the instability of the oxide in the metal-oxide-silicon configuration to chemical contamination levels. The final report details how the techniques of neutron activation analysis and precision profiling were applied to measurement of sodium levels in phosphorous diffused oxide as well as conventional and clean oxides. In this connection, the kinetics of thermal diffusion of phosphorous oxide in planar oxide were also detailed. Two techniques for the formation of clean oxides were discussed. Sufficient description was made to allow other investigators to repeat the work; hence some techniques for clean oxide formation have been extended to the industry at large. It was demonstrated that once a clean oxide has been produced, the problem of contamination caused by application of contacts still remains. The work describes how simple chemi-sorbed impurities may be efficiently removed with aqueous HF solution and de-ionized water washing. Further the importance of the method of metal contact application was detailed.

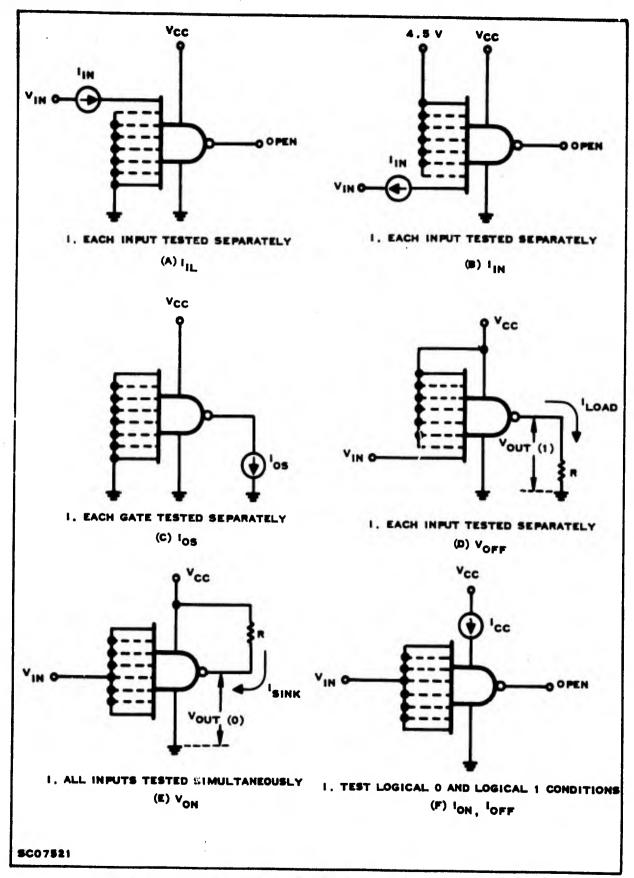

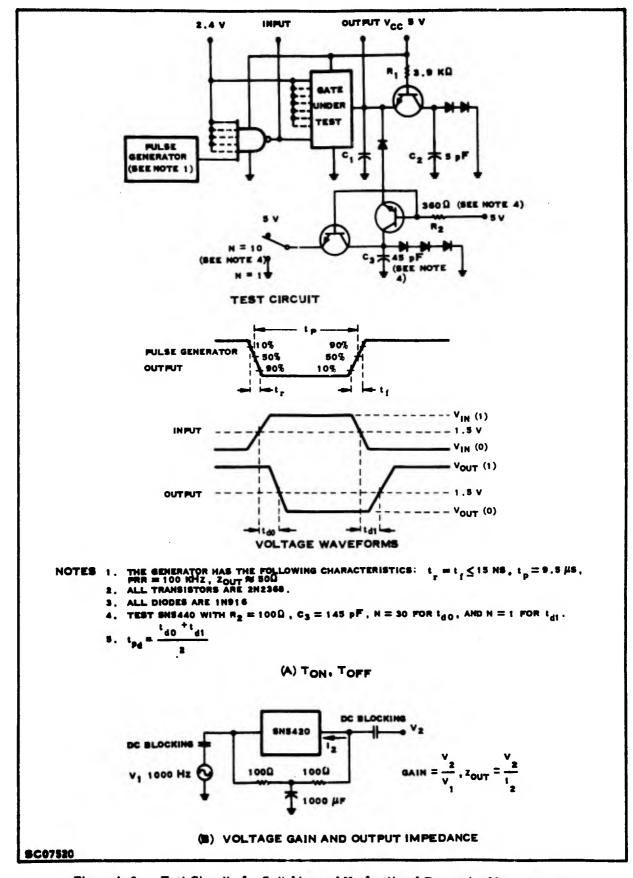

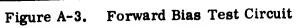

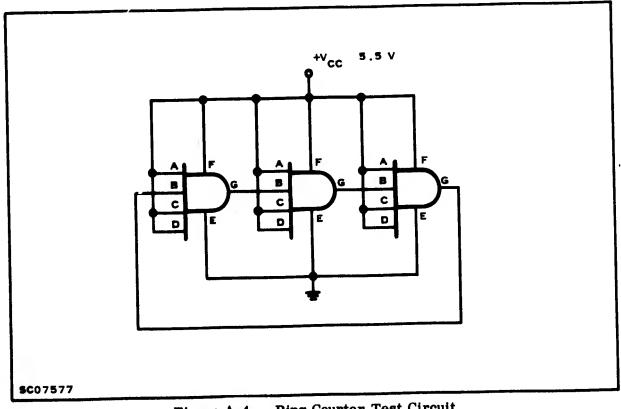

<u>Circuit Analysis</u>. A d-c analysis of the SN5420 under one set of operating conditions showed that the power dissipation was concentrated in diagonally opposite corners of the chip. From a power distribution standpoint, it appears that the circuit topology could be improved. However, such a change would probably result in increased lead resistance, shunt capacitance and possibly in crossovers. Furthermore, the actual operating stresses in a typical system probably depend more on transient effects than on steady state power dissipation. The point at which parasitic capacitance has the greatest effect on the output waveform, was identified. Any significant change in this capacitance, as a function of stress, would introduce a reliability problem. Fortunately, doping levels and applied voltages are such that this kind of change is not likely. From a power dissipation standpoint, it was found that d-c stress conditions were not particularly good approximations of use conditions wherein a device is rapidly switched between its two output states. A ring counter test with appropriate load capacitors recommended as more representative of actual use conditions was evaluated during the program. Results of this evaluation are reported in Appendix A.

Electrical measurements, voltage gain and output impedance which characterize the NAND gate as a linear device were developed as a part of the circuit studies. These measurements are referred to as non-functional since they are not specified on the standard data sheet of the device. Complete results of these circuit analysis studies were reported in a previous interim report  $\frac{3}{}$ . These measurements were used in addition to standard functional measurements to characterize devices subjected to the test program. <u>Contact Studies</u>. A study of the molybdenum-gold contact system was conducted. Results are contained in Section V of this report. Test samples were selected from the same manufacturing lots represented by devices used in the reliability test program. A study conducted to investigate bond strength and metallization adherance revealed that no significant degradation occurred as a result of high thermal and mechanical stress. However, bond strength and metallization adherence was found to be highly lot dependent. A correlation between measured bond strength, the modes by which the bonds separated, and the incidence of failure due to peeling metallization which occurred on the test program, was determined. A new technique to measure shear bond strength was used during the evaluation. This technique is included as a part of the reliability screening procedure outlined in Table I.

Additional studies were performed to evaluate voids, thin spots, scratches and metallization resistance by high thermal and electrical stresses. The emitter base junctions of transistor components were characterized during high thermal and electrical stress to detect any evidence of resistive contact formation. None was found.

## c. Test Program

Accelerated reliability tests were conducted during the program to determine the principle failure mechanisms of the SN5420 and the relationships between fixed and step stresses. The first approach to data analysis was the use of computer techniques to determine discriminant reliability screening and prediction methods suitable for incorporation into reliability specifications. It became evident early in the study that few failures could be obtained from stresses conducted as long as 1000 hours; functional electrical parameters (data sheet parameters) or combinations thereof, could be used to predict less than 10 percent of these failures. On the basis of the results, a fundamental change in the program was made. Electrical stresses were extended to 2000 hours and the levels of stress increased to the limits of device materials and test equipment capabilities. Die photographs taken prior to capsulation of the device were used to determine what visual information existed on the dice which would predict failure. While the extended stresses caused few additional failures, the study served to identify specific failure mechanisms associated with longer term stress. Photographic analysis revealed that one-third of the stress failures caused by die faults were related to visual information which existed on the dice prior to stress. This work was essential in developing the reliability screening procedure discussed in the following paragraph.

#### d. Nondestructive Reliability Screening

120

A reliability screening procedure developed during the contract for the SN5420 is shown in Table I. The effectiveness of two techniques developed from the physics of failure studies, namely shear bond strength and the nonfunctional electrical measurements, were demonstrated during the test program. In addition,

3

| Pr                       | Procedures                        |             | Effect | eness of S | creens | Effect. veness of Screens to Eliminate Failures** | the Failures |

|--------------------------|-----------------------------------|-------------|--------|------------|--------|---------------------------------------------------|--------------|

|                          |                                   |             |        | Die        |        | P                                                 | Package      |

| Screening Levels         | Techniques                        | Detail      | Oxide  | Metal      | Bulk   | Wire                                              | Die          |

| I. Precap lot acceptance | Shear Bond Strength               | Flo 27      |        | 200        |        | Dress                                             | Mounting     |

|                          |                                   |             |        | 80.8       |        |                                                   |              |

| II. Precap 100% screen   | 20X Package Screen                | Fig. 10     |        |            |        | 504                                               |              |

|                          | 70 X Die Screen                   | Table 4     | 50%    |            | 50%    | 2                                                 |              |

| III. Postcap 100% screen | Hermetic Seal*                    | Sec. IV.    |        |            |        |                                                   |              |

|                          | Electrical Measurements           | _           |        |            |        |                                                   |              |

|                          | Centrifuge - X, Z planes          | 1           |        |            |        | 404                                               |              |

|                          | Followed by X-ray                 | Fig. 10     |        |            |        | 800                                               |              |

|                          | Centrifuge - Y <sub>1</sub> plane | ,           |        | 200        |        | DOL                                               |              |

|                          | Electrical Measurements           | Table A-2   |        | 2          |        | Q.OT                                              | \$00T        |

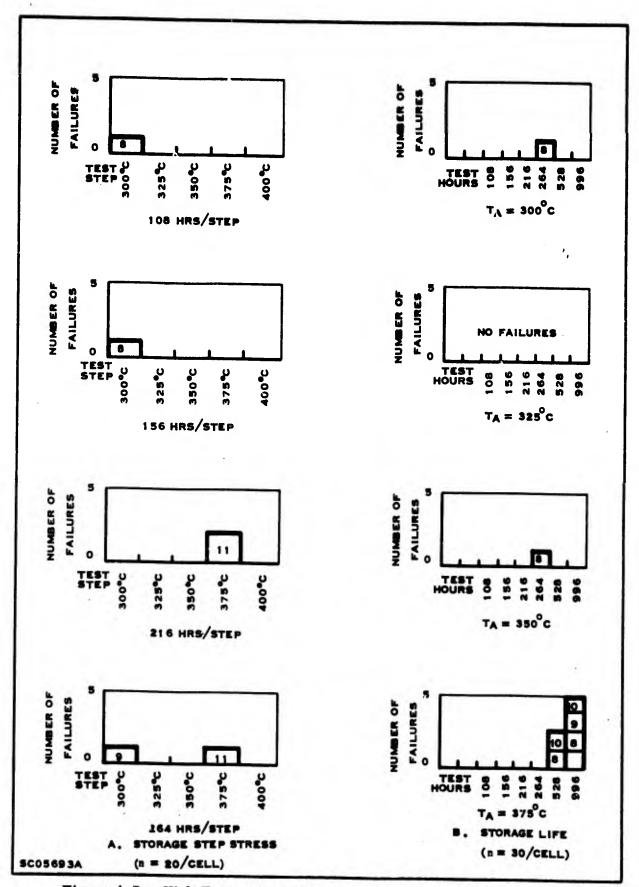

|                          | 300°C Storage-168 Hr.             |             |        |            | Snot   |                                                   |              |

|                          | Electrical Measurements           | Table A-2   |        |            | 2      |                                                   |              |

|                          | Electrical Burn-in                |             |        |            |        |                                                   |              |

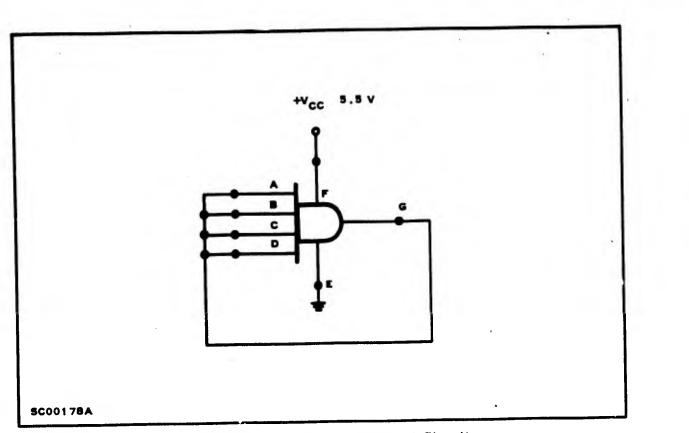

|                          | 160°C - 168 Hours                 | Figs. A-3,4 | 50%    |            | -      |                                                   |              |

|                          | Electrical Measurements           | Table A-2   |        |            |        |                                                   |              |

|                          | Hermetic Seal*                    | Sec. IV     |        |            |        |                                                   |              |

読み

Table 1. Reliability Screening Procedure for SN5420

No Failures were caused by poor hermetic seals. Refer to Section IV for discussion. \*

Effectiveness (%) = No. Failures detected by technique divided by total No. Failures X100. \*

precapsulation photographs of the devices subjected to stress were used to relate failure mechanisms to information which existed on the dies prior to capsulation. The screening procedure was developed by identifying the tailure mechanisms resulting from the test program and relating these to information which existed at the earliest point in the manufacturing cycle following the die mount and lead mount operations. The percentages shown in Table I demonstrate the effectiveness of the screens to identify failures which occurred during the stress program. The term "effectiveness" is used to describe the proportion of failures removed by the screen ing technique. This term should not be identified with the term "screening efficiency" used in this report to measure the ability of computer programs such as SERF and LINDA to discriminantly identify potential failures from a population of devices. A comprehensive discussion of the screening procedure, techniques, and cost of screening is presented in Section IV.

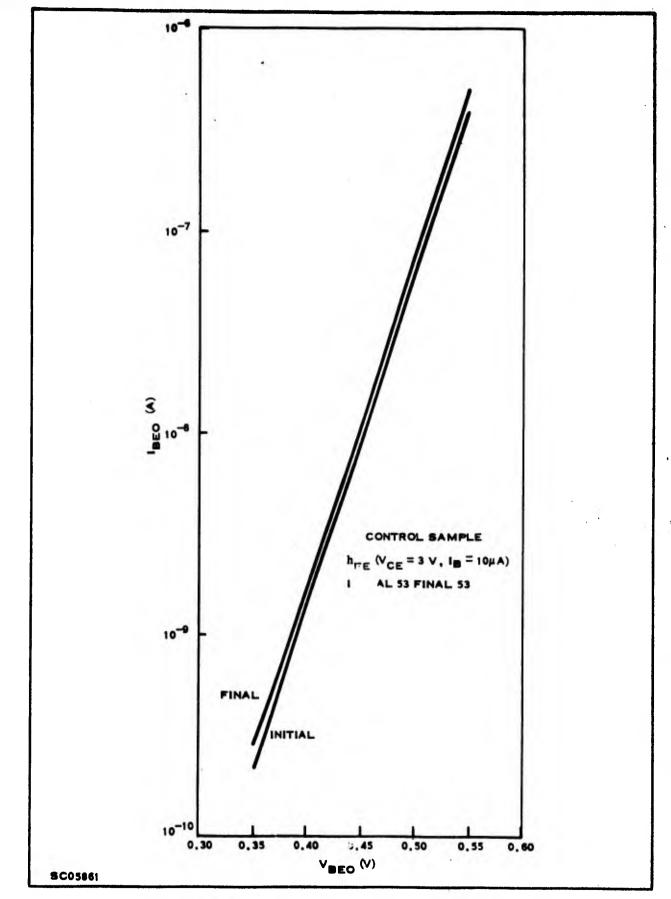

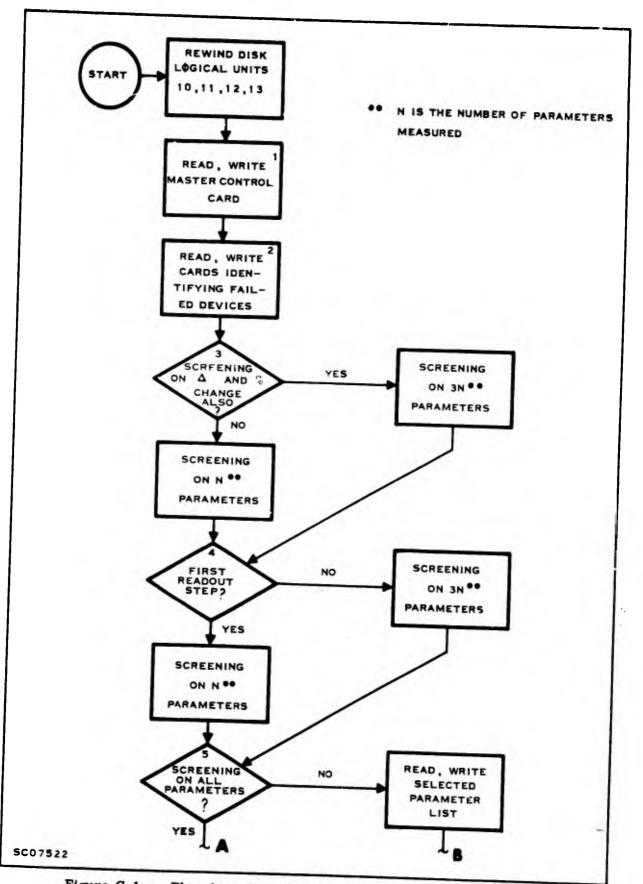

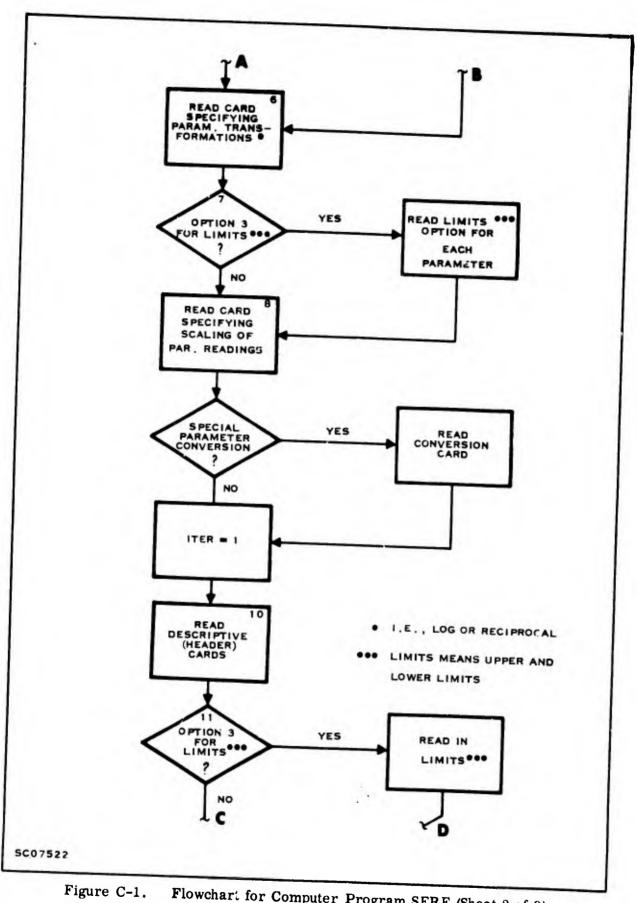

#### e. Computer Programs

The computer program SERF developed for this contract was demonstrated to be of value in isolating the preindicators of failure. It is based on the assumption that devices which are less reliable have at least one parameter whose value is higher or lower than the rest of the devices. The term "parameter" may refer to absolute values or to the change observed in the value of a parameter as a function of stress. The computer program examines the parameters of each device in the sample and selects the parameters and parameter values for the sample which optimize the screening efficiency, a term used to denote a quantitative measure of the efficitiveness of the screening procedure to eliminate failures. Screening efficiency was calculated in two ways:

$$e = \frac{\frac{\%}{7} \text{ Failures Removed}}{\% \text{ Population Removed}}$$

$e^* = 0.5 + 0.5 (F_f - F_g)$

or

where

$F_f$  = Fraction of total failures removed

$F_g = Fraction of total good devices removed$

Two other computer programs, LL<sub>N</sub>DA 1 and LINDA 2 which are based on linear discriminant analysis  $\frac{4}{}$  were written and adapted for use in the program. This method requires that a linear discriminant function be determined prior to screening the devices. The function is a weighted sum of the measurements to be used in screening; it is determined from measurements made on a group of devices, some of which are known to be stress failures, others known to have survived stress. It is assumed that the device to be evaluated is from the same general population as the devices used

5

to generate the linear discriminant function. The parameter measurements of a device in the population to be screened are converted to a value of the discriminant function. This procedure ultimately results in the division of the population into two groups, either good or bad, defined by a critical value of the discriminant function. The use of models to relate fixed and step stress and computer screening techniques to this program was severely limited for two reasons. First, few failures (5 to 10%) occurred from stresses conducted at levels far beyond the maximum ratings of the device. It was also determined that functional (or data sheet) parameters or combinations of these could be used to predict only certain types of failures, representing less than 10% of the devices which failed. However, the SERF Program was used to isolate parameters which preindicate failure for a few devices which failed high temperature storage stress. This work is discussed in Sections III and IV.

6

## f. <u>Publications</u>

The following is a list of the papers published as a result of the work performed on this contract.

H. G. Carlson, C. R. Fuller, and D. E. Meyer, "Effects of Phosphorus on Sodium Distributions in Oxides, "Las Vegas, Nevada (1965). Silicon Interface Specialist's Conference (SISC)

H. G. Carlson, C. R. Fuller, and J. F. Osborne, "Effects of Phosphorus Diffusion on Sodium Concentration Profiles in Thermally Grown Silicon-dioxide Films," Buffalo, New York, (October, 1965). Electro-chemical Society (ECS)

H. G. Carlson, G. A. Brown, C. R. Fuller, and J. F. Osborne, "Effects of Phosphorus Diffusion in Thermal Oxides on the Elevated Temperature Stability of MOS Structures," 1965 Physics of Failure in Electronics Symposium (November, 1965). Published in Volume 4 of <u>Physics of Failure in Electronics</u>, Defense Documentation Center, Cameron Station, Alexandria, Virginia. AD No. 637 529

H. G. Carlson, C. R. Fuller, J. F. Osborne and G. A. Brown, "Stability of Etched Oxides," The Electrochemical Society Meeting, Philadelphia, Pa. (October 1966).

H. G. Carlson, V. Harrap, and J. F. Osborne, "Sodium Free Oxides," Electrochemical Society Meeting, Philadelphia, Pa. (October 1966).

H. G. Carlson, D. E. Meyer, C. R. Fuller, V. Harrap, J. F. Osborne and G. A. Brown, "Clean MOS Systems," Fifth Annual Physics of Failure in Electronics Symposium, (November, 1966). To be published in Volume 5 of <u>Physics of Failure in</u> <u>Electronics</u>, Defense Documentation Center, Cameron Station, Alexandria, Va.

Walter L. Gill and Wilton Workman, "Reliability Screening Procedures for Integrated Circuits," Fifth Annual Physics of Failure in Electronics Symposium, (November, 1966). To be published in Volume 5 of <u>Physics of Failure in Electronics</u>, Defense Documentation Center, Cameron Station, Alexandria, Va.

D. F. Meyer, "Retention of HF on Surfaces Common to Silicon Devices - II," Cleveland, Ohio (May, 1966). Electro-chemical Society (ECS)

#### SECTION II

#### **PROGRAM REVIEW**

#### 1. INTRODUCTION

This section highlights results of the work discussed in two interim reports relative to this contract. These are identified by the following report numbers:

RADC-TR-65-463 — Technical Documentary Report I  $\frac{2}{}$

RADC-TR-66-345 – Technical Documentary Report II  $\frac{3}{}$

## 2. TEST VEHICLE $\frac{2}{}$

The SN 5420 dual four input NAND gate was studied throughout the program. The logic equation of the circuit is  $E = \overline{ABCD}$ . The device is fabricated on a single chip using the diffused isolation. The molybdenum-gold expanded contact system was used with the device, which is packaged in a fourteen-pin metal flat pack.

3. CIRCUIT ANALYSIS  $\frac{3}{}$

#### a. <u>Objective</u>

The objective of the circuit studies program were to determine the design factors which affect reliability of integrated circuits and to develop electrical measurements which are more sensitive to degradation and more useful for reliability prediction than standard functional tests. These studies were divided into three main parts; dc analysis, small signal analysis and a transient analysis.

b. DC Analysis

The dc analysis was performed under conditions representing a compromise between the on and off state encountered in an actual system. The ECAP computer program was utilized in this study. The power dissipated in each of the elements of the circuit was calculated and it was determined that the layout of the silicon chip was such that most of the power was dissipated in two diagonally opposite corners.

#### c. <u>Small Signal Analysis</u>

The operating level used in the dc analysis was used in conjunction with the small signal analysis to develop nonfunctional parameters which might be significant degradation indicators. Two useful parameters, circuit gain and output impedance, were determined from this study. The term "nonfunctional" is used to identify these parameters separately from the standard parameters which are used to specify electrical performance of the device. The measurements are affected by changes in current gain of three transistors and in the values of three resistors in the circuit. They were implemented into the main test program and used to study degradation phenomena in devices subjected to stress. Refer to Section III for discussions of this work.

## d. Transient Analysis

The main purpose of this study was to determine the effects of the various parasitic elements within the circuit. Both theoretical and measured output wave forms were obtained. Parasitic capacities were evaluated and it was determined that the frequency of a square-wave input is increased, the instantaneous power dissipated during switching may become significant. The instantaneous power dissipation in each component was calculated and it was determined that significant power pulses are present in the output and phase splitting transistors. The results indicated that for a squarewave drive at 50 MHz the average power dissipated by the circuit is about three times the low frequency power. It was further determined that from a power dissipation standpoint it appeared that de stress conditions are not particularly good approximations of use conditions wherein a device is rapidly switched between two output states. A ring counter test with appropriate load capacitors is more representative of actual use conditions. A stress test was performed to evaluate the effect of added power due to load capacitance on reliability. Results of the test are presented in Appendix A.

# 4. FAILURE DEFINITION AND STRESS CIRCUIT ANALYSIS<sup> $\frac{2}{}$ </sup>

A study of functional parameters was conducted to determine parameter failure limits on the basis of device physics. These limits were used throughout the test program.

An analysis of the ring counter, forward bias, and reverse bias stress circuits used in the test program was also performed. Nominal values of voltage and power dissipation for each component in the circuit were specified.

# 5. DATA ANALYSIS AND PRELIMINARY TESTS<sup>2/</sup>

At the beginning of the program a study was conducted to analyze reliability data of integrated circuits from other sources such as the Component Quality Assurance  $\frac{5}{100}$  This study was conducted to determine failure mechanisms for early

direction in the study. The analysis was supplemented by a preliminary investigation consisting of short term high stress tests to provide a preliminary identification of failure mechanisms and gross time-stress relationships directly applicable to the SN5420. Data acquired from the study provided information for design of the test program. The preliminary investigation indicated that it was not possible to predict device failure at high stress levels from lower stress data. Results further indicated that design of the test program should include an increase in both stress levels and duration.

## 6. TEST PROGRAM

As a result of the preliminary investigation, the test program was designed utilizing high level fixed and stress step tests.

## a. <u>Step Stress Series $\frac{3}{}$ </u>

The first replicate of the test program consisted entirely of step stress tests. Temperatures for operating tests ranged between 140°C and 200°C. Storage step stress was performed between 300°C and 500°C. Constant acceleration step stress was also performed. Devices which did not fail catastrophically were marked by extreme stability of their electrical parameters. Short-term electrical stress did not produce a significant number of failures even though stress temperatures greater than 200°C were employed. Analysis of very limited data indicated that devices specially processed to contain oxidative oxide did not differ appreciably from the standard production units and their response to stress. It was further demonstrated that few failures were being generated with tests other than storage and constant acceleration. A typical electrical stress test involving 15 devices produced two failures. Stress equipment limitations prohibited the increase of stress temperature, and secondly, since a study of device failure criteria indicated that few if any additional failures could be obtained by tightening the failure criteria, an additional test was performed to extend the time for which stress was applied to the devices. The devices were placed under the same stress which had been applied before but the temperature was maintained at 200°C for 264 hours. Special tests indicated that none of the devices exceeded any of the parameter failure criteria. In fact, the change in the parameter value was so small that any meaningful redefinition of the failure criteria would still not indicate any failures. The additional 264 hours on a special test gav.) a maximum total stress time of 744 hours on the device. As a result a second test, the Fixed and Step Stress Series was designed using 2000 hours as a maximum time for stress. 2/

## b. Fixed and Step Stress Series 3/

The design and performance of this program followed completion of the Step Stress Series. 2/ To aid in the development of the reliability screening procedure for integrated circuits, devices were subjected to a photographic analysis

11

just prior to capsulation. Anomalies observed from the photographs were categorized into 15 groupings. Results of studies performed to relate stress failures to information obtained from the photographic analysis are contained in Appendices A and D of this report. A visual die inspection procedure discussed in Section IV was developed from this work.

## 7. COMPUTER PROGRAMS $\frac{3}{2}$

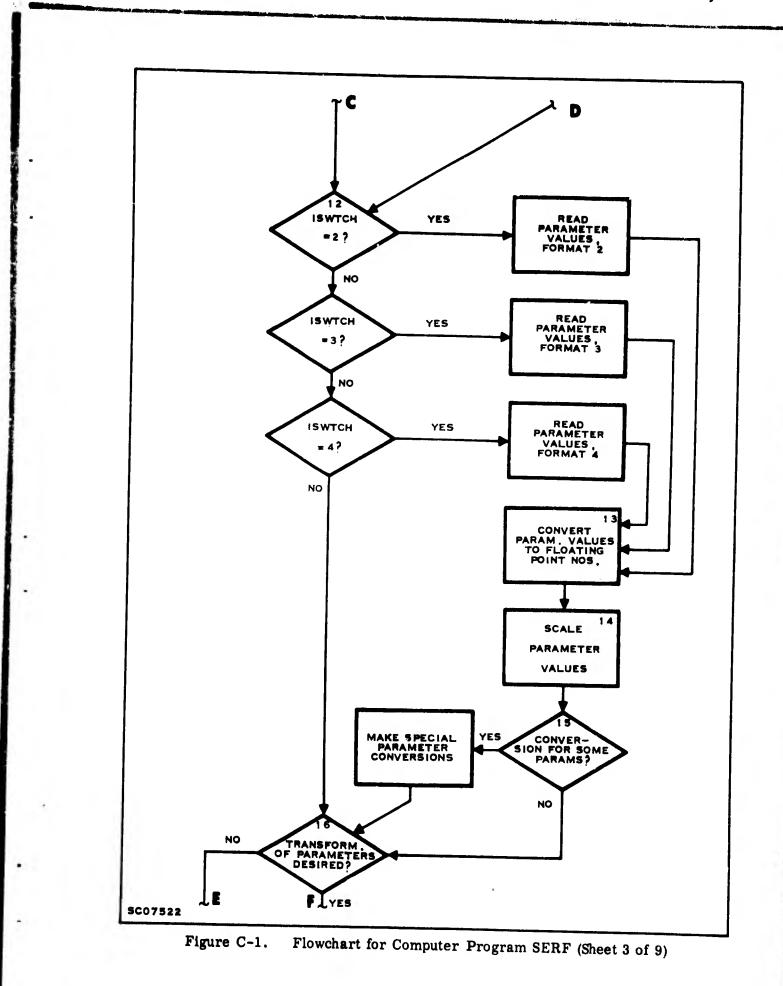

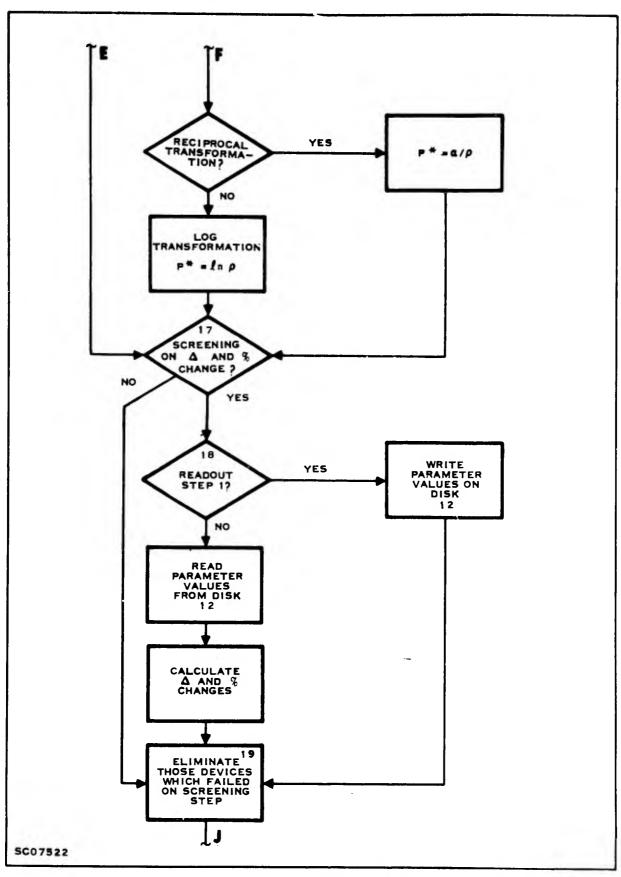

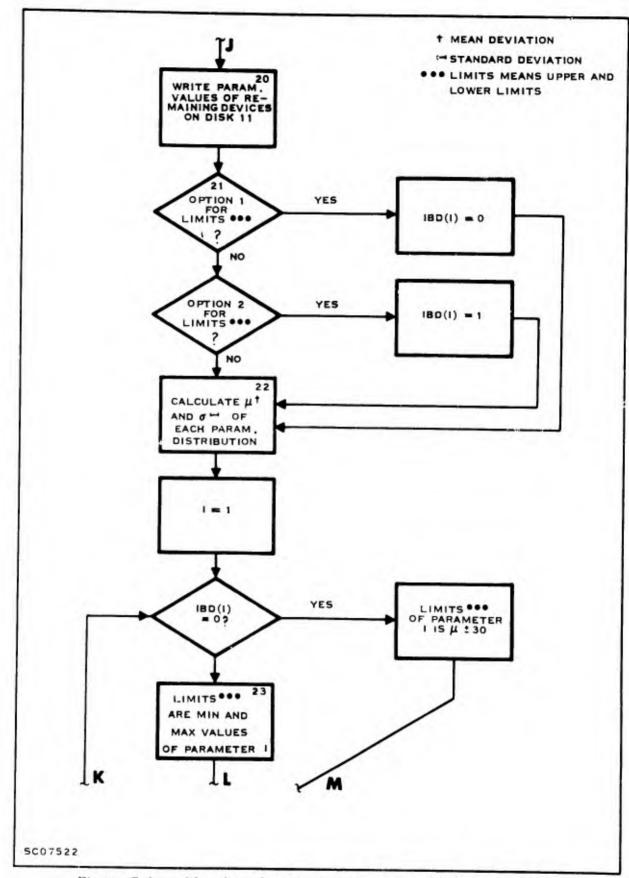

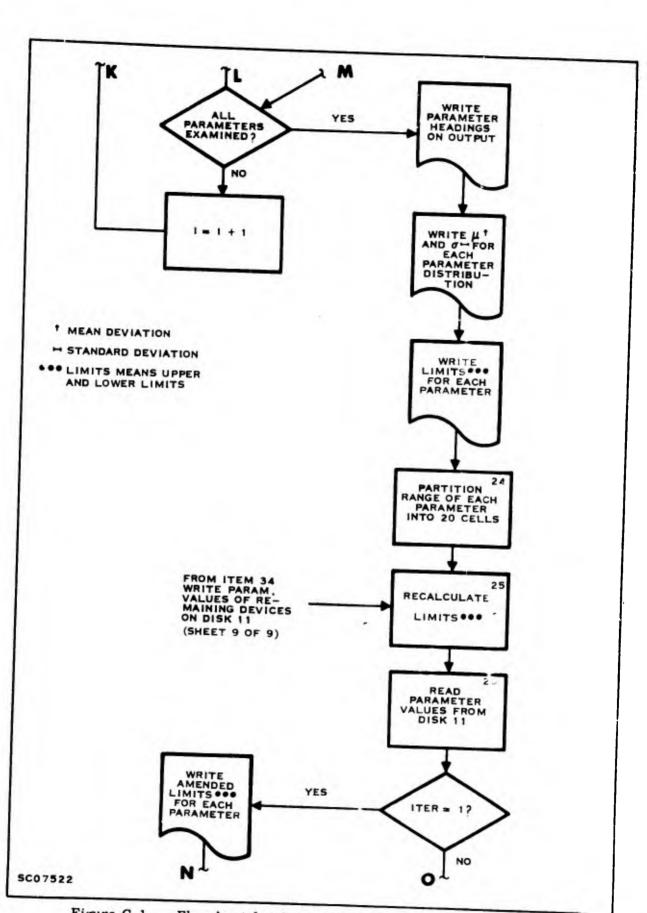

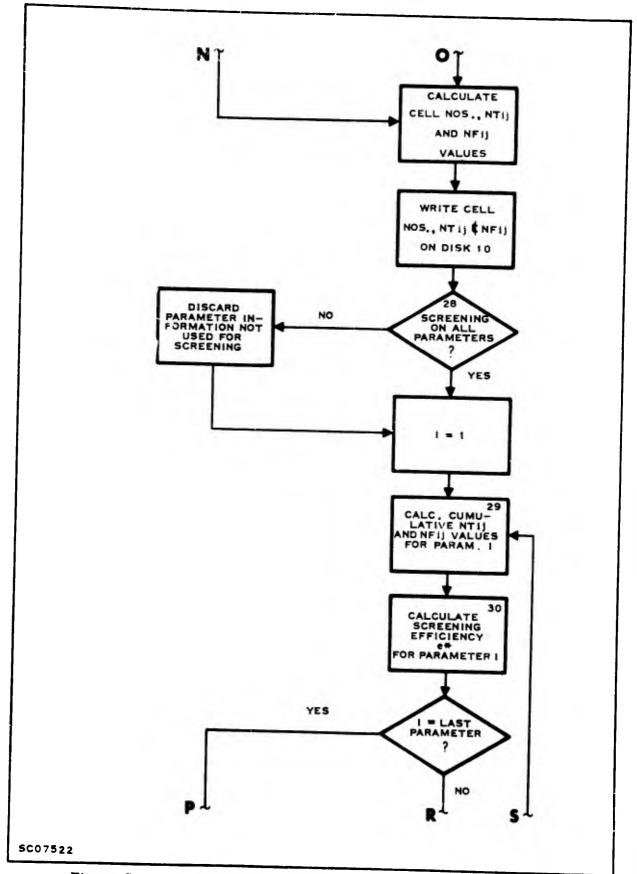

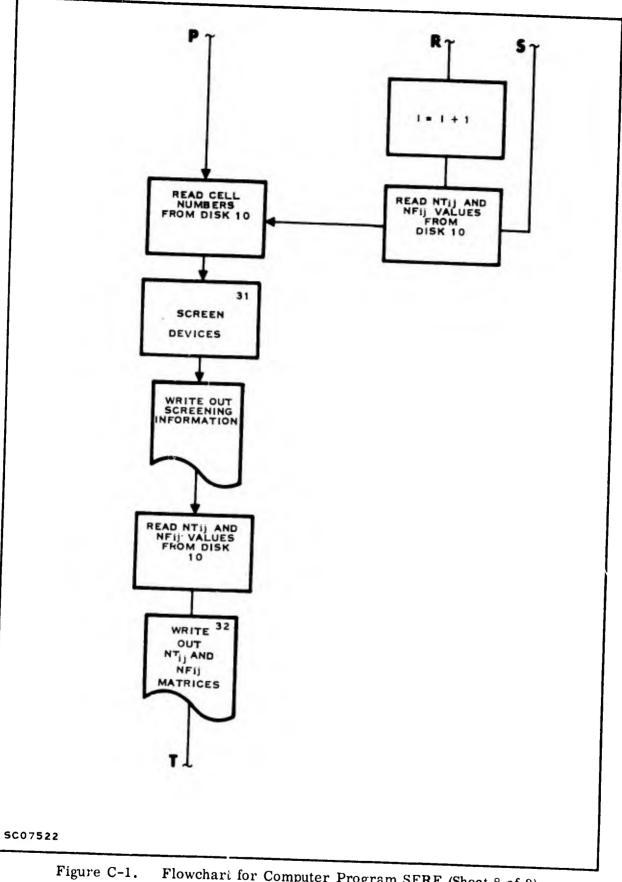

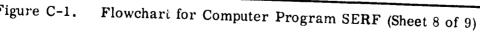

Three computer programs have been written for the analysis of the data generated on this program. SERF (Screening Efficiency Reliability Factors) determines from the input data the relative screening efficiencies of up to 40 measured parameter values as well as delta and percent change of these values, a total of 120 parameters on up to 100 components. Parameters predicting failure are isolated and the screening levels for these parameters are determined. LINDA I (Linear Discriminant Analysis) determines the weighting factors  $\lambda$  in the linear discriminant function

$$U = \sum_{i=1}^{m} \lambda_i P_i$$

(P are parameter values) as well as that value of U which gives maximum discrimination between the good and bad devices of a population. It is assumed in using LINDA 1 that the covariance matrices of the good and bad devices are identical. However, a more sophisticated program, LINDA 2, does not make this assumption. A complete description of SERF and LINDA are contained in Appendix C of this report.

#### SECTION III

## TEST RESULTS AND ANALYSIS

#### 1. INTRODUCTION

In this section, data is presented to demonstrate the results of screening using the SERF Computer Program, behavior of nonfunctional parameter measurements as a function of stress, and the highlights of the test program and related failure analysis activities. The reader is referred to Section II for a review which summarizes the results of work reported in two previous interim reports.  $\frac{2}{3}$  The items listed below are frequently referred to in the discussions which follow and serve as guides to more detailed information concerning the individual topics.

- a) Test Program Preliminary Investigation  $\frac{2}{(\text{Section II})}$ ; Step Stress Series  $\frac{3}{(\text{Section II})}$ ; Fixed and Step Stress Series (Appendix A); and Component Evaluation (Appendix B).

- b) Failure Analysis (Appendix D)

- c) Functional Parameters and Failure Limits  $\frac{2}{(\text{Appendix A})}$

- d) Nonfunctional parameters  $\frac{3}{3}$  (Section II)

- e) Theory Relating Fixed and Step Stress (Appendix E)

- f) Computer Programs (Appendix C)

2. MEASUREMENT ERROR DETECTION AND CONTROL

To detect and/or minimize errors in parameter measurements equipment mal--functions and faulty mechanical contacts, procedures to determine the variations in data due to these causes were followed for all of the tests conducted during the program. The procedures may be separated into two categories, error detection and error control.

Error detection consists of conducting measurements on unstressed control samples while simultaneously measuring stressed samples. Variations attributable to measure error can be detected by analyzing the repeated measurements taken on the "control" samples. This procedure is followed when the measurement technique is limited primarily to the laboratory or where a predetermining measurement failure criteria for the stressed samples is not specified. Examples of the types of evaluations in this program in which this approach was utilized are contact studies (Section V) and nonfunctional gain and output impedance parameters (this section).

The error control contains all the elements of error detection, but also incorporates additional procedures to control the accuracy of the measurements. This approach to error minimization was used in the test program where failure limits were assigned to parameters of the SN5420. Prior to conducting the test program, repeated measurements on the control samples were accumulated over a period of several days. The average  $(\bar{X})$  and range (R) of each of the parameters was calculated. This data from the control sample served two purposes. First it was used to demonstrate that limits used to define failure were not significantly affected by measurements taken on test samples were accurate, within the previously defined range of measurement error. When deviations in the control data occurred, corrections were made to the equipment to bring the control measurements back within the required range.

#### 3. SERF SCREENING RESULTS

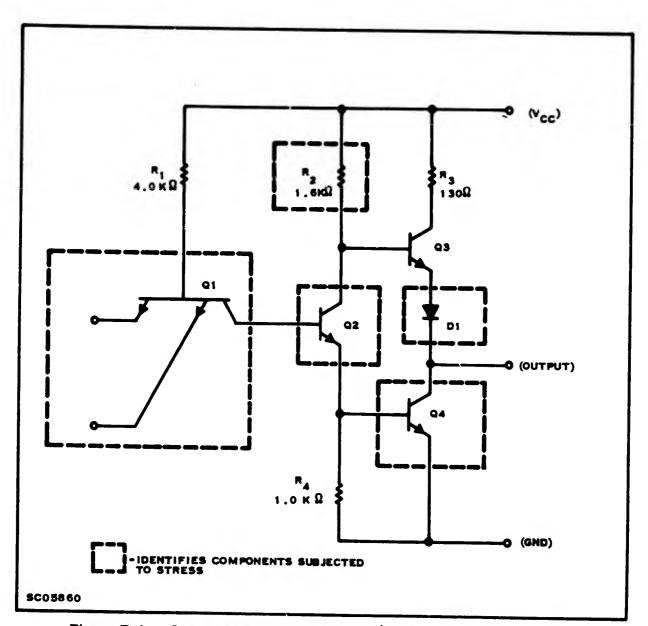

Application of the SERF program to results of high temperature storage data has revealed that short circuit output current (Ios) is an effective screening parameter. Previously reported analyses of the preliminary investigation indicated that a screening level of 33.9 mA could be used to eliminate 50% of the failures which occurred during storag: step stress. Analysis of data from the Fixed and Step Stress Series revealed that six devices degraded on Ios during high temperature storage. Failure analysis traced the cause of degradation to an increase in R<sub>2</sub> and R<sub>3</sub> resistor values (Refer to Appendix B for circuit diagram). The degradation was more greatly pronounced in the measurement of the nonfunctional output impedance and was evident at much earlier steps of applied stress. However, similar changes in the nonfunctional measurements of good devices were also observed and are discussed later in this section. Five of these six failures were predicted by the SERF computer programs discussed in the following paragraphs.

The six failures were located in five of the high temperature storage stress cells defined in Table A-1 of Appendix A. The criterion used to define failure was  $\pm 20\%$ change in the Ios parameter. To evaluate SERF, the Ios failure criteria was changed to  $\pm 15\%$  and applied to all of the cells to determine whether more failures could be generated. Twenty-one new failures were defined in this manner all of which occurred in the high temperature storage cells. In all cases, the measurements taken prior to stress were used for prediction. The results of analysis to determine the preindicators of failure for those devices is summarized in Table 2.

|                         | T anna T                                                                                                 |                | DELLE DUTODING THE DUTODING     |                                               |                                                |

|-------------------------|----------------------------------------------------------------------------------------------------------|----------------|---------------------------------|-----------------------------------------------|------------------------------------------------|

| Test                    | Screening<br>Conditions                                                                                  | Sample<br>Size | No. of<br>Failures<br>In Sample | No. of<br>Failures<br>Removed<br>By Screening | No. of Good<br>Devices Removed<br>By Screening |

| Storage Step Stress     |                                                                                                          |                |                                 |                                               |                                                |

| 108 Hours/Step          | T <sub>ON</sub> 2 9.9 ns                                                                                 | 20             | ~                               | 8                                             | -                                              |

| 156 Hours/Step          | T <sub>ON</sub> 2 8.6 ns                                                                                 | 20             | 4                               | +                                             | T                                              |

| 216 Hours/Step*         | (a) V <sub>OFF</sub> ≤ 2.7 V<br>or<br>(b) I <sub>O8</sub> ≥ 39.3 mA                                      | 20             | 9                               | ø                                             | 8                                              |

| 264 Hours/Step          | Т <sub>ОN</sub> ≥ 8.6 пв                                                                                 | 20             | п                               | 6                                             | 8                                              |

| Storage Life<br>375°C * | <ul> <li>(a) I<sub>IN</sub> &lt; 1.16 mA</li> <li>or</li> <li>(b) I<sub>IL</sub> &gt; 11.1 μA</li> </ul> | 30             | 9                               | 4                                             | m                                              |

\* Device is eliminated by screening if at least one of the two conditions are satisfied.

For example, the table reveals that all of the failures on the 216 hours/step test were removed together with two good devices by screening on  $V_{off}$  only. Nine of the eleven failures on the 264 hours/step test were removed together with two good devices by screening on the  $T_{on}$  switching parameter. The prediction results can be considered very good when considering that screening was done on initial data while most of the failures occurred after 500 hours of stress. It must be emphasized that the screening criteria are based on small samples and only two manufacturing lots (represented by the Preliminary Investigation and Fixed and Step Stress Series). Additional experimentation and analysis is necessary before definite screening criteria can be established.

# 4. ANALYSIS OF NONFUNCTIONAL MEASUREMENTS

The nonfunctional voltage gain and output impedance parameters discussed in Section II have revealed some interesting information about the stability of circuit components (transistors, resistors, etc.) during stress. Previously reported analyses of functional  $\frac{2}{2}$  and nonfunctional  $\frac{3}{2}$  measurements indicated that functional parameters are relatively insensitive to certain types of changes in component parameter values such as transistor  $h_{fe}$  degradation, when compared to the nonfunctional measurements. In the following discussions the results of analyses of the nonfunctional measurements taken during the Fixed and Step Stress Series are presented. The reader is referred to Appendix A for the description of the test circuits.

In the discussions which follow the term stress cell, ring counter and forward bias are used frequently. Stress cell refers to a particular stress to which a small sample (20 to 30 device) were subjected during the Fixed and Step Stress Series discussed in Appendix A. Ring counter and forward bias refer to two modes of electrical stress used throughout the test program. An analysis of these stress circuits was presented in a previous report,  $\frac{2}{}$  while circuit diagrams may be found in Appendix A.

a. Voltage Gain

The study of voltage gain was conducted by assigning to the measurement an arbitrary failure criteria of percent change relative to initial values. A device was defined as a failure in the following ways (there are two gates per device).

- 1)  $\pm 10\%$  and  $\pm 20\%$  change Gate 1

- 2)  $\pm 10\%$  and  $\pm 20\%$  change Gate 2

- 3)  $\pm 10\%$  and  $\pm 20\%$  change Either Gate

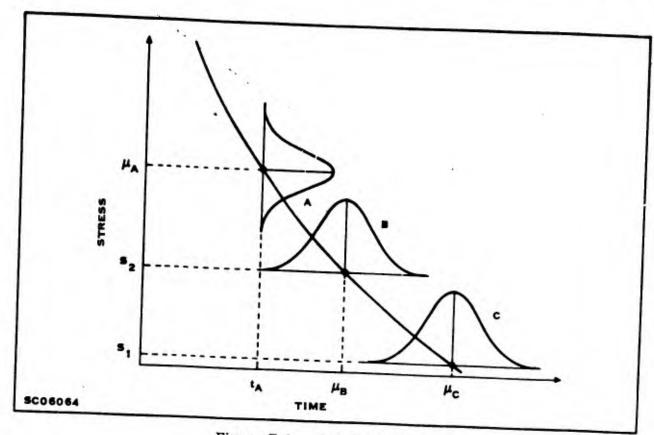

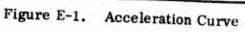

Failures were observed in every stress cell of the Fixed and Step Stress Series. The approach to the analyses was to find the distributions of failures as a function of time and temperature and to calculate activation energy. A theoretical discussion of

activation energy and the relationships between fixed and step stress is contained in Appendix E.

Distributions of failures which are lognormal in time were noted in some cases while discontinuities were observed in others. Degr. dation, which can be both circuit and design dependent  $\frac{2}{}$  is believed to have confounded the results. Curves representing the forward bias life tests, forward bias step stress tests and ring counter life tests are reproduced in this report.

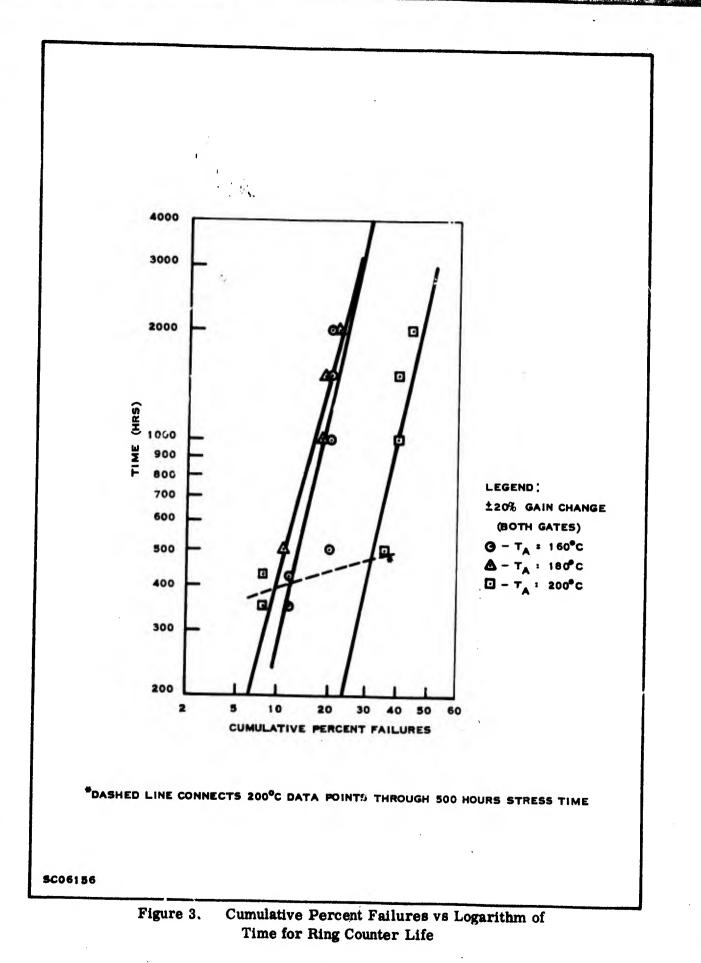

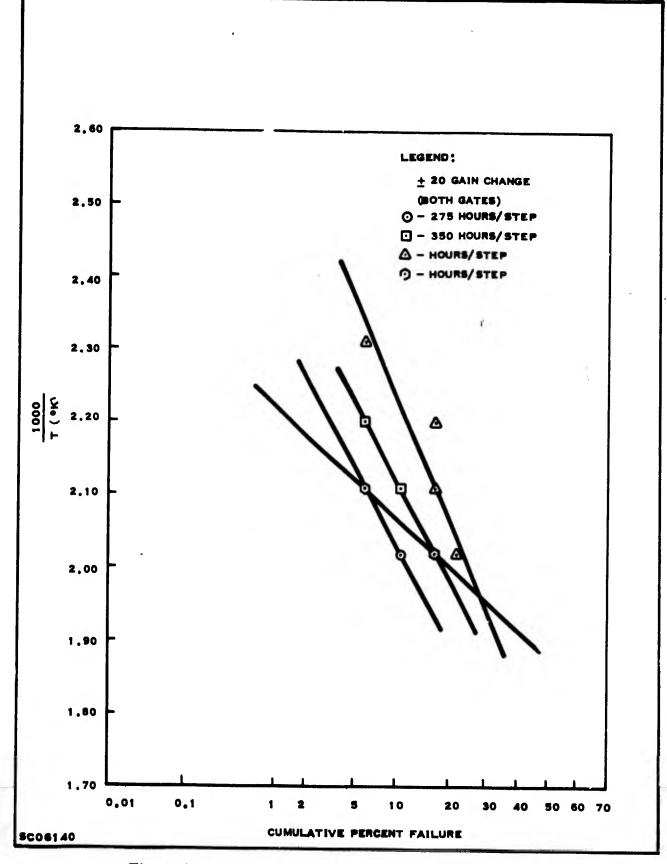

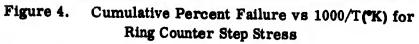

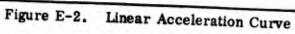

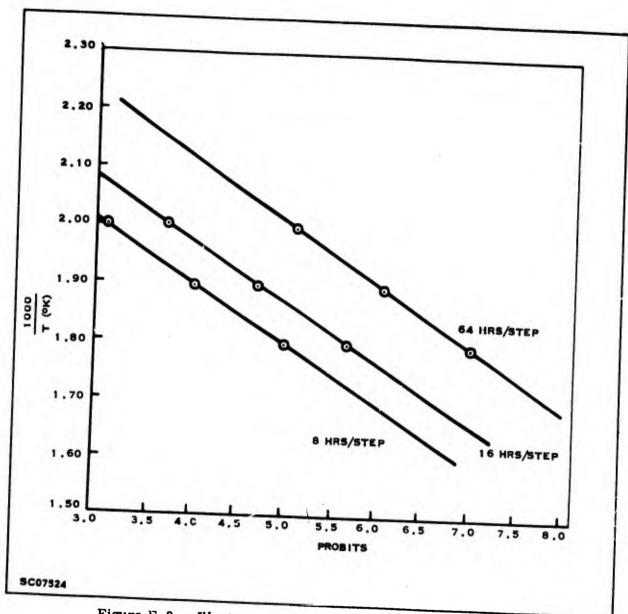

In Figure 1, the four cumulative percent failure curves are drawn for forward bias life test; the actual points are shown with each curve. These curves are summarized into one graph shown in Figure 2. Figures 3 and 4 show the cumulative percent failure curves for ring counter life and step stress, respectively. Finally, in Figure 5, the acceleration curves for ring counter life and step stress are given. The acceleration curves were used to determine a possible pattern to the ac gain failures, and whether a relationship between fixed and step stress existed. An activation energy which is disucssed in the following paragraph was calculated to obtain information about the mechanism causing change in the parameter values. It should be noted that the majority of devices represented by the data did not fail any functional parameters during stress.

The step stress data points in Figure 5 for the cumulative 10 and 20 percent failure yield a reasonably good fit to a linear acceleration curve. However, the correlation between the step stress and fixed stress data is not good. The lines connecting the 200°C and 180°C life test points for 10 and 20 percent cumulative failure are entirely different from the step stress lines. The dashed line shown in Figure 3 connects the data points observed through 500 hours for 200°C life test failures. The slope of this line is obviously quite different from the line connecting the 500 to 2000 hour data. Using the former curve (dashed line) to obtain 10 and 20 percent failure points, a reasonably good fit to the step stress data of Figure 3 is obtained as illustrated by  $\diamond$ 's on Figure 5. Using the step stress data, an activation energy of approximately 0.23 eV for the  $\pm$  20 percent gain failures is obtained from the forward bias life test data. Approximately the same value is obtained from the forward bias life test data (Figure 2). The gain measurement is known to be sensitive to changes in resistor values and transistor hFE's of the circuit components. 3/ Tests conducted on circuit components, discussed in Appendix B, revealed that transistor  $h_{FE}$  degradation occurred during electrical stressing; efforts to characterize the degradation and to determine a possible failure mechanism are discussed. However, during the test program, no failures defined by functional parameters were caused by transistor hFE degradation, nor was the nonfunctional gain parameter found to preindicate functional failures in the devices.

Of Time for Forward Bias Life

Χ.

1997 - S. A.

休息

22

## b. <u>Output Impedance</u>

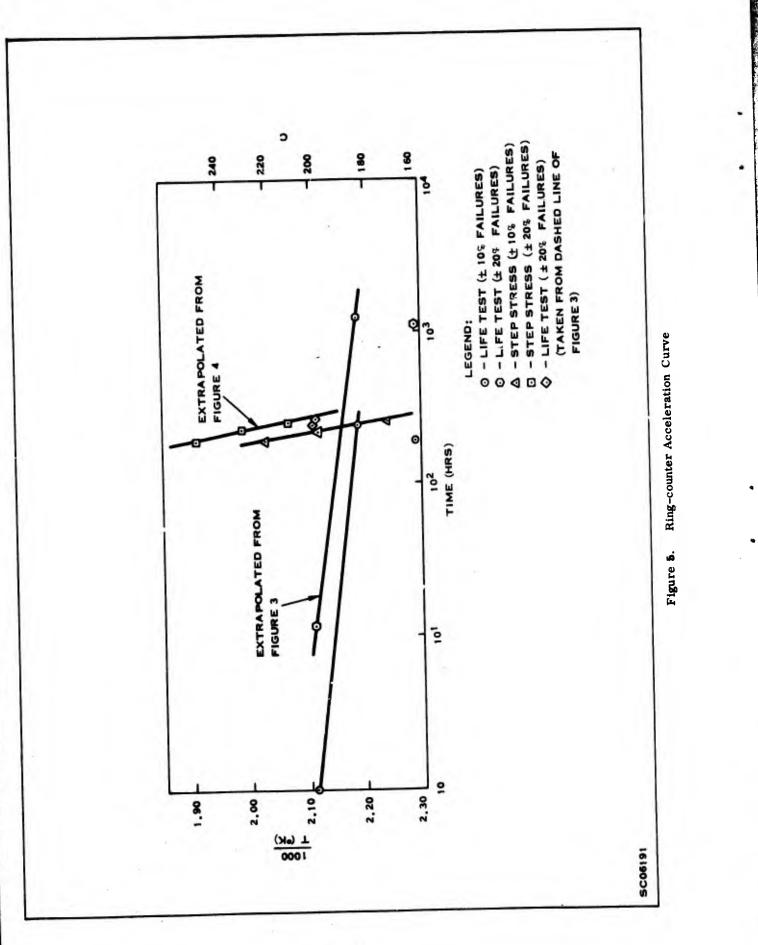

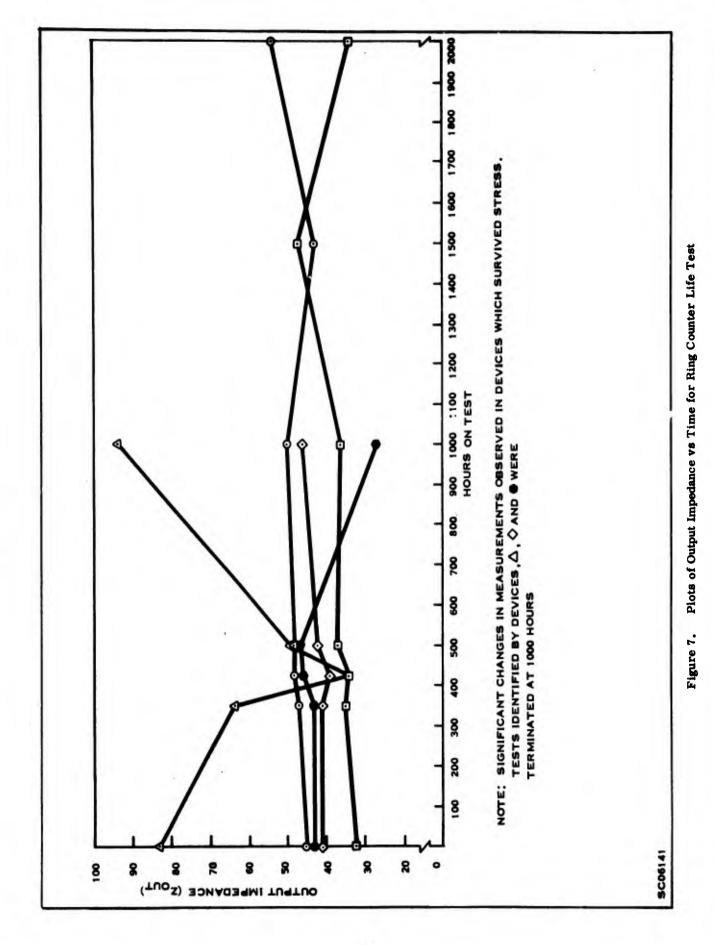

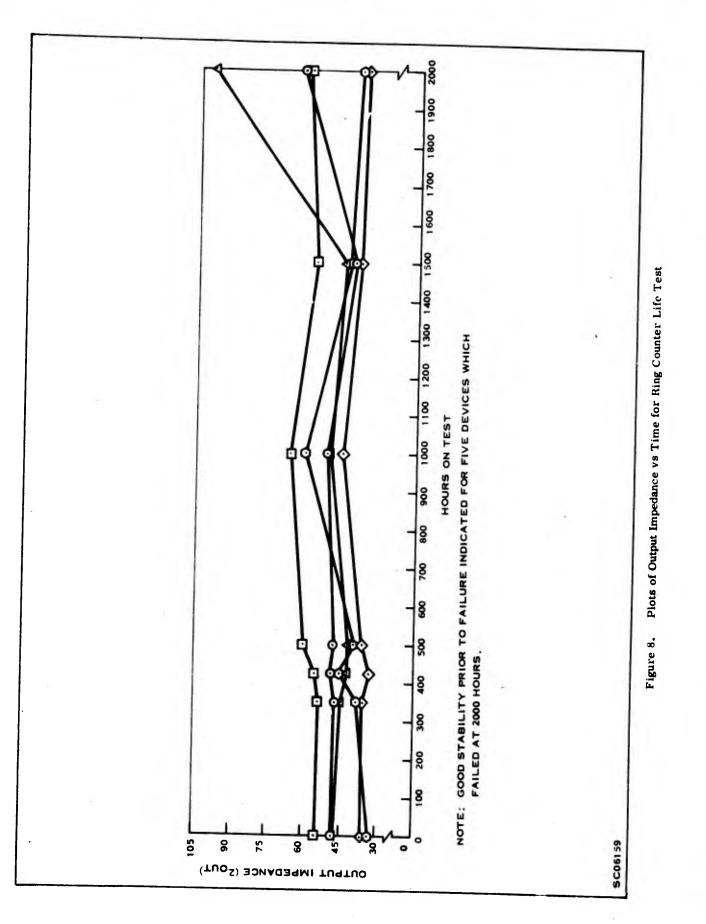

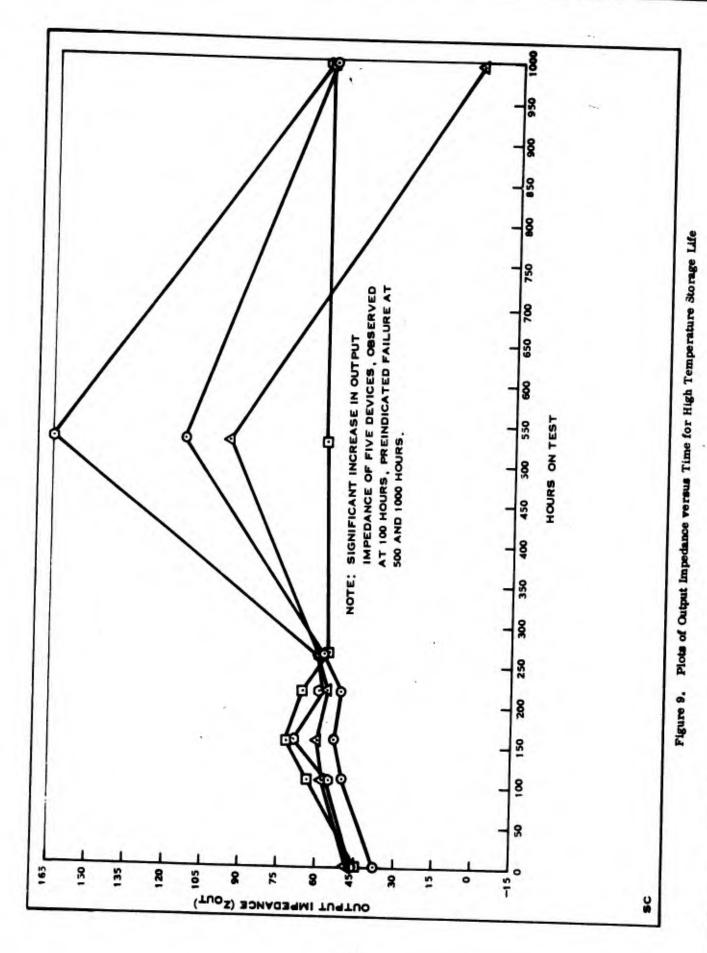

An analysis of the behavior of output impedance was performed to determine the effectiveness of the parameter to preindicate failure in functional devices. Curves showing the variation of output impedance with time were made for many devices subjected to stress. A few of these are presented in Figure 6 through Figure 9 to illustrate the results. Figure 6, shows curves for five devices which did not fail 2000-hour life test; these demonstrate good stability of the particular devices represented. However, Figure 7 demonstrates how considerable variation in the measurements of good devices can occur. Figure 8 illustrates how the measurements of devices which fail late in stress life can be well behaved prior to failure; all of these devices were found to be functional failures at 2000 hours (final stress interval), but there was no apparent preindication of failure. Figure 9 illustrates how output impedance can preindicate failure; all of these devices failed storage life test at either 500 or 1000 hours. A significant increase in output impedance was observed, however, after only 100 hours of stress. While the output impedance measurements were not found to discriminantly predict failure, their sensitivity to component parameter changes, not detectable by functional measurements, has been demonstrated.

#### -5. ANALYSIS OF STRESS FAILURES

The significant results of failure analysis are listed in Table 3, according to the type of stress causing failure. Few failures occurred from storage and electrical stress even though the minimum stress levels used were above the maximum ratings of the devices. The dominant mechanisms observed in failures from the Preliminary Investigation, Step Stress and Fixed and Step Stress Series differed considerably as shown in Appendix D (Table D-1).

Sixty percent of the Preliminary Investigation failures were caused by photo lithographic faults and die delamination. A production change to improve die mounting eliminated recurrence of this mechanism.

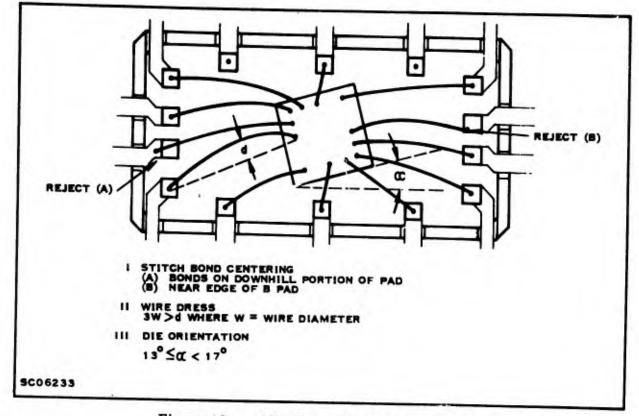

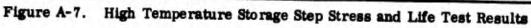

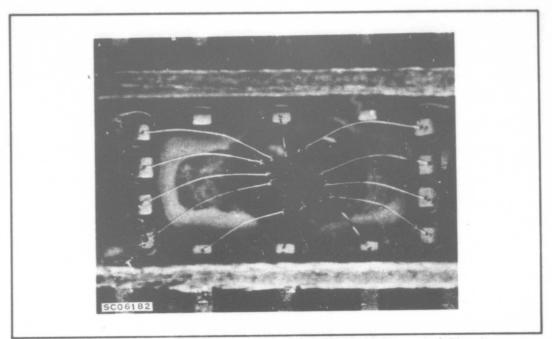

Seventy-five percent of the Step Stress Series failures were caused by ball bond separation and die and wire dress problems. Analysis of X-rays revealed the dice were oriented improperly in the package, decreasing the minimum separation between bond wires. Constant acceleration caused the wires to touch, which resulted in failure.

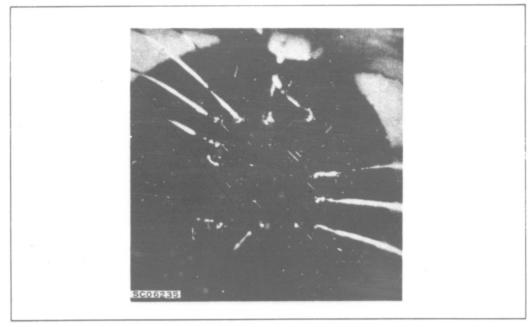

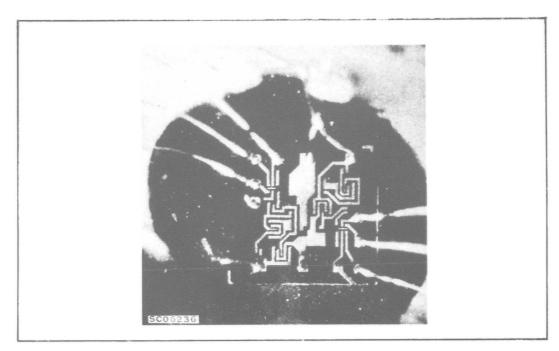

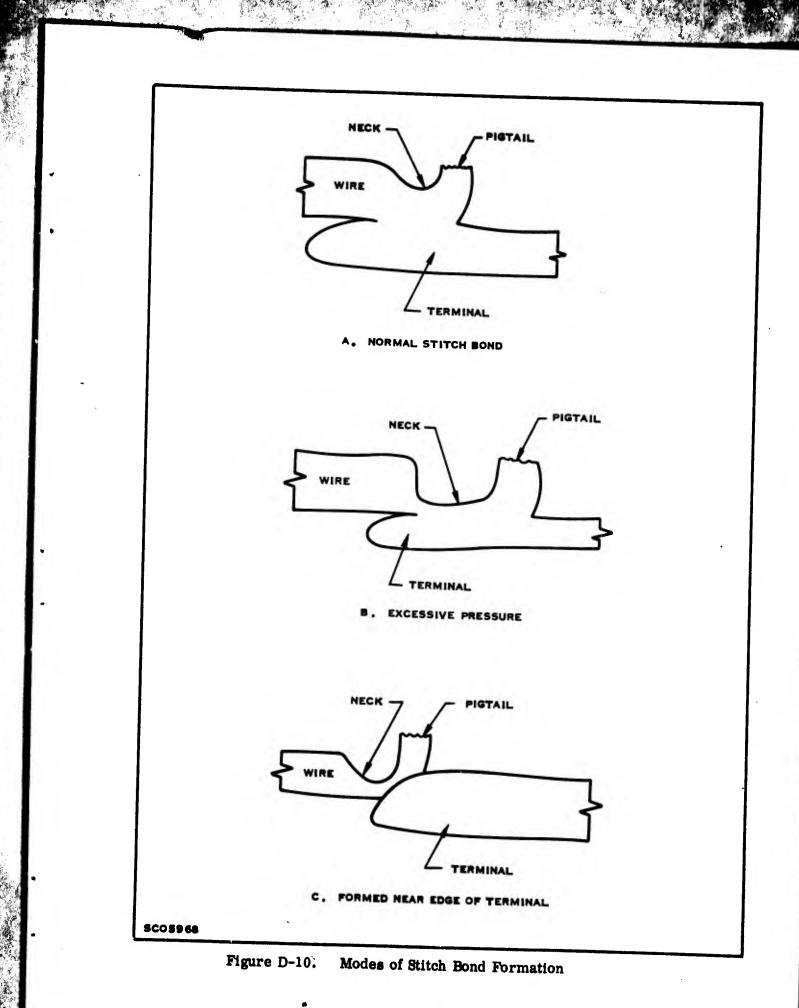

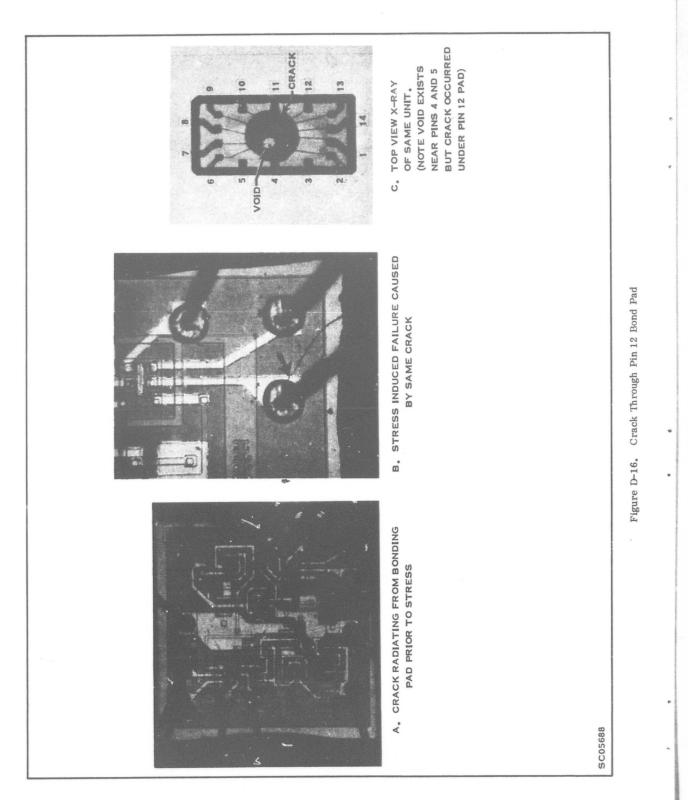

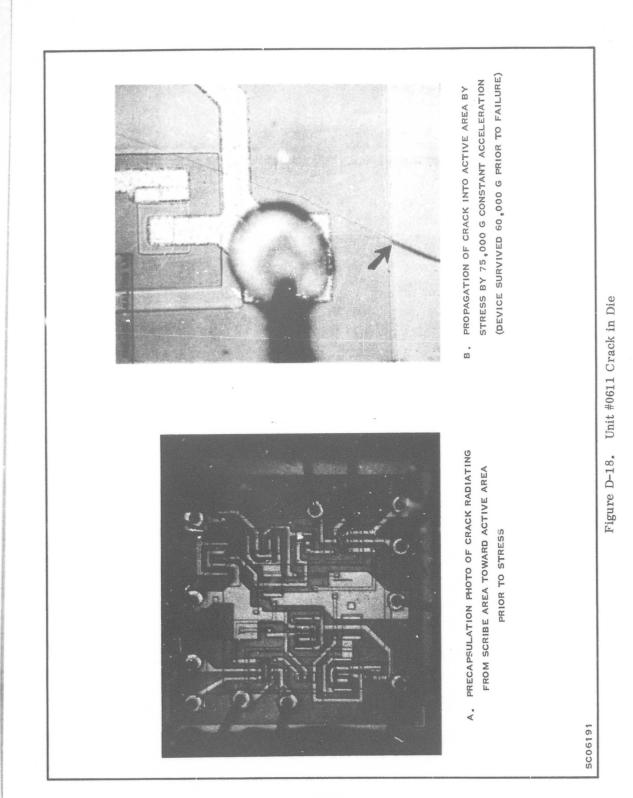

Sixty percent of the Fixed and Step Stress Series failures were caused by bond wire drass, peeling, metallization, and die cracks. Wire dress failures were caused primarily from excess slack in wires connecting the die to the package. The slack permitted the wires to move during constant acceleration stress causing the wire to weaken and break at the stitch bond. The incidence of wire breakage was increased if the stitch bond was not centered properly on the bonding pad. Die crack failures

|                                    | Failure                       | Quantity |                                                                                                                                            | Re                    | Reliability<br>Screens |

|------------------------------------|-------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------|

| Stress *                           | Mechanism<br>(Ref Appendix D) | Failed   | Comments                                                                                                                                   | Screening**<br>Levels | Effectiveness (2)      |

| High Temperature<br>Storage        | Photolithographic faults      | ß        | Mask misalignment; abnor-<br>mally large emitter window                                                                                    | Ħ                     | 100                    |

| (300-500°C)<br>(325 Devices        | Metal scratch                 | 1        | Scratch exposed molybdemum                                                                                                                 | п                     | 100                    |

| Tested)                            | Die crack                     | I        | Crack occurred during stress                                                                                                               | Ħ                     | 100                    |

|                                    | Peeling metal                 | S        | Gold peels from molybdemum -<br>occurred with equal probability<br>throughout all stress intervals                                         | I                     | 100                    |

|                                    | Resistor degradation          | ø        | Resistors R2, R3 increased.<br>Significant changes in non-<br>functional Z(out) parameter<br>observed.                                     | Ħ                     | 80                     |

| Electri Jal Stress<br>(160°-200°C) | Surface contamination         | 1        | Particulate matter bridged two<br>metal leads on die                                                                                       | H                     | 100                    |

| (880 Devices<br>Tested)            | Oxide defects                 | ۲        | Pinholes under metal; scratches<br>under metal; spurious diffusion;<br>particulate contamination                                           | п,п                   | 100                    |

|                                    | Peeling metal                 | +        | (Remarks for storage failures<br>apply)                                                                                                    | I                     | 100                    |

|                                    | Die cracks                    | თ        | Cracks under bonding pads -<br>existed prior to stress -<br>failures occurred with equal<br>probability throughout all<br>stress intervals | Ħ                     | 100                    |

| and the second                                     | Failure<br>Machaniam | Quantity |                                                                                                               | Re                   | Reliability<br>Screens                                |

|----------------------------------------------------|----------------------|----------|---------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------|

|                                                    | (Ref Appendix D)     | Failed   | COMMENTS                                                                                                      | Screening*<br>Levels | Screening** Estimated ***<br>Levels Effectiveness (%) |

| Constant<br>Acceleration<br>(90 Devices<br>Tested) | Die delamination     | 10       | Die mount material separated<br>from Au plated Kovar. Pro-<br>duction corrective action<br>eitminated problem | Ħ                    | 100                                                   |

|                                                    | Die and wire dress   | 29       | Die improperly oriented in<br>package; slack wires; non-<br>centered stitch bonds                             | П.П                  | 100                                                   |

|                                                    | Ball bond separation | ŝ        | Inadequate bonding pressure<br>or temperature; gold peeling<br>from molybdenum                                | Ē.                   | 100                                                   |

Includes preliminary investigation, Step Stress Series I and Fixed and Step Stress Series

Refer to Table 1. # #

Failures Removed

x 100 By Screening All Failures % Effectiveness =  $\_$

\*\*\*

許

26

12.00

100

1 A A A

a ser day.

were caused primarily from cracks beneath bonding pads and were known to exist prior to conducting the stress tests. Peeling metallization, caused by lack of adherence of gold to molybdenum was encountered on both high temperature storage, ring counter and forward bias operating tests.

#### 6. COMPONENT EVALUATION

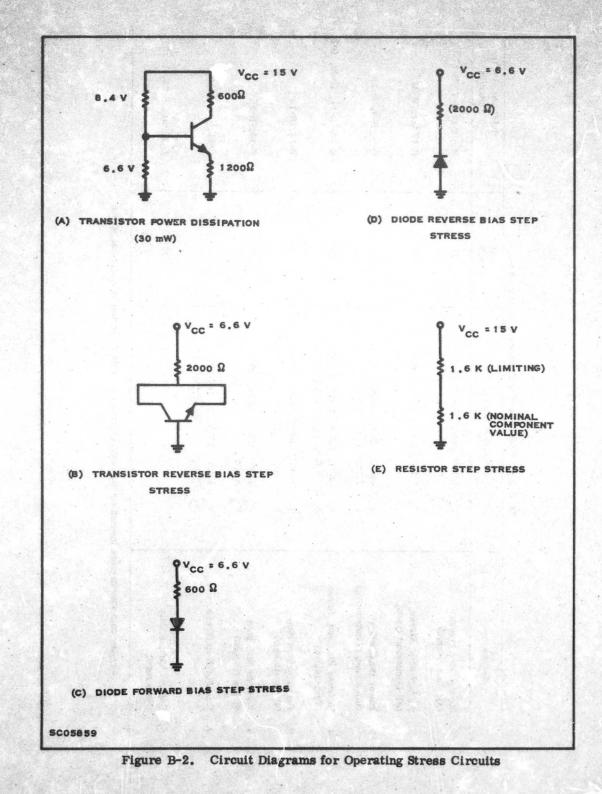

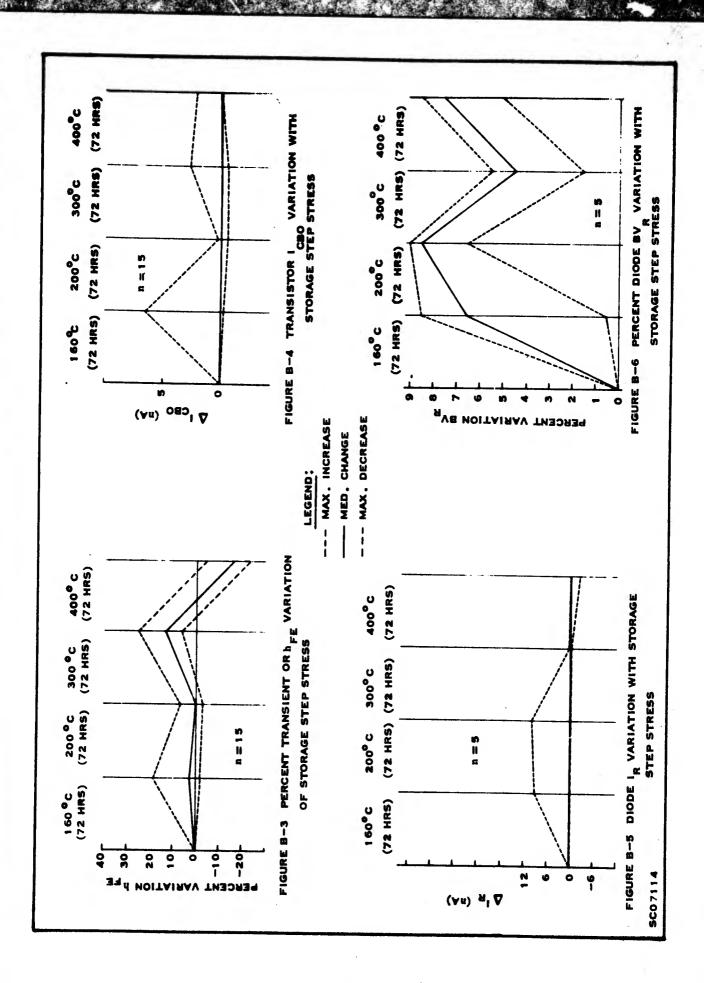

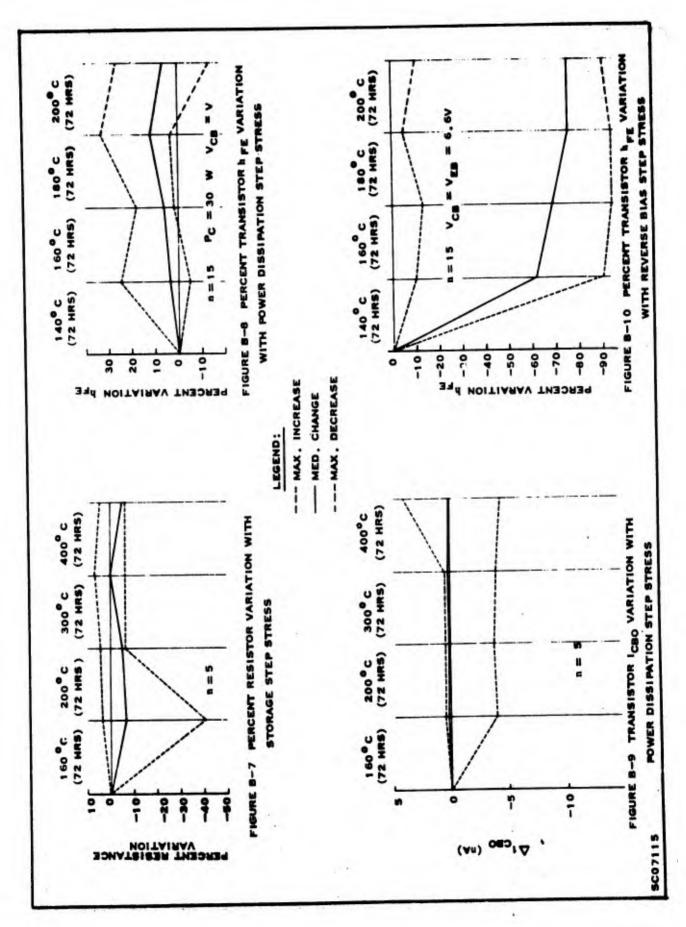

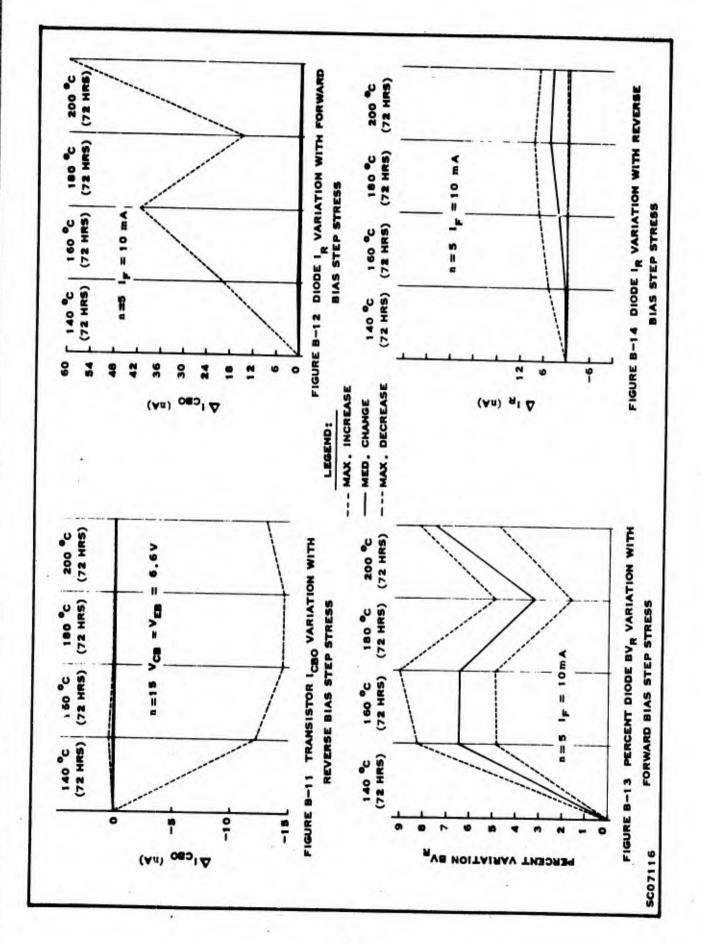

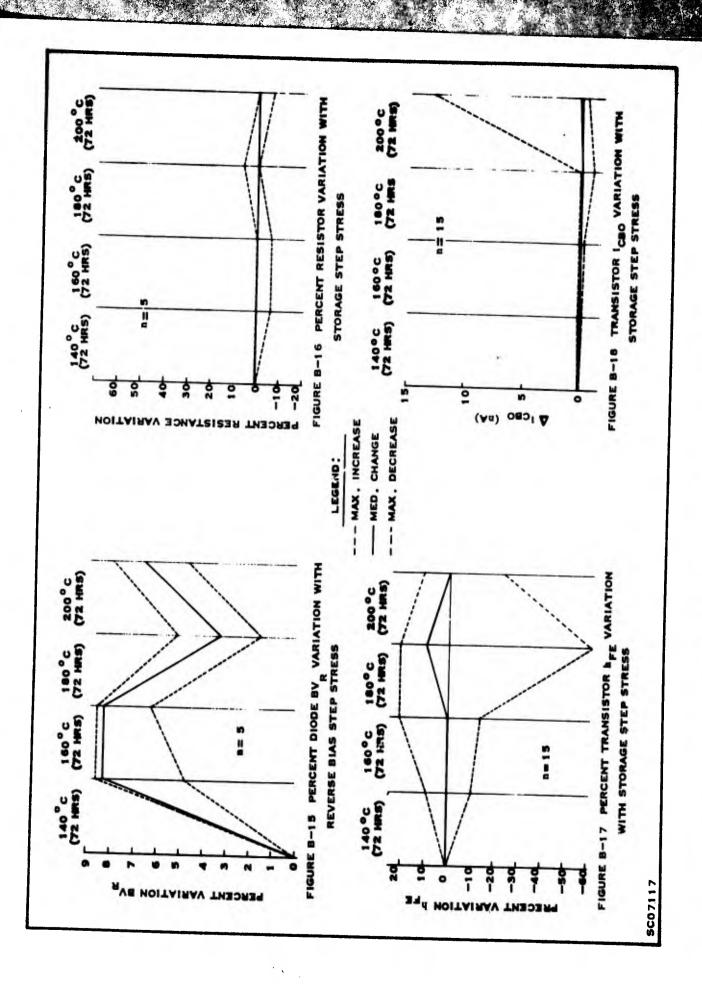

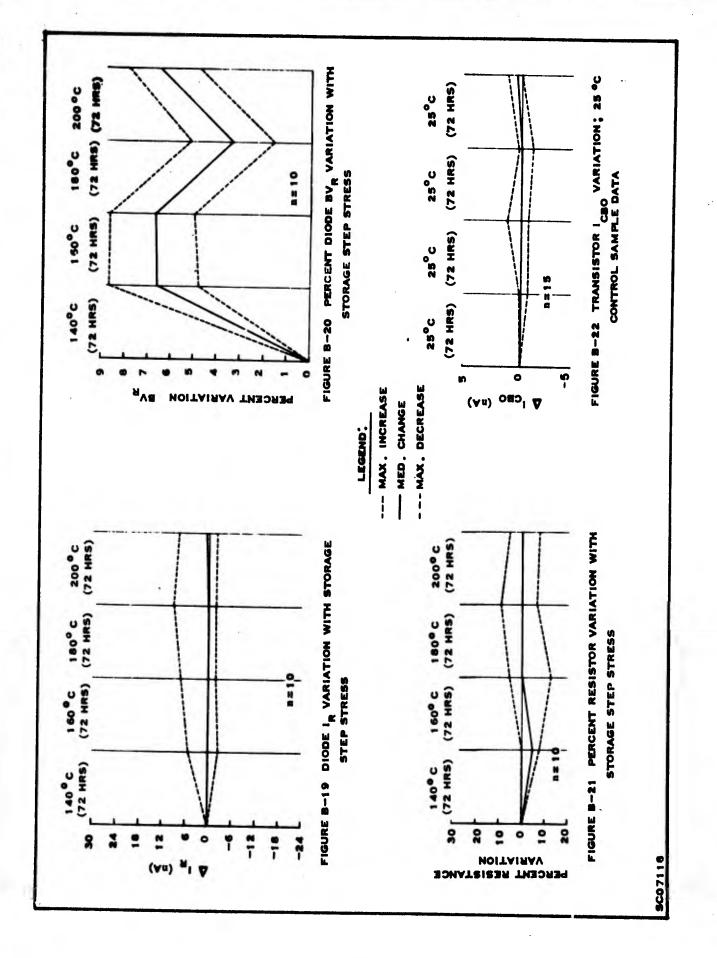

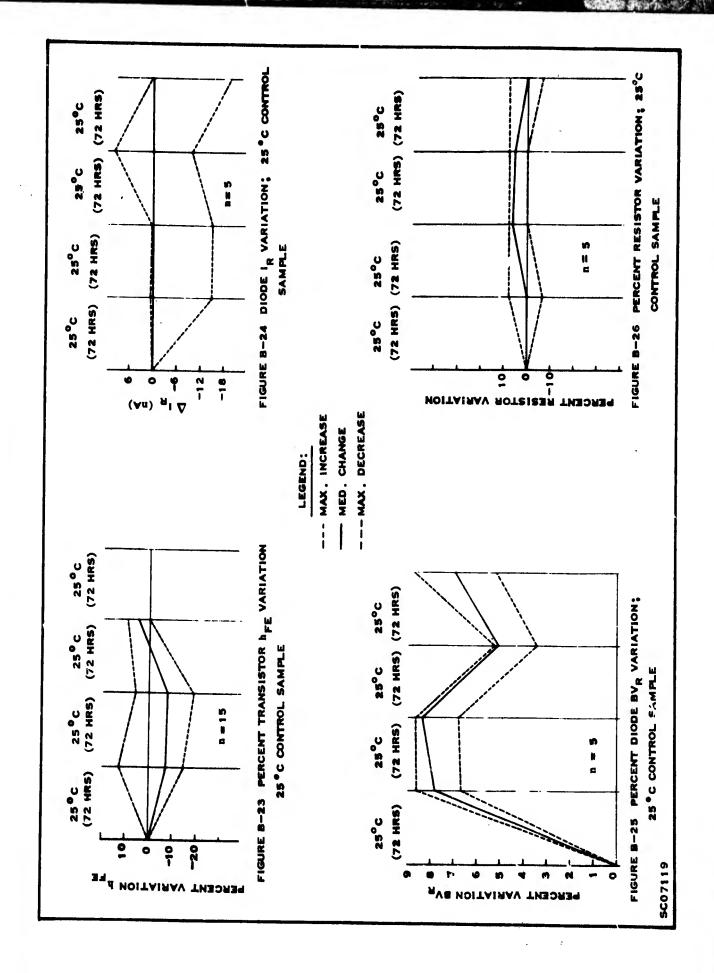

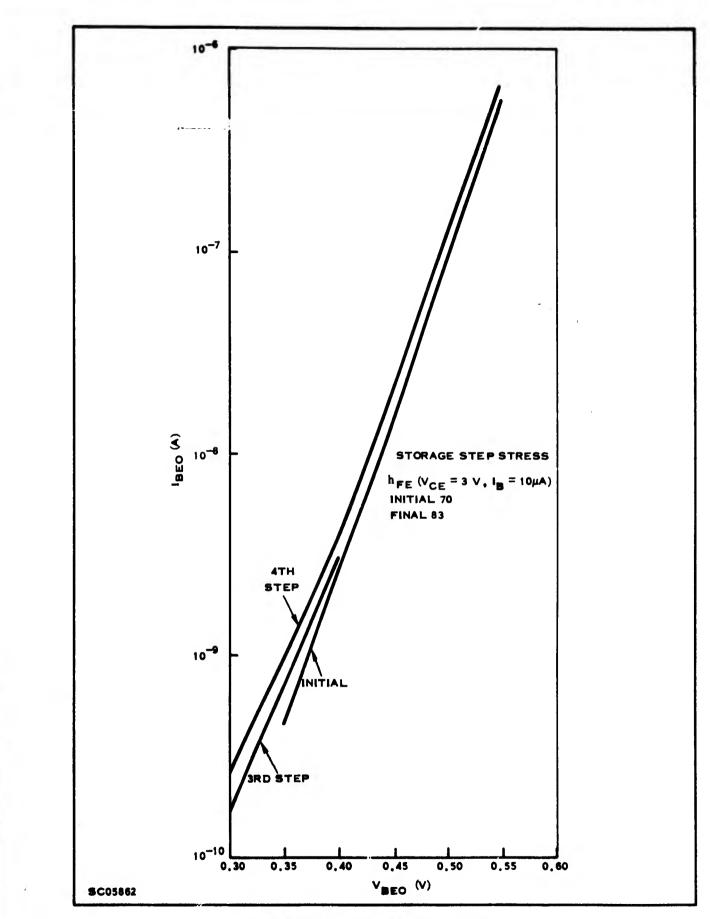

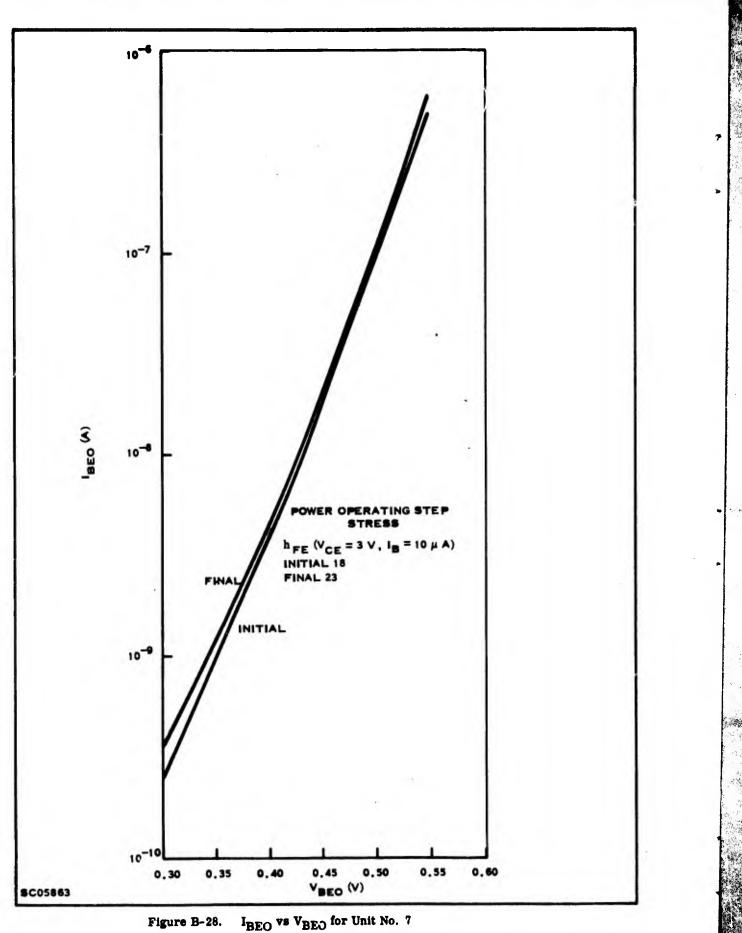

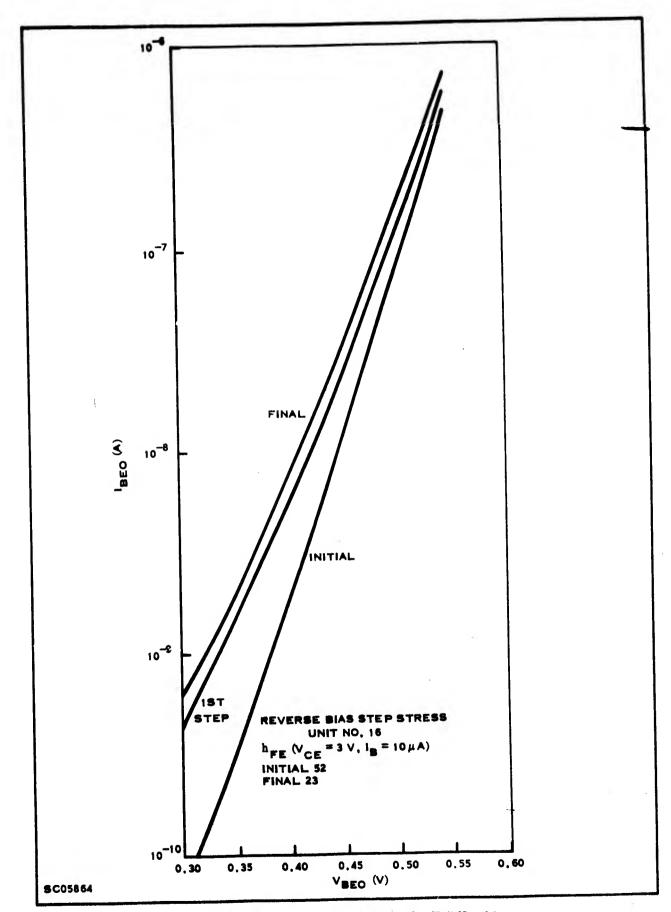

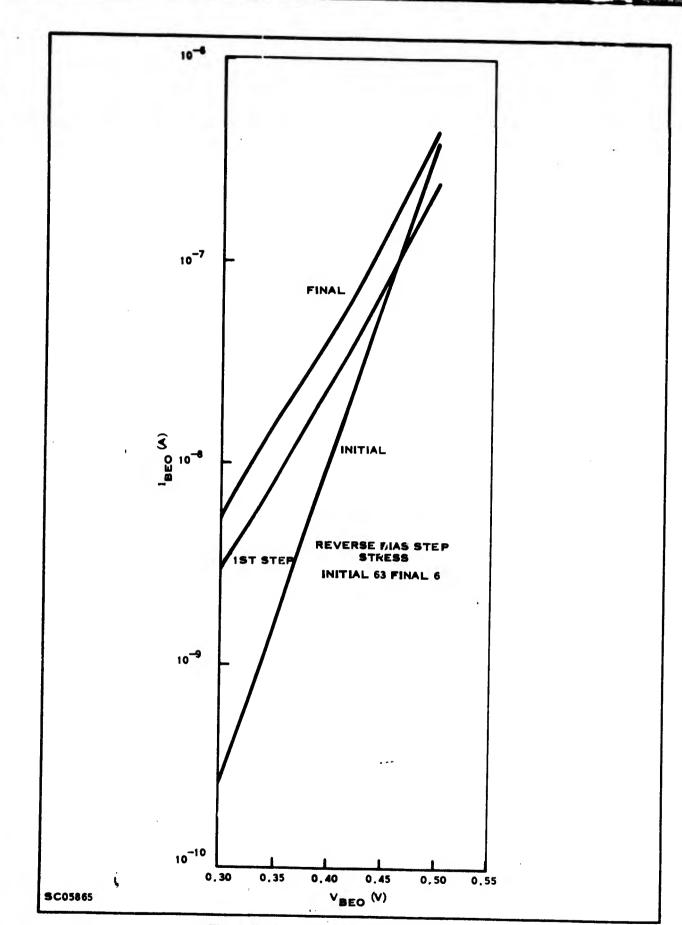

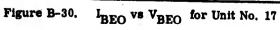

A step stress test program was conducted on transistor, diode, and resistor components of the SN5420. Results of the study are reported in Appendix B. The most significant parameter change was seen in transistor  $h_{FE}$  caused by reverse bias stress (both junctions reverse biased). The suspected mechanism of this change is emitter-base diode channeling, caused by the inversion of P type material.

Other less significant parameter changes were observed in components subjected to power dissipation and storage stress. The component parameters, transistor  $V_{\rm BE}$  and resistor values, which dominate the equations describing a functional device parameter, were found to be relatively stable during stress.

### SECTION IV

#### **RELIABILITY SCREENING**

#### 1. INTRODUCTION

A reliability screening procedure for the SN5420 digital NAND gate has been developed as a result of studies conducted during this contract. Three major work elements from which the screening procedure was developed are described below:

- 1) Circuit analysis was conducted to determine; design factors affecting reliability; the stresses which more nearly approximate circuit applications; define functional parameter failure criteria; and to develop non functional measurement techniques which are more sensitive to degradation than functional measurements. The results of these studies are contained in a previous report  $\frac{2}{2}$  and are summarized in Section II.

- 2) A study of the molybdenum-gold expanded contact system was conducted to define failure modes, their cause and the techniques to predict their occurrence. Refer to Section V for amplification.

- 3) A high stress test program coupled with failure analysis was conducted. The effectiveness of the techniques derived from circuit analysis and contact studies were demonstrated during the test program. Precapsulation photographs of the devices subjected to stress were used to relate failure mechanisms to visible anomalies which existed on the dies prior to capsulation. Refer to Section III and Appendix D for test and failure analysis results.

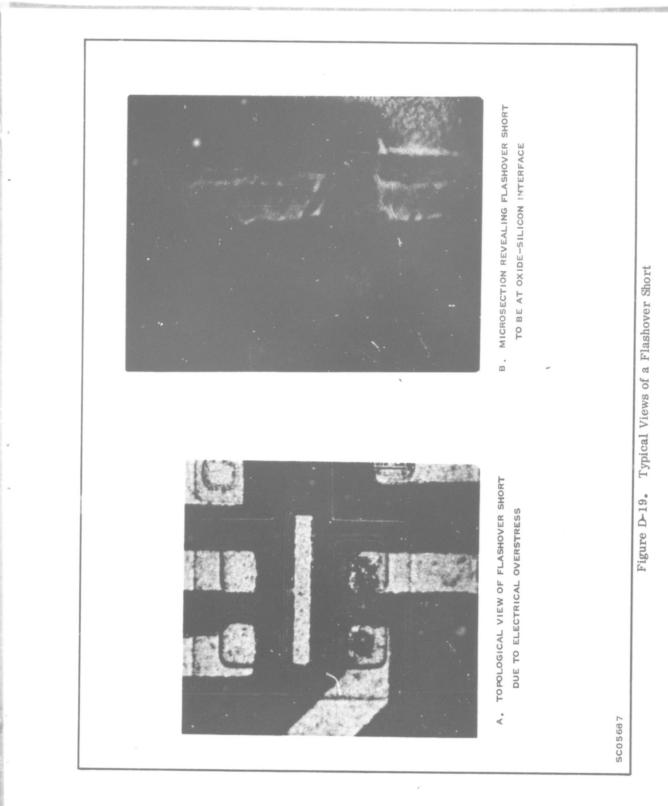

The reliability screening procedure is shown in Table 1. It was developed by identifying the failure mechanisms resulting from high stress tests and relating these to information which existed at the earliest point in the manufacturing cycle following the die mounting and lead bonding operations. Two types of failures are not included in the screening procedure, namely emitter flashover and stress errors. These are discussed in Appendix D. These were determined not to be related to use-conditions. The discussion which follows is organized according to the techniques used in the screening procedure shown in Table 1.

# 2. PRECAPSULATION LOT ACCEPTANCE FOR METAL ADHERENCE

Failures caused by peeling metallization were found to occur with equal probability throughout all intervals of the stress program. Since these failures could not be

discriminantly predicted by visual inspection or electrical measurements, a destructive shear bond strength test performed on a sampling basis is specified. The reject criteria is specified in terms of x (average) and R (range) of bond strength distributions. A discussion of the technique and its effectiveness to predict failures is contained in Section V of this report.

## 3. DIE AND WIRE DRESS

Die and wire dress problems were revealed from constant acceleration stress. Both pre and post capsulation screens are recommended to remove potential failures caused by:

- Wire breakage which occurs above the stitch bond terminal.

- Wires shorting together, to the case or die.

A comprehensive discussion of this problem is contained in Appendix D. Three steps in the screening procedure to remove potential failures are:

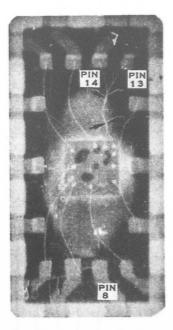

- 20 X visual inspection with diffused lighting prior to capsulation. Refer to Figure 10 for a criteria for inspection.

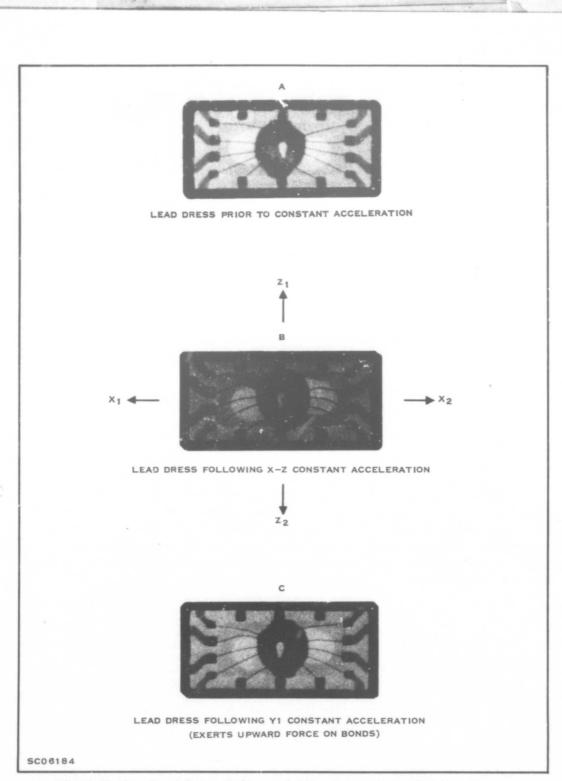

- Constant acceleration in the X Z planes after capsulation followed by topological X-ray. The visual inspection criteria of Figure 10 can be used in conjunction with the X-ray photographs. The following sequence for constant acceleration is recommended:  $X_1, X_2, Z_1, Z_2$ . Refer to Appendix Figure D-12 for illustration.

- Constant acceleration in the  $X_1$  plane.

Analysis of constant acceleration failures, coupled with prestress X-rays indicates 20 percent of potential failures caused by die or wire dress can be detected by 20X visual inspection prior to capsulation. However, figures presented in Appendix D demonstrate how slack wires can be seen by a topological X-ray following constant acceleration in the X and Z planes. The lateral centrifugal force causes wires with high arcs not previously visible from a vertical view to "fold over," revealing an extensive amount of bow in some wires. Thus, constant acceleration in the XZ planes followed by topological X-ray is a very effective tool for removing escapes from the precap inspection.

Constant acceleration in the  $Y_1$  plane is utilized to eliminate devices with stitch bonds formed with too little or too much pressure. The centrifugal force is exerted upward and snaps the narrow neck shown in the figures of Appendix D, or breaks a weak bond between the wire and bond pad. This screen also eliminates potential failures caused by weakly formed ball bonds.

Figure 10. 20X Visual Package Inspection

## 4. **DIE INSPECTION**

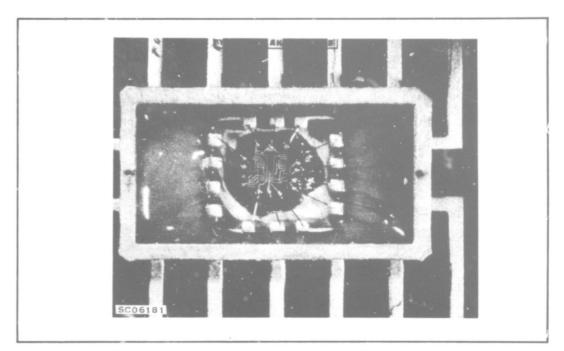

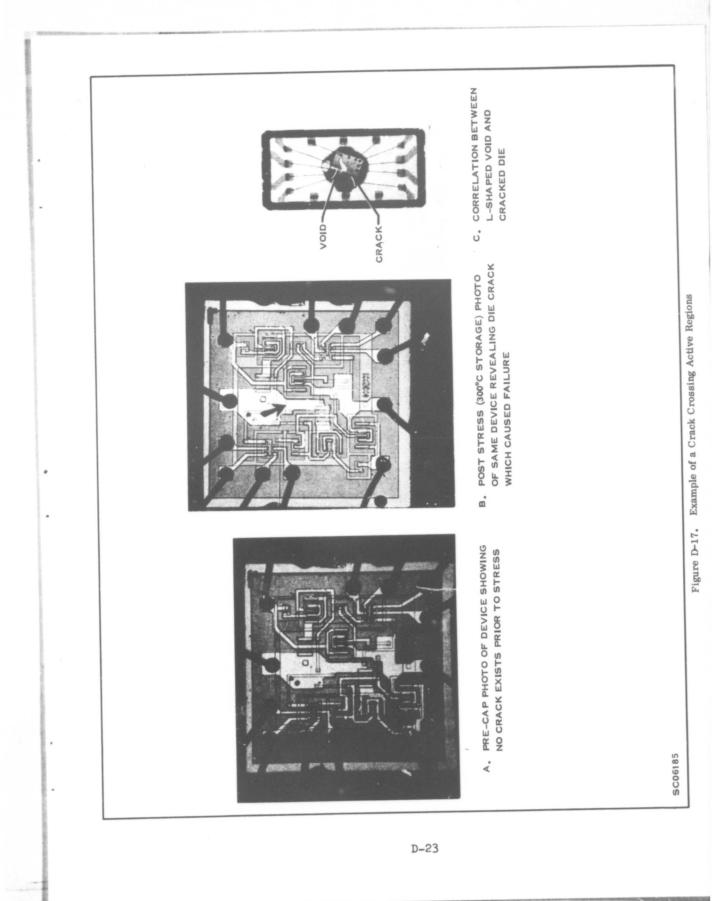

A 100-percent die inspection screen using 70X direct lighting techniques is specified in the screening procedure. Inspection criteria are outlined in Table 4 of this section; they were developed from analysis of the precapsulation die photographs of devices subjected to the fixed and step stress program. The technique for analysis was briefly summarized in Section II of this report, while the relationships between failures and information which existed on the dice prior to stress is contained in Appendix D.

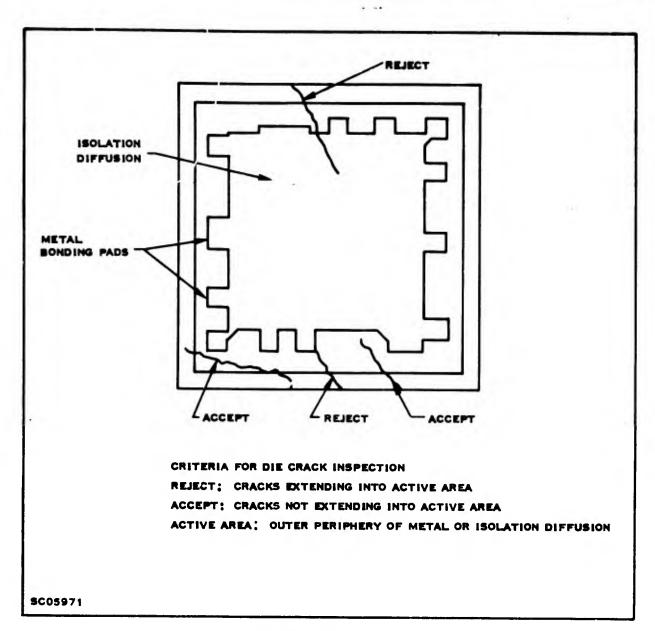

A summary of cracked die failures is given in Table 5. Note that nine failures were caused by die cracks under bonding pads and that seven of these were visible in the precapsulation photographs. It is believed that the remaining two were present when the photographs were taken, but were hidden by bond wires. Only one crack was found to extend as a result of stress which was 75,000 G constant acceleration. Since the device survived 60,000 G prior to failure, and since no other cracks were observed to propagate into the active region of the dice, the screening procedure requires only rejection for cracks which extend into the active area, defined by the outer periphery of metal or isolation diffusion as shown in Figure 11. It is interesting to note that only 16 percent of dice with cracks would have been rejected by this screening criteria; i. e., 84 percent of dice with cracks did not fail the high stress tests.

| Defect Classification | Reject Criteria                                                                                          |

|-----------------------|----------------------------------------------------------------------------------------------------------|

| 1. Cracked Bars       | Cracks extending into active circuit area defined by the outer periphery of metal or isolation diffusion |

| 2. Oxide Defects      | Concentric circles in oxide within the active region                                                     |