| UNCL            | ASSIFIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SEP | 76 R | E BARR | ERA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OPROGR          |          | PROCE | .550K. (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 01 | NL | /       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|---------|

|                 | DF 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 Jackhart Mare |          |       | <b>福</b> 古                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |    |         |

| Maria and Array | And the second s |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>The second second</li></ul> | ми:<br>         | A REPORT |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |    |         |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |        | And<br>And And And And And And And And And And                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |          |       | Hitl<br>Annual and a second seco    |    |    |         |

|                 | Additional 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |          |       | <ul> <li>Markara Markara, Santa Markara, Santa</li></ul> |    |    |         |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |        | Pro-<br>man and the second |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |    |         |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |          |       | The second secon      |    |    | 3 2 2 3 |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | LT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | END             |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |    |         |

THE UNIFIED PROCESSOR, A MICROPROGRAMMABLE PROCESSOR

La la marte at

INFORMATION MANAGEMENT BRANCH SYSTEM AVIONICS DIVISION

SEPTEMBER 1976

AFAL-TR-75-148

16. (12

TECHNICAL REPORT AFAL-TR-75-148 FINAL REPORT FOR PERIOD AUGUST 1972 THROUGH MARCH 1975

Approved for public release; distribution unlimited

AIR FORCE AVIONICS LABORATORY AIR FORCE WRIGHT AERONAUTICAL LABORATORIES AIR FORCE SYSTEMS COMMAND WRIGHT-PATTERSON AIR FORCE BASE, OHIO 45433

#### NOTICE

When Government drawings, specifications, or other data are used for any purpose other than in connection with a definitely related Government procurement operation, the United States Government thereby incurs no responsibility nor any obligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data, is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any patented invention that may in any way be related thereto.

This technical report has been reviewed and is approved for publication.

Rob & Barrena

RALPH'E. BARRERA Project Engineer

FOR THE COMMANDER

JAMES M. RILEY, MAJ USAF Chief, System Technology Branch System Avionics Division

Copies of this report should not be returned unless return is required by security considerations, contractual obligations, or notice on a specific document.

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) READ INSTRUCTIONS BEFORE COMPLETING FORM **REPORT DOCUMENTATION PAGE** 2. GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER AFAL-TR-75-148 YPE OF REPORT & PERIOD COVERED TITLE (and Subtitle) Final Technical Report. The Unified Processor, A Microprogrammable Aug 72 three Mar 75. PERFORMING ONG. REPOR NUM Processor . 8. CONTRACT OR GRANT NUMBER(s) AUTHOR(.) Ralph E./Barrera PERFORMING ORGANIZATION NAME AND ADDRESS 10. PROGRAM ELEMENT, PROJECT, TASK AREA & WORK UNIT NUMBERS Air Force Avionics Laboratory Systems Avionics Division (AA) 62204F-2003-04-08 Wright Patterson Air Force Base, Ohio 1. CONTROLLING OFFICE NAME AND ADDRESS Air Force Avionics Laboratory (AFSC) m 2076 Sept System Avionics Division (AA) Wright Patterson AFB, Ohio 79 14. MONITORING AGENCY NAME & ADDRESS(II dillerent from Conty Office) 15. SECURITY CLASS. (of this report) UNCLASSIFIED DECLASSIFICATION/DOWNGRADING 16. DISTRIBUTION STATEMENT (of this Report) Approved For Public Release; Distribution Unlimited. ck 20, if different from Report) DISTRIBUTIO 18. SUPPLEMENTARY NOTES 19 KEY WORDS (Continue on reverse side if necessary and identify by block number) Microprogramming; Processor; Avionics; Computers; Microprocessors; Architecture BSTRACT (Continue on reverse side if necessary and identify by block number) This report presents the design of a microprogrammable processor called the Unified Processor (UP). First a brief history of microprogramming is given followed by a description of a present day processor. The architecture of the Interpreter is presented along with several deficiencies that were present in 010 its design. A brief discussion of the microprogramming format of the UP is presented followed by an in-depth description of the UP. The features of the UP that are covered include general registers, special registers, internal bussing, CONTINUED DD 1 JAN 73 1473 EDITION OF I NOV 65 IS OBSOLETE UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) 011670 above the

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE(When Date Entered)

3: 34

....

microprogram addressing, and the Barrel Switch. Examples of how each of the various features can be used is included in each section. Finally, the UP is evaluated and recommended changes for a future design presented.

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE(When Deta Entered)

and the second se

3.84

## FOREWORD

This Final Engineering Report was prepared by the Air Force Avionics Laboratory (AFSC), System Avionics Division, Information Management Branch, Wright-Patterson AFB, Ohio. The work was accomplished under USAF Project 2003 entitled "Avionic System Design Technology," Task 04 entitled "Modular Processors." The work was administered under the direction of Mr. R. Barrera, Air Force Avionics Laboratory, AFAL/AAM, Wright-Patterson AFB, Ohio.

This report covers work conducted from August 1972 through March 1975 and was submitted by the author March 1975.

The author, Mr. R. Barrera, is grateful for the help and contributions received from Messrs. John Camp and Fred Schurr, associates at the Avionics Laboratory in fabricating and debugging the Unified Processor. In addition he wishes to thank Mr. Dewey E. Brewer also of the Avionics Laboratory for his overall guidance and encouragement during the initial study and design and Mr. Robert Davis of the Burroughs Corp. who spent many hours explaining the hardware and programming of the Interpreter.

| NTIS<br>DOC<br>UNANHO <b>UNCED</b><br>JUSTIFICATION | White Section<br>Buff Section |  |

|-----------------------------------------------------|-------------------------------|--|

| THE R. P. LEWIS CO., LANSING MICH.                  | WAILABILITY CODE              |  |

| A                                                   |                               |  |

iii

and the second

# TABLE OF CONTENTS

| SECTION |                                                                                                                                                                                                                                                      | PAGE                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| I       | INTRODUCTION                                                                                                                                                                                                                                         | 1                                      |

|         | 1 Background<br>2 Statement of the Problem<br>3 Approach                                                                                                                                                                                             | 1<br>4<br>4                            |

| II      | THE INTERPRETER                                                                                                                                                                                                                                      | 6                                      |

|         | 1 Architecture                                                                                                                                                                                                                                       | 6                                      |

|         | a. Logic Unit<br>b. Control Unit<br>c. Memory Control Unit<br>d. Control Store                                                                                                                                                                       | 6<br>10<br>12<br>14                    |

|         | 2. Interpreter Deficiencies                                                                                                                                                                                                                          | 16                                     |

| III     | MICROPROGRAMMING                                                                                                                                                                                                                                     | 19                                     |

|         | 1. Language<br>2. Example                                                                                                                                                                                                                            | 19<br>21                               |

| IV      | UNIFIED PROCESSOR                                                                                                                                                                                                                                    | 25                                     |

|         | <ol> <li>General Registers</li> <li>Barrel Switch</li> </ol>                                                                                                                                                                                         | 25<br>28                               |

|         | a. Barrel Switch Operation<br>b. Barrel Switch Control                                                                                                                                                                                               | 35<br>39                               |

|         | <ol> <li>Microprogram Addressing</li> <li>Memory/Device Addressing</li> <li>Micromemory Control Partitions</li> <li>Internal Bussing</li> <li>Programmable Instruction Decoder</li> <li>Input/Output Registers</li> <li>Special Registers</li> </ol> | 41<br>50<br>54<br>57<br>62<br>65<br>67 |

| v       | CONCLUSION                                                                                                                                                                                                                                           | 69                                     |

|         | 1. Summary<br>2. Recommendations                                                                                                                                                                                                                     | 69<br>69                               |

|         | a. Micromemory<br>b. B Register<br>c. Barrel Switch                                                                                                                                                                                                  | 69<br>70<br>70                         |

v

W. reserve

7

NOT FLUED

RECEDING PAGE BL

# TABLE OF CONTENTS (Cont'd)

| SECTION                                                   | PAGE |

|-----------------------------------------------------------|------|

| APPENDIX A - Unified Processor I/O Channel                | 71   |

| APPENDIX B - Unified Processor Micromemory Implementation | 75   |

| BIBLIOGRAPHY                                              | 79   |

vi

and the second second

# LIST OF ILLUSTRATIONS

| FIGURE |                                          | PAGE |

|--------|------------------------------------------|------|

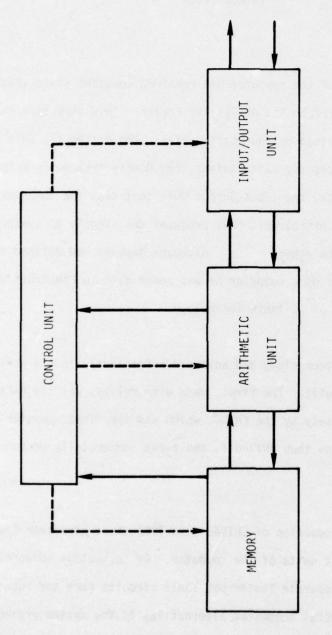

| 1      | Basic Computer Structure                 | 2    |

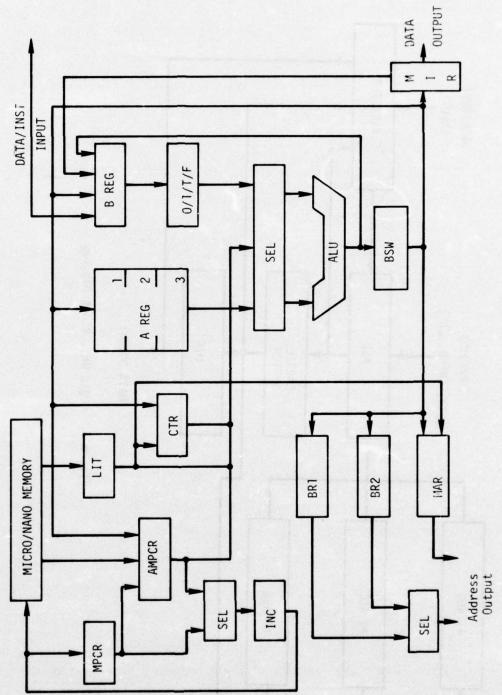

| 2      | Interpreter Block Diagram                | 7    |

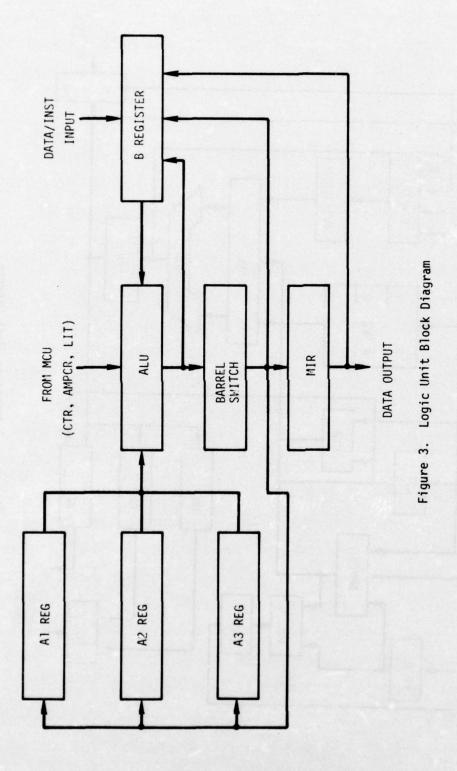

| 3      | Logic Unit Block Diagram                 | 8    |

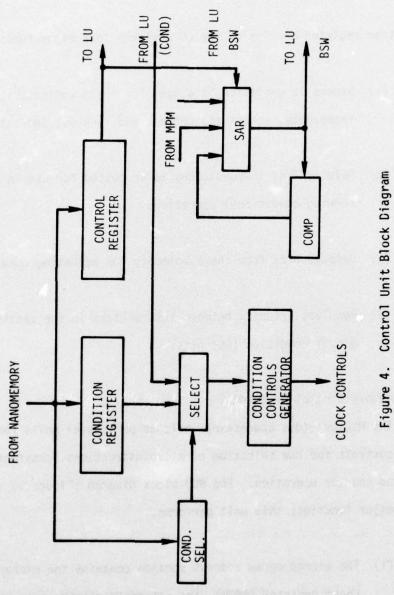

| 4      | Control Unit Block Diagram               | 11   |

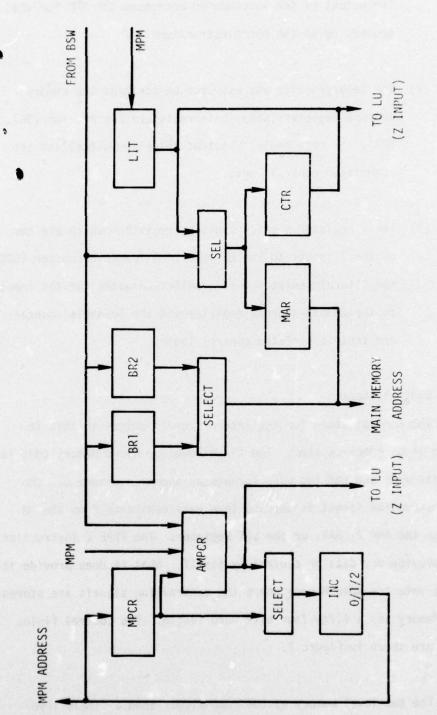

| 5      | Memory Control Unit Block Diagram        | 13   |

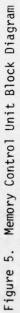

| 6      | Micromemory Word Formats                 | 15   |

| 7      | Nanomemory Word Format                   | 15   |

| 8      | Unified Processor Control Fields         | 20   |

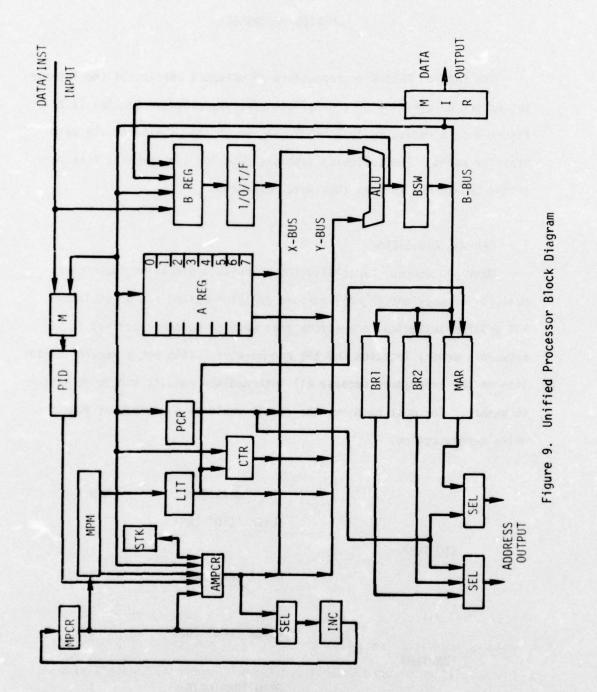

| 9      | Unified Processor Block Diagram          | 26   |

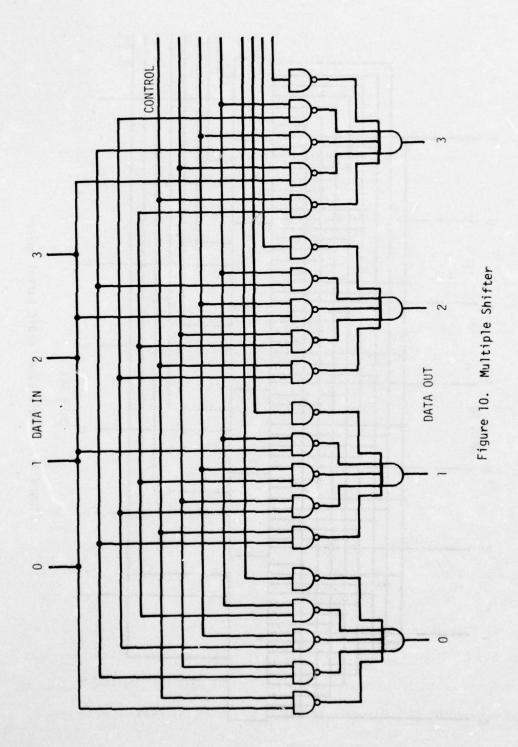

| 10     | Multiple Shifter                         | 31   |

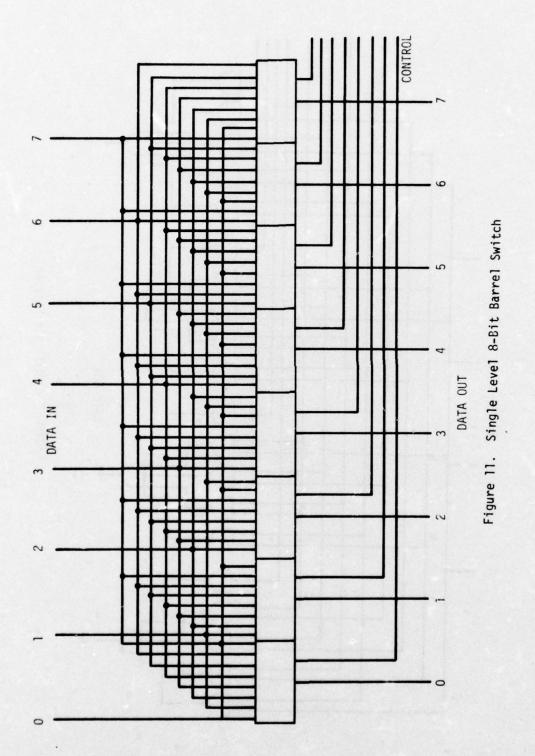

| 11     | Single Level 8-Bit Barrel Switch         | 32   |

| 12     | Single Level 8-Bit Barrel Switch Control | 33   |

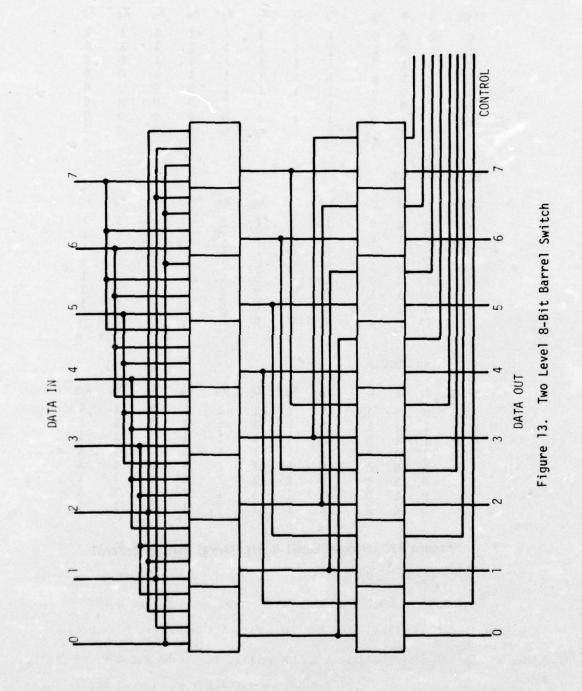

| 13     | Two Level 8-Bit Barrel Switch            | 34   |

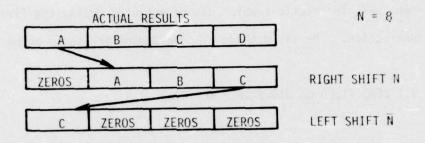

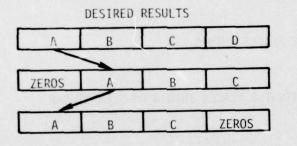

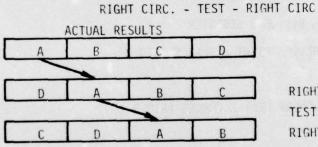

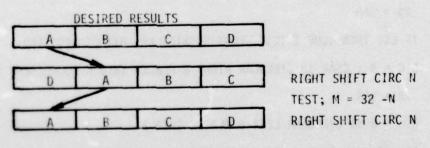

| 14     | Shifting Examples                        | 37   |

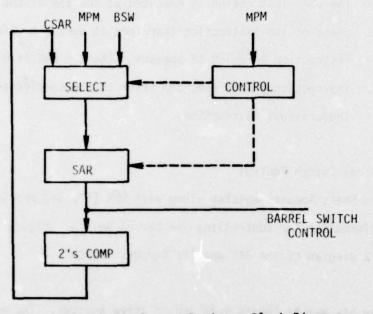

| 15     | Shift Amount Register Block Diagram      | 40   |

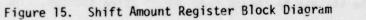

| 16     | Timing of CSAR Instruction               | 40   |

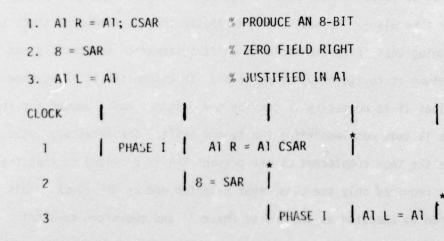

| 17     | SAVE Successor Timing                    | 45   |

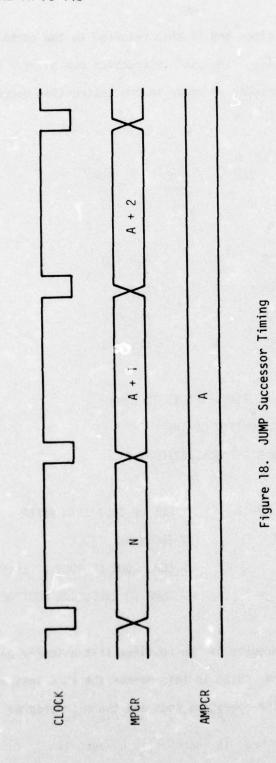

| 18     | JUMP Successor Timing                    | 47   |

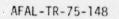

| 19     | EXEC Successor Timing                    | 49   |

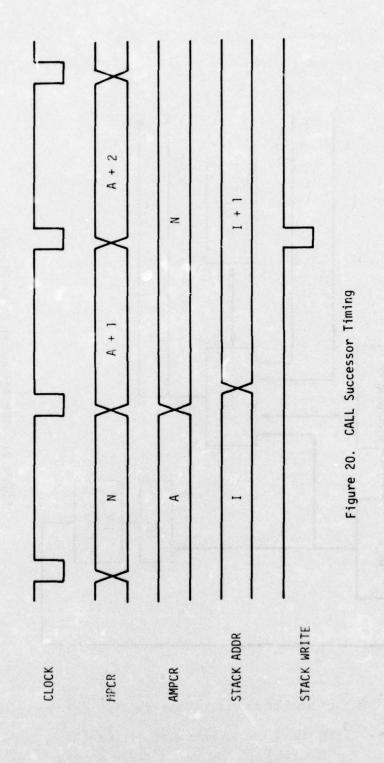

| 20     | CALL Successor Timing                    | 51   |

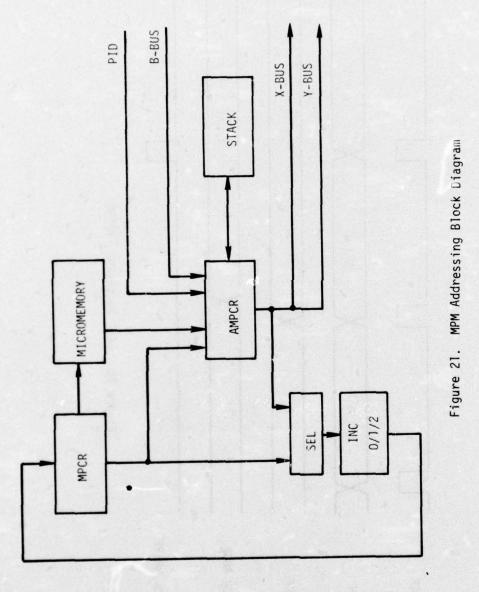

| 21     | MPM Addressing System Block Diagram      | 52   |

| 22     | Type I Microinstruction Control Fields   | 55   |

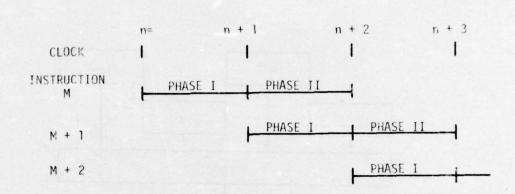

| 23     | Instruction Timing Diagram               | 57   |

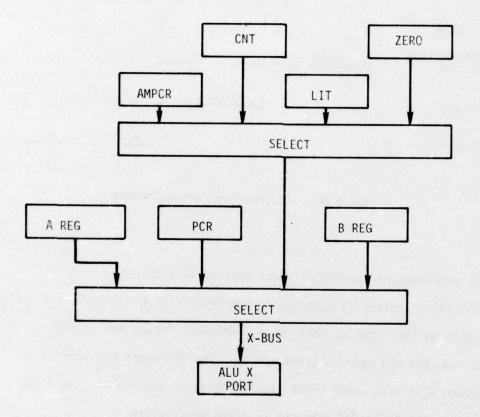

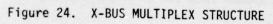

| 24     | X-Bus Multiplex Structure                | 58   |

| 25     | Y-Bus Tri-State Structure                | 61   |

and the second

# LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE |                                            | PAGE |

|--------|--------------------------------------------|------|

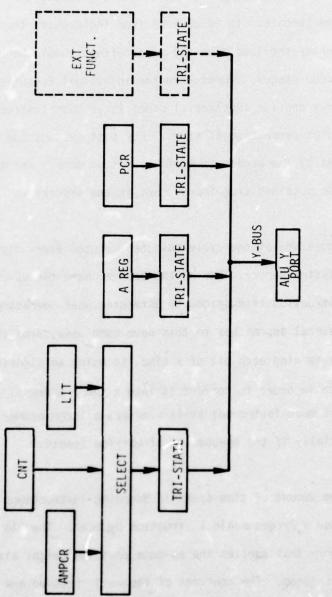

| 26     | Normal Fetch-Decode-Execute Cycle          | 63   |

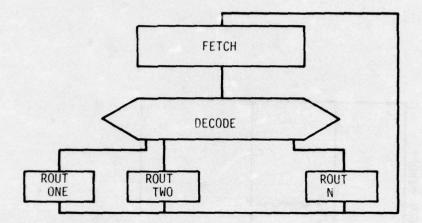

| 27     | Programmable Instruction Decoder Operation | 64   |

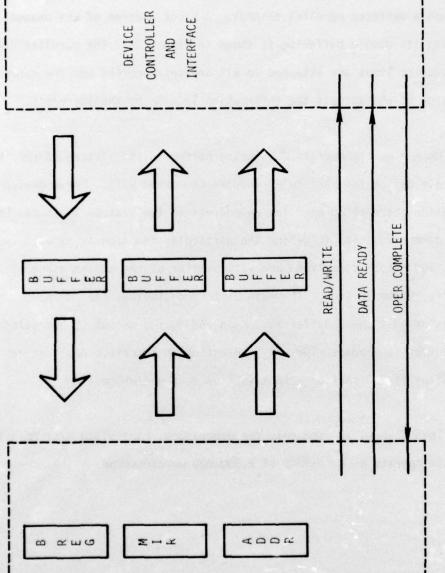

| 28     | I/O Channel Block Diagram                  | 72   |

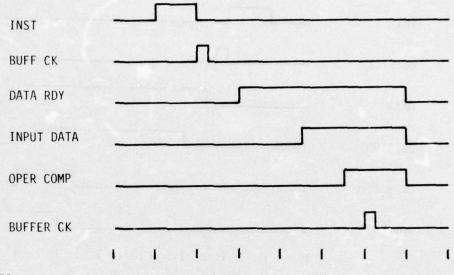

| 29     | Input Data Transfers Timing Diagram        | 73   |

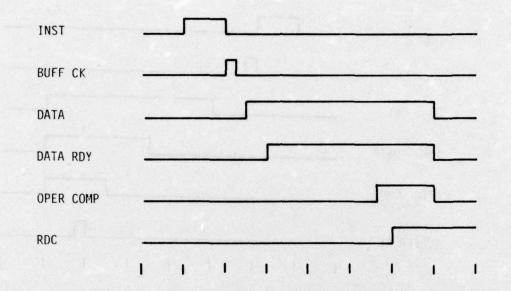

| 30     | Output Data Transfers Timing Diagram       | 74   |

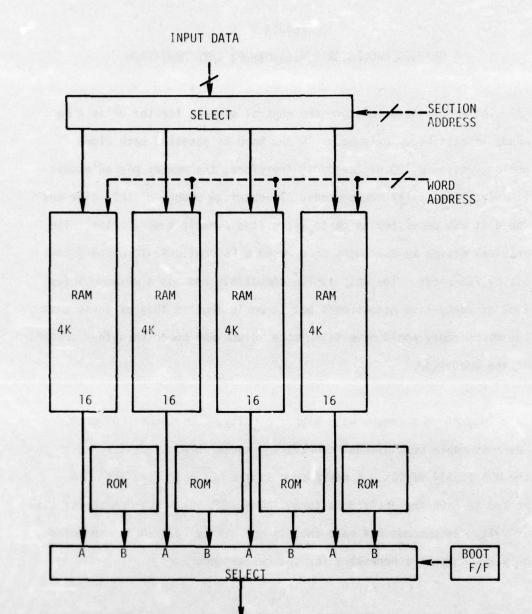

| 31     | UP Micromemory                             | 76   |

viii

star to

#### SUMMARY

This report presents the design of a microprogrammable processor called the Unified Processor (UP). First a brief history of microprogramming is given followed by a description of a present-day processor. The architecture of the Interpreter is presented along with several deficiencies that were present in its design. A brief discussion of the microprogramming format of the UP is presented followed by an in-depth description of the UP. The features of the UP that are covered include general registers, special registers, internal bussing, microprogram addressing, and the Barrel Switch. Examples of how each of the various features can be used is included in each section. Finally, the UP is evaluated and recommended changes for a future design presented.

and the second

# SECTION I

# INTRODUCTION

## 1. BACKGROUND

The structure of the computer has remained constant since 1830 when Charles Babbage described his Analytical Engine. This structure shown in Figure 1 is comprised of four basic units: the Arithmetic Unit that performs all the necessary calculations, the Memory that holds both the instructions and data, the Input/Output Unit that ties the computer to the world, and the Control Unit that produces the signals to synchronize the operations of the other units. Although Babbage had defined the necessary components of a computer he was never able to construct one because of the lack of suitable technology.

By the 1940's technology had advanced sufficiently that a working computer could be built. The first, made with relays, was the MARK I. It was followed closely by the ENIAC, which was the first computer to use vacuum tubes, and then UNIVAC I, the first commercially produced computer.

Since the introduction of UNIVAC I in 1951 there have been few changes to the basic units of the computer. As technology advanced the units were made to operate faster but their circuits remained unchanaged. There have been several suggested alternatives to the system presently being used but most of these have proved of little worth because of either limited applications or insufficient technology. One alternative

+ 1

AFAL-TR-75-148

-

that had been considered an academic curiosity, for the latter reason above, was the use of microprogramming.

The Arithmetic Unit, Input/Output Unit, and the Memory have almost since their inception been very systematically designed. The flow of data within these units is easy to follow and the design or modification of an existing unit is relatively easy to accomplish. The same cannot be said of the Control Unit because its design tends to be of random logic groupings. It was this ad hoc, nonsystematic approach to designing the Control Unit that concerned M. V. Wilkes and caused him in 1951 to put forth the scheme of microprogramming. Wilkes observed that every machine level instruction was really a combination of several less complex commands or machine states. For example an add instruction was composed of the following sequence of machine states.

MACHINE LEVEL

#### MICRO LEVEL

ADD R1, R2

ADDRESS R1 & R2 AND GATE ONTO ALU BUSSES

SET ALU FUNCTION TO ADD

ADDRESS DESTINATION REG R2

CLOCK RESULTS INTO REG R2