AD A 0 8 7 0 5 9 Bonald N. Lord George A. Walz Stan Green UTION UNLIMITE APPROVED FOR PUBLIC RELEASE, DIST ROME AIR DEVELOPMENT CEN Air Force Systems Command Griffiss Air Force Base, New Yor FILE 7 22 011

Indiana Children and

EPPROVED; <u>.</u> 9 L

BAVID C. LURE, Lt Col, USAF Chief, Reliability & Compatibility Division

FOR THE COMMANDER: CA

JOHN P. HUSS Acting Chief, Plans Office

1. Pla

If your address has changed or if you wish to be removed from the safe ing list, or if the addresses is no longer employed by your organization please notify SADC (RDET), Griffias APS MT 13441. This will mestal as maintaining a current mailing list.

Do not return this copy. Retain or destroy.

UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Date Entered) READ INSTRUCTIONS BEFORE COMPLETING FORM REPORT DOCUMENTATION PAGE . GOVT ACCESSION NO. 3. RECIPIENT'S CATALOG NUMBER 59 D-AARTA RADC-/TR-80-111 TYPE OF REPORT & PERIOD COVERED TIN' & fand Subtition DESIGN GUIDELINES AND OPTIMIZATION PROCEDURES Final Technical Report May 1978 - May 1979 FOR TEST SUBSYSTEM DESIGN 6. PERFORMING ORG. REPORT NUMBER . CONTRACT OR GRANT NUMBER(s) AUTHOR(+) Donald N. Lord 15 F30602-78-C-0167 A George A. Walz Stan/Green PROGRAM ELEMENT, PROJECT, AREA & WORK UNIT NUMBERS Grumman Aerospace Corporation 62702F Bethpage NY 11714 23380224 1. CONTROLLING OFFICE NAME AND ADDRESS Z. REPORT DATE April 1980 Rome Air Development Center (RBET) 13. NUMBER OF PAGES Griffiss AFB NY 13441 250 AGENCY NAME & ADDRESS(If different from Controlling Office) 15. SECURITY CLASS. (of this report) UNCLASSIFIED Same 154. DECLASSIFICATION/DOWNGRADING N/A 16. DISTRIBUTION STATEMENT (of this Report) Approved for public release; distribution unlimited  $\langle I2, \rangle$ 263 17. DISTRIBUTION STATEMENT (of the obstract entered in Black 20, if different from Report) ral Fort. Man 19-Ma. 115 Same 18. SUPPLEMENTARY NOTES RADC Project Engineer: Daniel Gleason, 1Lt. USAF (RBET) 9. KEY WORDS (Continue on reverse side if necessary and identify by block number) Ground Electronic System Built-in-Test Avionic Automatic Test Test Equipment AGE ASTNACT (Continue on reverse side if necessary and identify by block number) The study provides guidelines and procedures to optimize the design of built-in-test equipment. The procedures are applicable to the design of both avionic and ground electronic systems. Optimization of the test subsystem is achieved by properly specifying three key design parameters (test effectiveness, mean corrective maintenance time, and test subsystem production costs) during the Conceptual Phase. These parameters then form the design to criteria for optimization during DD 1 JAN 73 1473 EDITION OF I NOV 65 IS OBSOLETE UNCLASSIFIED SECURITY CLASSIFICATION OF THIS PAGE (When Data Entered) st 28124H

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIP PAGE(When Data Entered)

#### SUMMARY

The objectives of this study were to develop guidelines, mathematical tools, and procedures that can be used by equipment designers to optimize the cost effectiveness of the test subsystem. In the context of this study, the term "test subsystem" refers to Built-In-Test (BIT) or test points and external test equipment, or any combination thereof. Specifically, the guidelines and procedures were to provide:

- Techniques applicable to both early design and detailed design phases

- Techniques which are applicable to the design of test subsystems for both avionics and ground electronic systems

- Mathematical procedures and models to select the most cost effective test subsystem design, taking into account development, production, and total life cycle costs.

The study was initiated with a literature search and evaluation to establish a firm technology baseline and point of departure. Two significant conclusions drawn from the three-month review of current technology were:

- The terminology and parameters relating to BIT, test diagnostics, and fault isolation performance have proliferated, are frequently used improperly, or are misunderstood. In an effort to avoid such confusion, this report includes definitions of such terms and parameters

- There is unanimous agreement among the authoritative authors and the study team members that the performance of the test subsystem must be specified early in the system design cycle, i.e., during the Conceptual Phase. There is also unanimity that the driving factors in selecting the test subsystem's characteristics (BIT or external test equipment and its performance, automatic, semi-automatic, or manual) are the prime systems availability requirements.

However, all literature reviewed by the study fails to provide practical

design tools to relate availability to test subsystem performance and life cycle cost.

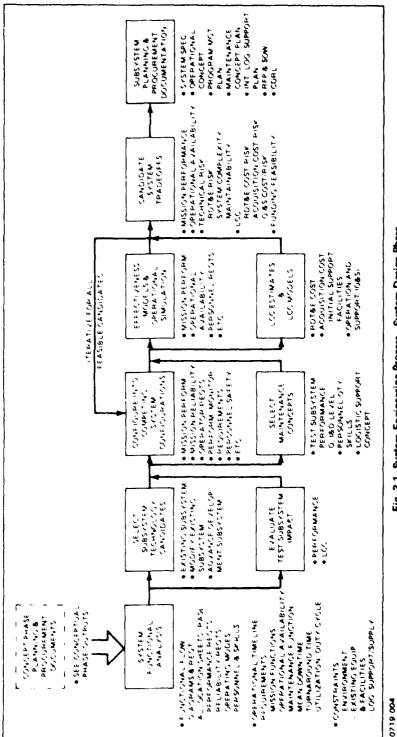

Therefore, the main body of this report addresses the four major phases of system design - The Conceptual Design Phase, the System Design Phase, the Subsystem Design Phase, and the Detailed Design Phase. Each section addresses availability, test subsystem's performance, and life cycle cost.

#### CONCEPTUAL DESIGN PHASE

The major objective of the Conceptual Design Phase is to select optimum system technologies which satisfy mission and operational requirements within a specified cost envelope. Similarly, the test subsystem design objective is to define the test subsystem technology and performance requirements within the overall cost target. To do this, a new definition of test subsystem "effectiveness" is provided. This effectiveness parameter is calculable during each design phase and is also measurable in the field. There is a complex relationship between prime system availability and test subsystem effectiveness. To complete the triad necessary to specify the test subsystem, the relationships between test subsystem effectiveness, mean active repair time, reliability and prime system life cycle cost are provided, together with the necessary guidelines, procedures, and mathematical design tools.

### SYSTEM DESIGN PHASE

Alternate system configurations are traded-off considering all elements of performance and cost. The test subsystem designer's task is to configure an optimum test subsystem for each candidate prime system within its specified performance, mean time to repair, and life cycle cost. The mathematical tools and procedures of the Conceptual Design Phase are equally applicable during the System Design Phase, with the exception that they are applied at a lower level of indenture. Thus, the optimization process is one of tailoring the test subsystem to the candidate prime system characteristics.

Two major issues facing the test subsystem designer during this phase are evaluating the cost impact of using existing subsystems (with less than adequate BIT) vs the development of a new subsystem, and selection of the BIT architecture. The System Design Phase Section of the report addresses these issues.

iv

#### SUBSYSTEM DESIGN PHASE

Test subsystem capability is determined by the number and quality of tests and by the thoroughness with which the resulting information is used. For this reason, the subsystem design methodology optimized the choice of signals measured and quality of measurement in terms of information gained per unit of test subsystem cost. These parameters are calculated individually for each signal, traded off to select the optimal set of measurements, and summed to calculate resulting test subsystem effectiveness and mean corrective maintenance times. In this methodology, the optimal test subsystem is one which meets or betters effectiveness and mean corrective maintenance time requirements of the design specification, within the given cost envelope, and at least production cost.

Initially, the subsystem is analyzed to identify functions, signals, and functional paths, and this information is recorded in functional diagrams. The signals are then analyzed in terms of their test requirements and parameters, and these data are recorded in matrix format. Both the diagrams and matrices are used as permanent design documents that identify and record the information developed during the process of test subsystem design. At any given time, these diagrams and matrices provide a complete architectural and parametric description of the test subsystem at its current stage of design completion.

Each of the signals listed in the matrices is analyzed to determine its tradeoff merit (worth) in terms of the actual testing information developed versus cost of measurement. Signal measurements of least worth are eliminated to the degree necessary to ensure that the evolving design remains within its production cost envelope. Effectiveness and mean corrective maintenance time are calculated, compared with specified values, and the design is reiterated as necessary to comply with the subsystem design specification. These trade-offs and design iterations occur in parallel with the mainstream subsystem design effort, and reach completion when the main effort is completed. The signal matrices and test subsystem design are then expressed in LRU design specifications.

#### **DETAILED DESIGN PHASE**

The principal additional design effort undertaken during detailed LRU design is to calculate final values of measurement quality by analysis of actual

v

circuit failure modes and frequencies. From these results, effectiveness and mean corrective maintenance times are recalculated. If necessary, the test subsystem design is adjusted to bring it into compliance with the effectiveness and/or mean corrective maintenance times of the LRU design specification.

Because effectiveness and mean corrective maintenance time may be actually measured in deployed systems, the results of test subsystem design calculations and signal matrices are saved for reference.

#### STUDY CONCLUSIONS AND RECOMMENDATIONS

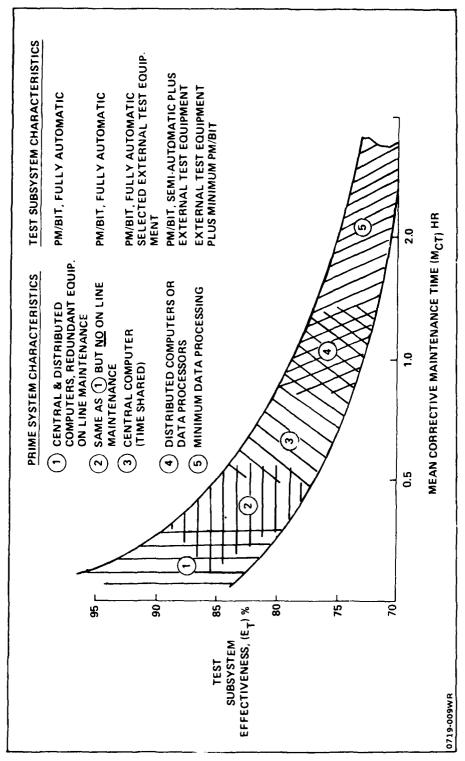

The study objective to develop straightforward engineering tools which permit optimization of the test subsystem design during the overall system design phase and also during the detailed design phase has been met. During the conceptual and system design phases, the test subsystem must be specified in realistic performance and cost parameters depending on the prime system's mission, operational and support concepts. Using the guidelines and design procedures provided, these parameters will fall within the following ranges:

- Test subsystems Effectiveness  $(E_{T}) = 75\%$  to 95%

- Mean Corrective Maintenance Time  $(\overline{M}_{ct}) = 30$  minutes to 4 hours

- Reliability of BIT (R<sub>BIT</sub>) less than 10% of the prime system's overall failure rate due to BIT

- Design-to-cost target for the Test Subsystem = 10% to 20% of the prime system's production costs

By designing to the above parameters during each phase of system design (using the study equations and models) an optimized test subsystem will be achieved.

The resultant test subsystem's performance will, at best, be less than perfect. This is due to the fact that hardware and/or software designers are faced with an inaccurate knowledge of what will fail and how often. Thus the major study recommendations are that the test subsystem must be tested and demonstrated in the field, prior to full-scale production. Further, a tracking and analysis system for all no defect removals will materially reduce the reported number of false alarms and significantly improve system availability.

vi

It is recommended that further subject related studies of existing military data sources and design reporting systems be performed. The objective would be to provide filtered data bases, and a procedural handbook to implement the application of the recommended design guidelines and procedures advanced in this report.

### PREFACE

This technical report presents the results of a study to develop design guidelines and optimization procedures for test subsystem designs. The study was performed under Contract F30602-78-C-0167. This report is prepared in accordance with CDRL item A002 and data item description DI-S-3591A/M.

The guidelines and optimization procedures detailed in this report satisfactorily achieve the objectives of the study.

viii

# CONTENTS

| Section |      |                                 |                                                                    | Page |

|---------|------|---------------------------------|--------------------------------------------------------------------|------|

| 1       | INTR | ODUCTIO                         | DN                                                                 | 1    |

|         | 1.1  | Scope .                         |                                                                    | 1    |

|         | 1.2  | Backgro                         | ound                                                               | 3    |

|         | 1.3  | Literatu                        | re Search                                                          | 3    |

|         | 1.4  | Technic                         | al Problems                                                        | 3    |

|         |      | 1.4.1                           | Specifying BIT Effectiveness                                       | 5    |

|         |      | 1.4.2                           | The BIT "Cost Data" Problem                                        | 6    |

|         |      | 1.4.3                           | BIT "Performance Data" Problem                                     | 6    |

|         | 1.5  | General                         | Methodology                                                        | 8    |

|         |      | 1.5.1                           | Study Approach                                                     | 9    |

|         |      | 1.5.2                           | Fundamental Test Subsystem Optimization<br>Concepts and Guidelines | 9    |

|         | 1.6  | Definiti                        | ors of Selected Terms and Parameters                               | 12   |

|         |      | System                          | 13                                                                 |      |

|         |      | 1.6.2                           | Subsystem                                                          | 13   |

|         |      | 1.6.3                           | Performance Monitor/BIT (PM/BIT)                                   | 13   |

|         |      | 1.6.4                           | Mission Cost Effectiveness                                         | 15   |

|         |      | 1.6.5                           | Inherent Availability                                              | 17   |

|         |      | 1.6.6                           | Corrective Maintenance Time and Mean<br>Time to Repair             | 17   |

|         |      | 1.6.7                           | As-Designed MTBF vs MTBF <sub>o</sub>                              | 18   |

| 2       |      |                                 | ELINES AND PROCEDURES - CONCEPTUAL                                 |      |

|         |      |                                 |                                                                    | 22   |

|         | 2.1  |                                 | n of the Maintenance Concept                                       | 22   |

|         | 2.2  | Test Su<br>U <sub>T</sub> ) (St | ubsystem Performance Requirements (E <sub>T</sub> and tep 1A)      | 25   |

|         |      | 2.2.1                           | PM/BIT False Alarm Rate (FA)                                       | 29   |

|         |      | 2.2.2                           | PM/BIT Diagnostic Error Rate (BDE)                                 | 30   |

|         |      | 2.2.3                           | PM/BIT Undetected Failure Rate (UF)                                | 31   |

|         |      | 2.2.4                           | PM/BIT Ambiguity Rate (BA)                                         | 32   |

|         |      | 2.2.5                           | Specification of $E_{T}$ Based on Historical Data                  | 32   |

子子子

3

j.

and the second second second

ix

10

| Section | -   |                                 |                                                                    | Page |

|---------|-----|---------------------------------|--------------------------------------------------------------------|------|

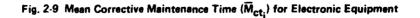

|         | 2.3 | Test Su<br>M <sub>ct</sub> ) (S | ubsystem Performance Requirements (MDT & tep 1B)                   | 34   |

|         | 2.4 | Selectio                        | on of Alternate Test Subsystem Concepts (Step 2)                   | 38   |

|         |     | 2.4.1                           | Test Subsystem Selection for Avionic Systems                       | 38   |

|         |     | 2.4.2                           | Test Subsystem Selection for Ground<br>Electronic Systems          | 42   |

|         | 2.5 | Test Su                         | ubsystem Life Cycle Cost (Step 3)                                  | 47   |

|         |     | 2.5.1                           | Test Subsystem RDT&E Costs                                         | 47   |

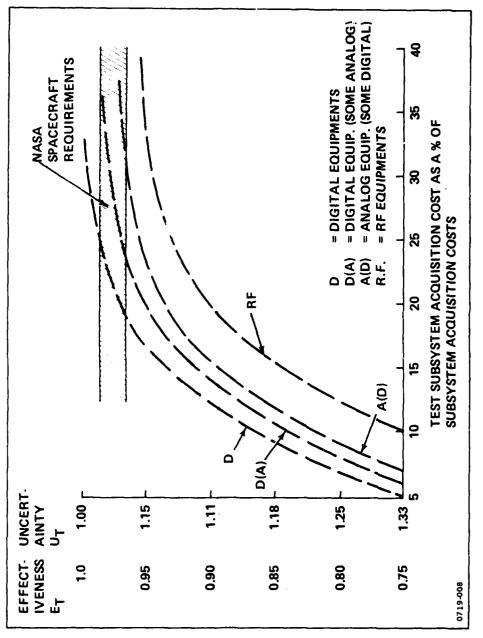

|         |     | 2.5.2                           | Test Subsystem Acquisition Costs                                   | 47   |

|         |     | 2.5.3                           | Operating and Support (O & S) Costs                                | 53   |

|         | 2.6 | Selectio                        | on of the Test Subsystem Concept (Step 4)                          | 54   |

|         | 2.7 | Test Su                         | ubsystem Requirements Specification (Step 5)                       | 55   |

|         |     | 2.7.1                           | System Performance Specification                                   | 56   |

|         |     | 2.7.2                           | Preliminary Plans and Conceptual Documents                         | 56   |

|         |     | 2.7.3                           | Request for Proposal (RFP) and Statement<br>of Work (SOW)          | 57   |

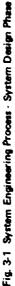

| 3       |     | GN GUID<br>GN PHAS              | ELINES AND PROCEDURES - SYSTEM                                     | 59   |

|         | 3.1 |                                 | ication of Subsystems Reliability and nability Parameters (Step 1) | 62   |

|         |     | 3.1.1                           | Quantification of the Subsystem's Reliability<br>Requirements      | 62   |

|         |     | 3.1.2                           | Quantification of the Subsystem's Maintainability                  | 62   |

|         | 3.2 |                                 | e Test Subsystem Design Concept for Subsystem<br>ates (Step 2)     | 68   |

|         |     | 3.2.1                           | BIT LCC Trade-Off Model                                            | 68   |

|         |     | 3.2.2                           | BIT LCC Trade-Off Model Equations                                  | 68   |

|         |     | 3.2.3                           | Application of the BIT LCC Trade-Off Model                         | 70   |

|         | 3.3 | Configu                         | re Test Subsystem Architecture (Step 3)                            | 70   |

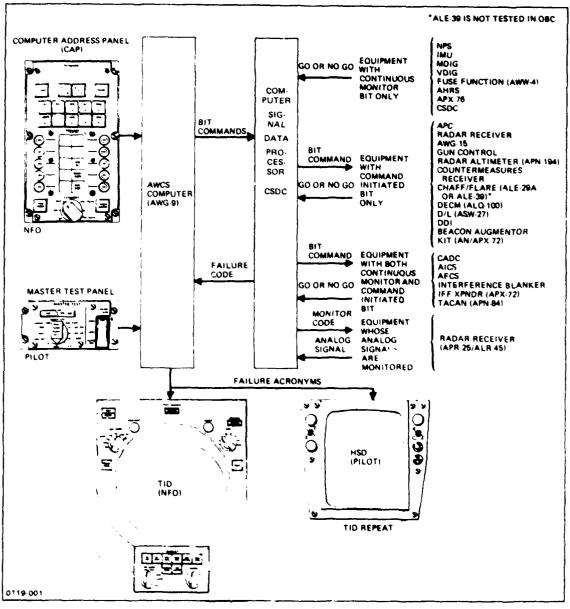

|         |     | 3.3.1                           | Avionics System PM/BIT Architecture                                | 72   |

|         |     | 3.3.2                           | Ground Electronic Systems PM/BIT Design                            | 79   |

|         | 3.4 | Select a                        | and Specify Test Subsystem Design (Step 4)                         | 82   |

|         |     | 3.4.1                           | Specification of the Test Subsystem Requirements.                  | 83   |

-

AC40146 - 1 19-1 1 1.

Constant where the state

| Section |      |          |                                                                     | Page           |

|---------|------|----------|---------------------------------------------------------------------|----------------|

| 4       | DESI | GN GUID  | ELINES AND PROCEDURES - SUBSYSTEM                                   |                |

|         | DESI | GN PHAS  | SE                                                                  | 88             |

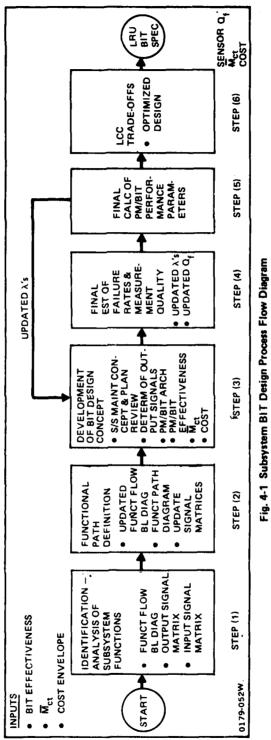

|         | 4.1  | Backgr   | ound and Summary of Methodology                                     | 88             |

|         | 4.2  | Identifi | cation/Analysis of Subsystem Functions (Step 1)                     | <del>9</del> 0 |

|         |      | 4.2.1    | Design Guidelines                                                   | 91             |

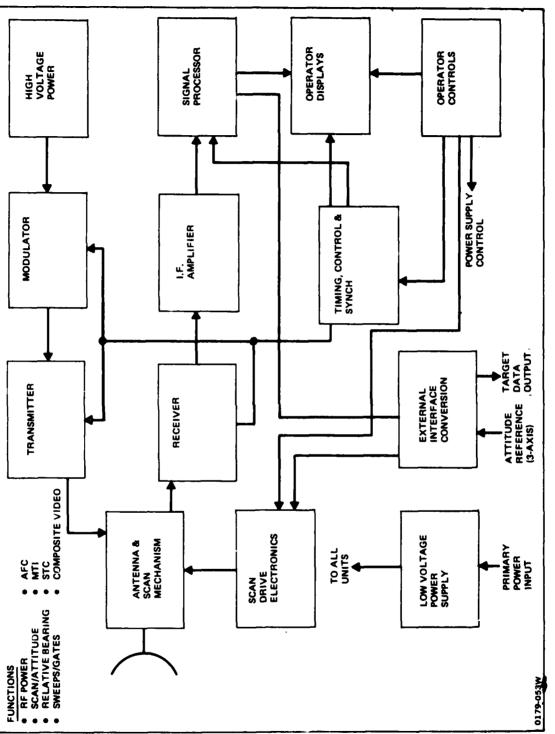

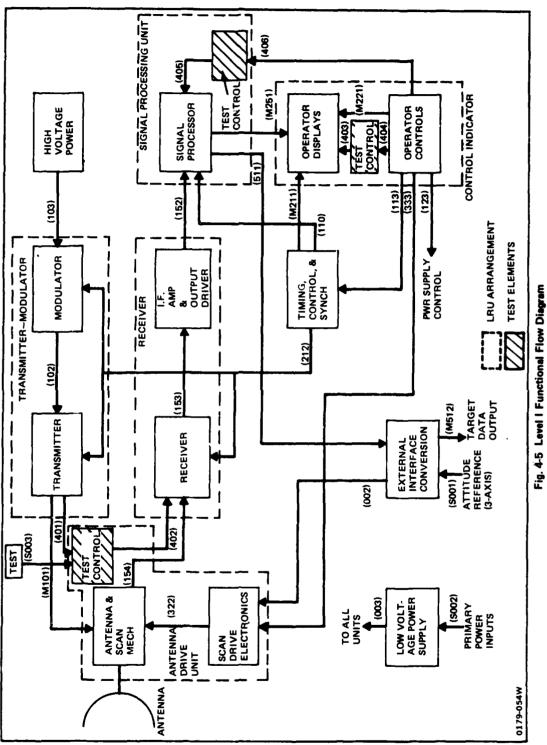

|         |      | 4.2.2    | Preparation of Level I Functional Block<br>Diagram (Step 1A)        | 92             |

|         |      | 4.2.3    | Preparation of Output Signal Matrix (Step 1B)                       | 92             |

|         |      | 4.2.4    | Preparation of Input/Stimulus Signal<br>Matrix (Step 1C)            | 103            |

|         | 4.3  | Functio  | nal Path Definition (Step 2)                                        | 108            |

|         |      | 4.3.1    | Design Guidelines                                                   | 109            |

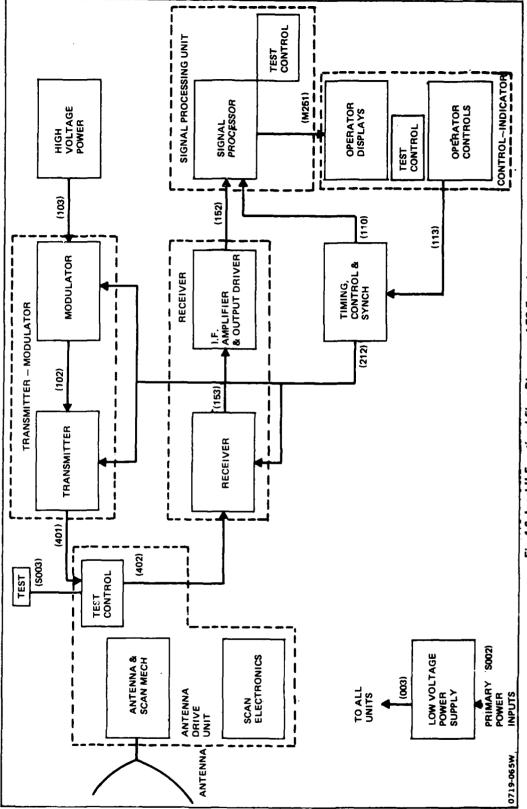

|         |      | 4.3.2    | Updated Level I Functional Flow Block<br>Diagram (Step 2A)          | 109            |

|         |      | 4.3.3    | Preparation of Level II Functional Flow<br>Block Diagrams (Step 2B) | 112            |

|         |      | 4.3.4    | Updating of Signal Matrices (Step 2C)                               | 112            |

|         | 4.4  | Develop  | oment of the PM/BIT Design Concept (Step 3)                         | 114            |

|         |      | 4.4.1    | Design Guidelines                                                   | 117            |

|         |      | 4.4.2    | Subsystem Maintenance Concept/Maintenance<br>Plan Review (Step 3A)  | 121            |

|         |      | 4.4.3    | Initial Determination of Output Signals<br>To Be Measured (Step 3B) | 122            |

|         |      | 4.4.4    | Development of a PM/BIT Architecture (Step 3C).                     | 127            |

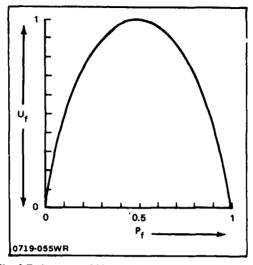

|         |      | 4.4.5    | Initial Estimation of PM/BIT Effectiveness<br>(Step 3D)             | 132            |

|         |      | 4.4.6    | Initial Estimate of Mean Test Time (Step 3E)                        | 134            |

|         |      | 4.4.7    | PM/BIT Cost Estimates (Step 3F)                                     | 136            |

|         |      | 4.4.8    | Adjustment of PM/BIT Design Concept (Step 3G).                      | 137            |

|         |      | 4.4.9    | Adjustment of Design Concept Effectiveness<br>Parameter (Step 3H)   | 140            |

|         |      | 4.4.10   | Adjustment $\overline{M}_{tt}$ Parameter (Step 3I)                  | 143            |

|         |      | 4.4.11   | System Effectiveness and $\overline{M}_{++}$ (Step 3J)              | 143            |

1. N. 1. N.

| Section |     |         |                                                                                                                                                                                                             | Page |

|---------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|         | 4.5 |         | 1 Estimate of Failure Rates and Measurement<br>(Step 4)                                                                                                                                                     | 145  |

|         |     | 4.5.1   | Design Guidelines                                                                                                                                                                                           | 145  |

|         |     | 4.5.2   | Updated Reliability Estimates (Step 4A)                                                                                                                                                                     | 147  |

|         |     | 4.5.3   | Updated Measurement Quality Estimates (Step 4B).                                                                                                                                                            | 148  |

|         | 4.6 |         | alculation of PM/BIT Performance and Cost<br>ters (Step 5)                                                                                                                                                  | 150  |

|         |     | 4.6.1   | Calculated Effectiveness, $\overline{M}_{tt}$ , and Production<br>Cost Meet the Requirements of the<br>Specification (Step 5A)                                                                              | 151  |

|         |     | 4.6.2   | Calculated Effectiveness and $\overline{M}_{tt}$ Are Less Than<br>Specified, and Costs Are Greater Than the<br>PM/BIT Production Cost Envelope (Step 5B)                                                    | 151  |

|         |     | 4.6.3   | Calculated Effectiveness and $\overline{M}_{tt}$ Are Not<br>Acceptable, while Costs Are Equal To or<br>Less Than the PM/BIT Production Cost<br>Envelope (Step 5C)                                           | 151  |

|         |     | 4.6.4   | Calculated Effectiveness Is Equal To or<br>Greater Than Specified, but the $\overline{M}_{t}$ Is Too<br>Great, while Costs Are Equal To or Less<br>Than the Cost Envelope Originally<br>Specified (Step 5D) | 152  |

|         |     | 4.6.5   | Calculated Effectiveness Is Equal To or<br>Greater Than Specified, but Both $M_{tt}$ and<br>Cost Appear Too Great (Step 5E)                                                                                 | 152  |

|         |     | 4.6.6   | Calculated Effectiveness Is Insufficient, while $\overline{M}_{tt}$ and Cost Are Both Acceptable (Step 5F)                                                                                                  | 153  |

|         |     | 4.6.7   | Calculated Effectiveness Is Insufficient, $\overline{M}_{tt}$<br>Is Acceptable, and Costs Are Too High<br>(Step 5G)                                                                                         | 153  |

|         |     | 4.6.8   | Calculated Effectiveness and $\overline{M}_{11}$ Are Acceptable,<br>but Costs Are Too Great (Step 5H)                                                                                                       | 153  |

|         | 4.7 | Life Cy | cle Cost Trade-Off (Step 6)                                                                                                                                                                                 | 153  |

|         | 4.8 | Specify | ing LRU Requirements                                                                                                                                                                                        | 154  |

xii

| Section          |              |          |                                                        | Page  |

|------------------|--------------|----------|--------------------------------------------------------|-------|

| 5                |              |          | DELINES AND PROCEDURES - DETAILED                      |       |

|                  |              |          | SE                                                     | 157   |

|                  | 5.1          | Backgr   | ound and Summary of Methodology                        | 157   |

|                  | 5.2          | Circuit  | Implementation Analysis (Step 1)                       | 159   |

|                  |              | 5.2.1    | Design Guidelines                                      | 159   |

|                  |              | 5.2.2    | Identification of Signal Failure Modes (Step 1A)       | 160   |

|                  |              | 5.2.3    | Modal Failure Rate Estimate (Step 1B)                  | 161   |

|                  |              | 5.2.4    | Analysis of Failure Detection, by Mode<br>(Step 1C)    | 162   |

|                  |              | 5.2.5    | Calculation of Signal Measurement Quality<br>(Step 1D) | 162   |

|                  | 5.3          | Calcula  | tion of Design Compliance (Step 2)                     | 163   |

|                  |              | 5.3.1    | Calculation of Effectiveness (Step 2A)                 | 163   |

|                  |              | 5.3.2    | Calculation of $\overline{M}_{++}$ (Step 2B)           | 164   |

|                  |              | 5.3.3    | Calculation of BIT Production Cost (Step 2C)           | 165   |

|                  |              | 5.3.4    | Assessment of BIT Life Cycle Cost Factors<br>(Step 2D) | 165   |

|                  | 5.4          | Design   | Adjustment (Step 3)                                    | 165   |

|                  | 5.5          | Prototy  | pe Test Planning (Step 4)                              | 166   |

|                  | 5.6          | Prototy  | pe Testing (Step 5)                                    | 167   |

|                  | 5.7          | Final D  | esign Adjustment (Step 6)                              | 167   |

|                  | 5.8          | Qualific | cation and Acceptance Test Considerations (Step 7).    | 167   |

|                  | 5.9          |          | entation of PM/BIT Design and Performance              | 168   |

| DEFINI<br>AND PA | TION<br>RAME | OF FREG  | QUENTLY USED ABBREVIATIONS, TERMINOLOGY,               | . 169 |

| BIBLIO           | GRAD         | HY       |                                                        | 175   |

|                  |              |          |                                                        | 175   |

| <u>APPENI</u>    |              | •        |                                                        |       |

| Append           | ix A         | BIT Lif  | fe Cycle Cost Trade-Off Model                          | 179   |

xiii

. .....

| Section    |                                                                                                                                          | Page |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Appendix B | Simulation, as Applied to the Optimization of<br>Built-in Test                                                                           | 189  |

| Appendix C | Simulated Application of the Subsystem BIT<br>Optimization Methodology                                                                   | 199  |

| Appendix D | Interrelationships Between Intermittent Malfunctions<br>and BIT False Alarms, and Some BIT Design<br>Guidelines Relating to These Issues | 241  |

xiv

الم ال

**的神**之。

# ILLUSTRATIONS

| Fig. |                                                                                              | Page |

|------|----------------------------------------------------------------------------------------------|------|

| 1-1  | Test Subsystem Design Optimization Procedure                                                 | 2    |

| 1-2  | Primary Reference Documents                                                                  | 4    |

| 1-3  | Time Phased Relationship Between the System Acquisition<br>Cycle and the System Design Cycle | 10   |

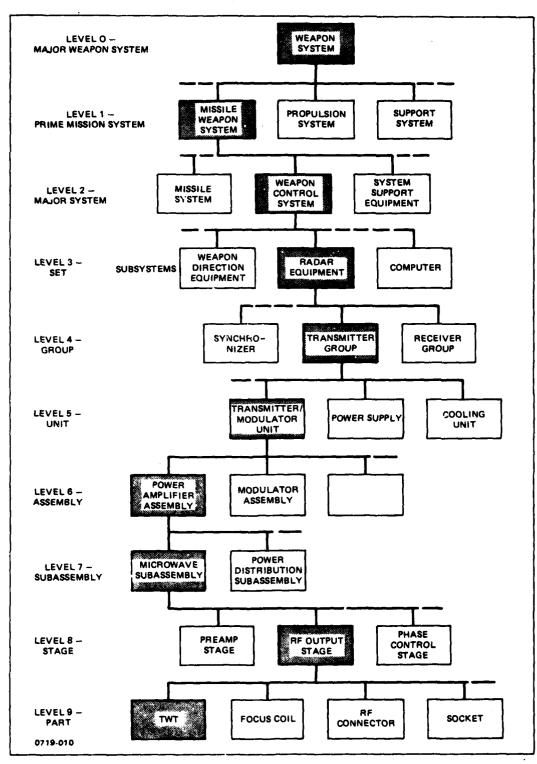

| 1-4  | Functional Level Breakdown of a Hypothetical Ground         Electronic System                | 14   |

| 1-5  | Reprint from AFLCP 800-3, "Logistics Performance Factors<br>in Integrated Logistic Support"  | 21   |

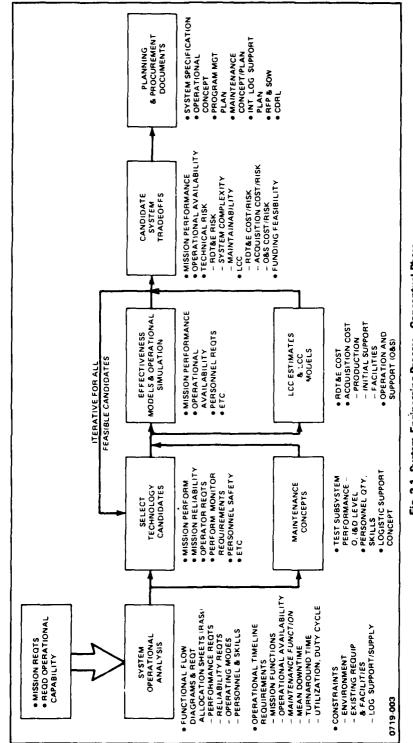

| 2-1  | System Engineering Process - Conceptual Phase                                                | 23   |

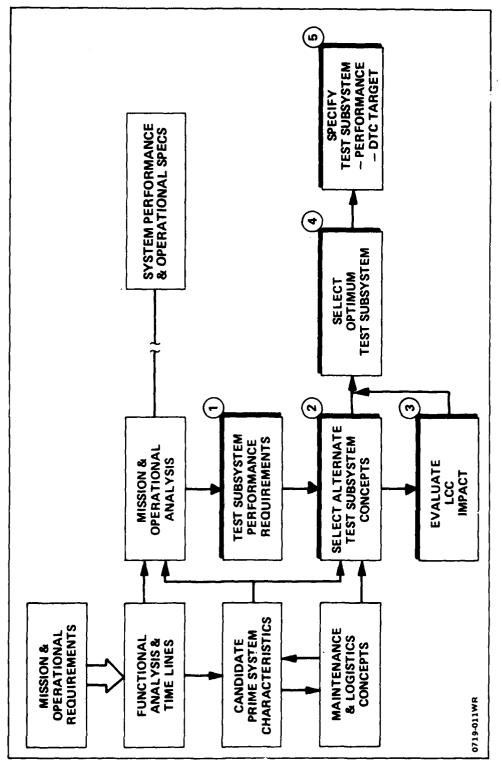

| 2-2  | Procedure for Test Subsystem Design - Concept Phase                                          | 26   |

| 2-3  | False Alarms? Symptoms vs Actual Problems                                                    | 30   |

| 2-4  | Undetected Failures? Symptoms vs Actual Problems                                             | 31   |

| 2-5  | State-of-the-Art (Circa '75-'80) Prime System vs Test<br>Subsystem Characteristics           | 33   |

| 2-6  | Theoretical Relationship Between Availability,<br>Maintainability and Reliability            | 37   |

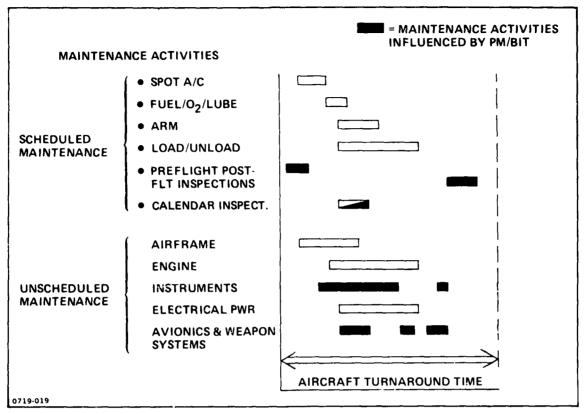

| 2-7  | Operational Mean Downtime                                                                    | 39   |

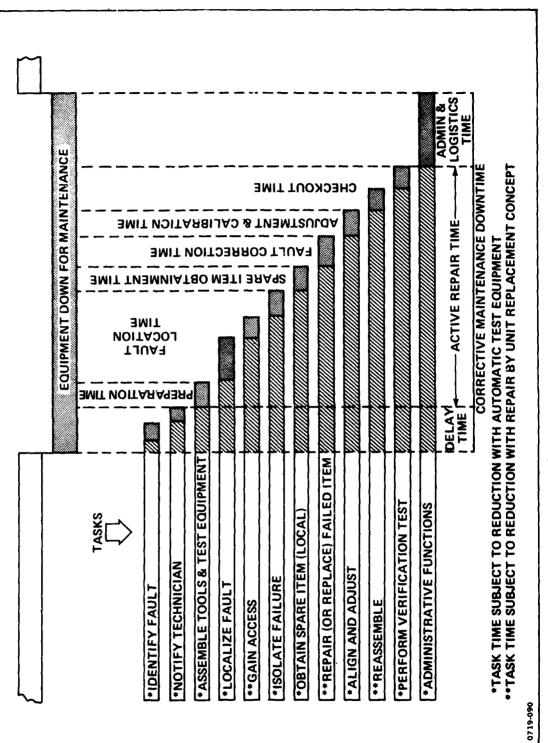

| 2-8  | Task and Time Composition of a Corrective<br>Maintenance Action                              | 40   |

| 2-9  | Mean Corrective Maintenance Time ( $ar{M}_{	extsf{ct}_{i}}$ ) for<br>Electronic Equipment    | 41   |

| 2-10 | Survey of Ground Equipment Operational<br>Demand vs Criticality                              | 43   |

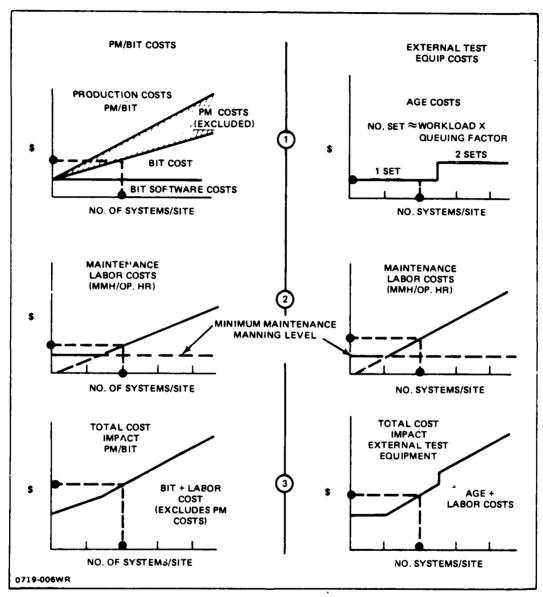

| 2-11 | PM/BIT vs External Test Equipment                                                            | 46   |

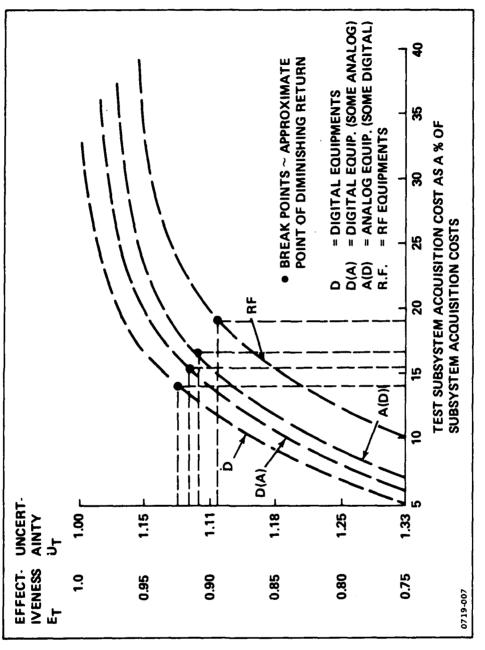

| 2-12 | Hypothetical Relation Between PM/BIT Performance<br>and Acquisition Cost                     | 50   |

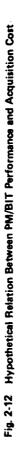

| 2-13 | Typical Breakdown of LCC Elements Affected by the Test Subsystem Design                      | 51   |

| 3-1  | System Engineering Process - System Design Phase                                             | 60   |

| 3-2  | Procedure for Test Subsystem Design - System<br>Design Phase                                 | 61   |

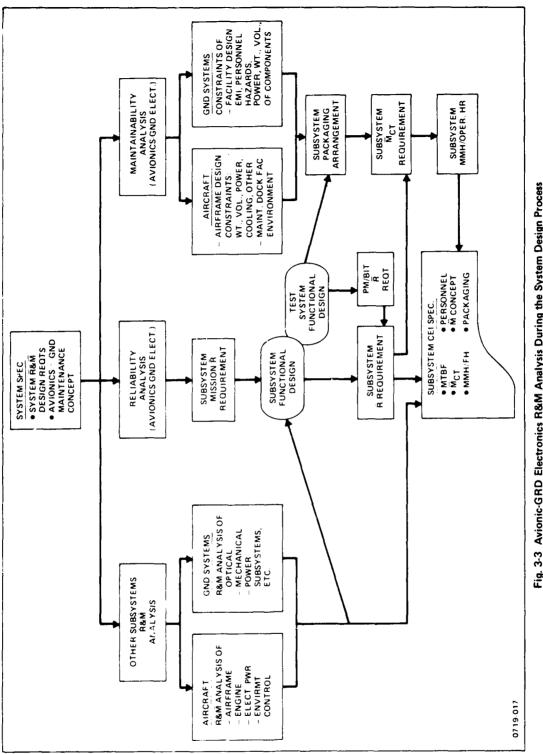

| 3-3  | Avionic-GRD Electronics R&M Analysis During the<br>System Design Process                     | 63   |

xv

# ILLUSTRATIONS (contd)

**54** -

| <u>rig</u> . |                                                                          | Page   |

|--------------|--------------------------------------------------------------------------|--------|

| 3-4          | Hypothetical Relation Between PM/BIT Performance<br>and Acquisition Cost | 67     |

| 3-5          | Procedure for Evaluating Existing Candidate Subsystem's                  |        |

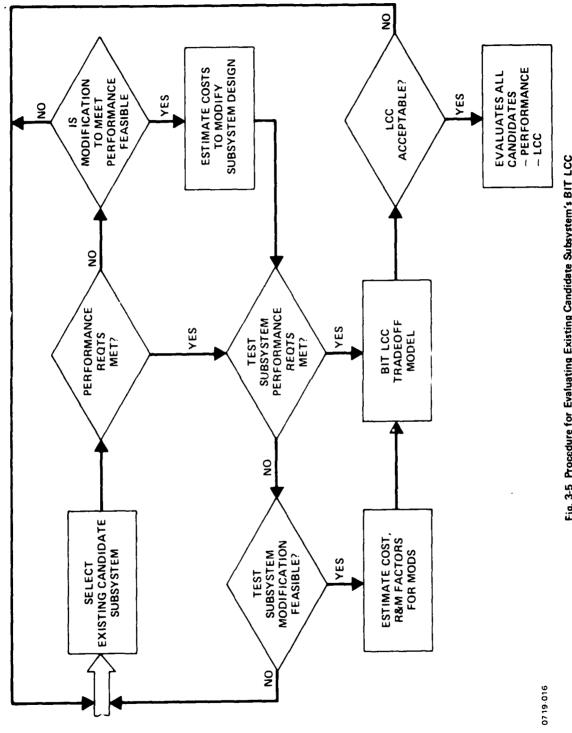

|              | BIT LCC                                                                  | 71     |

| 3-6          | F-14A PM/BIT Block Diagram                                               | 74     |

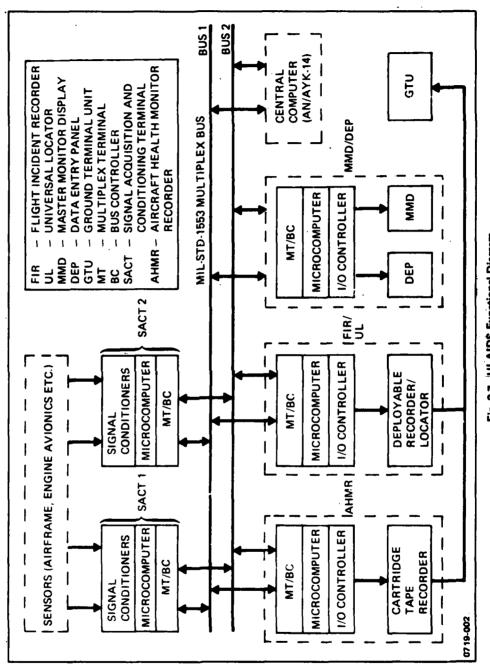

| 3-7          | ULAIDS Functional Diagram                                                | 77     |

| 4-1          | Subsystem BIT Design Process Flow Diagram                                | 89     |

| 4-2          | Level I Functional Flow Block Diagram                                    | 94     |

| 4-3          | Output Signal Matrix                                                     | 95/96  |

| 4-4          | Input/Stimulus Signal Matrix                                             | 105/6  |

| 4-5          | Level I Functional Flow Diagram                                          | 110    |

| 4-6          | Level II Functional Flow Diagram - AFC Function                          | 113    |

| 4-7          | Amount of Uncertainty Resolved by a Sensor                               | 126    |

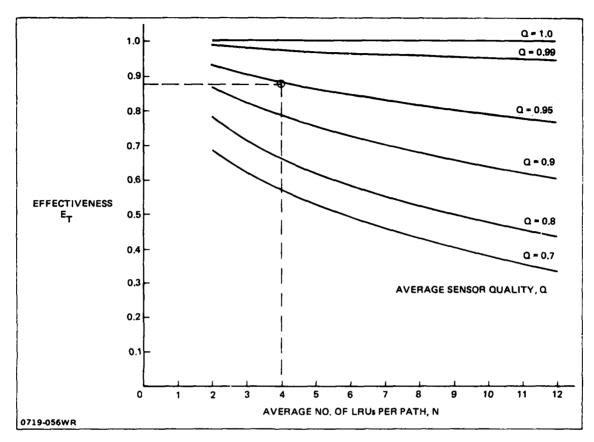

| 4-8          | Effectiveness as a Function of Measurement Quality and LRUs per Path     | 135    |

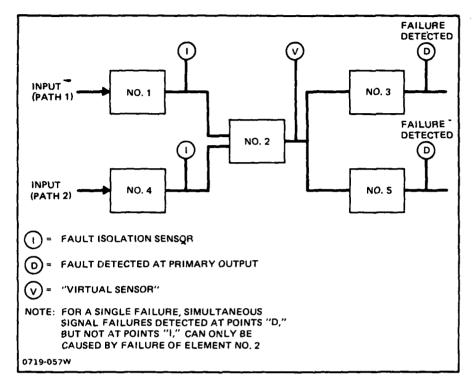

| 4-9          | Example of "Virtual Sensor"                                              | 139    |

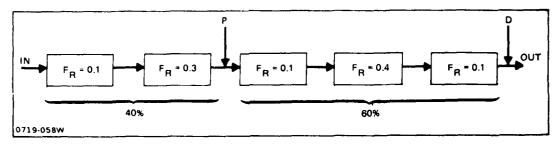

| 4-10         | Typical Signal Path                                                      | 141    |

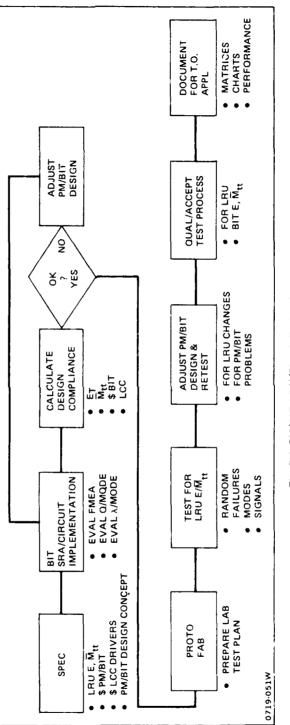

| 5-1          | PM/BIT LRU/Circuit Design Optimization                                   | 158    |

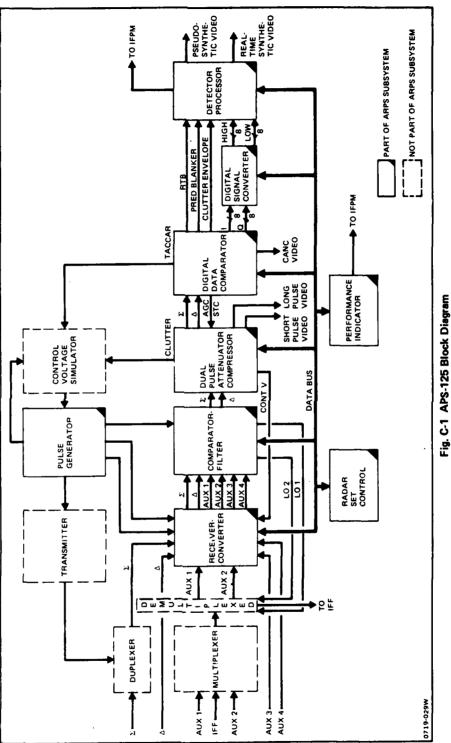

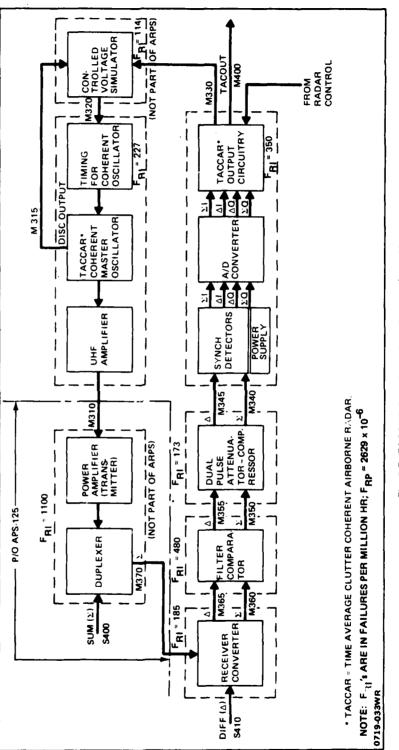

| C-1          | APS-125 Block Diagram                                                    | 201    |

| C-2          | Output Signal Matrix, Range (Step 1)                                     | 207/8  |

| C-3          | Output Signal Matrix, TACCAR                                             | 209/10 |

| C-4          | Input Signal Matrix, Range and TACCAR                                    | 211    |

| C-5          | TACCAR Functional Flow Diagram (Step 2)                                  | 212    |

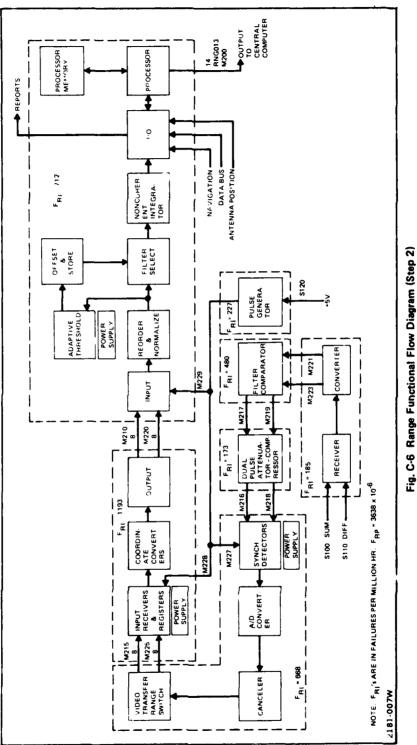

| C-6          | Range Functional Flow Diagram (Step 2)                                   | 213    |

| C-7          | Minimum Fault Indications and Characteristics                            | 215    |

| C-8          | Ranking of Sensors for Range Function                                    | 218    |

| C-9          | Ranking of Sensors for TACCAR Function                                   | 218    |

| C-10         | Range Function Proposed PM/BIT Output Configuration                      | 220    |

| C-11         | TACCAR Function Proposed PM/BIT Output Configuration                     | 221    |

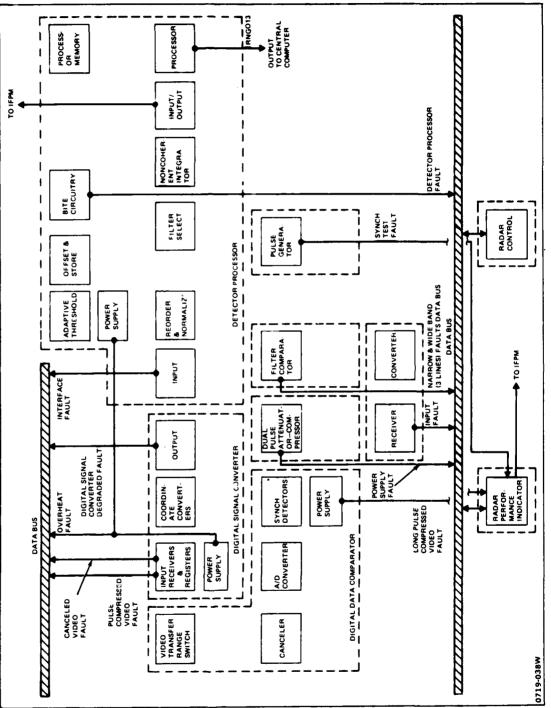

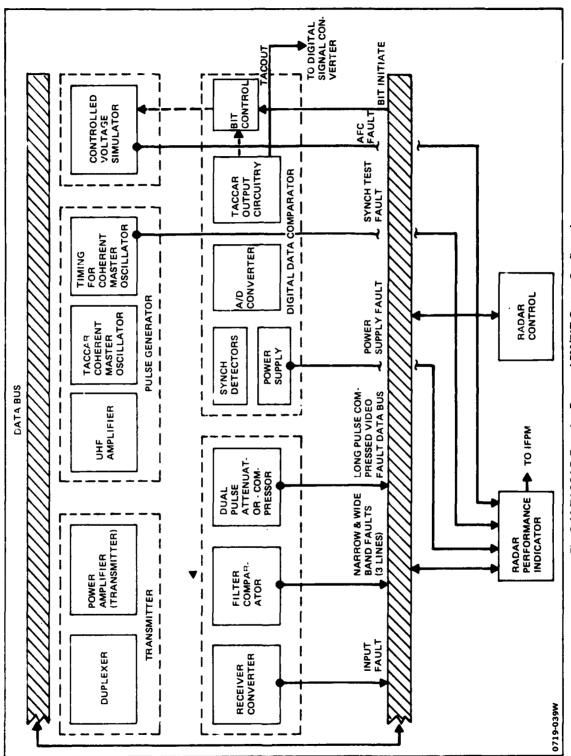

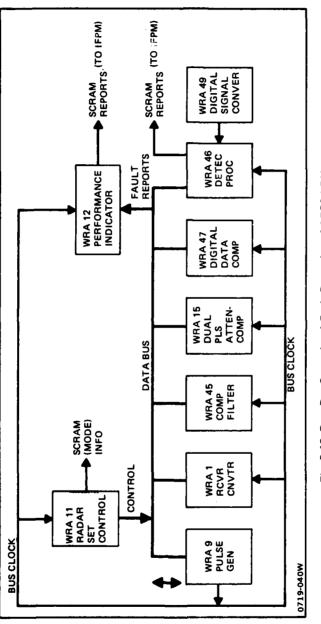

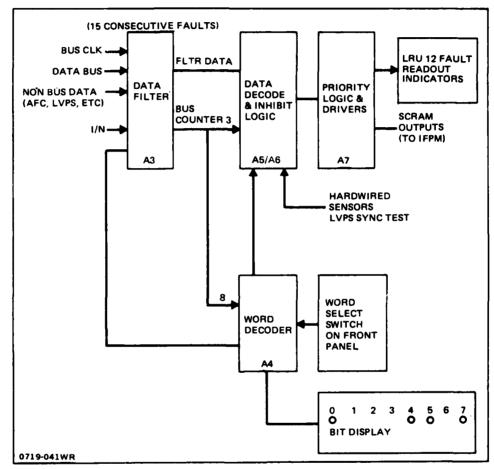

| C-12         | Data Bus Control and Fault Reporting of ARPS LRUs                        | 223    |

xvi

# ILLUSTRATIONS (contd)

| <u>Fig</u> . |                                                                                       | Page   |

|--------------|---------------------------------------------------------------------------------------|--------|

| C-13         | Performance Indicator Signal Processing Circuitry,<br>Block Diagram                   | 224    |

| C-14         | LRU Processing Times                                                                  | 226    |

| C-15         | Comparison of Parameters to the Design Specification                                  | 227    |

| C-16         | Maintenance Action Rate Due To Undetected Failures<br>for the Range Function          | 230    |

| C-17         | Maintenance Action Rate Due To Undetected Failures           for the TACCAR Function  | 230    |

| C-18         | Summary of Updated Measurement Quality Estimates,<br>Range Function                   | 232    |

| C-19         | Summary of Updated Measurement Quality Estimates,<br>TACCAR Function                  | 232    |

| C-20         | Revised Maintenance Action Rate Due To Undetected<br>Failures for the Range Function  | 233    |

| C-21         | Revised Maintenance Action Rate Due To Undetected<br>Failures for the TACCAR Function | 233    |

| C-22         | Summary of LRU PM/BIT Target Parameters and Costs                                     | 235    |

| C-23         | Example of Completed Output Signal Matrix (Range Function)                            | 237/8  |

| C-24         | Example of Completed Output Signal Matrix (TACCAR Function                            | 239/40 |

xvii

#### EVALUATION

1. The objective of this study was the investigation and development of optimization tools and algorithms that can be used during the design phases of a test subsystem, to aid in forming the most cost effective design configuration. The developed techniques were to take into account prime system failure rates, and test subsystem characteristics such as fault detection/isolation capabilities, false alarm rates, production costs and life cycle costs.

2. The methodology developed herein satisfactorily achieves the objectives for which it was intended. The methodology is applicable to all phases of the design of test subsystems. The study contains realistic design guidelines pertaining to the development of cost effective test subsystems. The optimization procedure is structured to systematically produce specified fault detection and isolation levels within a specified cost envelope.

3. The design and development of effective test subsystems is a critically important task in the effort to reduce the support costs associated with modern defense systems. The output of this study contributes to that end and will be used as input to future acquisition guides for test support

systems.

DANIEL GLEASON, 1Lt, USAF Project Engineer

xviii

#### 1. INTRODUCTION

Although there is a consensus that weapon systems and ground electronic systems maintenance and logistic costs are excessive, there is seldom agreement as to the causes. Built-In-Test (BIT) is a singular exception. The overwhelming evidence is that BIT performance has fallen far short of expectations. As a major cost driver, the failure of BIT to detect and fault-isolate impacts the entire spectrum of maintenance and logistic costs. The objective of this study is to develop optimization tools and algorithms that can be used to select the most cost-effective BIT designs.

### 1.1 SCOPE

Systematic methodologies and procedures for the design of BIT subsystems for avionic and ground electronics are to be developed. These techniques are to take into account the failure rate of each isolatable module, the total proportion of equipment faults that the BIT subsystem will recognize, the life cycle costs associated with fault detection and isolation of each failure, false alarm characteristics, and the resulting impact on equipment maintainability. All these factors, in combination, are to be used to guide the design of BIT subsystems

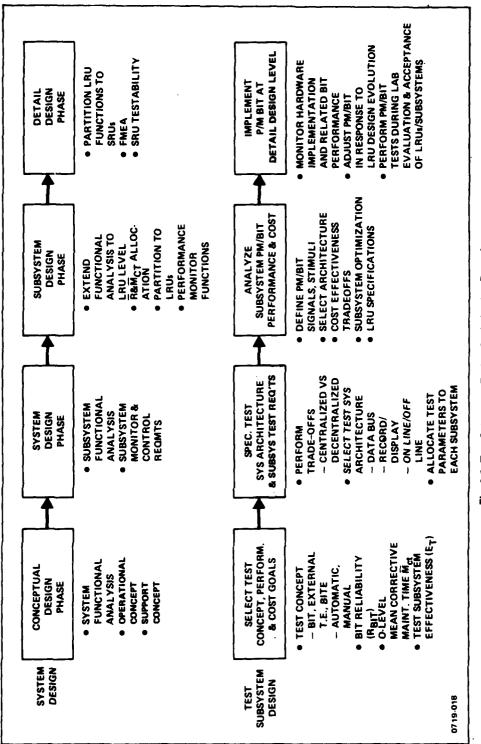

The quantitative requirements for a BIT subsystem are so inextricably woven into the prime system cost effectiveness equation that the determination of "how much and where" must be made as an integral part of the system design process. To optimize the BIT subsystem, its performance requirements must be analyzed and specified to the appropriate level during each phase of design. The only viable approach to deriving a systematic methodology is to include all phases of system design which are: the Conceptual Design Phase, the System Design Phase, the Subsystem Design Phase, and the Detailed Design Phase as shown by Fig. 1-1.

rig. 1-1 Test Subsystem Design Optimization Procedure

### 1.2 BACKGROUND

In present day military electronics, more and more use is being made of BIT to aid in maintenance. BIT usually makes it possible to have fewer and less qualified maintenance personnel and less external test equipment. However, even though the use of BIT is rapidly expanding, little research has been done to aid designers in how to apply BIT and diagnostics in a cost-effective fashion.

### **1.3 LITERATURE SEARCH**

The initial study task was to perform a thorough literature search and review existing technology to establish a state-of-the-art baseline from which the required BIT design procedures and diagnostic methodologies could be selected or developed.

Starting with an initial list of 44 books, articles, reports, and specifications, the study library grew to more than 100 reference documents. Most of these documents addressed procedures and methodologies to optimize a particular facet of detailed BIT circuit design. A few addressed the subject of test subsystem optimization procedures, giving general guidelines and "do's and don'ts" rather than quantitative data, mathematical tools, and trade-off procedures.

The documents and specifications which were most relevant and which formed the study baseline are listed in Fig. 1-2, together with the Design Phase addressed by that document.

Following Section 5 is a Bibliography of all references which are quoted or used in preparing this final report (see page 175).

### **1.4 TECHNICAL PROBLEMS**

The review of current military literature, specifications, and handbooks indicates that the fundamental principles of BIT design and optimization are frequently misunderstood or have not received adequate attention in the early phases of system design. In most cases, the first indication that performance requirements will not be met comes during the Full Scale Development Phase. In some cases additional funds are allocated to achieve improvements, such as greater reliability and effectiveness. In many cases, however, the BIT require-

|      |                                                                                                                                                                                                                  |   |            |   | DES        | GN PH     | ASE    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|---|------------|-----------|--------|

| ITEM | REFERENCE DOCUMENTS                                                                                                                                                                                              |   | CONCEPTUAL |   | aYSTEM     | SUBSYSTEM | DETAIL |

| 1    | AFLCP 800-3 LOGISTICS PERFORMANCE FACTORS IN INTEGRATED<br>LOGISTIC SUPPORT                                                                                                                                      | × |            | × | 1          |           |        |

| 2    | AFSC DH 1-9, MAINTAINABILITY DESIGN HANDBOOK, AIR FORCE<br>SYSTEMS COMMAND, 20 DECEMBER 1973                                                                                                                     | x |            | x | $\uparrow$ | x         | ·<br>  |

| 3    | ARINC RESEARCH CORPORATION, "A TECHNIQUE FOR EVALUATING<br>AVIONICS BUILT-IN TEST, FINAL REPORT," PREPARED FOR NAVAL<br>AIR SYSTEMS COMMAND, WASHINGTON, D.C. UNDER CONTRACT<br>N00019-71-C-0312, SEPTEMBER 1971 | × |            | x |            | x         | ×      |

| 4    | AFFDL-TR-123, MODULAR LIFE CYCLE COST MODEL FOR ADVANCED<br>AIRCRAFT SYSTEMS, AIR FORCE FLIGHT DYNAMICS LABORATORY,<br>OCTOBER 1976                                                                              | X |            | х |            | x         |        |

| 5    | AFSCM 375-5 SYSTEMS ENGINEERING MANAGEMENT PROCEDURES, 1966                                                                                                                                                      | X |            |   |            |           |        |

| 6    | A NOTE ON MAN-COMPUTER ADAPTIVE FAULT ISOLATION, S. I.<br>FIRSTMAN AND A. J. TRUELOVE, SYMPOSIUM FOR ADVANCED<br>MAINTAINABILITY, 1966                                                                           |   |            |   |            | x         | ×      |

| 7    | MIL-STD-1591 ON AIRCRAFT, FAULT DIAGNOSIS, SUBSYSTEMS<br>ANALYSIS/SYNTHESIS OF                                                                                                                                   |   |            |   |            | x         | ×      |

| 8    | NAVMATINST 3960.9, BUILT-IN TEST (BIT) DESIGN GUIDE, TEST AND<br>MONITORING SYSTEMS OFFICE (MAT 04T), NAVAL MATERIAL<br>COMMAND, 1 JULY 1976                                                                     | x |            | x |            | x         | x      |

| 9    | NAVORD OD 39223, MAINTAINABILITY ENGINEERING HANDBOOK                                                                                                                                                            | × |            | × |            | x         | x      |

| 10   | PERONNET, J. AND ROSENFELD, M., "BUILT-IN TEST IN AN ILS DESIGN<br>TO COST ENVIRONMENT," PROCEEDINGS OF THE SOCIETY OF<br>LOGISTIC ENGINEERS, 10TH INTERNATIONAL LOGISTICS SYMPOSIUM,<br>AUGUST 1975             |   |            |   |            |           |        |

| 11   | RADC-TR-71-281 DESIGN OF INTEGRAL SENSOR TEST SYSTEM, ROME<br>AIR DEVELOPMENT CENTER, REPORT AD-890479L                                                                                                          |   |            |   |            | x         | ×      |

| 12   | RADC-TR-69-356 MAINTAINABILITY PREDICTION AND DEMONSTRA-<br>TION TECHNIQUES, VOL. II, ROME AIR DEVELOPMENT CENTER,<br>REPORT NOS. AD 869396 AND AD 872873 (TR-70-89)                                             | x |            | × |            | ×         |        |

| 13   | RADC-TR-74-308, MAINTAINABILITY AND ENGINEERING DESIGN<br>NOTEBOOK, REVISION II, AND COST OF MAINTAINABILITY, ROME<br>AIR DEVELOPMENT CENTER, REPORT NOS. AD-A009043, A009044,<br>A009045, JANUARY 1975          | × |            | X |            | X         | ×      |

| 14   | STUDY TO ANALYZE THE ACQUISITION OF AUTOMATIC TEST<br>EQUIPMENT (ATE) SYSTEMS, U. S. NAVAL ELECTRONICS LABORA-<br>TORY CENTER                                                                                    | × |            | × |            | ×         | ×      |

Fig. 1-2 Primary Reference Documents

ments are simply lowered and the BIT system accepted without consideration of the resulting increase in maintenance and logistic costs.

The fundamental question to be answered by the study is, therefore, "How much funding should be expended to achieve what degree of BIT capability to meet the overall mission requirements?"

#### 1.4.1 Specifying BIT Effectiveness

The effectiveness of BIT has been specified for avionics in AR-10A as: "3.3.3 <u>Built in Test (BIT) Dependability</u> - The BIT features shall be such that at least 98% of the equipment failures shall be detected. At least 99% of the detected failures shall be located to the faulty WRA. At least 99% of the failure indications shall result from equipment failures (performance below acceptable levels)." Also: "3.4.2.2 <u>Non-Ambiguity (N-A) Ratio</u> - The ratio of the number of probable malfunctions detected and isolated directly to the WRA with built-intest features without ambiguity, to the total number of probable malfunctions, shall not be less than 0.97 unless otherwise specified in the detail specification. An example of this computation is shown in:

Non-ambiguity (N-A) ratio = Number of probable malfunctions isolated directly to faulty WRA/Total number of probable malfunctions"

BIT dependability and non-ambiguity as specified above are subject to interpretation, difficult (if not impossible) to measure in actual operations, and seldom, if ever, achieved.

Generalized maintainability and BIT requirements such as contained in AR-10A represented a significant step forward in 1969. However, the results of specifying either the "best that we can hope for" or "utopia" without regard to life cycle cost is not acceptable today. Rather, to optimize BIT, it must be specified in terms that are calculable during the systems engineering process and also measurable during system test, evaluation, and deployment.

The problem of specifying test effectiveness, (i.e., fault detection and isolation capability) for either BIT or external test equipment is complicated by the rapidly advancing state-of-the-art. The recorded performance of existing

test subsystems in the field (when available) is at best an inadequate measure of how much fault detection and isolation performance can be achieved.

Of equal importance, the problem of relating the BIT performance specification to its impact on system complexity, reliability, maintainability, and LCC remains virtually unaddressed in the current literature. Therefore, the derivation of means to specify BIT effectiveness is considered a prime objective of the study.

### 1.4.2 The BIT "Cost Data" Problem

Life cycle cost data are generally acknowledged to be elusive and inaccurate. Cost data for BIT are virtually non-existent since they are not an identifiable subsystem within the work-breakdown-structure (WBS) cost accounting system. With the exception of item 10 of Fig. 1-2, no substantive BIT cost data were found. While the "BIT LCC Trade-off Model" of Appendix A is an excellent vehicle for the collection of engineering estimates of LCC during the Design Phase, there is no apparent means to collect actual expended cost data for BIT hardware and software.

### 1.4.3 BIT "Performance Data" Problem

The basic objective of BIT or external testing is to detect and isolate equipment malfunctions to a replaceable unit. The measure of BIT performance, it would seem, is straightforward and could be recorded into the AFR 66-1/65-110 data system. However, the following issues complicate the recording of such data:

- False Alarms in which BIT falsely identifies an LRU as a malfunctioning unit where, in fact, there is no malfunction

- BIT Diagnostic Errors in which BIT incorrectly isolates an actual fault to one or more non-malfunctioning LRUs

- Undetected Failures in which BIT fails to detect a malfunctioning LRU

- BIT Ambiguity in which BIT detects a fault and correctly isolates to two or more LRUs

- Intermittents in which an electrical malfunction is present only at certain times, and which at all other times appears to be a false alarm.

This report addresses all of the above issues and their impact on the test subsystem design. However, these problems are not reported in the AFR 66-1/ 65-110 or the Navy 3M maintenance data systems. They can and should be included in a maintenance action tracking and analysis system to permit quantitative recording of their existence, analysis of their causes, and identification of corrective actions.

### 1.5 GENERAL METHODOLOGY

The DoD Acquisition Process emphasizes cost effectiveness and reduction of risk through validation, demonstration, and hardware proofing prior to production commitment. The process is one of optimizing the total system design. The "test subsystem" is an integral part of each system, subsystem, and LRU, and as such is not a uniquely identifiable subsystem. However, the term is useful in referring to the test points, BIT hardware and software, performance monitor, and external test equipment and will be used in that context throughout this report.

During the early system design phase, the engineering design progresses iteratively in increasing detail with the outputs of the preceding phase serving as the design requirements for the next phase. During these early phases the system designer requires mathematical tools for use in determining the optimum test subsystem (BIT or external), the degree of fault isolation to be achieved, and a valid projection of the resulting LCC benefits.

During the detailed design phase, the designer, who must implement actual hardware and software, requires similar mathematical tools tailored to his own disciplines. The cost/benefit aspect of his design must be weighed against its capability to detect and isolate faults. This means he needs a methodology to allocate BIT functions to those locations in his design where benefits are maximum per unit of life cycle cost.

The general methodology of the study then, is to address each phase of the system design cycle and provide optimization tools and procedures based on the evaluation and analysis of current literature and Grumman test subsystems design experience.

Because it is important that the tools and procedures be readily usable, we have performed a verification that simulated their application to an existing avionics subsystem E-2C Advanced Radar Processing System (ARPS) of the AN/APS-125 Radar System. (See Appendix C - Application of the Test Subsystem Coptimization Procedures).

### 1.5.1 Study Approach

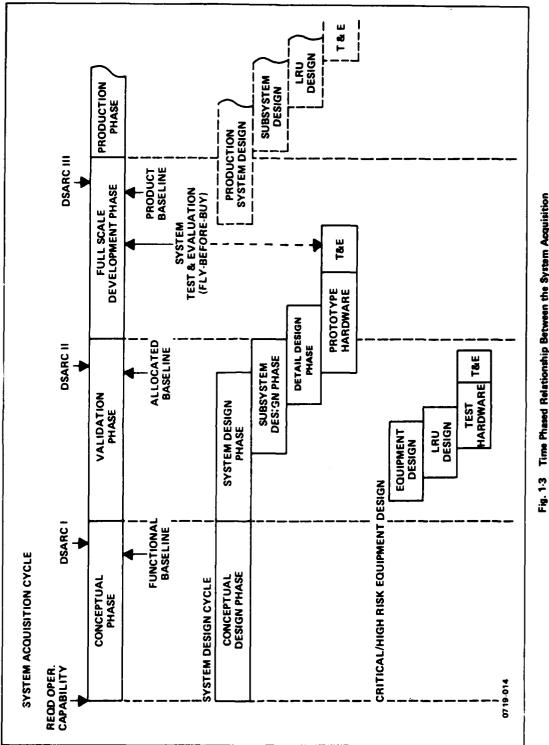

The design of a new system and the optimization of its test subsystem is an evolutionary process. Development proceeds in an orderly progression of system engineering during the System Acquisition Cycle, starting with the Conceptual Phase through the Production Phase as shown in Fig. 1-3. Optimization is achieved by applying the proven systems engineering methods of AFSCM 375-5 to the prime and subsystem designs to achieve a balance and depth of engineering effort during each phase.

The study approach has been influenced by our conviction that the optimization of a system or subsystem design is best achieved through strict adherence to the DoD system design procedures. The system engineering methods of AFSCM 375-5 and AFSCP 800-3, and the engineering management processes of MIL-STD-499A (USAF), as tailored to meet the needs of each program, provide the necessary methodology and management procedures to optimize the prime system design, including the test subsystem. Therefore, the study identified procedures consistent with the above referenced documents.

1.5.2 Fundamental Test Subsystem Optimization Concepts and Guidelines

The following concepts and guidelines are based on the review and evaluation of current literature, and Grumman experience in system design.

Early specification of test subsystem performance requirements and cost objectives is necessary.

Early, in this case, means during the Conceptual Design Phase. In the past, failure to specify these parameters early enough has led to a test capability that is sacrificed to achieve either greater prime system performance, reduced production cost, or both.

#### Optimization of built-in test must be accomplished by optimizing the system design.

BIT functions are not only inseparable from the prime mission functions of the system but are also critical to the performance of that mission. For example, if the BIT component or software fails, then the subsystem or LRU has failed since it can no longer perform as designed. BIT should not be deemed an entity that exists separately from the system's primary function and equipment.

The performance of the test subsystem must be specified in parameters which are observable, measurable, and reportable in field operation.

The parameters should be equally applicable to BIT, external test equipment, and built-in-test equipment.

The analysis and design of the test subsystem must include all components and all known failure modes.

It will be shown that the test subsystem performance, at its best, will be far from perfect.

The test subsystem must be treated as a high risk element of the system design.

The abilities of the circuit design engineer, the reliability engineer, and the maintainability engineer are severely taxed to perform a thorough failure mode and effects analysis (FMEA). It is improbable that a test subsystem can be designed to detect all possible malfunctions or to incorporate the infallible logic necessary for isolation to a single replaceable unit. Errors in paper analysis are magnified by the inability of the analyst to accurately predict the frequency of operational failures. Thus, the hardware and software designers are faced with an inaccurate knowledge of what will fail, and how often it will fail.

Other factors lead to the conclusion that the test subsystem is inherently a high risk design element:

- Intermittents cannot be readily isolated with state-of-the-art test subsystems (See Appendix D)

- Multiple faults cannot be accurately predicted or isolated with state-ofthe-art test subsystems

- Wiring harness and connector faults are generally not susceptible to BIT.

The study procedures and optimization tools presented herein provide a method of quantifying some of the above problems. The approaches taken in the study were to recognize that these problems exist, determine the elements of risk that they impose, and identify means to correct remaining design problems.

#### Early test and evaluation is required to optimize the test subsystem.

The time-phased relationship between the System Acquisition Cycle and the Design Cycle for new systems is shown in Fig. 1-3. Early prototype test and evaluation, during full scale development, is necessary for all complex, newly designed systems and subsystems. This will reduce the high risk elements of test subsystems with extensive BIT. Test and evaluation is necessary to identify and resolve the problems listed in the previous paragraph and the following additional problems which are not readily identified during the design process:

- BIT logic problems associated with multiple subsystem interfaces

- Signal tolerance problems which occur only when subsystems are married and operated as a system

- Operator and BIT human interface problems which cannot be predicted except in actual operation

- Maintenance personnel and BIT interface problems which cannot be predicted except in actual operation.

The prototype test and evaluation hardware must be close enough to the production system configuration to validate the BIT performance requirements specified in the Allocated Baseline Configuration Items (CI) Specification. Changes and modifications to achieve the specified performance are incorporated in the Product Baseline and Production CI Specifications.

To assure the quality of production BIT, formal qualification testing is required to demonstrate BIT performance. This requirement will ensure that BIT is utilized in maintenance of the prime system from its initial operation to its operational deployment.

# 1.6 DEFINITION OF SELECTED TERMS AND PARAMETERS

Definitions of common terms used in this report may be found in MIL-STD-1309 and MIL-STD-721. The definitions and discussions that follow involve selected terms whose meaning is unique to the study and/or which are frequently subject to misinterpretation.

#### 1.6.1 System

The study addressed the design of BIT and test equipment to support avionic and ground-based electronic systems. The term "system" will therefore refer to avionic and ground electronic equipment including its built-in test and/ or test equipment. When referring to the total weapon or ground system (e.g., F-15, F-4D, AN/FPS-27), the terms "prime system" or "host system" will be used. The procedure for BIT optimization will generally be applicable to both major or large scale system designs and to small scale systems except as noted in the text.

### 1.6.2 Subsystem

This term, as used in the study, denotes either a single equipment or a group of electronic equipments whose functions are interrelated within the group, but relatively isolated from those of other groups:

- Flight Controls and Displays

- Communication, Navigation, Identification (CNI)

- Weapon Control

- Weapon Delivery

- Electronic Countermeasures.

The definition of avionic subsystems will vary dependent upon the aircraft mission and the avionic system's design characteristics (i.e., attack, fighter, bomber, cargo) or the degree to which the functions are integrated (such as the CNI).

Ground electronic subsystems are extremely varied in function and complexity. For example, referring to Fig. 1-4, functional subsystems would be at either level 3 or 4, dependent upon the degree of autonomy. Figure 1-4 also illustrates the interdependence of systems and subsystems in specifying and achieving operational performance and maintainability goals.

# 1.6.3 Performance Monitor/BIT (PM/BIT)

Performance Monitoring equipment is designed to detect a malfunction within a series of critical functions. The monitoring equipment is required to alert the

...

.....

- 10

Mana Ball

۲

ni andra

يد ملا

Fig. 1-4 Functional Level Breakdown of a Hypothetical Ground Electronic System

14

operator of a failure or impending failure. Since performance monitoring equipment is required to achieve mission requirements, it is specified as one of the prime system functions.

Both hardware and software are required to control system operation as well as monitor performance. The performance monitoring function is accomplished using a multiplicity of sensors, displays, computer programs, and, in many cases, built-in-test equipment. The relation between the monitor function and BIT is complex and in many cases overlapping.

In this report BIT is defined as hardware and software added to the prime system for the sole purpose of detecting and isolating a malfunction to a replaceable unit. BIT does benefit from the overlap of Performance Monitoring capabilities. While the system designer will seek to optimize both BIT and System Performance Monitoring as a single integrated test subsystem, the cost and capabilities of the Performance Monitoring equipment cannot be traded off or degraded.

The following ground rule applies to the system analyst when dealing with the obvious overlap of Performance Monitoring and BIT (PM/BIT). They will be treated as a single combined function whose cost and performance is specified and designed as a single entity. However, during trade-off studies (e.g., BIT vs external test equipment) the costs of each (PM and BIT) must be estimated as separate entities and only the cost of BIT hardware will be considered in the trade studies.

#### 1.6.4 Mission Cost Effectiveness

During the Conceptual Phase, the analyst must evaluate alternative system configurations to achieve the desired Mission Effectiveness (E) at the lowest LCC. The interrelationship of prime system cost and effectiveness  $\frac{E}{\epsilon}$  is described by:

$$\frac{\mathbf{E}}{\mathbf{\xi}} = \mathbf{f} \left( \frac{\mathbf{PARS}}{\mathbf{LCC}} \right) \tag{Eq. 1}$$

where P = Performance, A = Operational Availability, R = Mission Reliability, S = Mission Survivability, and LCC = The Life Cycle Cost of the total system or subsystem.

The systems analyst must make both quantitative and qualitative judgments of the technological, military, and economic feasibility of the total system. The analysis and modeling of mission performance and survivability parameters are not a subject of this study. However, the MTBF used to calculate operational availability is impacted by BIT hardware and software.

The reliability of the cost effectiveness equation is the mission reliability:  $R = e^{-t/MTBF}$  (Eq. 2)

where t = mission time, and  $MTBF_0 = Operational$  mean time between failure.

The reciprocal of  $MTBF_0$  is the mission failure rate:

$$\lambda = \lambda_{\text{prime system}} + \lambda_{\text{BIT}}$$

(Eq. 3)

Operational availability is the unconditional probability that the system will be capable of operating at or above a specified level of performance if called upon to do so at a random point in time:

$$A_{0} = \frac{MTBF_{0}}{MTBF_{0} + MDT_{0}}$$

(Eq. 4)

where  $MDT_0$  = mean downtime, including active repair time, administrative time, and logistic delay time. Mean downtime is expressed as:

$$MDT_{o} = \overline{M}_{ct} + \overline{M}_{1} + \overline{M}_{a} + \overline{M}_{pt}$$

(Eq. 5)

where  $\overline{M}_{ct}$  = mean corrective maintenance time (active repair time),  $\overline{M}_1$  = mean logistic delay time,  $\overline{M}_a$  = mean administrative delay time, and  $\overline{M}_{pt}$  = mean preventive (scheduled) maintenance time and technical modification time.

Thus,  $MDT_0$  partly determines a prime system or subsystem's turnaround time (TAT). When combined with operational reliability, it defines the system or subsystem's operational availability.

The remaining term of the effectiveness equation (LCC) is also impacted by BIT. The classic elements of LCC as specified by DoD are:

- RDT&E

- Acquisition Cost (which includes Design, Production, and Ini<sup>\*</sup>ial Support Costs)

• Operation and Support (O&S) Costs.

These will be further defined in the sections that follow.

#### 1.6.5 Inherent Availability

Inherent availability is the conditional probability that a system or equipment will be capable of operating at or above a specified level of performance if called upon to do so at a random point in time, given that there is no waiting time for spares or delays before or during a maintenance action. This definition relates the readiness of the system or equipment to its inherent design characteristics and does not penalize the readiness assessment due to logistic shortages or administrative delays. Inherent availability, then, is the value which would be achieved under ideal conditions. It is defined as:

$$A_{i} = \frac{MTBF}{MTBF + M_{et}}$$

(Eq. 6)

where MTBF = the calculated mean time between failure, and  $\overline{M}_{ct}$  = the mean corrective maintenance time.

### 1.6.6 Corrective Maintenance Time and Mean Time to Repair

The terms  $M_{ct_i}$ ,  $\overline{M}_{ct_i}$ , and  $\overline{M}_{ct}$  will be used throughout this report. To avoid confusion, the abbreviation MTTR often denoted as  $\overline{M}_{ct}$  will not be used. The following definitions will be used:

- Corrective Maintenance Action the action required to repair a single failure, comprised of all those individual maintenance tasks (e.g., fault localization, isolation, repair, checkout, etc.) involved in the maintenance procedure. A maintenance event is comprised of one or more maintenance actions required to repair all failures associated with an equipment malfunction

- Individual Corrective Maintenance Task Time (M<sub>cti</sub>) the time required to complete an individual maintenance task or an individual maintenance action. Individual maintenance task or maintenance action times observed during a test, for example, would be denoted as M<sub>cti</sub>. When maintenance time estimates are based on an average of several observa-

tions, as used in prediction analysis for example, individual maintenance task or action times are denoted by  $\overline{M}_{ct_i}$  to indicate that the value is an average value for the individual task or action. The following notations for individual corrective maintenance time are used throughout and are interchangeable in the equations in which they appear:

- M<sub>cti</sub> = corrective maintenance required to complete the ith individual maintenance task or action, based on a single observation

- $-\overline{M}_{ct_i} = \frac{\Sigma M_{ct_i}}{N} = \text{average corrective maintenance time required to complete}$ the ith individual maintenance task or the ith individual maintenance action, averaged over several (e.g., N) observations for the same (ith) task or action

- <u>Mean corrective n.</u>  $tenance time (\overline{M}_{ct})$  the mean time required to complete a maintenance action, i.e., the total maintenance downtime divided by the total maintenance actions, over a given period of time. Mean corrective maintenance time is defined by MIL-STD-471 as the summation of all maintenance downtime during a given period divided by the number of maintenance actions during the same period of time, given as:

$$\overline{M}_{ct} = \Sigma(\lambda_i \ \overline{M}_{ct_i}) / \Sigma \lambda_i$$

(Eq. 7)

where  $\lambda_i$  = failure rate of the individual (ith) element of the item for which maintainability is to be determined, adjusted for duty cycle, catastrophic failures, tolerance and interaction failures, etc., which will result in deterioration of item performancé to the point that a maintenance action will be initiated and  $M_{ct_i}$ , in this case is the average repair time required to correct the ith repairable element in the event of its failure.

## 1.6.7 As-Designed MTBF vs MTBFo

$MTBF_0$  is the achieved apparent failure rate as reflected in AFR-66-1/65-110 data. It is expressed as:

$MTBF_{0} = \frac{Sum of operating hours for all systems}{Sum of all maintenance actions due to an indicated malfunction}$

where the number of maintenance actions includes "No-Defect Removals"  $(R_{nd})$ , "Repair in Place" (C), and "Remove and Replace"  $(R_r)$ .

The ratio of as-designed MTBF to operational  $MTBF_0$  is a heuristic K factor and will vary greatly according to system characteristics, maintenance policy, operational use of the equipment, and quality of maintenance. In general, the K factor represents the difference between the average (benign) environment for which MTBF is calculated and the actual multiplicity of environments (harsh) encountered for all operational systems. The K factor also accounts for the very real problems of maintenance induced failures, variable duty cycles, ground operate and off-line operate time, full systems capability vs alternate operational modes, etc. Regardless of the rationale, the K factor is very real as detailed below and must be used when converting from the as-designed MTBF to the operational MTBF<sub>0</sub>.

The following text and Fig. 1-5 are excerpted from AFLCP 800-3, "Logistic Performance Factors in Integrated Logistic Support," 19 April 1973, Section C, "Life Cycle Trends of Logistics Performance Factors," Pages 27, 28, and 29.

"It is common knowledge there is poor correlation between operational and design or test reliability. There is, however, a difference of this relationship. Many efforts have been made to compare operational MTBF with design MTBF and to determine why the lack of correlation. Results of these efforts have been the identification of reasons why they are different and the development of conversion or K factors by which to convert from one to the other. There are two categories of reasons for the difference; those that management can do something about, and those that are not subject to alteration by management. In addition to correcting the first, all agencies need to understand the latter in terms of the real world. In the first case, efforts are being made to standardize statistical elements and definitions used in measuring reliability through the life cycle, to develop a single-thread data system and prescribe more realistic test plans. In the second case, the production and test world does not simulate the operational world. We should not expect it to; we are not apt to spend the amount of test money that would be required to simulate a ten-year life cycle. As a consequence, mature reliability can only be measured during the operational

phase. Hardware characteristics alone do not determine operational results. Operational performance is affected by such things as:

- (1) Mission profile

- (2) Maintenance operating procedures and skills

- (3) Operational and maintenance concepts

- (4) Support and test equipment availability and effectiveness

- (5) Changes in operational requirements and use which exceed or differ from original specifications

- (6) Configuration changes after initial design

- (7) Systems interface of subsystems and equipment.

It is not likely that operation of military systems/equipment will be mandatorily constrained in a manner necessary to achieve precise correlation with design performance. Figure 14 [herein Fig. 1-5] provides additional insight into the relationship between test and operational reliability. Two additional factors are shown: The K factor which is the design or test MTBF divided by the operational MTBF and the & achieved which is the latter divided by the test MTBF. Both of these factors are useful in estimating one of the values when only the other is known. While general inferences can be drawn from these tables, the specific cause factors for variation in each equipment must be examined to determine appropriate corrective action if any, and K factors used in prediction of operational reliability should consider the particular system/equipment and mission being proposed."

|                                                              | MTBF, HR         |              |                   |            |  |

|--------------------------------------------------------------|------------------|--------------|-------------------|------------|--|

| MAJOR SUBSYSTEMS OR COMPONENTS                               | TEST MIN ACC     | к            | OPERATIONAL       | % ACHIEVE  |  |

| A-7D BOMB NAVIGATION SYS                                     |                  |              |                   | [          |  |

| FORWARD LOOKING RADAR                                        | 125              | 6.25         | 20                | 0.167      |  |

| WEAPON DELIVERY COMPUTER                                     | 650              | 6.84         | 95                | 0.146      |  |

| AIR DATA COMPUTER                                            | 500              | 2.85         | 175               | 0.350      |  |

| DOPPLER RADAR                                                | 250              | 5.20         | 48                | 0.192      |  |

| HEAD UP DISPLAY                                              | 350              | 3.97         | 88                | 0.251      |  |

| INERTIAL MEASUREMENT                                         | 325              | 4.22         | 77                | 0.237      |  |

| F-4 RADIO NAVIGATION SYS                                     |                  |              |                   |            |  |

| NAVIGATION COMPUTER SET                                      |                  |              |                   |            |  |

| (ASN 46A) (RF-4C)                                            | 320              | 8.00         | 40                | 0.125      |  |

| NAVIGATION COMPUTER SET (F-4E)                               | 320              | 3.67         | 87                | 0.272      |  |

| INERTIAL NAVIGATION SYS (RF-4C)                              | 175              | 4.60         | 38                | 0.217      |  |

| INERTIAL NAVIGATION SYS (F-4E)                               | 180              | 2.90         | 62                | 0.344      |  |

| LORAN (RF-4C)                                                | 50               | 2.00         | 25                | 0.500      |  |

| INTEGRATED ELECTRONIC CENTRAL                                |                  |              |                   | 1          |  |

| (ASQ-19A) (F-4C)                                             | 27.5             | 1.61         | 17                | 0.630      |  |

| INTEGRATED ELECTRONIC CENTRAL                                |                  |              |                   |            |  |

| (ASQ-19B) (F-4E)                                             | 27.5             | 0.85         | 32                | 1.16       |  |

| RADAR NAVIGATION SYSTEM                                      | 27.0             | 0.00         |                   |            |  |

| BADAR ALTIMETER (RF-4C)                                      | 400              | 15.38        | 26                | 0.065      |  |