AD-A233 110

RADC-TR-90-405 Final Technical Report December 1990

# QUALIFICATION PROCEDURES FOR VHSIC/VLSI

. Tini

**GE Aerospace**

Thomas A. Baumes

APPROVED FOR PUBLIC RELEASE; DISTRIBUTION UNLIMITED.

Rome Air Development Center Air Force Systems Command Griffiss Air Force Base, NY 13441-5700

91 3 14 019

This report has been reviewed by the RADC Public Affairs Division (PA) and is releasable to the National Technical Information Service (NTIS). At NTIS it will be releasable to the general public, including foreign nations.

RADC-TR-90-405 has been reviewed and is approved for publication.

APPROVED:

les & Messing

CHARLES G. MESSENGER Project Engineer

APPROVED:

Jahn? Sart

JOHN J. BART Technical Director Directorate of Reliability & Compatibility

FOR THE COMMANDER:

lam's

JAMES W. HYDE, III. Directorate of Plans & Programs

If your address has changed or if you wish to be removed from the RADC mailing list, or if the addressee is no longer employed by your organization, please notify RADC (RBRA) Griffiss AFB NY 13441-5700. This will assist us in maintaining a current mailing list.

Do not return copies of this report unless contractual obligations or notices on a specific document require that it be returned.

# DISCLAIMER NOTICE

THIS DOCUMENT IS BEST QUALITY AVAILABLE. THE COPY FURNISHED TO DTIC CONTAINED A SIGNIFICANT NUMBER OF PAGES WHICH DO NOT REPRODUCE LEGIBLY.

| REPORT DOC                                                                                                                                                                                                                                                                 |                                                                                                                                                                   |                                                                                                                           |                                                                                      | orm Approved<br>MB No. 0704-0188                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Public reporting burden for this collection of information I<br>gathering and maintaining the data needed, and complete                                                                                                                                                    | s estimated to average 1 hour per resor                                                                                                                           | nse, including the time for re                                                                                            | viewno instruction                                                                   | ns, searching existing data sources.                                                                                                      |

| colection of information, including suggestions for reduc<br>Davis Highway Suite 1204 Arlington, VA 22202-4302, and                                                                                                                                                        | ing this burden, to Washington Heedqu                                                                                                                             | arters Services, Directorate i                                                                                            | or Information Op                                                                    | erations and Reports, 1215 Jefferson                                                                                                      |

| 1. AGENCY USE ONLY (Leave Blank)                                                                                                                                                                                                                                           | 2. REPORT DATE<br>December 1990                                                                                                                                   | 3. F                                                                                                                      |                                                                                      | AND DATES COVERED                                                                                                                         |

| 4. TITLE AND SUBTILE                                                                                                                                                                                                                                                       |                                                                                                                                                                   | l,l,                                                                                                                      | 5. FUNDING                                                                           | NUMBERS                                                                                                                                   |

| QUALIFICATION PROCEDURES F                                                                                                                                                                                                                                                 | OR VHSIC/VLSI                                                                                                                                                     |                                                                                                                           | C - F3<br>PE - 63                                                                    | 0602-86-C-0172<br>3452F                                                                                                                   |

| 6. AUTHOR(S)                                                                                                                                                                                                                                                               |                                                                                                                                                                   |                                                                                                                           | PR - 27                                                                              |                                                                                                                                           |

| Thomas A. Baumes                                                                                                                                                                                                                                                           |                                                                                                                                                                   |                                                                                                                           | TA - 02<br>WU - 23                                                                   |                                                                                                                                           |

| 7. PERFORMING ORGANIZATION NAME(S                                                                                                                                                                                                                                          | ) AND ADDRESS(ES)                                                                                                                                                 |                                                                                                                           |                                                                                      | MING ORGANIZATION                                                                                                                         |

| GE Aerospace                                                                                                                                                                                                                                                               |                                                                                                                                                                   |                                                                                                                           | HEPORI                                                                               | NUMBER                                                                                                                                    |

| French Road<br>Utica NY 13503                                                                                                                                                                                                                                              |                                                                                                                                                                   |                                                                                                                           | N/A                                                                                  |                                                                                                                                           |

| 9. SPONSORING/MONITORING AGENCY                                                                                                                                                                                                                                            | NAME(S) AND ADDRESS(ES)                                                                                                                                           |                                                                                                                           |                                                                                      | ORING/MONITORING                                                                                                                          |

| Rome Air Development Cente                                                                                                                                                                                                                                                 | -                                                                                                                                                                 |                                                                                                                           | AGENC                                                                                | Y REPORT NUMBER                                                                                                                           |

| Griffiss AFB NY 13441-5700                                                                                                                                                                                                                                                 | I                                                                                                                                                                 |                                                                                                                           | RADC-TR                                                                              | -90-405                                                                                                                                   |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                                    | <u> </u>                                                                                                                                                          |                                                                                                                           | <u> </u>                                                                             |                                                                                                                                           |

| RADC Project Engineer: Ch                                                                                                                                                                                                                                                  | arles G. Messenger/                                                                                                                                               | RBRA/(315) 33                                                                                                             | 0-2047                                                                               |                                                                                                                                           |

| 12a. DISTRIBUTION/AVAILABILITY STATEN                                                                                                                                                                                                                                      | 1ENT                                                                                                                                                              | <u> </u>                                                                                                                  | 12b. DISTRI                                                                          | BUTION CODE                                                                                                                               |

| Approved for public releas                                                                                                                                                                                                                                                 | e; distribution unl                                                                                                                                               | imited.                                                                                                                   |                                                                                      |                                                                                                                                           |

| 13. ABSTRACT (Maximum 200 words)                                                                                                                                                                                                                                           |                                                                                                                                                                   |                                                                                                                           | _L                                                                                   | <del></del>                                                                                                                               |

| This program developed, ou<br>qualification criteria and<br>ity of microcircuit device<br>portion of the criteria ar<br>reduction in time and cost<br>by adressing up front simu<br>expensive manufacturing pr<br>(Statistical Process Contr<br>nology Review Board) and S | l procedures to be uses designed for inse<br>nd procedures, reflect<br>of the microcircus<br>ulations during desi<br>cocesses with in-lin<br>col) program and ong | ased to ensure<br>ertion into mi<br>ected herein,<br>it Quality/Rel<br>ign prior to c<br>ne quality pro<br>going QA Progr | the inte<br>litary sy<br>enables a<br>iability<br>ommitment<br>cesses co<br>am using | egrity and reliabil-<br>ystems. A major<br>a significant<br>Assurance process<br>t, complex and<br>ontrolled by a SPC<br>their TRB (Tech- |

| 14. SUBJECT TERMS                                                                                                                                                                                                                                                          |                                                                                                                                                                   |                                                                                                                           |                                                                                      | 15. NUMBER OF PAGES                                                                                                                       |

| Microcircuits, QML, Qualif<br>Generic Qualification, Int                                                                                                                                                                                                                   |                                                                                                                                                                   |                                                                                                                           |                                                                                      | 16 PRICE CODE                                                                                                                             |

|                                                                                                                                                                                                                                                                            | SECURITY CLASCIFICATION<br>OF THIS PAGE<br>UNCLASSIFIED                                                                                                           | 19. SECURITY CLAS<br>OF ABSTRACT<br>UNCLASSIE                                                                             |                                                                                      | 20. LIMITATION OF ABSTRACT<br>UL                                                                                                          |

| NSN 7540-01-280-5500                                                                                                                                                                                                                                                       |                                                                                                                                                                   |                                                                                                                           |                                                                                      | Standard Form 298 (Rev. 2 89)<br>Prescribed by ANSI Std. Z39-11<br>298-102                                                                |

1

Ľ

#### **EVALUATION**

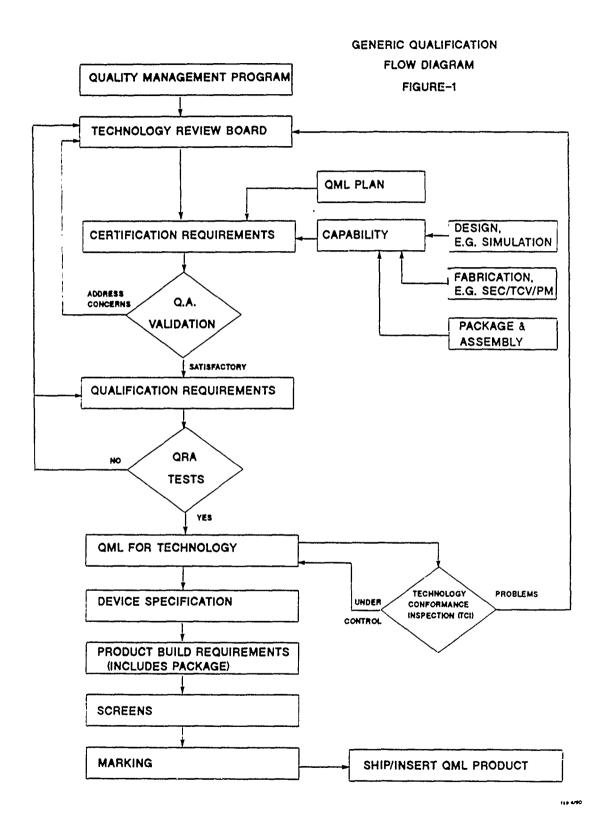

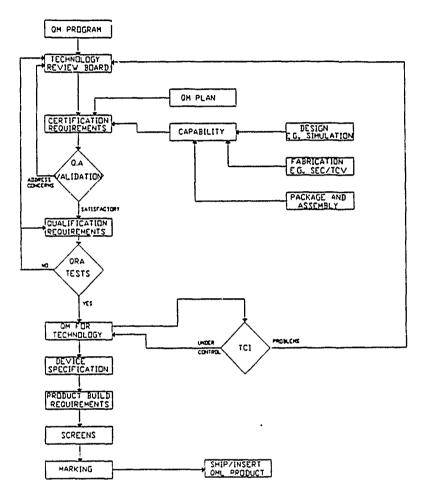

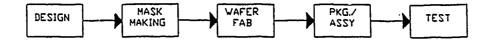

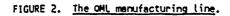

This program was sponsored by the VHSIC program office to investigate and develop an alternative approach for gualification of complex microcircuits. To address the technical issues related to a process oriented qualification approach, the contractor organized an Industry Coordinating Working Group (ICWG) which was divided into four microcircuit manufacturing disciplines: design, fabrication, assembly, and test. The ICWG spawned and refined several key concepts, such as Technology Review Board (TRB), Technology Characterization Vehicle (TCV) and Standard Evaluation Circuit (SEC). These concepts were then integrated with Total Quality Management (TQM) principles and formulated the basis for the Qualified Manufacturer's List (OML).

The final output of the program was a DOD specification MIL-I-38535, "General Specification for Integrated Circuit Manufacturing." This document details the requirements a manufacturer must address in order to be listed on the QML. Presently, several refinements to the requirements are ongoing. These refinements are addressing issues related to radiation hardness and third party design. Overall, this program was very successful and providesd the DOD with an approach to qualifying high complexity Application Specific Integrated Circuits (ASIC) for system usage.

CHARLES G. MESSENGER

Accesion 1 or NTIS CRACE DTIC 14.3 Unarrion cod Justification Ву ..... Dist 也 dio 于 ----Available 1, where Ava: 6 4. or Dict Sp):Cidi ESTED

NIALITY

З

| 1.   | INTRODUCTION       | ]-1 |

|------|--------------------|-----|

| 1.1. | GENERAL            | 1-1 |

| 1.2. | PROGRAM OBJECTIVE  | 1-1 |

| 1.3. | SUMMARY OF RESULTS | 1-2 |

| 2.       | TASK I - REVIEW OF DOCUMENTS                          | 2-1  |

|----------|-------------------------------------------------------|------|

| 2.1.     | OBJECTIVES                                            | 2-1  |

| 2.2.     | APPROACH                                              | 2-2  |

| 2.3.     | RESULTS                                               | 2-3  |

| 2.3.1.   | MIL-M-38510F: General Specification for Microcircuits | 2-3  |

| 2.3.1.1. | Discussion of MIL-M-38510F                            | 2-3  |

| 2.3.1.2. | Major Findings in MIL-M-38510F                        | 2-4  |

| 2.3.2.   | MIL-STD-883C                                          | 2-5  |

| 2.3.2.1. | Discussion of Series 1000 and 2000 Methods            | 25   |

| 2.3.2.2. | Major Findings in 1000 and 2000 Series                | 2-5  |

| 2.3.2.3. | Discussion of 3000 Series                             | 2-8  |

| 2.3.2.4. | Major Findings in 3000 Series                         | 2-10 |

| 2.3.2.5. | Discussion of 4000 Series                             | 2-13 |

| 2.3.2.6. | Major Findings in 4000 Series                         | 2-13 |

| 2.3.2.7. | Discussion of 5000 Series                             | 2-15 |

| 2.3.2.8. | Major Finding in 5000 Series                          | 2-17 |

| 2.3.3.   | MIL-STD-976A                                          | 2-17 |

| 2.3.3.1. | Discussion of MIL-STD-976A                            | 2-17 |

| 2.3.3.2. | Major Findings in MIL-STD-976A                        | 2-18 |

| 2.3.4.   | MIL-STD-1331                                          | 2-18 |

| 2.3.4.1. | Discussion of MIL-STD-1331                            | 2-18 |

| 2.3.4.2. | Major Findings in MIL-STD-1331                        | 2-19 |

| 2.4.     | SUMMARY                                               | 2-19 |

| 3.       | TASK II - INVESTIGATION                     | 3-1  |

|----------|---------------------------------------------|------|

| 3.1.     | INTRODUCTION                                | 3-1  |

| 3.2.     | INDUSTRY COORDINATING WORKING GROUP (ICWG)  | 3-1  |

| 3.2.1.   | ICWG Organization                           | 3-1  |

| 3.2.2.   | Quality Management ICWG Subcommittee        | 3-2  |

| 3.2.3.   | Design and Test ICWG Subcommittee           | 3-2  |

| 3.2.3.1. | Topics of Discussion                        | 3-2  |

| 3.2.3.2. | Major Results                               | 3-3  |

| 3.2.4.   | 「.brication ICWG Subcommittee               | 3-5  |

| 3.2.4.1. | Tooses of Discussion                        | 3-5  |

| 3.2.4.2. | Major Results                               | 3-6  |

| 3.2.5.   | Assembly/Packaging ICWG Subcommittee        | 3-9  |

| 3.2.5.1. | Topics of Discussion                        | 3-9  |

| 3.2.5.2. | Major Results                               | 3-9  |

| 3.2.6.   | SQC/QRA ICWG Subcommittee                   | 3-12 |

| 3.2.6.1. | Topics of Discussion                        | 3-12 |

| 3.2.6.2. | Major Results                               | 3-13 |

| 3.3.     | DRAFT OF QML REQUIREMENTS - APRIL '88 DRAFT | 3-14 |

| 3.3.1.   | Manufacturer's QA Program Plan              | 3-15 |

| 3.3.1.1. | QA Program Plan-Section A                   | 3-15 |

| 3.3.1.2. | QA Program Plan-Appendix 1 of Section A     | 3-16 |

| 3.3.1.3. | QA Program Plan-Section B                   | 3-18 |

| 3.3.2.   | Self Audit                                  | 3-18 |

| 3.3.2.1. | Self Audit-Section A                        | 3-18 |

| 3.3.2.2. | Self Audit-Appendix 1 of Section A          | 3-18 |

| 3.3.3.   | Technology Review Board (TRB)               | 3-19 |

| 3.3.3.1. | Technology Review Board-Section A           | 3-20 |

| 3.3.4.   | Total Quality Management/Control (TQM/TQC)  | 3-23 |

i

| 3.3.4.1. | Total Quality Management/Control (TQM/TQC)-               |      |

|----------|-----------------------------------------------------------|------|

|          | Appendix 1 of Section A                                   | 3-23 |

| 3.3.5.   | Statistical Process Control-Section A                     | 3-23 |

| 3.3.5.1. | Statistical Process Control-Appendix 1 of Section A       | 3-23 |

| 3.3.5.2. | Statistical Process Control-Section B                     | 3-23 |

| 3.3.6.   | Standard Evaluation Circuit (SEC)-Section A               | 3-24 |

| 3.3.6.1. | Standard Evaluation Circuit (SEC)-Section A               | 3-24 |

| 3.3.6.2. | Standard Evaluation Circuit (SEC)-Appendix 1 of Section A | 3-24 |

| 3.3.6.3. | Standard Evaluation Circuit (SEC) Section B               | 3-25 |

| 3.3.6.4. | Standard Evaluation Circuit (SEC)-Appendix 1 of Section B | 3-25 |

| 3.3.7.   | Quarterly Report                                          | 3-26 |

| 3.3.7.1. | Quarterly Report-Section A                                | 3-26 |

| 3.3.7.2. | Quarterly Report-Appendix 1 of Section A                  | 3-26 |

| 3.4.     | SUMMARY                                                   | 3-26 |

|          |                                                           |      |

| TASK III - DEMONSTRATION AND GENERAL SUPPORT | 4-1                                                                                                                                                                                                                                                   |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION                                 | 4-1                                                                                                                                                                                                                                                   |

| ALPHA SITE DEMONSTRATIONS                    | 4-1                                                                                                                                                                                                                                                   |

| Alpha Site Validation                        | 4-2                                                                                                                                                                                                                                                   |

| Pre Validation Submittal                     | 4-2                                                                                                                                                                                                                                                   |

| Validation Reviews                           | 4-2                                                                                                                                                                                                                                                   |

| BETA SITE DEMONSTRATIONS                     | 4-5                                                                                                                                                                                                                                                   |

| Companies Involved in Beta Sites             | 4-5                                                                                                                                                                                                                                                   |

| Progress                                     | 4-5                                                                                                                                                                                                                                                   |

| BETA SITE MEETINGS                           | 4-5                                                                                                                                                                                                                                                   |

| GENERAL SUPPORT                              | 4-6                                                                                                                                                                                                                                                   |

| Handbook                                     | 4-6                                                                                                                                                                                                                                                   |

| Proposed Test Methods                        | 1-6                                                                                                                                                                                                                                                   |

|                                              | INTRODUCTION<br>ALPHA SITE DEMONSTRATIONS<br>Alpha Site Validation<br>Pre Validation Submittal<br>Validation Reviews<br>BETA SITE DEMONSTRATIONS<br>Companies Involved in Beta Sites<br>Progress<br>BETA SITE MEETINGS<br>GENERAL SUPPORT<br>Handbook |

1

1

| 5.     | CONCLUSIONS AND RECOMMENDATIONS | 5-1 |

|--------|---------------------------------|-----|

| 5.1.   | CONCLUSIONS                     | 5-1 |

| 5.1.1. | Design                          | 5-1 |

| 5.1.2. | Fabrication                     | 5-1 |

| 5.1.3. | Assembly and Packaging          | 5-2 |

| 5.1.4. | Test                            | 5-2 |

| 5.2.   | RECOMMENDATIONS                 | 5-3 |

| Appendix A | General Specification for Integrated Circuits (Microcircuits)<br>Manufacturing |

|------------|--------------------------------------------------------------------------------|

| Appendix B | Proposed Test Methods for VHSIC/VLSI Generic Qualification                     |

| Appendix C | Proposed Requirements to Qualify CAD Tools for VHSIC/VLSI<br>Devices           |

# 1. INTRODUCTION

# 1.1. GENERAL

In September of 1986, GE/AES, Utica, NY received a contract to develop a Generic Qualification approach to microcircuit qualification that would not only benefit the military acquisition arena but also develop a methodology of microcircuit process control to promote the United States to a position of supplying the nighest quality and most reliable microcircuits in the world. This contract was awarded and administered by RADC.

In order to expand the technical team and provide expertise in the areas of commercial and bi-polar techniques and technologies, two subcontracts were awarded by GE to AT&T Bell Lab, Allentown PA and Honeywell Inc, Plymouth MN.

This effort was performed in conjunction with the VHSIC Program and the DOD effort to streamline the acquisition and costs of microcircuits used by the DOD. The Industry Coordinating Working Group (ICWG) which included the Government, Industry and Academia was formed to provide technical insights, critiques, and guidance in support of this effort.

# 1.2. PROGRAM OBJECTIVE

This program was derived to develop a new approach to qualifying complex microcircuits. Recent trends in military systems showed that there was wider use of low volume, complex, application specific integrated circuits and less reliance on high volume standard microcircuits. As a result there was an explosive increase of nonstandard, noncertified and nonqualified microcircuits in new systems. This raised concerns over system logistic support, reliability and availability.

Also studies of the DOD VHSIC program suggested that it was no longer economical to qualify piece parts using existing qualification procedures, due to the cost, complexity and relatively low quantity production of individual VHSIC/VLSI device designs. The advent of Computer Aided Design (CAD) tools which accurately simulate and predict device performance before

actual production allowed for more efficient and economical means of production and testing thus allowing quality and reliability to be designed in instead of tested in.

These issues along with the inability of the existing qualified parts list (QPL) system to handle these new device trends were the impetus for this program.

The objective, then, of this program was to develop a new approach to microcircuit qualification based on process control while taking advantage of new tools, such as Statistical Process Control (SPC) and CAD, and assure the quality and reliability for use in military systems of those devices produced from that process. All aspects related to microcircuit manufacturing from design through final test were to be addressed in the new procedures.

Three tasks were defined to accomplish this objective:

- Task I Review and Definition review existing procedures for applicability to VHSIC/VLSI devices.

- Task II Investigation research technical issues through the establishment of an Industry Coordinating Working Group (ICWG) and propose new procedures.

- Task III Verification and Demonstration verify and demonstrate the new procedures on the contractors' manufacturing process. Make improvements to the procedures based on the outcome of the demonstration.

# 1.3. SUMMARY OF RESULTS

The Qualification Procedures for VHSCI/VLSI program resulted in the following major accomplishments:

Existing military documents associated with microcircuit qualification were reviewed for applicability. This review outlined several areas where changes were necessary to facilitate the qualification of complex VHSIC/VLSI devices in military systems. To better address these issues and develop technical approaches, an Industry Coordinating Working Group (ICWG) was established. The ICWG recommended a quality management oriented approach to the problem. The contract team of GE, AT&T and Honeywell utilized many of the proposed recommendations of the ICWG in formulating a draft procedure.

Finally, a qualification procedure document was developed, completed and issued (on 18 Dec 1989) as MIL-I-38535, "INTEGRATED CIRCUIT MANUFACTURING, GENERAL SPECIFICATION FOR" (see Appendix-A). The MIL-I-38535 document establishes the general procedures and the quality and reliability assurance requirements for the manufacturing and acquisition of integrated circuits. Key to quality and reliability assurance is the requirement for quality management. Through quality management, a manufacturer is positioned to provide to the marketplace a cost effective, high quality and reliable microcircuit within the DoD acquisition requirements, as well as the commercial requirements, as a qualified manufacturer. Also, the DoD is ensured of the best possible integrated circuits qualified and ready for insertion in shorter cycle times.

Alpha site demonstrations were performed by GE and AT&T to provide confirmation of the applicability of the new procedures. Based on the results, changes to the QML requirements were recommended and implemented in MIL-I-38535. Following Alpha site demonstrations, Beta site meetings were held to further enhance the requirements applicability and acceptance.

Other outputs of this program included draft versions of new test methods for testing digital microcircuits. Also, a Manufacturing Guidelines document was developed to provide an up-to-date index of tools which can be utilized to improve manufacturing quality.

The particulars of these tasks are discussed in more detail in the following sections.

# 2. TASK I - REVIEW OF DOCUMENTS

# 2.1. OBJECTIVES

The objective of the review of existing MIL-STD documents was to use the teams' awareness of existing procedures and methods to determine which of the existing military documents require attention for implementation of the new qualification approach for VHSIC/VLSI. The approach encouraged utilization of that which is still relevant; identify areas that needed new methods or procedures; and flag areas not presently covered.

The review of the documents categorized them into one of the following:

- Retain: when the document was relevant to VHSIC/VLSI and needs no modification.

- o Modify: when the document was generally useful but requires modification for VHSIC/VLSI application, or because it required more clarity in the definition of the procedures, or for improved readability and/or user-friendliness.

- New: when the objectives of the document remained valid but new methods are needed for VHSIC/VLSI applicability.

- Not applicable: when the scope of the document was not pertinent to VHSIC/VLSI.

In addition to determining the usefulness of existing documentation, the team sought to identify gaps. Today's qualification approach is heavily dependent on testing of finished product, whereas the new approach seeks to qualify the processes that yield the finished product. It was, therefore, necessary to identify areas not covered by today's methods which will need to be covered under the new approach. For example, the process by which ICs are designed is minimally covered under existing procedures, but it will be critical under the new approach to identify a method for assuring that design rules are adhered to, and that CAD tools are adequate. Some new approaches to qualification were considered by the team at the beginning of Task 1, such as "Parametric Monitors" (PMs) for checking the electrical performance parameters of a process and "Standard Evaluation Circuits" (SECs) which can be used in place of the actual circuits for many of the require reliability tests.

# 2.2. APPROACH

The approach taken by the Task 1 team to best meet the objectives was:

- Establish a basis for the review criteria to give commonality in evaluation procedures.

- Assign document review responsibility on basis of expertise and available resources.

- Coordinate document reviews with weekly and monthly status reviews on progress.

- Summarize results and collate into four basic categories. (Not Applicable-N/A, Modify-Mod, Modify to include surrogate-Mod\*, and Retain-Ret)

- Include plans for ICWG involvement in document review through ICWG structuring and recruiting.

A common review sheet was prepared and distributed. The review sheet contained three main sections providing:

o A description of what was being evaluated.

- o What reliability information was gained.

- o Will modification be required for VHSIC?

With each document assigned for review, subtest methods and/or subparagraphs were partitioned and reviewed by assigned personnel.

To monitor progress and allow for continual interaction of all functions, weekly and monthly status reviews were held. This ensured that individual document reviewers were cognizant of concerns and accomplishments of the entire Task 1 team.

The review sheets were then summarized and collated to provide categorization for Task 2 follow-up review by the ICWG.

# 2.3. RESULTS

# 2.3.1. MIL-M-38510F: General Specification for Microcircuits

### 2.3.1.1. Discussion of MIL-M-38510F

The review of this document identified areas that were not compatible and/or adequate to VHSIC/VLSI technology. These are detailed below:

Paragraph 3.5 - Design and Construction: This section provides guidelines to be implemented in design. The major comment for this section is that it does not address CAD issues. Certification and monitoring of CAD is key to the new approach.

Paragraph 4.4.2 - Qualification (per MIL-STD-883C, Method 5005); and Paragraph 4.5 - Quality Conformance inspection (per MIL-STD-883C, Method 5005): this document requires that Method 5005 be used on real product, which implies high cost for low volume product such as VHSIC. In its present form, no provision is made for the use of PMs and SECs. The new approach will emphasize the use of PMs and SECs as a way to certify and monitor the processes that yield the final product.

Paragraph 4.6 - Screening (per MIL-STD-883C, Method 5004): the document requires testing of 100% of product per all the applicable tests in Method 5004. Some of the screening procedures are not effective for VHSIC/VLSI application. One example is the Method 2010, Internal Visual, which has very limited application to devices with very small design features. Appendix A - Product Assurance Program: this appendix addresses documentation, certification, qualification and other aspects of the product realization flow, from design to outgoing inventory. Many of the issues cited from the main body of the MIL-M-38510 document, apply here as well. For example, Paragraph 20.1.1.6 - Design, Processing, Manufacturing, Equipment, and Materials Instructions, does not address CAD, PMs, or SECs.

# 2.3.1.2. Major Findings in MIL-M-38510F

The major findings of this review of MIL-M-38510F are:

- Modification of the document is required for VHSIC/VLSI application.

- o CAD is not addressed.

- Some of the screening procedures are not suitable for VHSIC/VLSI (e.g., High Power Visual Inspection).

- Qualification and Quality Control Inspection procedures need to be modified for VHSIC/VLSI application because: the procedures are product, not process, oriented; no use is made of PMs or SECs; and sampling plans assume high volume production.

- o The document is complex, which makes it hard to follow, and prone to misinterpretation.

# 2.3.2. <u>MIL-STD-883C</u>

# 2.3.2.1. Discussion of Series 1000 and 2000 Methods

The Tables 1 and 2 below list the results of the review. The column labeled "VHSIC QRA Disposition" reflects the reviewer's current thinking on the applicability of the method to the new VHSIC QRA approach. The "Comments" column captures the underlying reasons for the disposition. The column labeled "Additional Comments for Task 2" provides recommendations and/or raises flags for the team to address during the Task 2 activity. The footnote reference to "surrogate devices" alludes to tests being performed on Process Monitors (PMs) or Standard Evaluation Circuits (SEC) rather than the primary product.

# 2.3.2.2. Major Findings in 1000 and 2000 Series

- o Most of the test methods in the 1000 and 2000 series remain applicable, either "as is" or with modification. Some test methods may need to be developed to properly address the QML approach. In some cases, it is envisioned that the QML approach may call for tests to be performed in a step of the product realization chain replacing tests that are now performed elsewhere downstream in the manufacturing cycle.

- o Many Test Methods may require updating for:

- Use with PMs and SECs;

- Application to VHSIC/VLSI technology requirements;

- Clarification of test criteria, purpose, assumptions, and technical references, where possible.

| SERIES   |

|----------|

| M 1000   |

| 883C: TM |

| -570-    |

| OF MIL   |

| ANALYSIS |

| Ι.       |

| TABLE    |

| Method<br>No. | Environmental Tests                                        | VHSIC QRA<br>Disposition | A<br>on Comments                            | Additional<br>Comments of Task 2                      |

|---------------|------------------------------------------------------------|--------------------------|---------------------------------------------|-------------------------------------------------------|

| 1001<br>1002  | Barometric Pressure<br>Immersion                           | NA                       |                                             |                                                       |

| 1003          | Insulation Resistance<br>Moisture Resistance               | Mod*                     | Insufficient Voltage Range<br>Needs flarity | Assembly: Address during package design.              |

| 1005          | Steady State Life                                          | *pow                     | Needs Clarity                               | Address in SQC/QRA**: relate to device                |

| 1006          | Intermittent Life                                          | *boM                     | Similar to 1005; Needs Clarity              | Address in SQC/QRA**:relate to device                 |

| 1007          | Agree Life                                                 | *boM                     | Similar to 1005; Needs Clarity              | Address in SQC/QRA**:relate to device                 |

| 1008<br>1009  | Stabilization Bake<br>Salt Atmosphere                      | Ret<br>Mod               | Review Procedures                           | Address in SQC/QRA**:relate to device                 |

| 1010          | (Corrosion)<br>Temperature Cycling                         | Ret                      |                                             | application<br>-                                      |

| 1011          | Thermal Shock                                              | *boM                     | Larger Packages                             | ,                                                     |

| 1012          | Dew Point                                                  | Ret*                     | raiger cutps/rackages                       | Address in Assembly: new techniques?                  |

| 1014          | Seal                                                       | Ret                      |                                             | •                                                     |

| 1015          | Burn-In Test                                               | *boM                     | Dynamic Burn-In Difficult                   | SQC/QRA**: Address infant mortality                   |

| 0101          | Characterization                                           | - DOM                    | rev:ew test conditions/<br>Procedures       | •                                                     |

| 1017          | Neutron Irradiation                                        | *boM                     | Simulation Correlation                      | Address in Design/Electrical Test                     |

| 1018          | Internal Water Vanor Content                               | Mod*                     | Questionable<br>Poor Reproducibility        | Address in Assembly                                   |

|               | Antennal nater tapol content                               | New*                     | Consider New Techniques                     |                                                       |

| 1019          | Steady State Total Dose                                    | *boM                     | Simulation Correlation                      | Address in Design/El Tests, Relate                    |

| 1020          | Elrradiation<br>Radiation Induced Latch Un                 | Mod*                     | questionable<br>Simulation Correlation      | to appincation.<br>Address in Design/El Tests. Relate |

|               | -                                                          | 2                        | Questionable                                | to application.                                       |

| 1021          | Dose Rate Threshold for                                    | N/A                      |                                             | ,                                                     |

| 1022          | opset of vigital microcircuits<br>MOSFET Threshold Voltage | N/A                      |                                             |                                                       |

| 1023          | Dose Rate Response of                                      | *pow                     | Simulation Correlation                      | Address in Design/El Tests, Relate                    |

| 000           | Linear Microcircuits                                       | 4                        | Questionable                                | to application.                                       |

| 1030          | Preseal burn-in<br>Thin Film corrosion Test                | Ket<br>N/A               |                                             | FOF Marginal devices/conditions.                      |

| 1032          | Soft Error Test Procedure                                  | Ret                      |                                             | Design/Electrical Test and SQC/QRA*:<br>new methods?  |

| *             | Consider Surrogate Devices                                 |                          | <pre>** ICWG Subcommittee (see 3.2.6)</pre> |                                                       |

i

Assembly and SQC/QRA: relate to Find more Find more Assembly: design eval./relate to application. consider for design Comments of Task 2 Assembly Fab: mostly for metal; new techniques? Add i t i onal Assembly: address VHSIC applicability Assembly: consider for design evaluation. sqc/qRA: quantitative tests. Assembly and SQC/QRA: quantitative tests. Assembly and application. evaluation. Assembly: Review Stress Tests, Limited Consider Larger Packages, Consider Larger Packages, **Consider Larger Packages** Consider Larger Packages **Consider Larger Packages Consider Larger Packages Consider Larger Packages** Limited Application/ Limited Application. **Review Stress Tests** Review Stress Tests Comments Ambiguous Criteria Ambiguous Criteria Application Disposition VHSIC QRA Ret Mod\* \*boM \*boM \*boM Ret\* Ret\* \*pow \*boM \*boM Ret\* Mod\* Mod\* Ret\* N/A Ret PoM PoM Ret New Variable Frequency Vibration Glassivation Layer Integrity Meniscograph Solderability Internal Visual (Monolithic) Bond Strength (Destructive Bond Pull Test) Substrate Attach Strength Non-Destructive Bond Pull Adhesion of Lead Finish Resistance to Solvents Physical Dimensions Environmental Tests Constant Acceleration Vibration Fatigue Random Vibration Mechanical Shock Vibration Noise **External Visual** Solderability Lead Integrity SEM Inspection Radiography Die Shear Method <u>8</u>0. 2003 2004 2005 2005 2006 2009 2010 2012 2015 2016 2018 2019 2023 2025 2026 2026 2002 2021 2022 2001 2011

TABLE 2. ANALYSIS OF MIL-STD-883C: IM 2000 SERIES

÷

Consider Surrogate Devices

\*

# 2.3.2.3. Discussion of 3000 Series

# o General

The 3000 series electrical test methods of MIL-STD-883C were reviewed next. Table 3 shows the VHSIC QRA disposition. It has been recommended that most of the test methods be retained (RET) and that some of the tests could be done possibly on a surrogate device (\*). Other dispositions and the reviewers thoughts are discussed below. Several new test methods were proposed and drafts prepared as a result of this review. These drafts are included in Appendix B.

#### o TM3005

For complex CMOS circuits, to do DC power supply current measurements, that is checking the leakage currents, adds little value. A better measure of the chip's power consumption is the measurement of dynamic current conditions. This gives the user a better idea of total power consumption to be used for board and power supply design.

# o TM3011

The output short circuit test is used to monitor the ability of the TTL output drivers to sustain a momentary short during transients such as power up. This could be a destructive test and may make little sense when complex CMOS circuits are used. If this test is deemed useful, then modifications should be made to clarify exactly how the test is to be performed and a safe time limit set for this test for CMOS technology.

o TM3013

The noise margin test as stated in MIL-STD-883 makes little sense for highly complex chip designs. It should be stated here that noise margin considerations are important; however, the current method of testing the chips is hard, error prone, and may make no sense for VHSIC parts. When one specifies the voltage levels for the input and output pins, the noise margins are implied, especially

| qRA<br>ition Comments        | Add Dynamic Supply Current Test<br>Meeds Clarity<br>Needs Clarity<br>Update for Complex Functions<br>Voltage Level/Machine Controversy                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Electrical Tests Disposition | Drive Source Dynamic<br>Load Conditions<br>Ret<br>Delay Measurements<br>Transition Time Measurement<br>Power Supply Current<br>Power Supply Current<br>Power Supply Current<br>Ret*<br>Nod<br>Evel Output Voltage<br>Net*<br>Input Current, High Level<br>Not<br>for Digital Microelectronics<br>Dutput Short Circuit<br>Ret*<br>Noise Margin Measurements<br>for Digital Microelectronics<br>Devices<br>Functional Testing<br>Functional Testing<br>Sonsitivity Classification<br>Mod<br>Activation Time Verification<br>Nod | Surrogate Devices |

| Method Electr                | <ul> <li>3001 Drive Source Dynamic 2002 Load Conditions</li> <li>3003 Delay Measurements</li> <li>3004 High Level Output Vol 3005 High Level Output Vol 3006 High Level Output Vol 3009 Input Current, High 3011 Output Short Circuit</li> <li>3013 Moise Margin Measuree</li> <li>3014 Functional Testing</li> <li>3014 ESD Sensitivity Clas</li> <li>3016 Activation Time Veri</li> </ul>                                                                                                                                   | * Consider Sur    |

TABLE 3. ANALYSIS OF MIL-STD-883C: TM 3000 SERIES

if TTL compatibility is required. That takes care of the DC noise margin. If one is interested in the AC noise margin, which is really the sensitivity to narrow pulse widths, then a simple surrogate could be used or simulation could be used. Testing the AC noise margin even with a simple circuit at pulse widths of subnanoseconds does not lend itself to Automated Test Equipment (ATE) and is very error prone.

# o TM3015

In the ESD testing area for SSI and MSI devices, there has been constant controversy as to the accuracy of various tests and test equipment, whether the test is destructive, and what the voltage level classifications mean. We agree that electro-static sensitive circuits should be protected, but that seems to be the only agreement. In general, for VHSIC/VLSI, the devices are more susceptible to ESD damage than the larger geometry devices currently in inventory. While I/O protection circuits reduce ESD susceptibility, their use results in diminished performance (at VHSIC clock frequencies). Therefore, the ESD protection/performance tradeoff must be evaluated.

# o TM3016

This test method needs to be updated to address today's technology where activation items are shorter.

# 2.3.2.4. Major Findings in 3000 Series

o General

The test methods, in general, accurately describe those tests necessary to measure DC parameters and to perform AC type measurements. The automated test equipment (ATE) in today's technology is capable of performing most of the tests described automatically and without the need of modification. Since many of these tests are not time consuming on ATE, there may be little value in considering alternative approaches, such as surrogates. There are others, however, such as transition time measurements which can be very time consuming. Alternative techniques should be considered for these tests.

General comments are summarized below:

- Test Methods, 3000 Series address for SSI issues and rely on manual testing

- Updates are needed to include test methods for the following:

- . Set Up and Hold Times

- . Tri-State Related Measurements

- . Bidirectional Pin Measurements

- . Min and Max Frequency Measurements

- . Clamp Voltage Test

# o TM3005

The power supply current measurement method should include techniques to measure dynamic current especially of CMOS devices.

o TM3011

The output short circuit test should be eliminated from those tests which are required in the VHSIC procurement specification.

o TM3013

The noise margin situation is a very important issue, however, modern techniques when applied to this problem can reduce or eliminate this test. The use of careful procurement specification for the DC voltage pin parameters can, along with design CAD and DC pin testing, eliminate the DC noise margin test as currently stated in the military documents. The AC noise margin of today's circuits is the sensitivity of the device to subnanosecond pulses, which can be easily simulated rather than tested.

# o TM3015

More discussion between the producer and user communities is needed to better define the type of test, test equipment, and classification.

# o TM3016

The reviewers see limited need for this test method since the acquisition times are shorter for newer technologies.

o New Test Methods Needed

Electrical test methods which need inclusion to the MIL-STD-883 are summarized here (see Appendix B for draft versions of these test methods).

- Set Up and Hold Time

Set up and hold time tests for circuits that have flip-flops at the input edge of the chip need to be incorporated. This is a critical parameter when interfacing to other circuits and clocks on a printed circuit board. These parameters become very critical especially in high speed parts when their magnitude is only a few nanoseconds.

Tri-State Related and Bidirectional Pin Measurements Many complex chips are designed with tri-state pins either to interface bidirectional buses or because of the need to multiplex pins. Test methods to measure the transitions from high impedance to low impedance and in reverse becomes important in these high speed data systems. Also there may be requirements to hold the high impedance state level to a certain magnitude. This parameter should also be checked.

Clamp Voltage

This test is used by many of the ATEs to check proper probe contact during wafer probe. This test should be done uniformly and standardized.

#### Frequency Measurements, Minimum and Maximum

The maximum frequency of the chip should be known so that the user can be assured that the chip operation is not near the specification limit. The minimum frequency of the chip should be known when one is designing the chip using dynamic logic or any logic that needs periodic refreshing.

# 2.3.2.5. Discussion of 4000 Series

The review of the 4000 series test methods of MIL-STD-883 showed that most tests were intended for single or dual operational amplifier testing which is a serious hindrance when trying to apply these methods to highly complex chips and automated test equipment. Analysis results are shown in Table 4.

Today's technology allows many complex analog functions and even analog and digital functions on the same substrate. New and modified test methods must be found to adequately test these devices. Off-line surrogate testing of simple devices could be used to characterize some of the analog cells used in more complex designs.

# 2.3.2.6. <u>Major Findings in 4000 Series</u>

The reviewer's conclusion is that the methods stated in the current document are fine for what they were intended. However, new methods are needed to test complex analog and analog to digital converters.

Comments are summarized below:

- o Parameters measured are all valid

- o Test Methods 4000 Series address SSI and manual testing

- o Update for ATE and VHSIC level complexity needed

o Update should include:

- A/D and D/A devices

- Incorporation of digital test methods

| SERIES        |

|---------------|

| 4000          |

| TM            |

| MIL-STD-883C: |

| OF            |

| ANALYSIS      |

| TABLE 4.      |

ſ

| VHSIC QRA<br>Disposition Comments | Consider ATE, and Analog and<br>Digital on Same Chips<br>Consider ATE, and Analog and<br>Digital on Same Chips<br>Consider ATE, and Analog and<br>Digital on Same Chips                                   | Consider ATE, and Analog and<br>Digital on Same Chips<br>Consider ATE, and Analog and | Consider ATE, and Analog and<br>Consider ATE, and Analog and<br>Digital on Same Chips<br>Consider ATE, and Analor and |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|

|                                   | *boM<br>*boM                                                                                                                                                                                              | *boM                                                                                  | *boM                                                                                                                  |  |

| Electrical Tests                  | Input Offset Voltage and<br>Current and Bias Current<br>Phase Margin and Slew Rate<br>Measurements<br>Common Mode Input Voltage<br>Range<br>Common Mode Rejection Ratio<br>Supply Voltage Rejection Ratio | Open Loop Performance<br>Output Performance                                           | Power Gain and Noise Figure<br>Automatic Gain Control Range                                                           |  |

| Method<br>No.                     | 4001<br>4002<br>4003                                                                                                                                                                                      | 4004 4005                                                                             | 4006<br>4007                                                                                                          |  |

Consider Surrogate Devices

\*

.

# 2.3.2.7. <u>Discussion of 5000 Series</u>

The 5000 series of test methods serve several functions. For the most part, these are procedures (or Road Maps) rather than methods (Cook Books). More simply put, the 5000 series provides a listing of the tests and screens to be performed in chronological order.

Methods 5001 and 5002 are mathematical formulae for determining parameter mean value and distribution. These are well established and therefore should be useful for VHSIC/VLSI devices.

o TM5003

Method 5003 provides the flow for microcircuit failure analysis. The procedure described is sound and reasonable for VHSIC/VLSI. Some valuable techniques have been developed since the last revision and should be considered for inclusion (eg., IR Scan, AUGER). It should be noted that many of the faults that have been easily detectable through optical examination will be detectable at best using SEM for VHSIC/VLSI. The problem is then one of isolating the functional/electrical fault to a minimum of chip real estate. It is therefore recommended that fault isolation circuitry, perhaps built-in test (BIT), be considered.

o TM5004

Method 5004 Screening Procedures are well established and proven. It is desirable to retain these screens. In cases where Parametric Monitor (PM) or Standard Evaluation Circuit (SEC) data allows parameters to be guaranteed by design, their use will be recommended in place of actual devices or as a complement to actual device screening. The QML approach is intended to eliminate devices of low quality and reliability in the early phases of design, fabrication, and assembly. This will greatly reduce the fallout during screening.

o TM5005

Method 5005 Quality Conformance and Qualification Procedures serves as the road map for current qualification of microelectronic circuits. A similar document will be necessary to establish qualification procedures for VHSIC/VLSI under the QML. Use of surrogate devices for all destructive testing should be given consideration. This approach is already in place (e.g., use of electrical rejects for bond pull, die shear) but needs to be expanded since VHSIC/VLSI material lots are of significantly low volume and do not lend themselves to samples sizes currently required. In addition, the use of high cost VHSIC/VLSI devices for destructive tests is not cost effective. Therefore, the use of surrogate devices and the development of better prevention techniques and in-line screening is recommended over end-of-line testing.

o TM5006

Method 5006 has the purpose of determining the maximum capabilities and limitations of a device. Modifications should be made to relate these important device characteristics to process and design parameters which can, in turn, be derated. This will ensure that adequate margins of operation are defined to enhance overall reliability.

o TM5007

Along with an emphasis on detecting failure early in fabrication/assembly, a set of requirements should be considered to assess the quality of a wafer lot. Method 5007 currently uses sample testing of potential finished products to determine lot acceptance. The testing is primarily physical (i.e., optical, SEM examination). Method 5007 should be modified to measure primarily parametric monitors (PMs) by means of electrical or other quantitative tests. This requires a comprehensive set of PMs.

o TM5010

Method 5010 has many good elements suitable for a VHSIC/VLSI Quality and Reliability Assurance program since it addresses low volumes which are related to custom devices and VHSIC/VLSI. The low volume/high price issue is the driving force to utilize

surrogate devices in QCI since a much broader quality database can be drawn from QCI of the same design, lot after lot.

# 2.3.2.8. <u>Major Finding in 5000 Series</u>

- Method 5010 has many good features applicable to VHSIC/VLSI screening and QCI.

- Use of surrogate devices is desirable for destructive testing. A summary of the comments for the 5000 Series of test procedures is given below:

- o Destructive testing (5006, 5009) mandates use of SECs.

- o Failure analysis (5003) could be enhanced by incorporation of BIT, and modern analytic tools.

- o For VHSIC devices, screening and qualification procedures could be incorporated in TM 5010.

# 2.3.3. <u>MIL-STD-976A</u>

# 2.3.3.1. Discussion of MIL-STD-976A

MIL-STD-976A, Certification Requirements for Microcircuits, establishes the requirements which must be met by a manufacturer during an audit. It addresses technology up to the LSI level and does not address design issues. The technology of today is characterized by high density, high cost, submicron feature sizes and low process yields.

The following areas need to be addressed in Mil-Std-976:

- o Use of surrogate devices.

- o Address design function.

- o Clarify what constitutes a Major or Minor process change.

- o Need to provide direction to Industry on Foundry concept and how to deal with multi-group QML certification.

- o A "Road Map" or some other method is required to better utilize the interaction between referenced documents.

- o Include state-of-the-art process control techniques in areas of Mask Fabrication and highly sensitive process steps.

# 2.3.3.2. <u>Major Findings in MIL-STD-976A</u>

Stress testing of actual circuits should be reviewed for cost effectiveness and value. Use of surrogate devices and emphasis on process control rather than individual product stress testing should be considered.

Areas that require revamping will be reviewed by the ICWG to provide a document that not only leads to certification but also allows industry to improve their processing capabilities in the areas related to yields and quality. Clarification of a major or minor changes is critical.

# 2.3.4. <u>MIL-STD-1331</u>

# 2.3.4.1. Discussion of MIL-STD-1331

This document describes the parameters required as a minimum for the specification of microcircuits during the 1960s. The purpose was to provide minimum parameters (independent of the circuit design), abbreviations, definitions, and symbols, which are necessary for the evaluation of the circuit design and procurement of the microcircuits.

It refers to the following documents:

Specification Military:

MIL-M-55565 Packaging of Microcirc\_its

Standards Military:

MIL-STD-806 Graphic Symbols for Logic Diagrams MIL-STD-883 Test Methods and Procedures for Microelectronics. MIL-STD-1313 Microelectronic Terms and Definitions.

Although the purpose of this document was to make it independent of the circuit design, the definitions and related terminology did not keep up with the evolution of technology. For example, today's packages with their vast number of pin-outs require different approaches. Also, this document does not define terms, such as gate delays, propagation delay as a function of temperature, or supply voltage as well as the parameters related to modern VHSIC/VLSI and Analog-to-Digital/Digital-to-Analog Converters.

# 2.3.4.2. <u>Major Findings in MIL-STD-1331</u>

This document is useful and needs to be updated, seeking help from sources like IEEE Standards Dictionary, ANSI and NBS Standards. It was a unanimous decision that this document needs a thorough overhaul.

#### 2.4. SUMMARY

The Task 1 team performed a thorough review and analysis of the current military standards and specifications that pertain to the manufacture of microcircuits. Each document was evaluated for its applicability to the generic qualification approach of complex microcircuits and recommendations were made as to whether a document was appropriate as is or needed to be modified, or replaced. In the area of electrical tests the need for several new methods was identified.

# 3. TASK II - INVESTIGATION

# 3.1. INTRODUCTION

The investigation task had two major objectives. The first objective was to obtain the cooperation and participation of the microcircuit industry in identifying the methods to be used for generic qualification of microcircuits. The second objective was to draft a set of specifications defining requirements for obtaining a Qualified Manufacturer's List (QML) listing.

The first objective was met through the establishment of an Industry Coordinating Working Group (ICWG) composed of representatives of the manufacturers and users of microcircuits.

The second objective was met by the contract team of GE, AT&T, and Honeywell through a series of working sessions in cooperation with the RADC program office. This effort produced a detailed draft of QML requirements which was then submitted to the ICWG for review and comment.

# 3.2. INDUSTRY COORDINATING WORKING GROUP (ICWG)

A key aspect of the program was the establishment of a technical group to discuss issues related to controlling quality and reliability through process control. This group was the Industry Coordinating Working Group (ICWG) and consisted of 90 individuals from government, manufacturing, users and academia. The charter of this group was to insure maximum industry technical input, applicability, concurrence and utility of the proposed QRA procedures.

# 3.2.1. ICWG Organization

The ICWG was divided in five subcommittees to help facilitate the discussions. These subcommittees were: Quality Management, Design, Fabrication, Assembly/Packaging, and SQC/QRA.

The first meeting of the ICWG was held in February 1987. At this meeting the entire ICWG met and listened to presentations on the task of developing new qualification procedures for microcircuits. This new procedure had been given a name by that time and was known as Generic Qualification. The application of Generic Qualification became known as the Qualified Manufactures Listing (QML). After the general session the ICWG divided into the five subcommittees and initiated their discussions.

The various subcommittees met throughout 1987 and provided technical solutions to the problems associated in implementing a quality/process oriented qualification system. These inputs included: Standard Evaluation Circuit (SEC), Technology Characterization Vehicle (TCV), Technology Review Board (TRB), SPC, Total Quality Management (TQM) and other significant concepts which were readily adaptable to the QML. Further discussion on the output of the subcommittees follows.

# 3.2.2. Quality Management ICWG Subcommittee

The main objective of this subcommittee was to discuss quality management implementation issues, and feasibility and cost effectiveness of the proposed technical outputs of the other subcommittees. Most members of this subcommittees actively participated in the other subcommittees, thus this group became more of an overseer and coordinator of the other four subcommittees.

# 3.2.3. Design and Test ICWG Subcommittee

# 3.2.3.1. Topics of Discussion

The design subcommittee was organized to address design techniques and CAD tool control related to certification and qualification. The design process, especially those using CAD tools had never been included in the quality audit function. The major obstacle was to develop procedures which document the design process without limiting flexibility. There was a great deal of concern that design creativity might suffer as a result of the implementation of quality controls.

The discussions in the Design and Test ICWG subcommittee meetings included the following topics:

- o Design Rules

- o Electrical Rules

- o Cell Libraries

- o Testability

- o Layout

- o Test Generation

- o Design Transfer Procedures

- o Test procedures

- o VHDL/TISSS

- o Electrical tests

# 3.2.3.2. <u>Major Results</u>

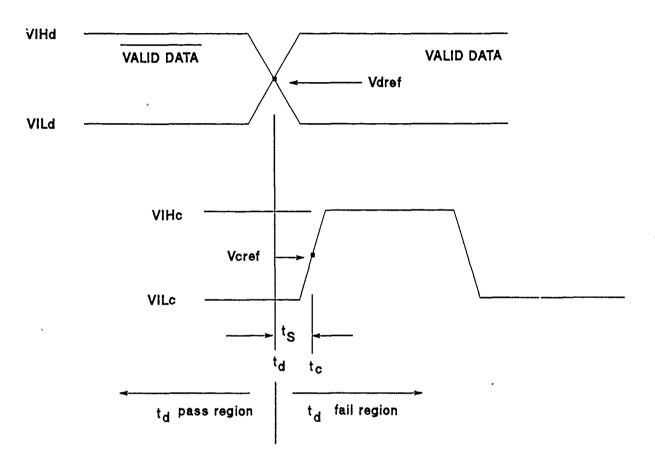

The Design and Test ICWG Subcommittee focused on quality and reliability issues concerning the microcircuit designer and the wafer test facility personnel. This subcommittee met four times with each meeting attended by 20 people representing industry, DoD, and other government agencies. The following items received the most attention at the meetings: