# CMX90G701 6 - 18 GHz Positive Gain-Slope Amplifier +1dB

### Description

The CMX90G701 is a low-power 50  $\Omega$  gain block suitable for a wide variety of wireless applications operating in the 6 – 18 GHz frequency range.

The gain block has a positive gain-slope of +1dB across the 6 – 16 GHz band, eliminating the need for equalisation and compensates for increasing system losses with frequency.

CMX90G701 is highly integrated for ease of use, minimising external component count and board area. RF ports are matched on-chip to 50  $\Omega$  with an output DC-blocking capacitor. An active bias circuit with enable function, allows the device to operate over a wide supply voltage of 2 V to 5 V with typical current of 22 mA.

The device is fabricated using a GaAs pHEMT process to provide a combination of high linearity, low noise and low DC power consumption.

An alternative part, CMX90G702, is available for applications that require more gain-slope compensation.

### **Applications**

- Satcom Ku-band

- Fixed wireless access (FWA)

- 5G infrastructure & backhaul

- X-band (8 12GHz)

- PA Modules

- Eliminate passive equaliser

3x3mm VQFN-16 Package

### **Product Features**

- Wide frequency range 6 18 GHz

- Positive gain-slope +1 dB (6 16 GHz)

- Small signal gain 9.4 10.4 dB

- Single positive DC supply 2 5 V

- Low current consumption (typ 22 mA)

- Low noise figure 3 dB

- Output P1dB +10 dBm @ 12 GHz

- 1.8 V logic compatible enable

- $105^{\circ}C$  operating temperature (Vd  $\leq 3.3$  V)

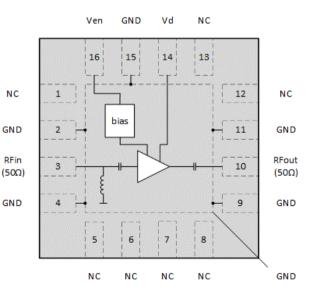

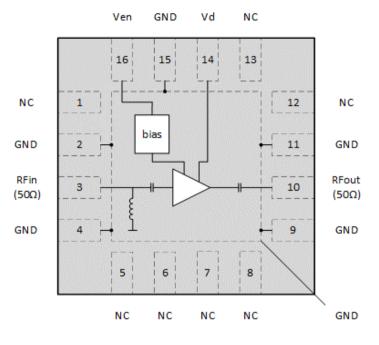

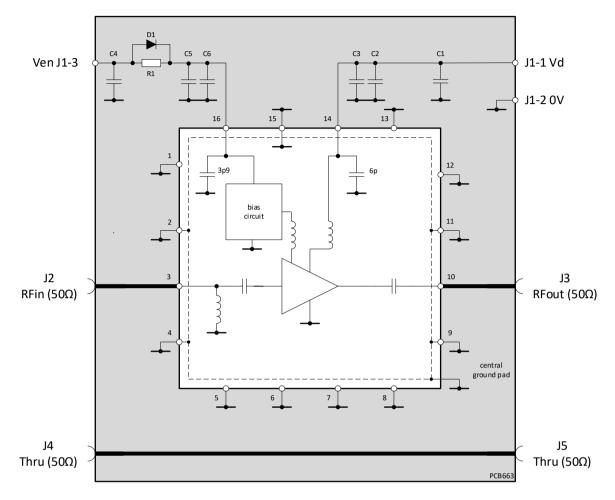

### **Block Diagram**

### **Ordering Information**

| Part Number      | Description               |

|------------------|---------------------------|

| CMX90G701QF-R705 | 7" Reel with 500 pieces   |

| CMX90G701QF-R710 | 7" Reel with 1,000 pieces |

| EV90G701         | Evaluation board          |

### **Absolute Maximum Ratings**

| Parameter                    | Rating                                                     |

|------------------------------|------------------------------------------------------------|

| RF Input Power               | +12dBm                                                     |

| Device Voltage (Vd, Ven)     | +5.5V                                                      |

| Case Temperature (Tc)        | -40 to +85 °C (Vd > 3.3V), -40 to +105 °C (Vd $\leq$ 3.3V) |

| Junction Temperature (Tjmax) | 165 °C (Process MTTF = 10^6 hours)                         |

| Storage Temperature          | -40 to +125 °C                                             |

| ESD Sensitivity              | HBM 250V (Class 1A), CDM 750V (Class C2b)                  |

| MSL Level                    | Level 3                                                    |

Exceeding the maximum ratings may result in damage or reduced device reliability.

## **Thermal Characteristics**

| Parameter                | Rating                                                                          |

|--------------------------|---------------------------------------------------------------------------------|

| Thermal Resistance (Rjc) | 540 °C/W (Tc = 85°C, Vd = Ven = 5 V)<br>550 °C/W (Tc = 105 °C, Vd = Ven = 3.3V) |

Thermal resistance is junction-to-case, where case refers to the exposed die pad on the backside which is in contact with the board.

### **Recommended Operating Conditions**

| Parameter                        | Min | Тур | Max  | Units |

|----------------------------------|-----|-----|------|-------|

| <b>Operating Frequency Range</b> | 6   |     | 18   | GHz   |

| Case Temperature (Tc) Vd > 3.3V  | -40 |     | +85  | °C    |

| Case Temperature (Tc) Vd ≤ 3.3V  | -40 |     | +105 | °C    |

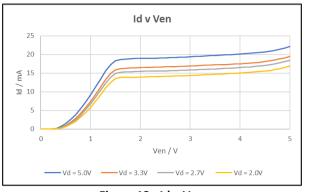

| Device Voltage (Vd)              | 2   |     | 5    | V     |

| Enable Voltage (Ven)             | 0   |     | 5    | V     |

The device will be tested under certain conditions, but performance is not guaranteed over the full range of recommended operating conditions.

### **ESD Caution**

CMX90G701 incorporates ESD protection circuitry however ESD precautions are strongly recommended for handling and assembly. Ensure that devices are protected from ESD in antistatic bags or carriers when being transported. Personal grounding is to be worn at all times when handling these devices.

### **RoHS Compliance**

All devices supplied by CML Microcircuits are compliant with RoHS directive (2011/65/EU), containing less than the permitted levels of hazardous substances

### **Electrical Specification**

Results taken on EV90G701 EVB, where track losses have been de-embedded using the calibration line on the EV90G701 evaluation board.

| Zo = 50 Ω, Vd = +5 V, Ven = +5 V, Ta = +25 | °C (unless otherwise noted) |

|--------------------------------------------|-----------------------------|

|--------------------------------------------|-----------------------------|

| Parameter                            | Conditions                                                        | Min Typ | Max | Units |

|--------------------------------------|-------------------------------------------------------------------|---------|-----|-------|

| Frequency                            |                                                                   | 6       | 18  | GHz   |

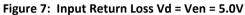

| Small Signal Gain                    | 6 GHz                                                             | 9.4     |     | dB    |

| Small Signal Gain                    | 16 GHz                                                            | 10.4    |     | dB    |

| Small Signal Gain                    | 18 GHz                                                            | 10.2    |     | dB    |

| Gain Slope                           | 6 GHz to 16 GHz                                                   | +1      |     | dB    |

| Reverse Isolation                    | 6 GHz to 18 GHz                                                   | >16     |     | dB    |

| P1dB                                 | At 12 GHz                                                         | 10      |     | dBm   |

| OIP3                                 | Two-tone test $\Delta f$ = 10 MHz, at 12 GHz,<br>Pout/Tone = 0dBm | - 19    | -   | dBm   |

| Noise Figure                         | 12GHz                                                             | 2.6     |     | dB    |

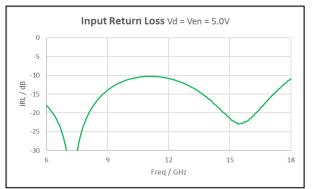

| Input Return Loss                    | 6 GHz to 18 GHz                                                   | >10     |     | dB    |

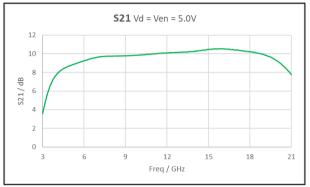

| Output Return Loss                   | 6 GHz to 18 GHz                                                   | >10     |     | dB    |

| Device Current (Id)                  |                                                                   | 22      |     | mA    |

| Ven (Logic 1 = Enabled)              | Amplifier normal operation                                        | 1.8     | 5   | V     |

| Ven (Logic 0 = Standby)              | Amplifier in standby mode                                         | 0       | 0.2 | V     |

| Id                                   | Ven = 0 V                                                         | 1.5     |     | uA    |

| Id                                   | Ven = 0.2 V                                                       | 15      |     | uA    |

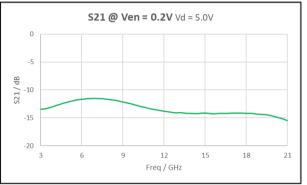

| S21                                  | Ven = 0 to 0.2 V                                                  | -11.8   |     | dB    |

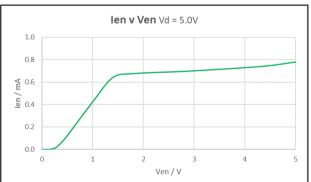

| Ven Current (Ien)                    | Ven = 5 V                                                         | 0.8     |     | mA    |

| Turn-On Time<br>RFout: 10 % to 90 %  | RFin = -10 dBm, 10 GHz                                            | 0.6     |     | μs    |

| Turn-Off Time<br>RFout: 90 % to 10 % | RFin = -10 dBm, 10 GHz                                            | 0.9     |     | μs    |

## **Pin Assignments**

Top View

| Pin     | Name  | Description                                                                                            |  |  |

|---------|-------|--------------------------------------------------------------------------------------------------------|--|--|

| 1       | NC    | Connect to GND                                                                                         |  |  |

| 2       | GND   | Connect to GND                                                                                         |  |  |

| 3       | RFin  | RF input. Internally matched to 50 $\Omega$ with DC path to ground to provide enhanced ESD robustness. |  |  |

| 4       | GND   | Connect to GND                                                                                         |  |  |

| 5       | NC    | Connect to GND                                                                                         |  |  |

| 6       | NC    | Connect to GND                                                                                         |  |  |

| 7       | NC    | Connect to GND                                                                                         |  |  |

| 8       | NC    | Connect to GND                                                                                         |  |  |

| 9       | GND   | Connect to GND                                                                                         |  |  |

| 10      | RFout | RF output. Internally matched to 50 $\Omega$ with integrated DC-blocking capacitor.                    |  |  |

| 11      | GND   | Connect to GND                                                                                         |  |  |

| 12      | NC    | Connect to GND                                                                                         |  |  |

| 13      | NC    | Connect to GND                                                                                         |  |  |

| 14      | Vd    | Voltage supply to amplifier                                                                            |  |  |

| 15      | GND   | Connect to GND                                                                                         |  |  |

| 16      | Ven   | Amplifier enable input                                                                                 |  |  |

| Die pad | GND   | DC and RF ground. Exposed die pad must be connected to GND.                                            |  |  |

#### Notes

CML recommends that all no connect (NC) pins are connected to ground. The bottom exposed die pad must be connected to the ground plane on the board.

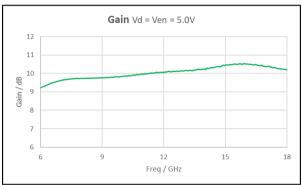

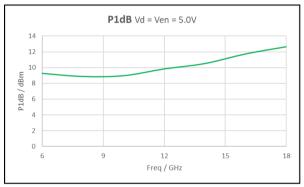

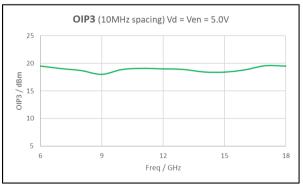

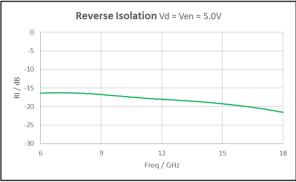

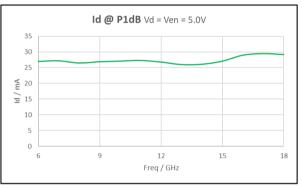

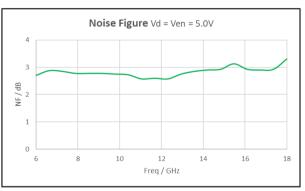

## **Typical Performance**

The following plots show typical performance characteristics of CMX90G701 measured on the evaluation board (Part Number EV90G701). Board losses have been de-embedded from the measurement results using the through line that is included on the EV90G701.

RF typical performance: Vd = Ven = 5.0V, Ta = 25 °C, Z0 = 50  $\Omega$

Figure 1: Gain Vd = Ven = 5.0V

Figure 3: P1dB Vd = Ven = 5.0V

Figure 5: OIP3 (10MHz spacing) Vd = Ven = 5.0V

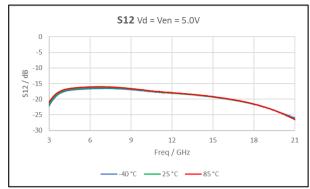

Figure 2: Reverse Isolation Vd = Ven = 5.0V

Figure 4: Id @P1dB Vd = Ven = 5.0V

Figure 6: Noise Figure Vd = Ven = 5.0

#### RF typical performance: Vd = Ven = 5.0V, Ta = 25 °C, Z0 = 50 $\Omega$ (continued)

Figure 9: S21 Vd = Ven = 5.0V

Figure 8: Output Return Loss Vd = Ven = 5.0V

Figure 10: S21 @ Ven = 0.2V Vd = 5.0V

#### DC typical performance: Vd = 5.0 V, Ta = 25 °C

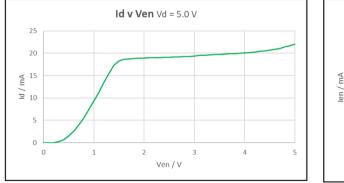

Figure 11: Id v Ven Vd = 5.0V

Figure 12: Ien v Ven Vd = 5.0V

#### DC Performance over voltage: Ta = 25°C

Figure 13: Id v Ven

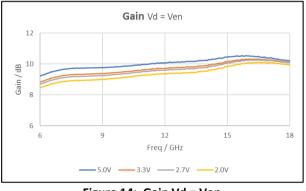

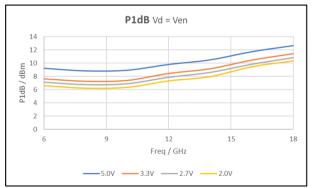

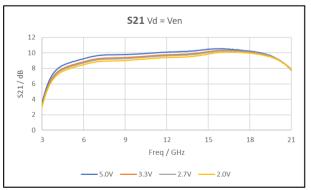

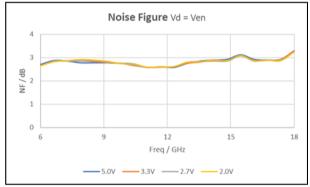

#### RF Performance over voltage: Vd = Ven, Ta = 25°C, Z0 = $50\Omega$

Figure 14: Gain Vd = Ven

Figure 16: P1dB Vd = Ven

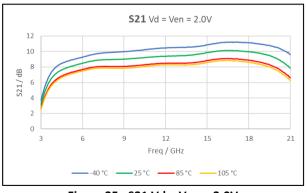

Figure 18: S21 Vd = Ven

Figure 15: Noise Figure Vd = Ven

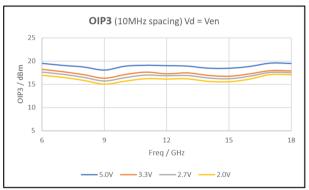

Figure 17: OIP3 (10MHz spacing) Vd = Ven

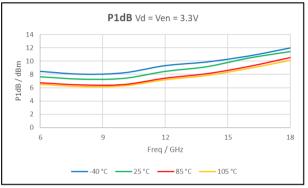

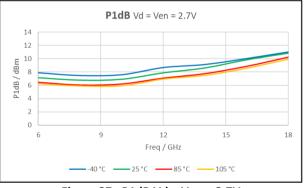

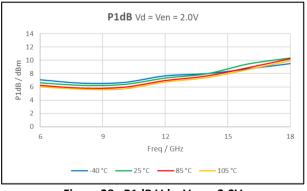

#### RF Performance over temperature: Vd = Ven, Z0 = $50\Omega$

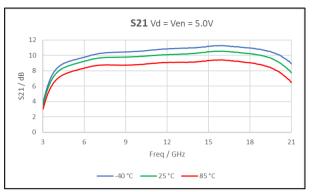

Figure 19: S21 Vd = Ven = 5.0V

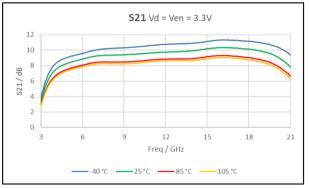

Figure 21: S21 Vd = Ven = 3.3V

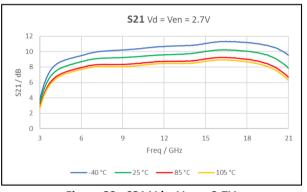

Figure 23: S21 Vd = Ven = 2.7V

Figure 25: S21 Vd = Ven = 2.0V

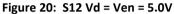

Figure 22: S12 Vd = Ven = 3.3V

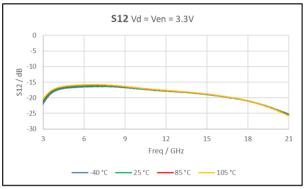

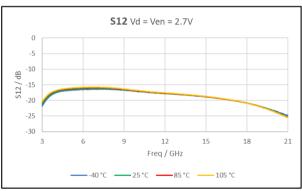

Figure 24: S12 Vd = Ven = 2.7V

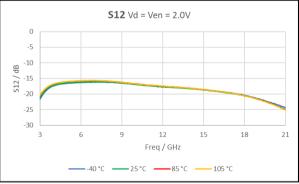

Figure 26: S12 Vd = Ven = 2.0V

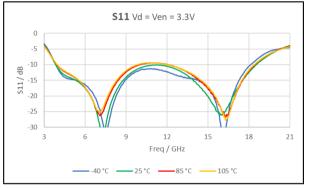

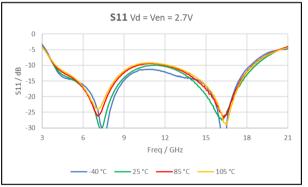

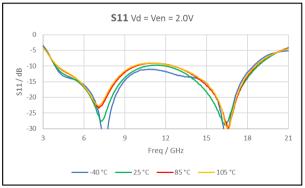

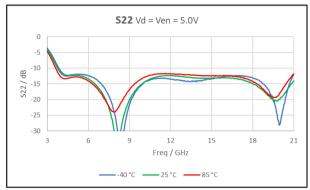

#### RF performance over temperature: Vd = Ven, Z0 = 50 $\Omega$

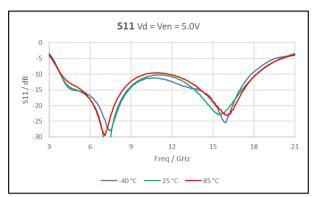

Figure 29: S11 Vd = Ven = 3.3V

Figure 31: S11 Vd = Ven = 2.7V

Figure 33: S11 Vd = Ven = 2.0V

Figure 28: S22 Vd = Ven = 5.0V

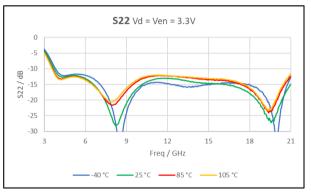

Figure 30: S22 Vd = Ven = 3.3V

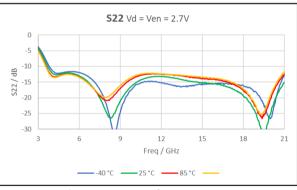

Figure 32: S22 Vd = Ven = 2.7V

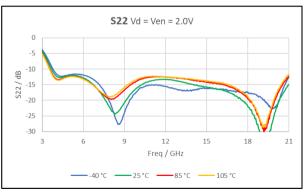

Figure 34: S22 Vd = Ven = 2.0V

#### RF performance over temperature: Vd = Ven, Z0 = 50 $\Omega$

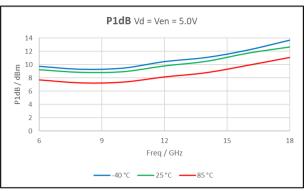

Figure 35: P1dB Vd = Ven = 5.0V

Figure 36: P1dB Vd = Ven = 3.3V

Figure 37: P1dB Vd = Ven = 2.7V

Figure 38: P1dB Vd = Ven = 2.0V

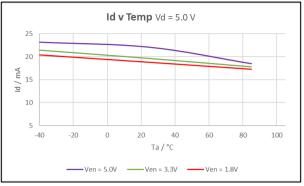

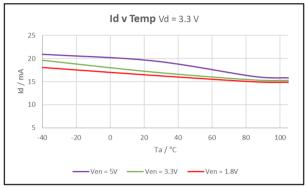

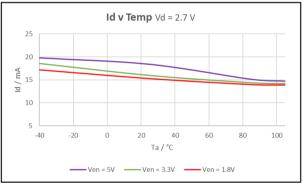

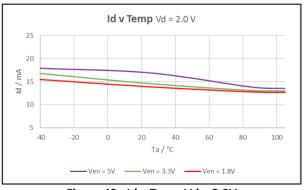

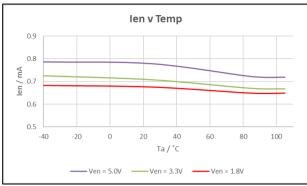

#### DC performance over temperature

Figure 39: Id v Temp Vd = 5.0V

Figure 41: Id v Temp Vd = 3.3V

Figure 42: Id v Temp Vd = 2.7V

Figure 43: Id v Temp Vd = 2.0V

Figure 40: Ien v Temp

### **Application Information**

#### Schematic Diagram

#### Bill Of Materials (BOM)

| Reference<br>Designator | Value | Size     | Description    |

|-------------------------|-------|----------|----------------|

| C1                      | 1 uF  | 0603     | 16 V, +/- 10 % |

| C2                      | 10 nF | 0402     | 16 V, +/- 10%  |

| C3                      | DNF   | 0402     |                |

| C4                      | 10 nF | 0402     | 16 V, +/- 10%  |

| C5                      | 1 nF  | 0402     | 25 V, +/- 5%   |

| C6                      | DNF   | 0402     |                |

| R1                      | 0 R   | 0402     | 0.063 W        |

| D1                      | DNF   | SOD-523F |                |

#### Notes

• DNF = Do not fit component

#### PCB Layout

Careful layout of the printed circuit board (PCB) is essential for optimum RF and thermal performance. The recommended layout, including ground via pattern underneath the device, may be taken from the evaluation board (Part Number EV90G701).

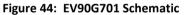

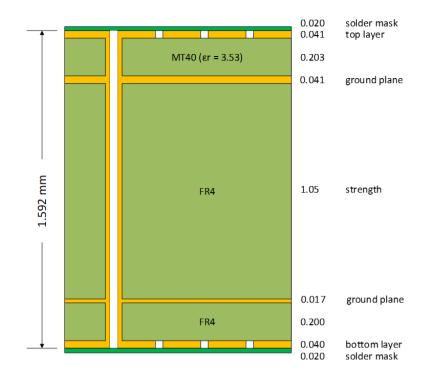

The PCB consists of a top layer of MT40 backed by 2 layers of FR-4 with a total thickness of 1.632 mm (Figure 45) and the EV90G701 PCB (Figure 46) is 20 mm x 45 mm. The coplanar RF transmission lines have a width of 0.33 mm with a gap of 0.14 mm to ground either side. The through line length has been reduced by 3mm to account for the length of the device.

Figure 46: EV90G701 PCB Top Layer View

#### **Thermal Design**

The primary RF/DC ground and thermal path is via the exposed die pad on the backside of the package, which must be connected to the PCB ground plane. An array of plated through-hole vias directly underneath the die pad area is essential to conduct heat away and minimise ground inductance. A typical solution will have 9 grounding vias connecting the top layer to the bottom layer, with inner diameter of 0.2 mm (and 0.025 mm plating) on a 0.55 mm grid pattern. The vias do not need to be filled. The PCB layout should provide a thermal radiator appropriate for the intended operation, adding as much copper to inner and outer layers as possible to avoid excessive junction temperature.

Device junction temperature (Tj) can be calculated using Tj = Tc + (Pdiss x Rjc) where Pdiss = Pdc + Pin – Pout and Tc is the case temperature on the backside of the package (die pad) in contact with the PCB.

#### Ven Input

The device is enabled by applying a voltage between 1.8 V and 5.0 V to pin 16 (Ven). The resulting Id taken by the device is relatively independent of the Ven voltage applied. If the enable feature is not required, the Ven pin can be connected to the same voltage as Vd.

The device can be placed into standby mode when not in use by setting Ven low (<0.2V) to disable all circuitry.

If lower len and Id leakage current and/or if the highest forward isolation is needed in standby mode, a diode can be used in series with the Ven pin to increase the switch-on threshold of the device. This can be particularly important at elevated temperatures. Some suggested diodes in suitable packages (SOD-523F) for the evaluation board are:

- 1N914BWT-D PN fast switching diode

- BAT43XV2-D Schottky diode

#### **Evaluation Board & Bias Procedure**

In general, sequencing of the Vd and Ven supplies is not necessary however applying Vd before or simultaneously with Ven is recommended.

The separate through line can be used to measure the evaluation board and connector losses. These results can then be used to de-embed the device performance from evaluation board measurements.

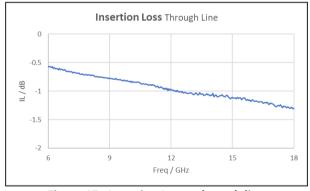

Figure 47: Insertion Loss – through line

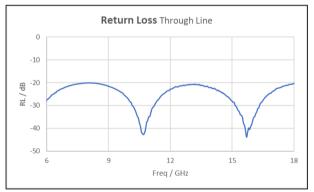

Figure 48: Return Loss – through line

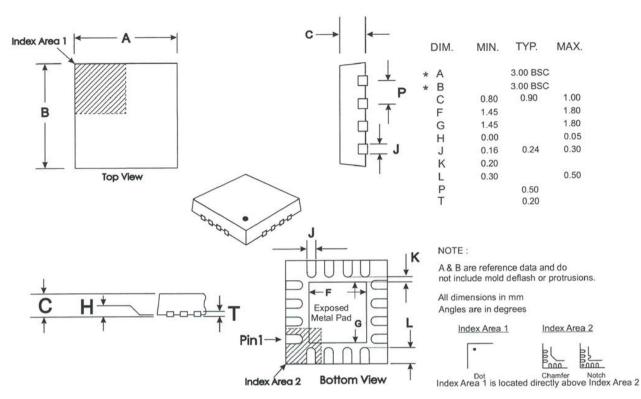

### Package Outline

16-lead 3x3mm VQFN Package (QF)

### **Package Marking**

Pin 1 indicator (dot) and 3 rows of text for device identification.

Line 1: CMX90 SµRF series Line 2: 4-character part code Line 3: Batch code

# **Revision History**

| Issue | Description                      | Date          |

|-------|----------------------------------|---------------|

|       |                                  |               |

| 1     | First release for product launch | November 2022 |

### **Contact Information**

For additional information please visit <u>www.cmlmicro.com</u> or contact a sales office.

| Europe                    | America                                   | Asia                                             |

|---------------------------|-------------------------------------------|--------------------------------------------------|

| • Maldon, UK              | Winston-Salem, NC                         | Singapore                                        |

| • Tel +44 (0) 1621 875500 | • Tel +1 336 744 5050                     | • Tel +65 6288129                                |

| <u>sales@cmlmicro.com</u> | <ul> <li>us.sales@cmlmicro.com</li> </ul> | <ul> <li><u>sg.sales@cmlmicro.com</u></li> </ul> |

Although the information contained in this document is believed to be accurate, no responsibility is assumed by CML for its use. The product and product information is subject to change at any time without notice. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with product specification.

© 2022 CML Microsystems Plc