# Cours sur le Microprocesseur

# **Le Processeur:**

Le **processeur**, (ou **CPU**, Central Processing Unit, « Unité centrale de traitement » en\_français) est le composant essentiel d'un <u>ordinateur</u> qui interprète les instructions et traite les données d'un <u>programme</u>.

La vitesse de traitement d'un processeur est encore parfois exprimée en MIPS (million d'instructions par seconde) ou en Mégaflops (millions de floating-point operations per second) pour la partie virgule flottante, dite FPU (Floating Point Unit). Pourtant, aujourd'hui, les processeurs sont basés sur différentes architectures et techniques de parallélisation des traitements qui ne permettent plus de déterminer simplement leurs performances. Des programmes spécifiques d'évaluation des performances (benchmarks) ont été mis au point pour obtenir des comparatifs des temps d'exécution de programmes réels.

C'est le processeur qui apporte aux ordinateurs leur capacité fondamentale à être programmés, c'est un des composants nécessaires au fonctionnement de tous les types d'ordinateurs, associés aux mémoires primaires et aux dispositifs d'entrée/sortie. Un processeur construit en un seul circuit intégré est communément nommé microprocesseur, à l'inverse, certains fabricants ont développé des processeurs en tranches, dans ce cas les fonctions élémentaires (ALU, FPU, séquenceur, etc.) sont réparties dans plusieurs circuits intégrés spécialisés.

L'invention du <u>transistor</u> en 1947 a ouvert la voie de la miniaturisation des composants électroniques et le terme d'unité centrale (CPU) est utilisé dans l'industrie électronique dès le début de<u>s années</u> 1960 (Weik 1961). Depuis le milieu des <u>années 1970</u>, la complexité et la puissance des microprocesseurs n'a cessé d'augmenter au-delà de tous les autres types de processeurs au point qu'aujourd'hui les termes de processeur, microprocesseur ou CPU, s'utilisent de manière indifférenciée pour tous les types de processeurs.

Les processeurs des débuts étaient conçus spécifiquement pour un ordinateur d'un type donné. Cette méthode coûteuse de conception des processeurs pour une application spécifique a conduit au

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

développement de la production de masse de processeurs qui conviennent pour un ou plusieurs usages. Cette tendance à la standardisation qui débuta dans le domaine des ordinateurs centraux (mainframes à transistors discrets et mini-ordinateurs) a connu une accélération rapide avec l'avènement des circuits intégrés. Les circuits intégrés ont permis la miniaturisation des processeurs dont les dimensions sont réduites à l'ordre de grandeur du millimètre. La miniaturisation et la standardisation des processeurs ont conduit à leur diffusion dans la vie moderne bien au-delà des usages des machines programmables dédiées. On trouve les microprocesseurs modernes partout, de l'automobile aux téléphones portables, en passant par les jouets pour enfants.

### Histoire

口

EDVAC. L'un des premiers ordinateurs à programme enregistré.

Avant l'arrivée des machines qui ressemblent aux unités centrales de traitement d'aujourd'hui, les ordinateurs tels que l'<u>FNIAC</u> devaient être physiquement recâblés avant d'exécuter chaque programme, c'est pour cette raison qu'on les a appelés « ordinateurs à un programme ». Puisque le terme « unité centrale de traitement » est généralement défini comme dispositif d'exécution de logiciel (programme machine), les premiers dispositifs que l'on pourrait appeler processeur sont arrivés avec les ordinateurs à programme enregistré.

L'idée d'un ordinateur à programme enregistré était déjà présente pendant la conception d'ENIAC, mais avait été volontairement écartée pour que la machine soit terminée plus tôt. Le 30 juin 1945, avant qu'ENIAC ait été achevé, le mathématicien John von Neumann a diffusé le document intitulé « première ébauche d'un rapport sur l'EDVAC. » Il a décrit la conception d'un ordinateur à programme enregistré qui sera par la suite complété en août 1949. EDVAC a été conçu pour exécuter un certain nombre d'instructions (ou opérations) de divers types. Ces instructions pouvaient être

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

combinées pour créer des programmes utiles au fonctionnement de l'EDVAC. De manière significative, les programmes écrits pour EDVAC ont été stockés dans de la mémoire d'ordinateur à grande vitesse plutôt que définis par le câblage physique de l'ordinateur. Ceci a surmonté une limitation importante d'ENIAC, qui était la grande quantité de temps et d'effort nécessaires pour modifier l'ordinateur en vue d'exécuter un nouveau programme. Avec la conception de von Neumann, le programme, ou le logiciel, qu'EDVAC exécutait pouvait être changé par simple modification du contenu de la mémoire d'ordinateur.

Tandis que von Neumann le plus souvent est crédité de la conception de l'ordinateur à programme enregistré en raison de sa conception d'EDVAC, d'autres avant lui tel que Konrad Zuse avaient suggéré des idées semblables. De plus, l'architecture de Harvard (Harvard Mark I), qui a été réalisée avant EDVAC, a également utilisé une conception à programme enregistré en utilisant le<u>ruban perforé</u> plutôt que la mémoire électronique. La différence principale entre les architectures von Neumann et Harvard est que la dernière sépare le stockage et le traitement des instructions et des données d'unité centrale de traitement, tandis que l'autre utilise le même espace mémoire pour les deux. La plupart des unités centrales de traitement modernes sont principalement von Neumann dans la conception, mais des éléments de l'architecture de Harvard y sont généralement ajoutés.

Comme tous les dispositifs numériques, les processeurs traitent des états discrets et requièrent donc des éléments de commutation pour différencier et changer ces états. Avant l'acceptation commerciale du transistor, les relais électromécaniques et les tubes électroniques étaient utilisés généralement comme éléments de commutation. Bien que ceux-ci présentent des avantages certains de vitesse sur les précédents, de conception purement mécanique, ils étaient peu fiables pour différentes raisons. Par exemple, réaliser des circuits de logique séquentielle à courant continu avec des relais impose du matériel additionnel pour régler le problème du rebond de contact. Tandis que les tubes à vide ne souffrent pas du rebond de contact, ils doivent être préchauffés avant de devenir complètement opérationnels et par la suite peuvent cesser de fonctionner brutalement. Régulièrement, quand un tube tombe en panne il faut procéder à un diagnostic de l'unité centrale de traitement en localisant et en remplaçant l'élément défaillant. Par conséquent, les ordinateurs électroniques plus récents (utilisant des tubes à vide) étaient généralement plus rapides mais moins fiables que les anciens (utilisant des relais) ordinateurs électromécaniques. Les ordinateurs à tubes comme EDVAC fonctionnaient en moyenne huit heures entre les pannes, tandis que les ordinateurs à relais (plus lents mais arrivés plus tôt) d'architecture Harvard ne tombaient en panne que très rarement (Weik 1961:238). En fin de compte, les unités centrales de traitement à tubes ont supplanté les autres parce que leurs avantages significatifs de vitesse ont été prépondérants par rapport aux problèmes de fiabilité. La plupart de ces premières unités centrales de traitement synchrones ont fonctionné à de basses fréquences de base comparées aux conceptions microélectroniques modernes. Les <u>fréquences</u> de signal d'horloge s'étendant de 100 kilohertz à 4 mégahertz étaient très communes

Tél: (00229) 96 15 81 18 E-mail: cyze2002@yahoo.fr / cyze2002@hotmail.com

à l'époque, limitées en grande partie par la vitesse des dispositifs de commutation qu'elles utilisaient.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

# Processeurs à transistors discrets ou à circuits intégrés modifier

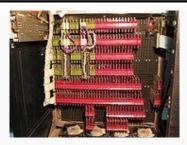

口

Processeur, Mémoire centrale, etbus d'interface d'un MSI PDP-8/I.

La complexité de conception des unités centrales de traitement s'est accrue lorsque diverses technologies ont facilité la construction de dispositifs électroniques plus petits et plus fiables. La première de ces améliorations est apparue avec l'avènement du transistor. Les processeurs transistorisés des années 1950 et des années 1960 n'ont plus besoin de faire appel à des éléments de commutation encombrants, peu fiables et fragiles comme les tubes à vide et les relais électromécaniques. Avec cette amélioration, des unités centrales de traitement plus complexes et plus fiables ont été construites sur une ou plusieurs cartes de circuit imprimé contenant des composants discrets (individuels). Au cours de cette période, une nouvelle méthode de fabrication a vu le jour, permettant de grouper un grand nombre de transistors sur une surface réduite de matériau semi-conducteur, lecircuit intégré (IC) était né.

Au tout début, des circuits numériques non spécialisés, tels que les portes NOR, ont été miniaturisés dans des circuits intégrés. Les unités centrales de traitement basées sur ces modules élémentaires sont généralement appelés dispositifs à faible intégration (SSI, pour Small Scale Integration). Les circuits intégrés SSI, comme ceux utilisés dans l'ordinateur de guidage de la station spatiale Apollo, ne comptent généralement qu'une dizaine de transistors. Construire une unité centrale de traitement entièrement en circuits SSI nécessite des milliers de circuits intégrés individuels, mais consomme toujours beaucoup moins d'espace et de puissance que les montages à transistors discrets précédents. Pendant que la technologie microélectronique avançait, un nombre croissant de transistors ont été intégrés dans les circuits, de ce fait diminuant le nombre de circuits individuels nécessaires pour une unité centrale de traitement complète.

L'échelle d'intégration définit le nombre de portes par boîtier :

- SSI (small scale integration) petite : inférieur à 12 ;

- MSI (medium scale integration) moyenne : 12 à 99 ;

- LSI (large scale integration) grande : 100 à 9 999 ;

- VLSI (very large scale integration) très grande : 10 000 à 99 999 ;

- ULSI (ultra large scale integration) ultra grande : 100 000 et plus.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Ces distinctions ont peu à peu perdu de leur utilité avec la croissance exponentielle du nombre de portes logique. Aujourd'hui plusieurs centaines de millions de transistors (plusieurs dizaines de millions de portes logique) représentent un chiffre normal (pour un microprocesseur ou un circuit intégré graphique haut de gamme).

En 1964 IBM a présenté son architecture d'ordinateur System/360, qui a été employée dans une série d'ordinateurs qui pouvaient exécuter les mêmes programmes à différentes vitesses et performances. C'était significatif à un moment où la plupart des ordinateurs étaient incompatibles entre eux, même ceux construits par le même fabricant. Pour développer cette avancée, IBM mis au point le concept de microprogramme (souvent appelé « microcode »), dont l'utilisation est encore fréquente dans des unités centrales de traitement modernes. L'architecture System/360 était si populaire qu'elle a dominé le marché des ordinateurs centraux pendant plusieurs décennies laissant un héritage encore utilisé par des ordinateurs modernes comme les zSeries d'IBM. Au cours de la même année (1964) Digital Equipment Corporation (DEC) a présenté un autre ordinateur déterminant destiné au marché des ordinateurs scientifiques et de recherche, le PDP-8. DEC lancera plus tard la famille très populaire des PDP-11 qui fut à l'origine basée sur des circuits intégrés SSI puis finalement dotée de circuits LSI dès que ceux-ci furent disponibles. Contrastant avec ses prédécesseurs SSI et MSI, la première implémentation en LSI du PDP-11 comportait une unité centrale de traitement à seulement quatre circuits intégrés.

Les ordinateurs à transistors avaient plusieurs avantages certains par rapport à leurs prédécesseurs. Hormis la meilleure fiabilité et la moindre consommation d'énergie, les transistors ont permis aux processeurs de fonctionner à des vitesses beaucoup plus élevées car les temps de commutation des transistors sont beaucoup plus courts que ceux des tubes et des relais. Grâce à ces deux avancées, la fréquence d'horloge des processeurs s'est accrue considérablement pour atteindre plusieurs gigahertz. Alors que les processeurs à transistors et à circuits intégrés étaient d'usage courant, de nouveaux concepts d'architecture à haute performance comme les processeurs vectoriels et le SIMD (Simple Instruction Multiple Data - données multiples instruction simple) commencèrent à apparaître et ouvrirent la voie au développement des processeurs spécialisés comme ceux qui furent réalisés par la société Cray Research.

# Microprocesseurs

Article détaillé : microprocesseur.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

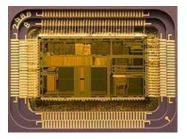

口

Intel 80486DX2 microprocesseuren boîtier céramique PGA

L'introduction du microprocesseur dans les années 1970 a marqué de manière significative la conception et l'implémentation des unités centrales de traitement. Depuis l'introduction du premier microprocesseur (Intel 4004) en 1970 et du premier microprocesseur employé couramment (Intel 8080) en 1974, cette classe de processeurs a presque totalement dépassé toutes les autres méthodes d'implémentation d'unité centrale de traitement. Les fabricants d'ordinateurs centraux (mainframe et miniordinateurs) de l'époque ont lancé leurs propres programmes de développement de circuits intégrés pour mettre à niveau les architectures anciennes de leurs ordinateurs et ont par la suite produit des microprocesseurs à jeu d'instructions compatible en assurant la compatibilité ascendante avec leurs anciens modèles. Les générations précédentes des unités centrales de traitement comportaient un assemblage de composants discrets et de nombreux circuits faiblement intégrés sur une ou plusieurs cartes électroniques. Les microprocesseurs sont construits avec un très petit nombre de circuits très fortement intégrés (ULSI), habituellement un seul. Les microprocesseurs sont implémentés sur une seule <u>puce électronique</u>, donc de dimensions réduites, ce qui veut dire des temps de commutation plus courts liés à des facteurs physiques comme par exemple la diminution de la capacité parasite des portes. Ceci a permis aux microprocesseurs synchrones d'augmenter leur fréquence de base de quelques dizaines de mégahertz à plusieurs gigahertz. De plus, à mesure que la capacité de fabriquer des transistors extrêmement petits sur un circuit intégré a augmenté, la complexité et le nombre de transistors dans un seul processeur a considérablement augmenté. Cette tendance largement observée est décrite par la loi de Moore, qui s'est avérée être jusqu'ici un facteur prédictif assez précis de la croissance de la complexité des processeurs (et de tout autre circuit intégré).

Les <u>processeurs multi cur</u> (multicores) récents comportent maintenant plusieurs curs dans un seul circuit intégré, leur efficacité dépend grandement de la topologie d'interconnexion entre les curs. De nouvelles approches comme la superposition de la mémoire et du cur de processeur (memory stacking) sont à l'étude et devraient conduire à un nouvel accroissement des performances. En se basant sur les tendances des 10 dernières années, les performances des processeurs devraient atteindre le <u>Pétaflop</u>, vers 2010 pour les serveurs, et à l'horizon 2030 dans les PC.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Début juin 2008 le <u>supercalculateur</u> militaire IBM Roadrunner est le premier à franchir cette barre symbolique du <u>Pétaflop</u>. Puis en <u>novembre 2008</u> c'est au tour du supercalculateur Jaguar de <u>Cray</u>. En avril 2009 ce sont les deux seuls supercalculateurs à avoir dépassé le Petaflop.

Tandis que la complexité, la taille, la construction, et la forme générale des processeurs ont fortement évolué au cours des soixante dernières années, la conception et la fonction de base n'ont pas beaucoup changé. Presque tous les processeurs communs d'aujourd'hui peuvent être décrits très précisément comme machines à programme enregistré de von Neumann. Alors que la loi de Moore, mentionnée ci-dessus, continue à être vérifiée, des questions ont surgi au sujet des limites de la technologie des circuits intégrés à transistors. La miniaturisation des portes électroniques est si importante que les effets de phénomènes comme l'électromigration (dégradation progressive des interconnexions métalliques entraînant une diminution de la fiabilité des circuits intégrés) et les courants de fuite (leur importance augmente avec la réduction des dimensions des circuits intégrés, ils sont à l'origine d'une consommation d'énergie électrique pénalisante), auparavant négligeables, deviennent de plus en plus significatifs. Ces nouveaux problèmes sont parmi les nombreux facteurs conduisant les chercheurs à étudier d'une part, de nouvelles technologies de traitement telles que l'ordinateur quantique l'usage du calcul parallèle, et d'autre part, d'autres méthodes d'utilisation du modèle classique de von Neumann.

### **Fonctionnement**

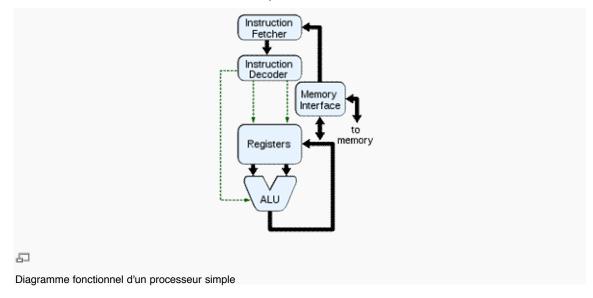

## Composition d'un processeur

Les parties essentielles d'un processeur sont :

- Unité Arithmétique et Logique (UAL, en anglais Arithmetic and Logical Unit ALU), qui prend en charge les calculs arithmétiques élémentaires et les tests ;

- l'<u>unité de contrôle</u> ou séquenceur, qui permet de synchroniser les différents éléments du processeur. En particulier, il initialise les registres lors du démarrage de la machine et il gère les interruptions;

- les registres, qui sont des <u>mémoires</u> de petite taille (quelques<u>octets</u>), suffisamment rapides pour que l'UAL puisse manipuler leur contenu à chaque cycle de lhorloge. Un certain nombre de registres sont communs à la plupart des processeurs :

- <u>Compteur ordinal</u>: ce registre contient ladresse <u>mémoire</u> de linstruction en cours d exécution;

- accumulateur : ce registre est utilisé pour stocker les données en cours de traitement par I UAL;

- registre d adresses : il contient toujours l'adresse de la prochaine information à lire par I UAL, soit la suite de l'instruction en cours, soit la prochaine instruction ;

- registre d instructions : il contient linstruction en cours de traitement ;

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

- registre d état : il sert à stocker le contexte du processeur, ce qui veut dire que les différents <u>bits</u> de ce registre sont des <u>drapeaux</u> (flags) servant à stocker des informations concernant le résultat de la dernière instruction exécutée ;

- pointeurs de pile : ce type de registre, dont le nombre varie en fonction du type de processeur, contient l'adresse du sommet de la <u>pile</u> (ou des piles) ;

- registres généraux : ces registres sont disponibles pour les calculs ;

- I horloge qui synchronise toutes les actions de lunité centrale. Elle est présente dans les <u>processeurs synchrones</u>, et absente des <u>processeurs asynchrones</u> et des <u>processeurs</u> autosynchrones;

- l'unité d entrée-sortie, qui prend en charge la communication avec la mémoire de l ordinateur ou la transmission des ordres destinés à piloter ses processeurs spécialisés, permettant au processeur d'accéder aux périphériques de lordinateur.

Les processeurs actuels intègrent également des éléments plus complexes :

- plusieurs UAL, ce qui permet de traiter plusieurs instructions en même temps. L'architecture superscalaire, en particulier, permet de disposer des UAL en parallèle, chaque UAL pouvant exécuter une instruction indépendamment de l'autre;

- l'architecture <u>superpipeline</u> permet de découper temporellement les traitements à effectuer.

C est une technique qui vient du monde des <u>supercalculateurs</u>;

- une unité de prédiction de saut, qui permet au processeur danticiper un saut dans le déroulement d un programme, permettant déviter d attendre la valeur définitive d'adresse du saut.

Cela permet de mieux remplir le <u>pipeline</u>;

- une <u>unité de calcul en virgule flottante</u> (en anglais Floating Point Unit FPU), qui permet d'accélérer les calculs sur des <u>nombres réels</u> codés en virgule flottante ;

- la <u>mémoire cache</u>, qui permet d'accélérer les traitements, en diminuant les temps d'accès à la <u>mémoire</u>. Ces mémoires tampons sont en effet beaucoup plus rapides que la RAM et ralentissent moins le CPU. Le cache instructions reçoit les prochaines instructions à exécuter, le cache données manipule les données. Parfois, un seul cache unifié est utilisé pour le code et les données. Plusieurs niveaux de caches peuvent coexister, on les désigne souvent sous les noms de L1, L2 ou L3. Dans les processeurs évolués, des unités spéciales du processeur sont dévolues à la recherche, par des moyens statistiques et/ou prédictifs, des prochains accès en mémoire centrale.

Un processeur est défini par :

- la largeur de ses registres internes de manipulation de données (8, 16, 32, 64, 128) bits;

- la cadence de son horloge exprimée en MHz (mega hertz) ou GHz (giga hertz);

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

- le nombre de noyaux de calcul (core) ;

- son <u>jeu d'instructions</u> (ISA en anglais, Instructions Set Architecture) dépendant de la famille (CISC, RISC, etc);

- sa finesse de gravure exprimée en <u>nm</u> (nanomètres) et sa <u>microarchitecture</u>.

Mais ce qui caractérise principalement un processeur est la famille à laquelle, il appartient :

- <u>CISC</u> (Complex Instruction Set Computer : choix d'instructions aussi proches que possible d'un langage de haut niveau);

- RISC (Reduced Instruction Set Computer : choix d'instructions plus simples et d'une structure permettant une exécution très rapide);

- <u>VLIW</u> (Very Long Instruction Word);

- DSP (Digital Signal Processor). Même si cette dernière famille (DSP) est relativement spécifique. En effet un processeur est un composant programmable et est donc a priori capable de réaliser tout type de programme. Toutefois, dans un souci d'optimisation, des processeurs spécialisés sont conçus et adaptés à certains types de calculs (3D, son, etc.). Les DSP sont des processeurs spécialisés pour les calculs liés au traitement de signaux. Par exemple, il n'est pas rare de voir implémenter des <u>Transformées de Fourier</u> dans un DSP.

Un processeur possède trois types de bus :

- un bus de données, définit la taille des données manipulables (indépendamment de la taille des registres internes);

- un bus d'adresse définit le nombre de cases mémoire accessibles ;

- un **bus de contrôle** définit la gestion du processeur IRQ, RESET etc.

#### Les opérations du processeur

Le rôle fondamental de la plupart des unités centrales de traitement, indépendamment de la forme physique qu'elles prennent, est d'exécuter une série d'instructions stockées appelées <u>"programme"</u>.

Les instructions (parfois décomposées en micro instructions) et les données transmises au processeur sont exprimées en mots <u>binaires</u> (<u>code machine</u>). Elles sont généralement stockées dans la <u>mémoire</u>. Le séquenceur ordonne la lecture du contenu de la mémoire et la constitution des mots présentées à l'<u>ALU</u> qui les interprète.

L ensemble des instructions et des données constitue un programme.

Le langage le plus proche du code machine tout en restant lisible par des humains est le langage d'assemblage, aussi appelé langage assembleur (forme francisée du mot anglais « assembler »). Toutefois, l'informatique a développé toute une série de langages, dits de haut niveau (comme le <u>BASIC, Pascal, C, C++, Fortran, Ada,</u> etc), destinés à simplifier lécriture des programmes.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Les opérations décrites ici sont conformes à l'architecture de von Neumann. Le programme est représenté par une série d'instructions qui réalisent des opérations en liaison avec la mémoire vive de l'ordinateur. Il y a quatre étapes que presque toutes les architectures von Neumann utilisent :

- FETCH (Recherche de l'instruction);

- **DECODE** (Décodage de l'instruction : opérations et opérandes) ;

- EXECUTE (Exécution des opérations);

- WRITEBACK (Ecriture du résultat).

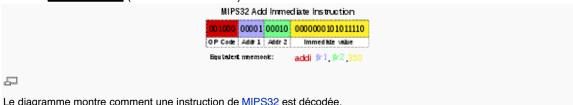

Le diagramme montre comment une instruction de MIPS32 est décodée.

La première étape, FETCH (recherche), consiste à rechercher une instruction dans la mémoire vive de l'ordinateur. L'emplacement dans la mémoire est déterminé par le compteur de programme (PC), qui stocke l'adresse de la prochaine instruction dans la mémoire de programme. Après qu'une instruction a été recherchée, le PC est incrémenté par la longueur du mot d'instruction. Dans le cas de mot de longueur constante simple, c'est toujours le même nombre. Par exemple, un mot de 32 bits de longueur constante qui emploie des mots de 8 bits de mémoire incrémenterait toujours le PC par 4 (excepté dans le cas des sauts). Le jeu d'instructions qui emploie des instructions de longueurs variables comme l'x86, incrémentent le PC par le nombre de mots de mémoire correspondant à la dernière longueur d'instruction. En outre, dans des unités centrales de traitement plus complexes, l'incrémentation du PC ne se produit pas nécessairement à la fin de l'exécution d'instruction. C'est particulièrement le cas dans des architectures fortement parallélisées et superscalaires. Souvent, la recherche de l'instruction doit être opérée dans des mémoires lentes, ralentissant l'unité centrale de traitement qui attend l'instruction. Cette question est en grande partie résolue dans les processeurs modernes par l'utilisation de <u>caches</u> et d'architectures <u>pipelines</u>.

L'instruction que le processeur recherche en mémoire est utilisée pour déterminer ce que le CPU doit faire. Dans l'étape DECODE (décodage), l'instruction est découpée en plusieurs parties telles qu'elles puissent être utilisées par d'autres parties du processeur. La façon dont la valeur de l'instruction est interprétée est définie par le jeu d'instructions (ISA) du processeur<sup>2</sup>. Souvent, une partie d'une instruction, appelée opcode (code d'opération), indique quelle opération est à faire, par exemple une addition. Les parties restantes de l'instruction comportent habituellement les autres informations nécessaires à l'exécution de l'instruction comme par exemples les opérandes de l'addition. Ces opérandes peuvent prendre une valeur constante, appelée valeur immédiate, ou bien contenir l'emplacement où retrouver (dans un registre ou une adresse mémoire) la valeur de l'opérande, suivant le mode d'adressage utilisé. Dans les conceptions anciennes, les parties du processeur

E-mail: cvze2002@yahoo.fr / cvze2002@hotmail.com Tél: (00229) 96 15 81 18

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

responsables du décodage étaient fixes et non modifiables car elles étaient codées dans les circuits. Dans les processeurs plus récents, un <u>microprogramme</u> est souvent utilisé pour traduire les instructions en différents ordres. Ce microprogramme est parfois modifiable pour changer la façon dont le CPU décode les instructions, même après sa fabrication.

Après les étapes de recherche et de décodage arrive l'étape **EXECUTE** (exécution) de l'instruction. Au cours de cette étape, différentes parties du processeur sont mises en relation pour réaliser l'opération souhaitée. Par exemple, pour une addition, l'unité arithmétique et logique (ALU) sera connectée à des entrées et des sorties. Les entrées présentent les nombres à additionner et les sorties contiennent la somme finale. L'ALU contient la circuiterie pour réaliser des opérations d'arithmétique et de logique simples sur les entrées (addition, opération sur les bits). Si le résultat d'une addition est trop grand pour être codé par le processeur, un signal de débordement est positionné dans un registre d'état (voir ci-dessous le chapitre sur le codage des nombres).

La dernière étape **WRITEBACK** (écriture du résultat), écrit tout simplement les résultats de l'étape d'exécution en mémoire. Très souvent, les résultats sont écrits dans un registre interne au processeur pour bénéficier de temps d'accès très courts pour les instructions suivantes. Dans d'autres cas, les résultats sont écrits plus lentement dans des mémoires <u>RAM</u>, donc à moindre coût et acceptant des codages de nombres plus grands.

Certains types d'instructions manipulent le compteur de programme plutôt que de produire directement des données de résultat. Ces instructions sont appelées des sauts (jumps) et permettent de réaliser des boucles (loops), des programmes à exécution conditionnelle ou des fonctions (sous-programmes) dans des programmes<sup>a</sup>. Beaucoup d'instructions servent aussi à changer l'état de drapeaux (flags) dans un registre d'état. Ces états peuvent être utilisés pour conditionner le comportement d'un programme, puisqu'ils indiquent souvent la fin d'exécution de différentes opérations. Par exemple, une instruction de comparaison entre deux nombres va positionner un

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

drapeau dans un registre d'état suivant le résultat de la comparaison. Ce drapeau peut alors être réutilisé par une instruction de saut pour poursuivre le déroulement du programme.

Après l'exécution de l'instruction et l'écriture des résultats, tout le processus se répète, le prochain cycle d'instruction recherche la séquence d'instruction suivante puisque le compteur de programme avait été incrémenté. Si l'instruction précédente était un saut, c'est l'adresse de destination du saut qui est enregistrée dans le compteur de programme. Dans des processeurs plus complexes, plusieurs instructions peuvent être recherchées, décodées et exécutées simultanément, on parle alors d'architecture <u>pipeline</u>, aujourd'hui communément utilisée dans les équipements électroniques.

# Conception et implémentation

# Le codage des nombres

La manière dont un CPU représente les <u>nombres</u> est un choix de conception qui affecte de façon profonde son fonctionnement de base. Certains des ordinateurs les plus anciens utilisaient un modèle électrique du système numérique <u>décimal</u> (<u>base</u> 10). Certains autres ont fait le choix de systèmes numériques plus exotiques comme les <u>systèmes trinaires</u> (base 3). Les processeurs modernes représentent les nombres dans les <u>systèmes binaire</u> (base 2) dans lequel chacun des <u>chiffres</u> est représenté par une grandeur physique qui ne peut prendre que 2 valeurs comme une <u>tensionélectrique</u> "haute" ou "basse".

Le concept physique de tension électrique est <u>analogique</u> par nature car elle peut prendre une infinité de valeurs. Pour les besoins de représentation physique des nombres binaires, les valeurs des tensions électriques sont définies comme des états 1 et 0. Ces états résultent des paramètres opérationnels des éléments de commutation qui composent le processeur comme les niveaux de seuil des transistors.

Le microprocesseur 6502 en technologie MOS dans un boîtierdual in-line une conception très répandue.

En plus du système de représentation des nombres, il faut s'intéresser à la taille et la précision des nombres qu'un processeur peut manipuler. Dans le cas d'un processeur binaire, un "bit" correspond à une position particulière dans les nombres que le processeur peut gérer. Le nombre de bits (chiffres) qu'un processeur utilise pour représenter un nombre est souvent appelé "taille du mot" (word size, bit width, data path width) ou "précision entière" lorsqu'il s'agit de nombres entières (à l'opposé des nombres flottants). Ce nombre diffère suivant les architectures, et souvent, suivant les différents modules d'un même processeur. Par exemple, un CPU 8-bit gère des nombres qui peuvent être représentés par 8 chiffres binaires (chaque chiffre pouvant prendre 2 valeurs), soit 2 ou 256 valeurs

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

discrètes. En conséquence, la taille du nombre entier défini une limite à la plage des nombres entiers que le <u>logiciel</u> exécuté par le processeur pourra utiliser.

La taille du nombre entier affecte également le nombre d'emplacements mémoire que le processeur peut adresser (localiser). Par exemple, si un processeur binaire utilise 32 bits pour représenter une adresse mémoire et que chaque adresse mémoire est représentée par un octet (8 bits), la taille mémoire maximum qui peut être adressée par ce processeur est de  $2^2$  octets, ou 4 Gio. C'est une vision très simpliste de l'espace d'adressage d'un processeur et beaucoup de conceptions utilisent des types d'adressages bien plus complexes, comme la pagination, pour adresser plus de mémoire que la taille du nombre entier le leur permettrait avec un espace d'adressage à plat.

De plus grandes plages de nombres entiers nécessitent plus de structures élémentaires pour gérer les chiffres additionnels, conduisant à plus de complexité, des dimensions plus importantes, plus de consommation d'énergie et des coûts plus élevés. Il n'est donc pas rare de rencontrer des microcontrôleurs 4-bit ou 8-bit dans des applications modernes, même si des processeurs 16-bit, 32-bit, 64-bit et même 128-bit sont disponibles. Pour bénéficier des avantages à la fois des tailles d'entier courtes et longues, beaucoup de CPU sont conçus avec différentes largeurs d'entiers dans différentes parties du composant. Par exemple, le System/370 d'IBM est doté d'un CPU nativement 32-bit mais qui utilise une unité de calcul flottant (FPU) de 128-bit de précision pour atteindre une plus grande précision dans les calculs avec les nombres flottants. Beaucoup des processeurs les plus récents utilisent une combinaison comparable de taille de nombres, spécialement lorsque le processeur est dédié à un usage généraliste pour lequel il est nécessaire de trouver le juste équilibre entre les capacités à traiter les nombres entiers et les nombres flottants.

#### Le signal d'horloge

La plupart des processeurs, et plus largement la plupart des circuits de logique séquentielle, ont un fonctionnement synchrone par nature. Cela veut dire qu'ils sont conçus et fonctionnent au rythme d'un <u>signal</u> de<u>synchronisation</u>. Ce signal, qu'on appelle généralement **signal d'horloge**, prend souvent la forme d'une <u>onde</u> carrée <u>périodique</u>. En calculant le temps maximum que prend le signal électrique pour se <u>propager</u> dans les différentes branches des circuits du processeur, le concepteur peut sélectionner la <u>période</u> appropriée du signal d'horloge.

Cette période doit être supérieure au temps que prend le signal pour se propager dans le pire des cas. En fixant la période de l'horloge à une valeur bien au-dessus du pire des cas de temps de propagation, il est possible de concevoir entièrement le processeur et la façon dont il déplace les données autour des "fronts" montants ou descendants du signal d'horloge. Ceci a pour avantage de simplifier significativement le processeur tant du point de vue de sa conception que de celui du nombre de ses composants. Par contre, ceci a pour inconvénient le ralentissement du processeur puisque sa vitesse doit s'adapter à celle de son élément le plus lent, même si d'autres parties sont

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

beaucoup plus rapides. Ces limitations sont largement compensées par différentes méthodes d'accroissement du parallélisme des processeurs (Voir ci-dessous).

Les améliorations d'architecture ne peuvent pas, à elles seules, résoudre tous les inconvénients des processeurs globalement synchrones. Par exemple, un signal d'horloge est sujet à des retards comme tous les autres signaux électriques. Les <u>fréquences</u> d'horloge plus élevées que l'on trouve dans les processeurs à la complexité croissante engendrent des difficultés pour conserver le signal d'horloge en <u>phase</u> (synchronisé) à travers toute l'unité centrale de traitement. En conséquence, beaucoup des processeurs d'aujourd'hui nécessitent la fourniture de plusieurs signaux d'horloge identiques de façon à éviter que le retard d'un seul signal ne puisse être la cause d'un dysfonctionnement du processeur. La forte quantité de chaleur qui doit être dissipée par le processeur constitue un autre problème majeur dû à l'accroissement des fréquences d'horloge. Les changements d'état fréquents de l'horloge font commuter un grand nombre de composants, qu'ils soient ou non utilisés à cet instant. En général, les composants qui commutent utilisent plus d'énergie que ceux qui restent dans un état statique. ainsi, plus les fréquences d'horloge augmentent et plus la dissipation de chaleur en fait autant, ce qui fait que les processeurs requièrent des solutions de refroidissement plus efficaces.

La méthode dite de clock gating permet de gérer la commutation involontaire de composants en inhibant le signal d'horloge sur les éléments choisis mais cette pratique est difficile à implémenter et reste réservée aux besoins de circuits à très faible consommation.

Une autre méthode consiste à invalider le signal global d'horloge, la consommation d'énergie et la dissipation thermique sont réduites mais la conception du circuit devient plus complexe. Certaines conceptions ont été réalisés sans signal global d'horloge, comme par exemple les familles de processeurs <u>ARM</u> ou <u>MIPS</u>, d'autres ne présentent que des parties asynchrones comme par exemple l'utilisation d'un ALU asynchrone avec un <u>pipelining superscalaire</u> pour atteindre des gains de performance dans les calculs arithmétiques. Il n'est pas certain qu'un processeur totalement asynchrone puisse délivrer un niveau de performance comparable ou supérieur à un processeur synchrone alors qu'il est évident qu'il sera meilleur dans les opérations mathématiques simples, il sera donc plutôt réservé aux applications embarquées (ordinateurs de poche, consoles de jeux...).

# Le surfréquençage ou surcadençage (overclocking en anglais)

L'overclocking aussi noté o/c est une méthode qui consiste pour l'utilisateur à augmenter la fréquence de l'horloge du processeur (ou, plus généralement, d'un composant) pour bénéficier de plus de performances.

Le fonctionnement des composants à une vitesse supérieure à leur vitesse nominale est possible dans certaines limites non garanties et souvent non documentées par les <u>constructeurs</u>. La mise au point de tels systèmes s'avère donc délicate et nécessite une démarche progressive et empirique, notamment pour la définition des moyens de refroidissement complémentaires.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

# <u>Parallélisme</u>

La description du mode de fonctionnement de base d'un processeur présentée au chapitre précédent présente la forme la plus simple que peut prendre un CPU. Ce type de processeur, appelé subscalaire, exécute une <u>instruction</u> sur un ou deux champs de données à la fois.

Ce processus est inefficace et inhérent aux processeurs subscalaires. Puisqu'une seule instruction n'est exécutée à la fois, tout le processeur attend la fin du traitement de cette instruction avant de s'intéresser à la suivante avec pour conséquence que le processeur reste figé sur les instructions qui nécessitent plus d'un cycle d'horloge pour s'exécuter. L'ajout d'une seconde unité de traitement (voir ci-dessous), ne permet pas d'améliorer notablement les performances, ce n'est plus une unité de traitement qui se trouve figée mais 2, en augmentant encore le nombre de transistors inutilisés. Ce type de conception, dans laquelle les ressources d'exécution du CPU ne traitent qu'une seule instruction à la fois ne peut atteindre que des performances scalaires (une instruction par cycle d'horloge), voire subscalaires (moins d'une instruction par cycle d'horloge).

En tentant d'obtenir des performances scalaires et au-delà, on a abouti à diverses méthodes qui conduisent le CPU a un comportement moins linéaire et plus parallèle. Lorsqu'on parle de <u>parallélisme</u> de processeur, deux termes sont utilisés pour classifier ces techniques de conception :

- Instruction Level Parallelism (ILP) Parallélisme au niveau instruction;

- Thread Level Parallelism (TLP) Parallélisme au niveau thread (groupe d'instructions).

L'ILP cherche à augmenter la vitesse à laquelle les instructions sont exécutées par un CPU (œst-à-dire augmenter l'utilisation des ressources d'exécution présentes dans le circuit intégré). L'objectif du TLP est d'accroître le nombre de <u>threads</u> que le CPU pourra exécuter simultanément. Chaque méthode diffère de l'autre d'une part, par la façon avec laquelle elle est implémentée et d'autre part, du fait de leur efficacité relative à augmenter les performances des processeurs pour une application.

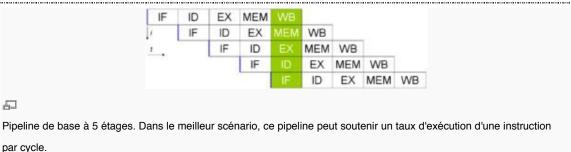

ILP: Pipelining d'instructions et architecture superscalaire

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Une des méthodes les plus simples pour accroître le parallélisme consiste à démarrer les premières étapes de recherche (fetch) et décodage (decode) d'une instruction avant la fin d'exécution de l'instruction précédente. C'est la forme la plus simple de la technique de pipelining, elle est utilisée dans la plupart des processeurs modernes non spécialisés. Le pipelining permet d'exécuter plus d'une instruction à la fois en décomposant le chemin d'exécution en différentes étapes. Ce découpage peut être comparé à une chaîne d'assemblage.

Le pipelining peut créer des conflits de dépendance de données, lorsque le résultat de l'opération précédente est nécessaire à l'exécution de l'opération suivante. Pour résoudre ce problème, un soin particulier doit être apporté pour vérifier ce type de situation et retarder, le cas échéant, une partie du pipeline d'instruction. Naturellement, les compléments de circuits à apporter pour cela ajoutent à la complexité des processeurs parallèles. Un processeur parallèle peut devenir presque scalaire, ralenti uniquement par les attentes du pipeline (une instruction prend moins d'un cycle d'horloge par étape).

昼

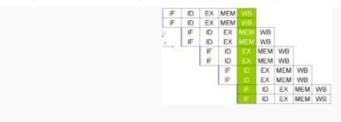

Pipeline superscalaire simple. En recherchant et affectant deux instructions à la fois, le CPU peut exécuter un maximum de deux instructions par cycle.

Les développements suivants du pipelining ont conduit au développement d'une méthode qui diminue encore plus les temps d'attente des composants du processeur. Les conceptions dites superscalaires comportent un pipeline à instruction longue et plusieurs unités d'exécution identiques . Dans un pipeline superscalaire, plusieurs instructions sont lues et transmises à un répartisseur qui décide si les instructions seront exécutées en parallèle (simultanément) ou non. Le cas échéant, les instructions sont réparties sur les unités d'exécution disponibles. En général, plus un processeur superscalaire est capable d'exécuter d'instructions en parallèle et plus le nombre d'instructions exécutées dans un cycle sera élevé.

La plupart des difficultés rencontrées dans la conception des architectures de processeurs superscalaires résident dans la mise au point du répartisseur. Le répartisseur doit être disponible rapidement et être capable de déterminer sans erreur si les instructions peuvent être exécutées en parallèle, il doit alors les distribuer de façon à charger les unités d'exécution autant qu'il est possible. Pour cela, le pipeline d'instructions doit être rempli aussi souvent que possible, créant le besoin d'une quantité importante de mémoire cache. Les techniques de traitement aléatoire comme la prédiction de branchement, l'exécution spéculative et la résolution des dépendances aux données deviennent cruciales pour maintenir un haut niveau de performance. En tentant de prédire quel branchement (ou chemin) une instruction conditionnelle prendra, le processeur peut minimiser le nombre de fois que

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

tout le pipeline doit attendre jusqu'à la fin d'exécution de l'instruction conditionnelle. L'exécution spéculative améliore les performances modestes en exécutant des portions de code qui seront, ou ne seront pas, nécessaires à la suite d'une instruction conditionnelle. La résolution de la dépendance aux données est obtenue en réorganisant l'ordre dans lequel les instructions sont exécutées en optimisant la disponibilité des données.

Lorsque seule une partie de processeur est superscalaire, la partie qui ne l'est pas rencontre des problèmes de performance dus aux temps d'attente d'ordonnancement. Le <u>Pentium</u> original (P5) disposait de 2 ALU superscalaires qui pouvaient chacune accepter une instruction par cycle. Ensuite le P5 est devenu superscalaire pour les calculs sur les nombres entiers mais pas sur les nombres à virgule flottante. Les successeurs des architectures Pentium d'Intel, les P6, ont été dotés de capacités superscalaires pour les calculs sur les nombres à virgule flottante améliorant par là leurs performances en calcul flottant.

Les conceptions de pipelining simple et superscalaires augmentent le parallélisme (ILP) des CPU en permettant à un processeur unique d'exécuter des instructions à un rythme de plus d'une instruction par cycle. La plupart des processeurs d'aujourd'hui ont au moins une partie superscalaires. Au cours des dernières années, certaines évolutions dans la conception des processeurs à fort parallélisme ne se trouvent plus dans les circuits du processeur mais ont été placées dans le logiciel ou dans son interface avec le logiciel (LSA). La stratégie des instructions très longues (very long instruction word) conduit à implémenter certains parallélismes directement dans le logiciel, cela réduit la participation du processeur au gain de performance mais en réduit la complexité.

#### TLP : Exécution simultanée de programmes

Une autre stratégie communément employée pour augmenter le parallélisme des processeurs consiste à introduire la capacité d'exécuter plusieurs programmes (threads) simultanément. De manière générale, les processeurs multi-threads ont été utilisés plus longtemps que les processeurs à architecture pipeline. Bon nombre des conceptions pionnières, réalisées par la société Cray Research, datant de la fin des années 1970 et des années 1980, mettaient en uvre principalement la méthode TLP, dégageant alors de très grandes capacités de calcul (pour l'époque). En fait, le multithreading était connu dès les années 1950 (Réf : Smotherman 2005). Dans le cas des processeurs simples, les 2 méthodologies principales employées pour développer des TLP sont le multiprocessing au niveau des circuits (Chip-level multiprocessing - CMP) et le multithreading simultané (Simultaneous multithreading - SMT). À un plus haut niveau, il est d'usage de réaliser des ordinateurs avec plusieurs processeurs totalement indépendants dans des organisations de type symétrique (symetric multiprocessing - SMP)ou à accès mémoire non uniforme (non uniform memory access - NUMA). Alors que ces techniques diffèrent par les moyens qu'elles mettent en uvre, elles visent toutes le même but : augmenter le nombre de threads qu'un processeur peut exécuter en parallèle.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Les méthodes de parallélisme CMP et SMP sont assez semblables, elles demandent plus d'effort de conception que l'utilisation de 2 ou 3 processeurs totalement indépendants. Dans le cas du CMP, <u>plusieurs c\_urs</u> (core, en anglais) de processeurs sont intégrés dans le même boîtier, parfois même dans le même circuit intégré. Les SMP, eux, utilisent plusieurs boîtiers indépendants. NUMA est comparable au CMP mais met en\_uvre un modèle d'accès mémoire non uniforme (les temps d'accès sont différents suivant que la mémoire est locale ou non locale à un processeur donné). Cette caractéristique est fondamentale dans les ordinateurs à plusieurs processeurs car pour les modèles SMP à mémoire partagée, les temps d'accès à la mémoire sont rapidement dégradés en cas d'accès simultané par plusieurs processeurs. À ce titre, NUMA est considéré comme un modèle plus évolutif en nombre de processeurs.

SMT diffère des autres améliorations de TLP puisqu'il vise à dupliquer aussi peu de portions de CPU que possible. La mise en uvre d'une stratégie de type TLP ressemble à une architecture superscalaire et se trouve souvent utilisée dans les microprocesseurs superscalaires (comme les <u>POWER5</u> d'<u>IBM</u>). Plutôt que de dupliquer un CPU complet, la conception SMT ne duplique que les parties nécessaires pour la recherche (fetch), le décodage, (decode) et la répartition des instructions (dispatch) ainsi que les registres non spécialisés. Ceci permet a un processeur SMT de maintenir ses unités d'exécution occupées plus souvent, en leur fournissant des instructions en provenance de 2 programmes différents. Comme on vient de la voir, le SMT est proche de l'architecture ILP superscalaire mais, plutôt que d'exécuter simultanément plusieurs instructions en provenance de 2 programmes différents, elle permet d'exécuter simultanément plusieurs instructions en provenance du même programme.

# Description

Jusqu au début des années <u>1970</u>, les différents <u>composants électroniques</u> formant un processeur ne pouvaient tenir sur un seul circuit intégré. On devait donc les placer sur plusieurs circuits intégrés. En 1971, la société américaine <u>Intel</u> a réussi, pour la première fois, à placer tous les transistors qui constituent un processeur sur un seul circuit intégré donnant ainsi naissance au microprocesseur.

Cette miniaturisation a permis :

- d'augmenter les vitesses de fonctionnement des processeurs, grâce à la réduction des distances entre les composants entre autres;

- de réduire les coûts, grâce au remplacement plusieurs circuit par un seul entre autres ;

- d'augmenter la fiabilité : en supprimant les connexions entre les composants du processeur, on supprime l'un des principaux vecteurs de panne ;

- de créer des ordinateurs bien plus petits : les micro-ordinateurs ;

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

de réduire la consommation énergétique<sup>3</sup>.

Les principales caractéristiques d'un microprocesseur sont :

- Le <u>ieu d'instructions</u> qu'il peut exécuter. Voici quelques exemples dinstructions que peut exécuter un microprocesseur : additionner deux nombres, comparer deux nombres pour déterminer s'ils sont égaux, comparer deux nombres pour déterminer lequel est le plus grand, multiplier deux nombres,... Un processeur peut exécuter plusieurs dizaines dinstructions différentes.

- La complexité de son architecture. Cette complexité se mesure par le nombre de <u>transistors</u> contenus dans le microprocesseur. Plus le microprocesseur contiendra de transistors, plus il pourra effectuer des opérations complexes, et/ou traiter des chiffres de grande taille.

- Le nombre de <u>bits</u> que le processeur peut traiter ensemble. Les premiers microprocesseurs ne pouvaient traiter plus de 4 bits d'un coup. Ils devaient donc exécuter plusieurs instructions pour additionner des nombres de 32 ou 64 bits. Les microprocesseurs actuels (en 2007) peuvent traiter des nombres sur 64 bits ensemble. Le nombre de <u>bits</u> est en rapport direct avec la capacité à traiter de grands nombres rapidement, ou des nombres d'une grande précision (nombres de décimales significatives),

- La vitesse de l'horloge. Le rôle de l'horloge est de cadencer le rythme du travail du microprocesseur. Plus la vitesse de l'horloge augmente, plus le microprocesseur effectue de calculs en une seconde.

Tout ceci est théorique, dans la pratique, selon l'architecture du processeur, le nombre de cycles d'horloge pour réaliser une opération élémentaire peut varier d'un cycle à plusieurs dizaines par unité d'exécution (typiquement une sur un processeur classique).

Par exemple, un processeur **A** à 400 MHz peut être plus rapide qu'un autre **B** tournant lui à 1 GHz, tout dépend de leurs architectures respectives.

La combinaison des caractéristiques précédentes détermine la puissance du microprocesseur. La puissance d'un microprocesseur sexprime en <u>MIPS</u>. Dans les années 1970, les microprocesseurs effectuaient moins d'un million d'instructions par seconde, les processeurs actuels (en 2007) peuvent effectuer plus de 10 milliards d'instructions par seconde.

#### Histoire

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

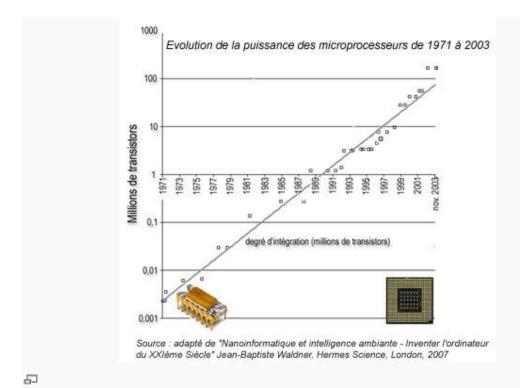

Illustration de la loi dite de « progression géométrique » qui régit l'évolution du nombre de transistors sur les puces de silicium. Source : adapté de "Nanoinformatique et intelligence ambiante - Inventer l'ordinateur du xxIe siècle" Jean-Baptiste Waldner, Hermes Science, London, 2007 (avec la permission de l'auteur).

Le microprocesseur a été inventé par <u>Marcian Hoff (surnommé Ted Hoff)</u> en <u>1971</u>, alors qu'il était <u>ingénieur</u> chez <u>Intel</u>.

En 1990, Gilbert Hyatt a revendiqué la paternité du microprocesseur en se basant sur un brevet qu'il avait déposé en 1970. La reconnaissance de lantériorité du brevet de Hyatt lui aurait permis de réclamer des <u>redevances</u> sur tous les microprocesseurs fabriqués de par le monde. Cependant, le brevet de Hyatt a été invalidé en 1995 par loffice américain des brevets sur la base du fait que le microprocesseur décrit dans la demande de brevet n'avait pas été réalisé et n'aurait d'ailleurs pas pu l'être avec la technologie disponible au moment du dépôt du brevet. Il semble que Gilbert Hyatt n'ait pas abandonné et espère faire revoir cette décision.

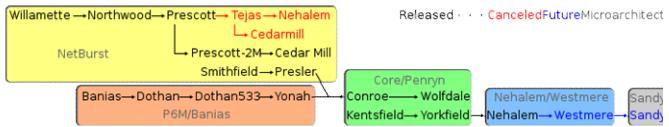

Le premier microprocesseur commercialisé, le <u>15 novembre 1971</u>, est l'<u>Intel 4004</u> 4-bits. Il fut suivi par l'<u>Intel 8008</u>. Ce microprocesseur a servi initialement à fabriquer des contrôleurs graphiques en mode texte, mais jugé trop lent par le client qui en avait demandé la conception, il devint un processeur d'usage général. Ces processeurs sont les précurseurs des <u>Intel 8080</u>, <u>Zilog Z80</u>, et de la future famille des Intel <u>x86</u>.

Le tableau suivant décrit les principales caractéristiques des microprocesseurs fabriqués par Intel et montre la fulgurante évolution des microprocesseurs autant en augmentation du nombre de transistors, en miniaturisation des circuits et en augmentation de puissance.

# VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

| Date | Nom                        | Nombre de<br>transistors | Finesse de<br>gravure<br>(µm) | Fréquence<br>de l'horloge | Largeur<br>des données | MIPS  |

|------|----------------------------|--------------------------|-------------------------------|---------------------------|------------------------|-------|

| 1971 | 4004                       | 2 300                    |                               | 108 kHz                   | 4 bits/4 bits<br>bus   |       |

| 1974 | 8080                       | 6 000                    | 6                             | 2 MHz                     | 8 bits/8 bits<br>bus   | 0,64  |

| 1979 | 8088                       | 29 000                   | 3                             | 5 MHz                     | 16 bits/8 bits<br>bus  | 0,33  |

| 1982 | 80286                      | 134 000                  | 1,5                           | 6 MHz                     | 16 bits/16 bits<br>bus | 1     |

| 1985 | 80386                      | 275 000                  | 1,5                           | 16 à 40 MHz               | 32 bits/32 bits<br>bus | 5     |

| 1989 | 80486                      | 1 200 000                | 1                             | 16 à 100 MHz              | 32 bits/32 bits<br>bus | 20    |

| 1993 | Pentium                    | 3 100 000                | 0,8 à 0.28                    | 60 à 233 MHz              | 32 bits/64 bits<br>bus | 100   |

| 1997 | Pentium II                 | 7 500 000                | 0,35 à 0.25                   | 233 à 450 MHz             | 32 bits/64 bits<br>bus | 300   |

| 1999 | Pentium III « !!! »        | 9 500 000                | 0,25 à 0.13                   | 450 à 1400 MHz            | 32 bits/64 bits<br>bus | 510   |

| 2000 | Pentium 4                  | 42 000 000               | 0,18 à<br>0.065               | 1,3 à 3.8 GHz             | 32 bits/64 bits<br>bus | 1 700 |

| 2004 | Pentium 4D<br>« Prescott » | 125 000 000              | 0,09 à<br>0.065               | 2.66 à 3.6 GHz            | 32 bits/64 bits<br>bus | 9 000 |

Tél: (00229) 96 15 81 18 E-mail: cyze2002@yahoo.fr / cyze2002@hotmail.com

**CYZE PRODUCTION**

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

| 2006 | Core 2 Duo                      | 291 000 000      | 0,065                              | 2,4 GHz (E6600)                                              | 64 bits/64 bits<br>bus | 22 000          |

|------|---------------------------------|------------------|------------------------------------|--------------------------------------------------------------|------------------------|-----------------|

| 2007 | Core 2 Quad                     | 2*291 000<br>000 | 0,065                              | 3 GHz (Q6850)                                                | 64 bits/64 bits<br>bus | 2*22 000<br>(?) |

| 2008 | Core 2 Duo<br>(Penryn)          | 410 000 000      | 0,045                              | 3,33 GHz (E8600)                                             | 64 bits/64 bits<br>bus | ~24 200         |

| 2008 | Core 2 Quad<br>(Penryn)         | 2*410 000<br>000 | 0,045                              | 3,2 GHz (QX9770)                                             | 64 bits/64 bits<br>bus | ~2*24 200       |

| 2008 | Intel Core i7<br>(Nehalem)      | 731 000 000      | 0,045<br>(2008)<br>0,032<br>(2009) | 2,66 GHz (Core i7 920)<br>3,33 GHz (Core i7 Ext.<br>Ed. 975) | 64 bits/64 bits<br>bus | ?               |

| 2009 | Intel Core i5/i7<br>(Lynnfield) | 774 000 000      | 0,045<br>(2009)                    | 2,66 GHz (Core i5 750)<br>2,93 GHz (Core i7 870)             | 64 bits/64 bits<br>bus | ?               |

Date : I année de commercialisation du microprocesseur.

Nom : le nom du microprocesseur.

Nombre de transistors : le nombre de transistors contenus dans le microprocesseur.

**Finesse de gravure (μm)**: le diamètre (en <u>micromètres</u>) du plus petit fil reliant deux composantes du microprocesseur. En comparaison, l'épaisseur d'un cheveu humain est de 100 microns.

**Fréquence de l horloge** : la fréquence de l'horloge de la carte mère qui cadence le microprocesseur. MHz = millions de cycles par seconde. GHz = milliards de cycles par seconde.

Largeur des données : le premier nombre indique le nombre de bits sur lequel une opération est faite. Le second nombre indique le nombre de bits transférés à la fois entre la mémoire et le microprocesseur.

MIPS : le nombre de millions dinstructions complétées par le microprocesseur en une seconde.

Tél: (00229) 96 15 81 18 E-mail: cyze2002@yahoo.fr / cyze2002@hotmail.com

**CYZE PRODUCTION**

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

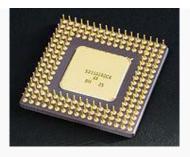

口

Microprocesseur PowerPC 4755.

5

Microprocesseur ARM60.

口

Microprocesseur Intel Core 2 Duo.

# Familles de microprocesseurs

Une famille de microprocesseurs est lensemble des modèles de microprocesseurs qui peuvent exécuter le même <u>jeu d'instructions</u> de base. Ce jeu d'instructions est un minimum commun et souvent les processeurs les plus récents d'une famille présentent de nouvelles instructions qui ne sont pas toujours mises à profit par souci de compatibilité avec les autres processeurs de la famille. Par exemple le code actuel dit x86 est souvent du code pour 80386 qui permet la protection mémoire et qui ne fonctionnerait pas sur des processeurs antérieurs au 80386 (par exemple 8086 et 80286), mais qui fonctionne parfaitement (performances mises à part) sur les processeurs plus récents (par exemple un Core Duo d'Intel ou un Athlon d'AMD).

Il existe plusieurs familles de microprocesseurs :

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

- La famille la plus connue par le grand public est la famille x86, développée principalement par les entreprises Intel (fabricant du Pentium), AMD (fabricant du Athlon), VIA etTransmeta. Les deux premières entreprises dominent maintenant le marché et elles fabriquent la plus grande partie des microprocesseurs pour micro-ordinateurs compatibles PC. Intel fournit également les microprocesseurs pour les micro-ordinateurs Macintosh depuis 2006.

- Les microprocesseurs <u>PowerPC</u> d'IBM et de <u>Motorola</u> équipaient jusqu'en <u>2006</u> les microordinateurs <u>Macintosh</u> (fabriqués par <u>Apple</u>). Ces microprocesseurs sont aussi utilisés dans les

serveurs de la série p d'IBM et dans divers <u>systèmes embarqués</u>. Dans le domaine des <u>consoles</u>

de <u>ieu</u>, des microprocesseurs dérivés du PowerPC équipent la <u>Wii(Broadway)</u>,

la <u>GameCube</u> (<u>Gekko</u>), <u>Xbox 360</u> (dérivé à trois c urs nommé Xenon). La <u>Playstation 3</u> est

équipée du microprocesseur <u>Cell</u>, dérivé du POWER4, une architecture proche de PowerPC.

- Le microprocesseur <u>6502</u> de la compagnie <u>MOS Technology</u> a servi à fabriquer le célèbre <u>Apple II</u>.

- Le microprocesseur <u>Zilog Z80</u> a été largement utilisé dans les années 1980 dans la conception des premiers micro-ordinateurs personnels 8 bits comme le Radio Shack TRS-80, les Sinclair ZX80, ZX81, ZX Spectrum, les <u>Apple II</u> grâce à une carte fille, le standard MSX, les Amstrad CPC et plus tard dans les systèmes embarqués.

- La famille <u>6800</u> de la compagnie <u>Motorola</u>.

- La famille <u>68000</u> de <u>Motorola</u> animait les anciens <u>Macintosh</u>, les <u>Megadrive</u>, les <u>Atari ST</u> et les <u>Commodore Amiga</u>. Leurs dérivés (<u>Dragonball</u>, <u>ColdFire</u>) sont toujours utilisés dans des systèmes embarqués.

Parmi les familles moins connues du grand public :

- La famille <u>Sparc</u> anime la plus grande partie des <u>serveurs</u> et <u>stations de travai</u>l de <u>Sun</u> <u>Microsystems</u>, bien que de plus en plus de nouveaux produits soient réalisés à base de x86.

- La famille <u>PA-RISC</u> de <u>HP</u> et VLSI Technology, anime les anciens serveurs et stations de travail de HP, remplacée aujourd'hui par la famille IA-64

- La famille <u>IA-64</u> de <u>HP</u> et <u>Intel</u>, apporte l'architecture 64 bits aux serveurs et stations de travail de HP

- La famille MIPS anime les stations de travail de <u>Silicon Graphics</u>, des consoles de jeux comme les <u>PSone</u>, les <u>Nintendo 64</u> et des systèmes embarqués, ainsi que

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

des <u>routeursCisco</u>. C'est la première famille à proposer une architecture 64 bits avec le R4000 en 1991. Les processeurs du fondeur chinois <u>Loongson</u>, sont une nouvelle génération basées sur les technologies du MIPS, utilisés dans des supercalculateurs et des ordinateurs faible consommation.

- La famille <u>ARM</u> est de nos jours utilisée uniquement dans les <u>systèmes embarqués</u>, dont de nombreux <u>PDA</u> et <u>Smartphones</u>, elle a précédemment été utilisée par <u>Acorn</u> pour ses <u>Archimedes</u> et <u>RiscPC</u>.

- La famille <u>DEC Alpha</u> animait les ordinateurs <u>DEC</u>, repris par <u>Compaq</u> puis par <u>HP</u> qui l'a définitivement arrêtée.

#### Fonctionnement

Les microprocesseurs sont cadencés par une horloge (signal régulier, imposant un rythme au circuit et, permettant une synchronisation avec d'autres composants, tel que la mémoire). Au milieu des années 1980, les microprocesseurs fonctionnaient de 4 à 8 MHz. Courant 2004, cette vitesse d'horloge atteint 4 GHz pour les modèles commerciaux (5 GHz en laboratoire). Plus la vitesse de l'horloge est élevée, plus le microprocesseur peut exécuter à un rythme élevé les instructions de base des programmes. L'augmentation de la vitesse d'horloge présente des inconvénients : plus elle est élevée, plus le processeur consomme d'électricité, et plus il chauffe; Cela implique d'avoir une solution de refroidissement du processeur adapté. Il faut aussi prendre en compte le fait que plus un transistor commute vite, moins son fonctionnement est stable (sûr).

Les microprocesseurs actuels sont optimisés pour exécuter plus d'une instruction par cycle d'horloge, ce sont des microprocesseurs avec des unités d'exécution parallélisées. De plus ils sont dotés de procédures qui « anticipent » les instructions suivantes avec l'aide de la statistique.

Dans la course à la puissance des microprocesseurs, deux méthodes d'optimisation sont en concurrence :

- La technologie du jeu d'instructions simplifié (<u>RISC</u>, Reduced Instruction Set Computer), rapide avec des instructions simples de taille standardisée, facile à fabriquer et dont on peut monter la vitesse de l'horloge sans trop de difficultés techniques.

- 2. La technologie appelée <u>CISC</u> (Complex Instruction Set Computer), dont chaque instruction complexe nécessite plus de cycles d'horloge, mais qui a en son c ur beaucoup d'instructions pré-câblées.

Néanmoins, avec la considérable diminution de la taille des puces électroniques et la gigantesque accélération des fréquences d'horloge, la distinction entre RISC et CISC a quasi complètement disparu. Là où des familles tranchées existaient, on observe aujourd'hui des microprocesseurs où une

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

structure interne RISC apporte de la puissance tout en restant compatible avec une utilisation de type CISC (la famille Intel x86 a ainsi subi discrètement une transition entre une organisation initialement très typique d'une structure CISC. Actuellement elle utilise un c ur RISC très rapide, s'appuyant sur un système de réarrangement du code à la volée) mis en uvre, en partie, grâce à des mémoires cache de plus en plus étendues, comportant jusqu'à trois niveaux.

# Structure d'un microprocesseur

L'unité centrale d'un microprocesseur comprend essentiellement :

- une <u>unité arithmétique et logique</u> (UAL) qui effectue les opérations ;

- des registres qui permettent au microprocesseur de stocker temporairement des données;

- une unité de contrôle qui commande l'ensemble du microprocesseur en fonction des instructions du programme.

Certains registres ont un rôle très particulier :

- le registre indicateur d'état (flags), ce registre donne l'état du microprocesseur à tout moment,

il peut seulement être lu ;

- le compteur de programme (PC, Program Counter), il contient l'adresse de la prochaine instruction à exécuter;

- le pointeur de pile (SP, Stack Pointer), c'est le pointeur d'une zone spéciale de la mémoire appelée <u>pile</u> où sont rangés les arguments des <u>sous-programmes</u> et les <u>adresses</u> de retour.

Seul le Program Counter est indispensable, il existe de (rares) processeurs ne comportant pas de registre d'état ou pas de pointeur de pile (par exemple le <u>NS32000</u>).

L'unité de contrôle peut aussi se décomposer :

- le registre d'instruction, mémorise le code de l'instruction à exécuter;

- le décodeur décode cette instruction ;

- le séquenceur exécute l'instruction, c'est lui qui commande l'ensemble des organes du microprocesseur.

Article détaillé : Architecture des processeurs.

# Overclocking

### **Principe**

On peut traduire overclocking en français par le terme **surcadençage**. Overclocker un processeur (quel que soit son type : <u>graphique GPU, DSP</u>, processeur principal, etc.) consiste à faire fonctionner ce composant à une vitesse supérieure à la vitesse de fonctionnement normale, vitesse pour laquelle son fabricant garantit un bon fonctionnement. On comprend donc assez rapidement l'intérêt

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

d'overclocker son processeur ou sa carte graphique surtout quand on sait que le gain peut atteindre jusqu'à 10~20% pour la plupart des processeurs. Les Core 2 Duo (et dans une moindre mesure les Core 2 Quad, du fait de leur dissipation thermique élevée) se distinguent du reste des processeurs par leur capacités d'overclocking incroyables : +30% pour l'immense majorité des C2D sans effort, jusqu'à +50% en prenant le temps de régler correctement tous les paramètres, et plus encore en utilisant des systèmes de refroidissement plus évolués (radiateurs haut de gamme plus ventilation, refroidissement par circulation de liquide -watercooling-, ou même azote liquide pour aller jusqu'à doubler la fréquence initiale du processeur).

Augmenter la fréquence du processeur augmente en fait la vitesse du bus de données principal de la machine (FSB), et donc accélère tous les composants branchés sur la carte mère. La fonction PCI-Lock, présente sur absolument toutes les cartes mères récentes, permet d'éviter ce problème et limite l'augmentation de fréquence au processeur et à la mémoire.

### Risques et dangers

Le principal risque de l'overclocking est de détruire le processeur par application d'une tension d'alimentation trop importante (Vcore), d'une température trop élevé au niveau du c ur, ou encore de courant de fuite inter-transistor trop important. Dans le passé, les processeurs risquaient également de brûler si la température devenait trop élevée, mais actuellement absolument tous les processeurs sont équipés d'un système de sonde qui coupe automatiquement le système si la température dépasse les limites fixées par le constructeur (coupure automatique sur les C2D et C2Q à 120/125°C). Le bon fonctionnement de ce coupe circuit est garanti dans la cadre d'une utilisation normale du processeur. Le fait d'utiliser le processeur à une fréquence supérieure a également une influence sur sa durée de vie (20 ans en moyenne), même si on considère en général que la réduction est négligeable comparé au temps de vie d'un processeur (rarement plus de 5 ans).

Si toutefois la puce n'est pas détruite par l'overclocking, il existe un risque accru de faute de calcul et/ou de d'apparition d<u>'artefacts</u> durant un traitement, ce qui peut avoir diverses conséquences suivant l'utilisation du processeur au moment de l'apparition de l'artefact, on peut citer pour l'exemple:

- Apparition de taches sur des images,

- Déclenchement intempestif d'une alarme,

- Instabilité/Blocage/Destruction de l'OS suite à des écritures corrompues,

- Erreurs de calculs du type 1 + 1 = 3,

..

# Refroidissement du processeur

Le problème le plus important de l'overclocking est donc le refroidissement du processeur.

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

- Le système le plus couramment utilisé est le ventilateur monté sur un radiateur (le radiateur est une plaque de métal comportant des ailettes qui permet d'améliorer les échanges de température entre le processeur sur lequel il est monté et l'air ambiant). Le ventilateur peut aussi être monté directement sur le processeur, mais le refroidissement sera moins bon; parfois une petite plaque de métal intercalée entre le ventilateur et le processeur aide à dissiper la chaleur du processeur. Le ventilateur doit être le plus volumineux possible pour permettre un brassage d'air important qui contribuera aussi à la ventilation du boîtier...

- L'aération est, elle aussi, très importante car c'est le brassage de l'air du boîtier qui va permettre d'évacuer la chaleur, que les éléments ont fourni à l'air, à l'extérieur. C'est pour cela qu'un boîtier "ordonné" permet de minimiser les obstacles à la ventilation. En effet les nappes des disques dur, avec par exemple les nappes PATA (IDE), qui sont très larges, si elles sont situées devant un élément qui chauffe (devant le processeur par exemple) vont nuire à la circulation d'air et risquent de provoquer une surchauffe (même pour un processeur non-overclocké) ; ce problème est rendu négligeable par l'utilisation de nappes Serial-ATA très fines (de 0,5 à 1 cm). Nouvellement, des nappes Pata "rondes" ont fait surface améliorant la ventillation dans les boîtiers encore équipés en IDE

- On peut trouver de plus en plus de systèmes de refroidissement de processeur par liquide (

Watercooling). Ces systèmes plus coûteux que les précédents ont l'avantage de mieux refroidir.

Ils sont surtout utilisés lors de sur-fréquençage et ils sont aussi plus silencieux. Attention tout de même à la place nécessaire dans l'unité centrale, certains kits de fabricants proposent même de pouvoir refroidir divers élément de l'ordinateur: (carte graphique, mémoire vive, etc...).

# Fabrication des microprocesseurs

La fabrication d'un microprocesseur est essentiellement identique à celle de n'importe que<u>l circuit intégré</u> (voir le chapitre à ce sujet). Elle suit donc un procédé complexe. Mais l'énorme taille de la plupart des microprocesseurs a tendance à augmenter encore le coût de l'opération.

La <u>loi de Moore</u>, qui indique que le degré d'intégration des microprocesseurs double tous les 18 mois, indique également que les coûts de production doublent en même temps que le degré d'intégration.

La fabrication des microprocesseurs est aujourd'hui considérée comme l'un des deux facteurs d'augmentation de la capacité des unités de fabrication (avec les contraintes liées à la fabrication des mémoires à grande capacité). La finesse de la gravure industrielle atteint désormais 45 nm. Cela fixe la vitesse de traitement maximale d'un microprocesseur aux alentours de 4GHz. En diminuant encore la finesse de gravure, les fondeurs se heurtent aux règles perturbantes de la Mécanique quantique qui bouleversent les résultats des calculs.

# Fonctions à développer

# Organisation parallèle

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Selon le <u>système d'exploitation</u>, la tendance actuelle est l'installation de plusieurs processeurs parallèles et de multiples tâches d'où l'importance grandissante des fonctions d'arbitrages entre processus (par exemple l'hyper threading). En effet, l'architecture super scalaire (mise en parallèle des tâches dans une unité d'exécution) des processeurs actuels ne suffit actuellement plus au multi-threading tel qu'il est utilisé.

En revanche, les processeurs à plusieurs <u>c urs</u> demandent que soit étudié de près la <u>répartition</u> des tâches entre eux si on ne veut pas voir observer un ralentissement des opérations; c'est ce qu'on nomme l'affinité du processeur (processor affinity).

#### Sécurité et location

Il existe de nombreux projets d'intégration au c ur des microprocesseurs de fonctions visant à empêcher les copies illégales de fichiers (technologies <u>DRM</u>). Le consortium <u>Trusted Computing Group</u>, notamment, a déjà créé des puces permettant de créer une "zone de confiance" au sein du système informatique, à l'aide d'une puce d'identification spécifique. Certains modèles d'ordinateurs, comme les portables d'IBM intègrent déjà de telles puces. La prochaine génération de cette technologie sera probablement intégrée dans les processeurs centraux des ordinateurs.

Ces technologies sont décriées, notamment par des partisans du <u>logiciel libre</u>, pour qui elles possèdent un potentiel liberticide. En effet, conjuguées à un <u>système d'exploitation</u> prévu à cet effet, par exemple dérivé du projet <u>NGSCB</u> de <u>Microsoft</u>, ce type de technologie permet au <u>tiers de confiance</u> (le prestataire qui va vérifier la validité des composants du système) d'accéder à distance au contenu de l'ordinateur, voire d'empêcher l'exécution de certaines opérations sur celui-ci. <u>Linus Torvalds</u> estime inapproprié de comparer un <u>logiciel</u> à un <u>contenu</u>, et approuve totalement la protection des contenus par leurs propriétaires, bien qu'il considère que celle des logiciels ne soit pas une bonne idée pour ceux qui la pratiquen<del>f</del>.

#### Mémoire étendue

Ancien système d'extension de la mémoire permettant de dépasser la limite de 1 Mio du microprocesseur 8086 de l'époque. Cette mémoire était accessible par pages de 64 Kio. On ne l'utilise plus de nos jours en raison des capacités d'adressages étendues des processeurs récents ainsi qu'en raison de l'extrême lenteur des accès aléatoires dès que ceux-ci nécessitent un changement de page mémoire.

#### Systèmes d'exploitation multiple

Vanderpool/Silvervale : si un système d'exploitation de travail est infecté par un virus coriace, un autre de préférence sur une autre base comme <u>Linux</u> vers <u>Mac OS</u> ou <u>Windows</u> pourrait agir comme gardien et désinfecter le premier tout en ne laissant pas la possibilité au virus de se propager.

### Anticipation des problèmes et gestion à distance

#### VOUS PRESENTELE COURS SUR LES MICROPROCESSEURS ET LEURS FABRICANTS

Particulièrement utile pour les serveurs.

# Le problème de l'échauffement

L'échauffement des microprocesseurs reste approximativement et malgré l'usage de techniques de gravures de plus en plus fines, proportionnel au carré de leur tension à architecture donnée. AvecV la tension, f la fréquence, et k un coefficient d'ajustement, on peut calculer la puissance dissipéeP:

$$P = k \times V^2 \times f$$

- Un i686 à 1 GHz (1,7 V), deux fois plus rapide, consomme typiquement 34 W, ce qui n'est pas loin du quadruple.

- À 2 GHz un Opteron dissipe 107 W et un G5 55 W.

Ce problème est lié à un autre, celui de la <u>dissipation thermique</u> et donc souvent de<u>s ventilateurs</u>, sources de nuisances sonores difficilement compatibles avec un environnement de bureau. Le refroidissement liquide (à eau) est proposé.

- L'utilisation d'une pâte thermique assure une meilleure conduction de la chaleur du processeur vers le radiateur, une des plus connues étant l'Artic silver 5.

- Un microprocesseur contenant beaucoup de transistors verra sa puissance dépendre fortement de la température. Ceci est dû aux mouvements de plus en plus aléatoires des électrons en fonction de la hausse de la température.