# Intel® Xeon Phi™ Coprocessor System Software Developers Guide

Revision: 2.03

Last Modified: November 8, 2012

**IBL Doc ID:** 488596

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The Intel® MIC Architecture coprocessors described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The code names Knights Ferry, Aubrey Isle, and Knights Corner presented in this document are only for use by Intel to identify products, technologies, or services in development, that have not been made commercially available to the public, i.e., announced, launched or shipped. They are not "commercial" names for products or services and are not intended to function as trademarks.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, Intel literature may be obtained by calling 1-800-548-4725, or go to: <a href="http://www.intel.com/design/literature.htm">http://www.intel.com/design/literature.htm</a>

Intel, the Intel logo, Intel® Pentium®, Intel® Pentium® Pro, Xeon®, Intel® Xeon Phi™, Intel® Pentium® 4 Processor, Intel Core™ Solo, Intel® Core™ Duo, Intel Core™ 2 Duo, Intel Atom™, MMX™, Intel® Streaming SIMD Extensions (Intel® SSE), Intel® Advanced Vector Extensions (Intel® AVX), Intel® VTune™ Amplifier XE are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright 2011-2012 Intel Corporation. All rights reserved.

## **Table of Contents**

| Table o   | of Conte         | nts         |                                                      | 3    |  |  |

|-----------|------------------|-------------|------------------------------------------------------|------|--|--|

| List of I | List of Figures7 |             |                                                      |      |  |  |

| List of   | Tables           |             |                                                      | 8    |  |  |

| 1         | Introdu          | iction      |                                                      | .10  |  |  |

|           | 1.1              | Programmi   | ng Model                                             | 10   |  |  |

|           |                  | 1.1.1       | Application Programming                              | 10   |  |  |

|           |                  | 1.1.2       | System Programming                                   | 10   |  |  |

|           | 1.2              | Section Ove | erview                                               | 11   |  |  |

|           | 1.3              | Related Ted | chnologies and Documents                             | 11   |  |  |

| 2         | Intel® >         | (eon Phi™ C | oprocessor Architecture                              | . 13 |  |  |

|           | 2.1              | Intel® Xeon | Phi™ Coprocessor Architecture                        | 13   |  |  |

|           |                  | 2.1.1       | Core                                                 | 17   |  |  |

|           |                  | 2.1.2       | Instruction Decoder                                  | 19   |  |  |

|           |                  | 2.1.3       | Cache Organization and Hierarchy                     | 19   |  |  |

|           |                  | 2.1.4       | Page Tables                                          | 22   |  |  |

|           |                  | 2.1.5       | Hardware Threads and Multithreading                  | 23   |  |  |

|           |                  | 2.1.6       | Faults and Breakpoints                               | 24   |  |  |

|           |                  | 2.1.7       | Performance Monitoring Unit and Events Monitor       | 24   |  |  |

|           |                  | 2.1.8       | System Interface                                     | 26   |  |  |

|           |                  | 2.1.9       | VPU and Vector Architecture                          | 32   |  |  |

|           |                  | 2.1.10      | Intel® Xeon Phi™ Coprocessor Instructions            | 33   |  |  |

|           |                  | 2.1.11      | Multi-Card                                           | 33   |  |  |

|           |                  | 2.1.12      | Host and Intel® MIC Architecture Physical Memory Map | 34   |  |  |

|           |                  | 2.1.13      | Power Management                                     | 35   |  |  |

|           | 2.2              | Intel® Xeon | Phi™ Coprocessor Software Architecture               | 36   |  |  |

|           |                  | 2.2.1       | Architectural Overview                               | 36   |  |  |

|           |                  | 2.2.2       | Intel® Manycore Platform Software Stack (MPSS)       | 38   |  |  |

|           |                  | 2.2.3       | Bootstrap                                            | 40   |  |  |

|           |                  | 2.2.4       | Linux* Loader                                        | 41   |  |  |

|           |                  | 2.2.5       | The Coprocessor Operating System (coprocessor OS)    | 42   |  |  |

|           |                  |             |                                                      |      |  |  |

|   |       | 2.2.6        | Symmetric Communication Interface (SCIF)                           | 44    |

|---|-------|--------------|--------------------------------------------------------------------|-------|

|   |       | 2.2.7        | Host Driver                                                        | 44    |

|   |       | 2.2.8        | Sysfs Nodes                                                        | 50    |

|   |       | 2.2.9        | Intel® Xeon Phi™ Coprocessor Software Stack for MPI Applications   | 52    |

|   |       | 2.2.10       | Application Programming Interfaces                                 | 63    |

| 3 | Power | Manageme     | nt, Virtualization, RAS                                            | 64    |

|   | 3.1   | Power Ma     | nagement (PM)                                                      | 64    |

|   |       | 3.1.1        | Coprocessor OS Role in Power Management                            | 65    |

|   |       | 3.1.2        | Bootloader Role in Power Management                                | 66    |

|   |       | 3.1.3        | Host Driver Role in Power Management                               | 66    |

|   |       | 3.1.4        | Power Reduction                                                    | 67    |

|   |       | 3.1.5        | PM Software Event Handling Function                                | 84    |

|   |       | 3.1.6        | Power Management in the Intel® MPSS Host Driver                    | 87    |

|   | 3.2   | Virtualizati | on                                                                 | 91    |

|   |       | 3.2.1        | Hardware Assisted DMA Remapping                                    | 91    |

|   |       | 3.2.2        | Hardware Assisted Interrupt Remapping                              | 91    |

|   |       | 3.2.3        | Shared Device Virtualization                                       | 91    |

|   | 3.3   | Reliability  | Availability Serviceability (RAS)                                  | 91    |

|   |       | 3.3.1        | Check Pointing                                                     | 92    |

|   |       | 3.3.2        | Berkeley Labs Check point and Restore (BLCR)                       | 93    |

|   |       | 3.3.3        | Machine Check Architecture (MCA)                                   | 95    |

|   |       | 3.3.4        | Cache Line Disable                                                 | 108   |

|   |       | 3.3.5        | Core Disable                                                       | 109   |

|   |       | 3.3.6        | Machine Check Flows                                                | 109   |

|   |       | 3.3.7        | Machine Check Handler                                              | 111   |

|   |       | 3.3.8        | Error Injection                                                    | 111   |

| 4 | Opera | ting System  | Support and Driver Writer's Guide                                  | . 113 |

|   | 4.1   | Third Party  | OS Support                                                         | 113   |

|   | 4.2   | Intel® Xeor  | n Phi™ Coprocessor Limitations for Shrink-Wrapped Operating System | s113  |

|   |       | 4.2.1        | Intel x86 and Intel 64 ABI                                         | 113   |

|   |       | 4.2.2        | PC-AT / I/O Devices                                                | 113   |

|   |       | 4.2.3        | Long Mode Support                                                  | 113   |

|   |         | 4.2.4        | Custom Local APIC                         | .113  |

|---|---------|--------------|-------------------------------------------|-------|

|   |         | 4.2.5        | Custom I/O APIC                           | .114  |

|   |         | 4.2.6        | Timer Hardware                            | .114  |

|   |         | 4.2.7        | Debug Store                               | .114  |

|   |         | 4.2.8        | Power and Thermal Management              | .114  |

|   |         | 4.2.9        | Pending Break Enable                      | .115  |

|   |         | 4.2.10       | Global Page Tables                        | .115  |

|   |         | 4.2.11       | CNXT-ID – L1 Context ID                   | .115  |

|   |         | 4.2.12       | Prefetch Instructions                     | .115  |

|   |         | 4.2.13       | PSE-36                                    | .115  |

|   |         | 4.2.14       | PSN (Processor Serial Number)             | .116  |

|   |         | 4.2.15       | Machine Check Architecture                | .116  |

|   |         | 4.2.16       | Virtual Memory Extensions (VMX)           | .116  |

|   |         | 4.2.17       | CPUID                                     | .116  |

|   |         | 4.2.18       | Unsupported Instructions                  | .116  |

| 5 | Applica | ation Progra | mming Interfaces                          | . 119 |

|   | 5.1     | The SCIF AI  | Pls                                       | .119  |

|   | 5.2     | MicAccess    | API                                       | .122  |

|   | 5.3     | Support for  | r Industry Standards                      | .125  |

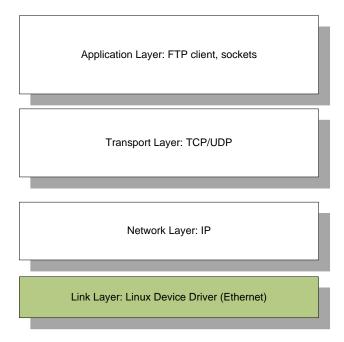

|   |         | 5.3.1        | TCP/IP Emulation                          | .126  |

|   | 5.4     | Intel® Xeor  | n Phi™ Coprocessor Command Utilities      | .126  |

|   | 5.5     | NetDev Vir   | tual Networking                           | .126  |

|   |         | 5.5.1        | Introduction                              | .126  |

|   |         | 5.5.2        | Implementation                            | .127  |

| 6 | Compu   | ite Modes a  | nd Usage Models                           | . 129 |

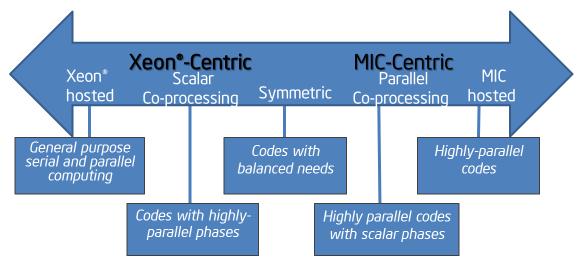

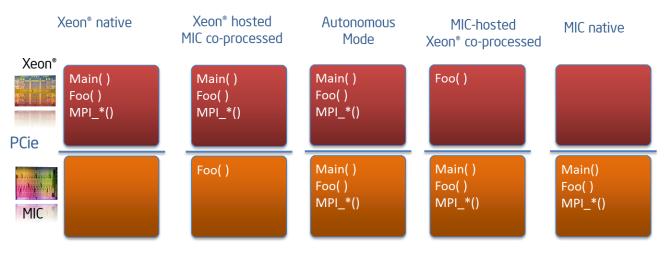

|   | 6.1     | Usage Mod    | dels                                      | .129  |

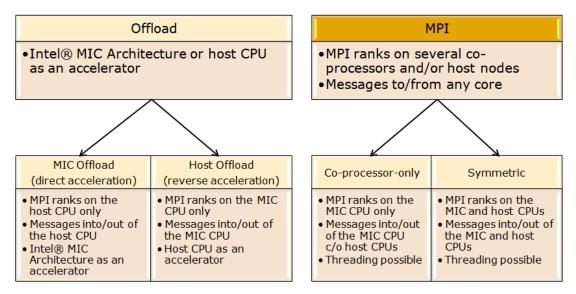

|   | 6.2     | MPI Progra   | mming Models                              | .130  |

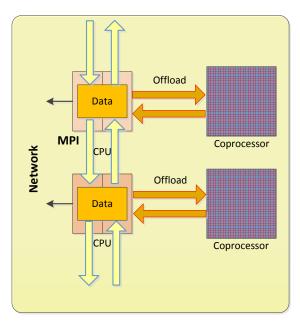

|   |         | 6.2.1        | Offload Model                             | .131  |

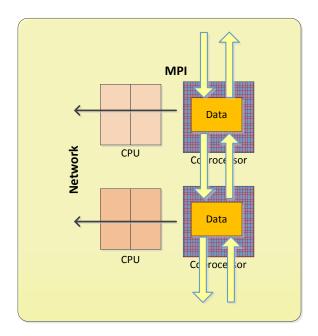

|   |         | 6.2.2        | Coprocessor-Only Model                    | .132  |

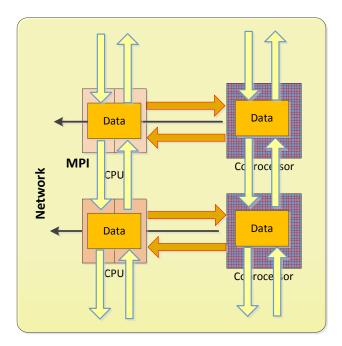

|   |         | 6.2.3        | Symmetric Model                           | .132  |

|   |         | 6.2.4        | Feature Summary                           | .133  |

|   |         | 6.2.5        | MPI Application Compilation and Execution | .134  |

| Intel® | Xeon Phi™ | Coprocessor Vector Architecture                         | 135 |  |

|--------|-----------|---------------------------------------------------------|-----|--|

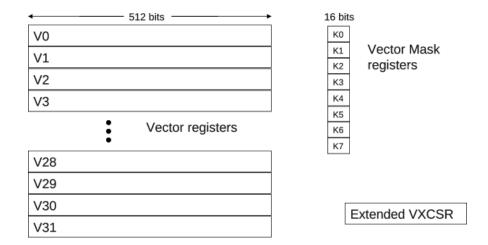

| 7.1    | Overview  | v                                                       | 135 |  |

| 7.2    | Vector St | tate                                                    | 135 |  |

| 7.3    | VPU Basi  | c Functions                                             | 135 |  |

| 7.4    | VPU Data  | a Types                                                 | 136 |  |

| 7.5    | Extended  | d Math Unit                                             | 137 |  |

| 7.6    | SP FP Op  | SP FP Operations                                        |     |  |

| 7.7    | DP FP Op  | perations                                               | 138 |  |

| 7.8    | Vector IS | A Overview                                              | 138 |  |

| 7.9    | Vector N  | omenclature                                             | 141 |  |

| 7.10   | Write Ma  | asking                                                  | 142 |  |

| 7.11   | Swizzling |                                                         | 147 |  |

|        | 7.11.1    | Swizzle Limitations                                     | 148 |  |

|        | 7.11.2    | Register-Register Swizzle Form                          | 149 |  |

|        | 7.11.3    | Register-Memory Swizzle Form                            | 151 |  |

|        | 7.11.4    | Swizzle Usage Examples                                  | 153 |  |

| 7.12   | The Shuf  | fle                                                     | 156 |  |

| 7.13   | Memory    | and Vectors                                             | 157 |  |

|        | 7.13.1    | Load and Store Operations                               | 158 |  |

|        | 7.13.2    | Alignment                                               | 160 |  |

|        | 7.13.3    | Packing and Unpacking Operations                        | 161 |  |

|        | 7.13.4    | Non-Temporal Data                                       | 163 |  |

|        | 7.13.5    | Prefetching                                             | 164 |  |

| 7.14   | New Inst  | ructions                                                | 165 |  |

|        | 7.14.1    | Mask Manipulation Instructions                          | 165 |  |

|        | 7.14.2    | Packed Typeless Instructions                            | 166 |  |

|        | 7.14.3    | New Packed SP FP Instructions                           | 167 |  |

|        | 7.14.4    | New Packed Double-Precision Floating-Point Instructions | 167 |  |

|        | 7.14.5    | New Packed Int32 Instructions                           | 168 |  |

7

| 8      | Glossary and Abbreviations169                                                                    |     |

|--------|--------------------------------------------------------------------------------------------------|-----|

| 9      | References                                                                                       |     |

| Appen  | dix: SBOX Control Register List174                                                               |     |

|        |                                                                                                  |     |

| list o | f Figures                                                                                        |     |

| LISCO  | T I Igui C3                                                                                      |     |

| Figure | 2-1. Basic building blocks of the Intel® Xeon Phi™ Coprocessor                                   | 14  |

| Figure | 2-2: Core Pipeline Components                                                                    | 18  |

| Figure | 2-3: Intel® Xeon Phi™ Coprocessor Core Architecture                                              | 18  |

| Figure | 2-4: MESI Protocol                                                                               | 20  |

| Figure | 2-5 Globally Owned Locally Shared (GOLS) Diagram                                                 | 21  |

| Figure | 2-6. Multithreading Architectural Support in the Intel® Xeon Phi™ Coprocessor                    | 23  |

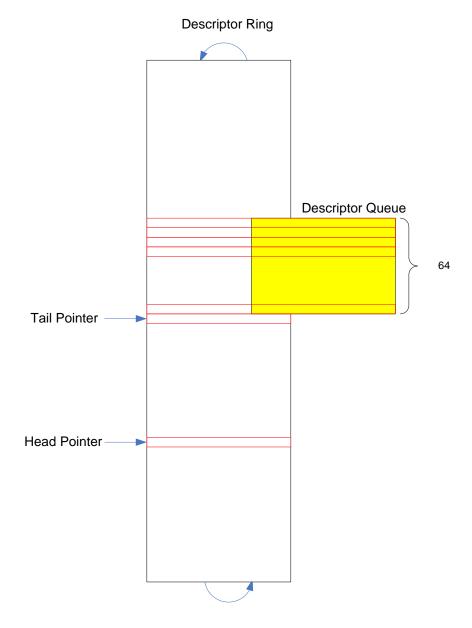

| Figure | 2-7. DMA Channel Descriptor Ring plus Local Descriptor Queue                                     | 29  |

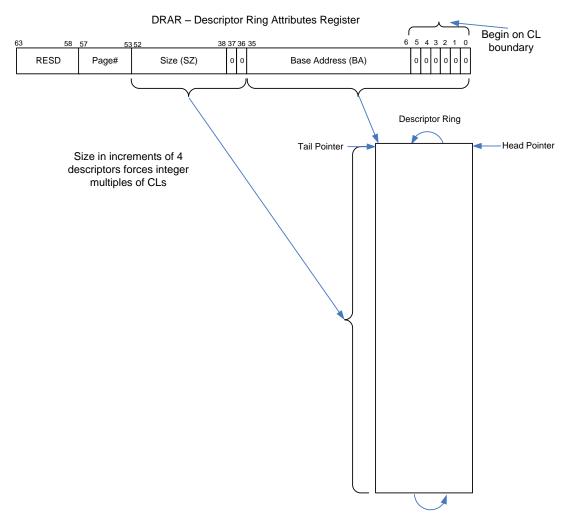

| Figure | 2-8. Descriptor Ring Attributes                                                                  | 30  |

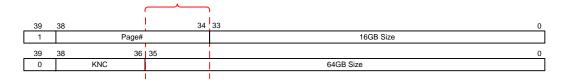

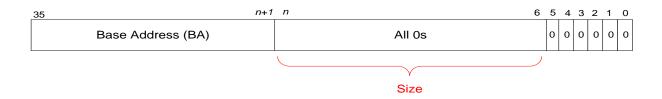

|        | 2-9. Intel® Xeon Phi™ Coprocessor Address Format                                                 |     |

| _      | 2-10. Base Address Width Variations                                                              |     |

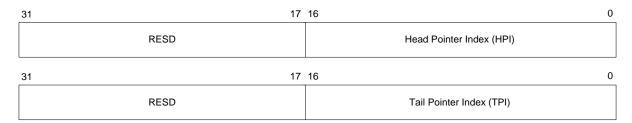

|        | 2-11 Head and Tail Pointer Index Registers                                                       |     |

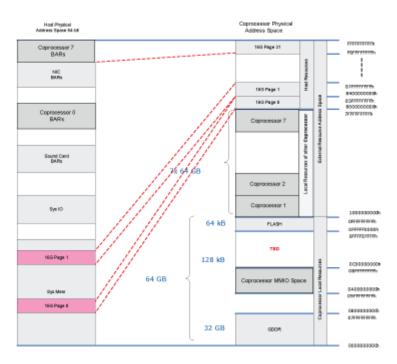

| _      | 2-12. Host and Intel® MIC Architecture Physical Memory Map                                       |     |

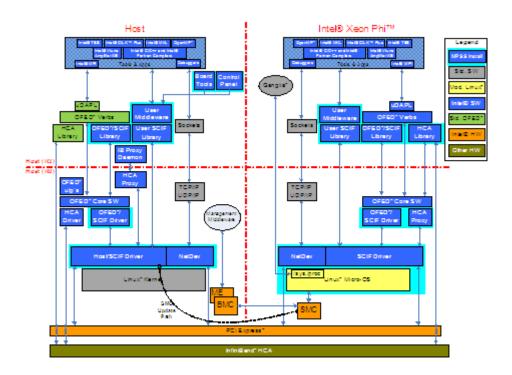

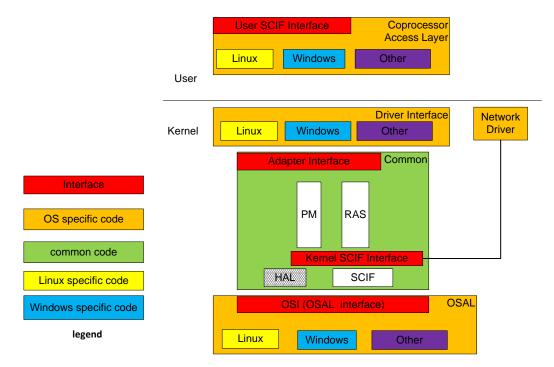

| _      | 2-13. Intel® Xeon Phi™ Coprocessor Software Architecture                                         |     |

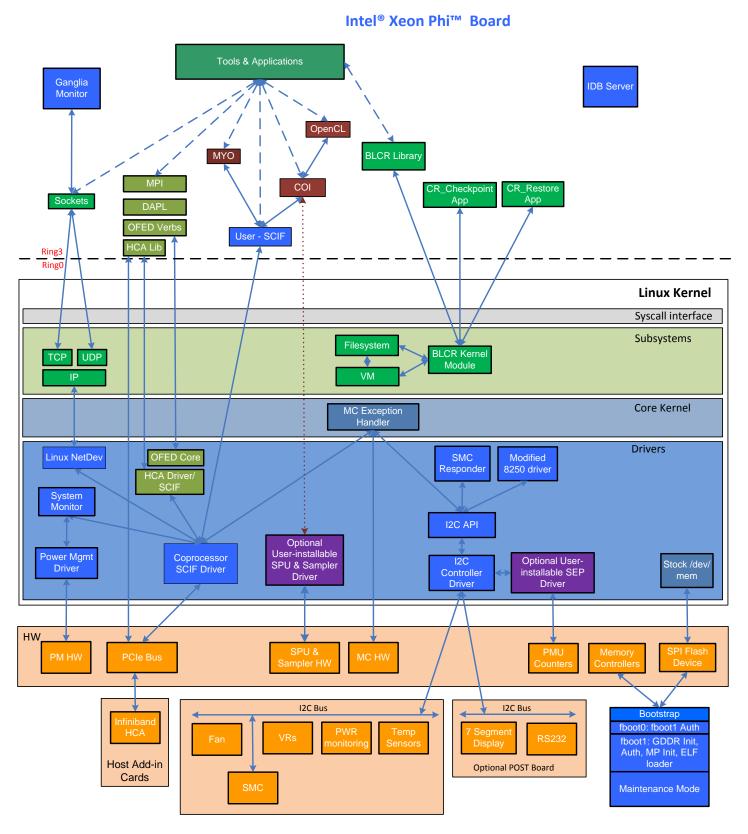

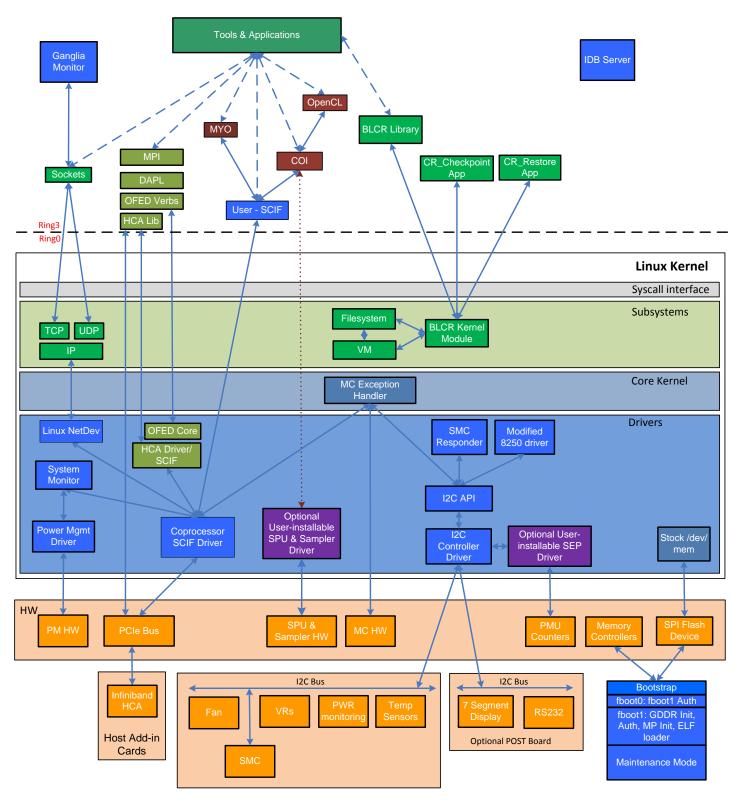

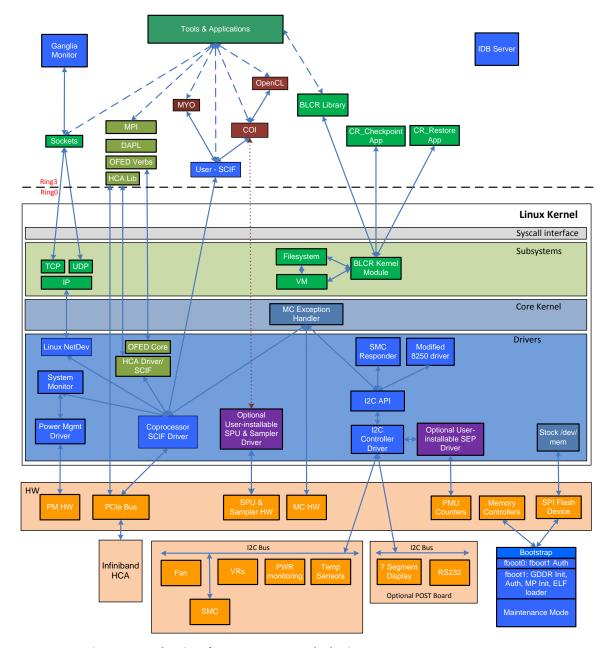

| _      | 2-14. Intel® Xeon Phi™ Coprocessor Software Stack                                                |     |

| •      | 2-15. The Linux* Coprocessor OS Block Diagram                                                    |     |

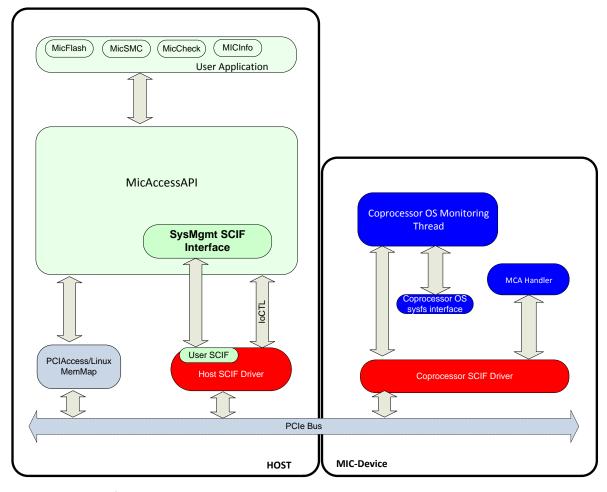

| -      | 2-16. Intel® Xeon Phi™ Coprocessor Host Driver Software Architecture Components                  |     |

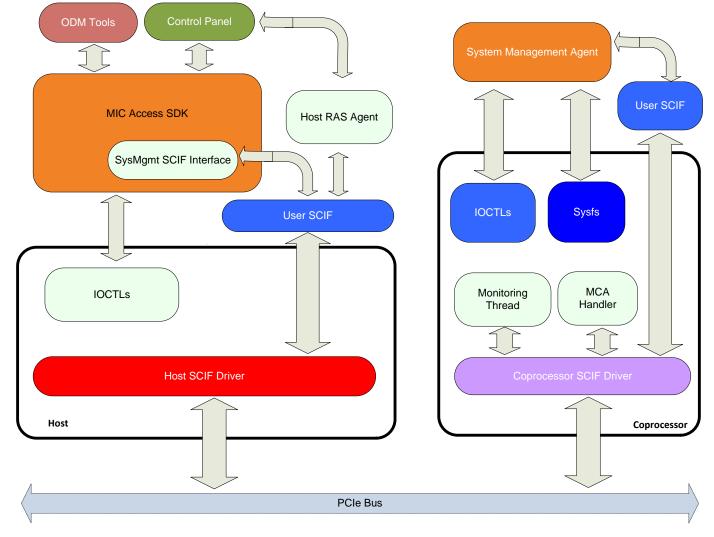

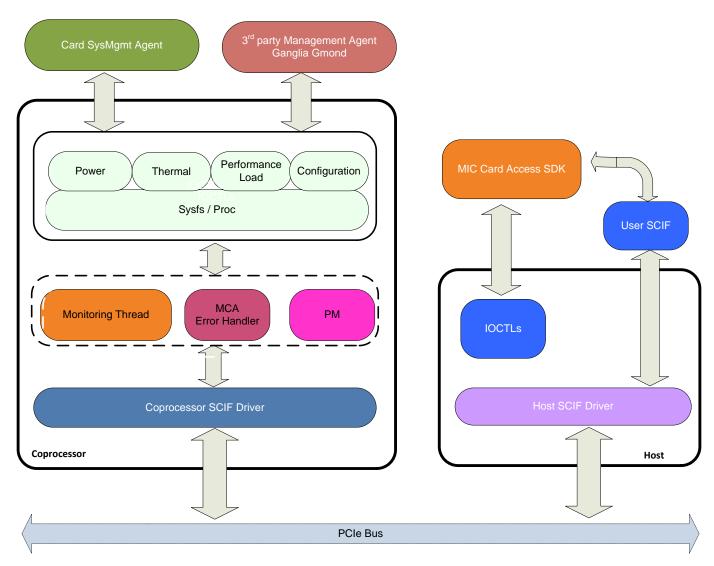

| _      | 2-17. Control Panel Software Architecture                                                        |     |

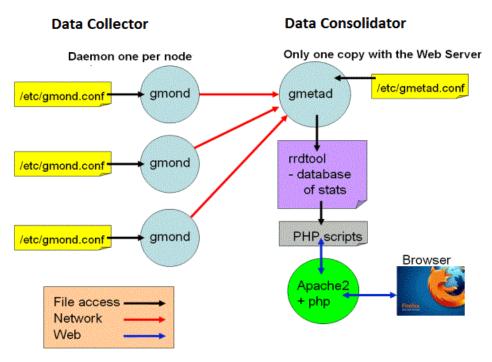

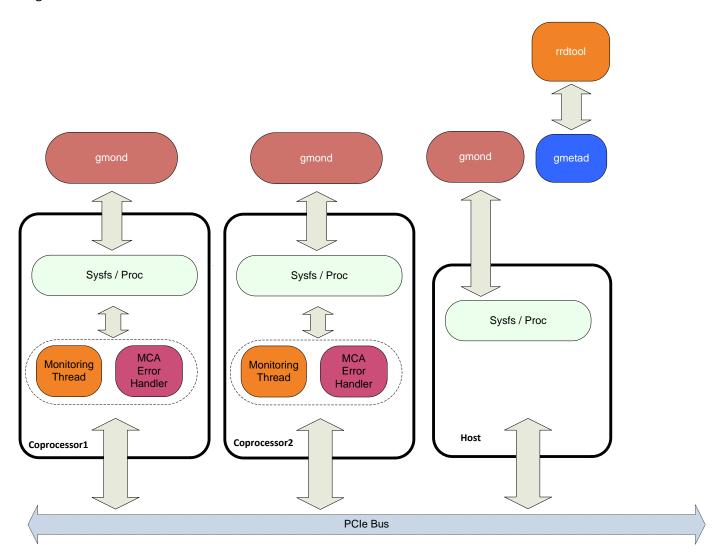

| •      | 2-18. Ganglia* Monitoring System Data Flow Diagram                                               |     |

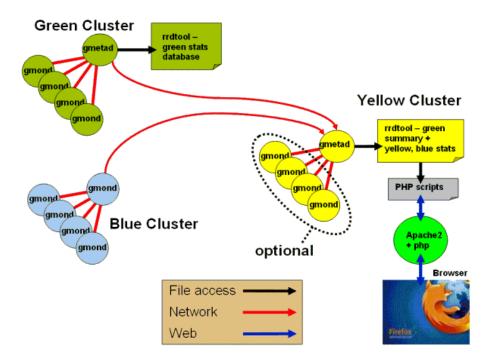

| _      | 2-19: Ganglia* Monitoring System for a Cluster                                                   |     |

| _      | 2-20. Intel® Xeon Phi™ Coprocessor Ganglia* Support Diagram                                      |     |

| _      | 2-21: MPSS Ganglia* Support                                                                      |     |

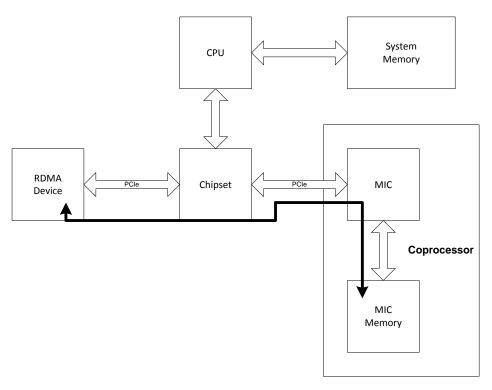

| _      | 2-22 RDMA Transfer with CCL                                                                      |     |

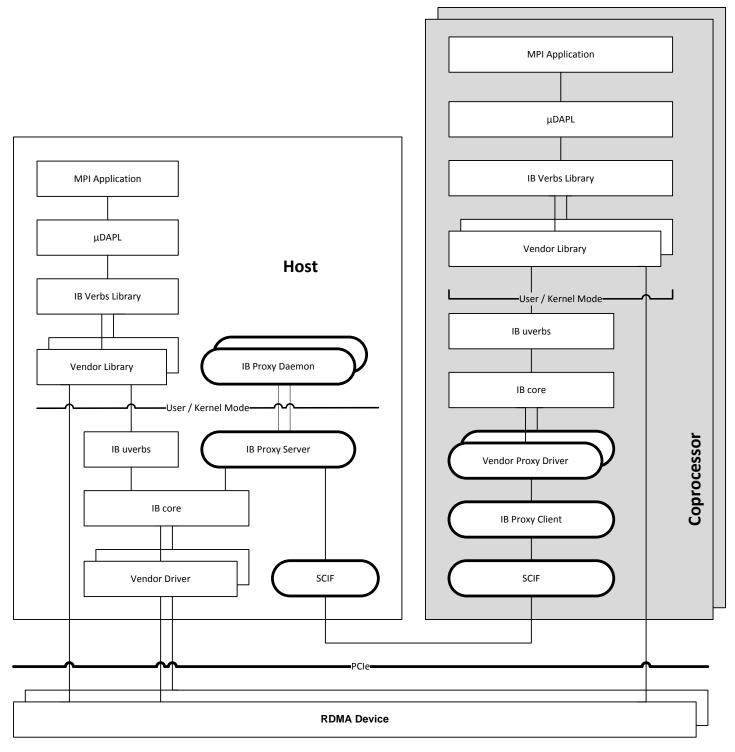

| _      | 2-23 MPI Application on CCL                                                                      |     |

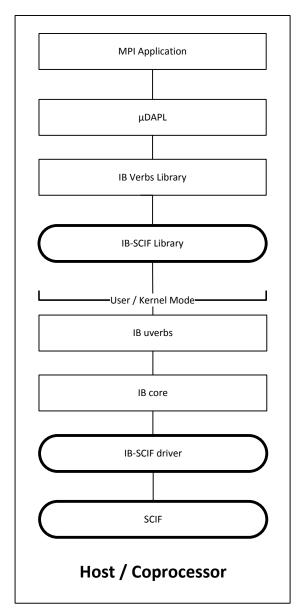

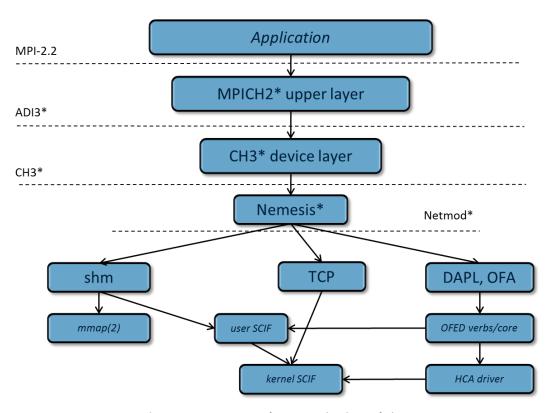

| _      | 2-24: OFED*/SCIF Modules                                                                         |     |

| _      | 2-25. Supported Communication Fabrics                                                            |     |

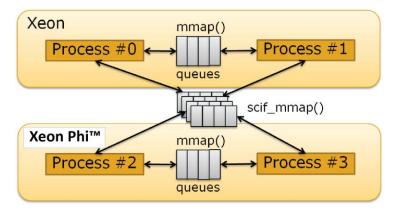

| •      | 2-26. Extended SHM Fabric Structure                                                              |     |

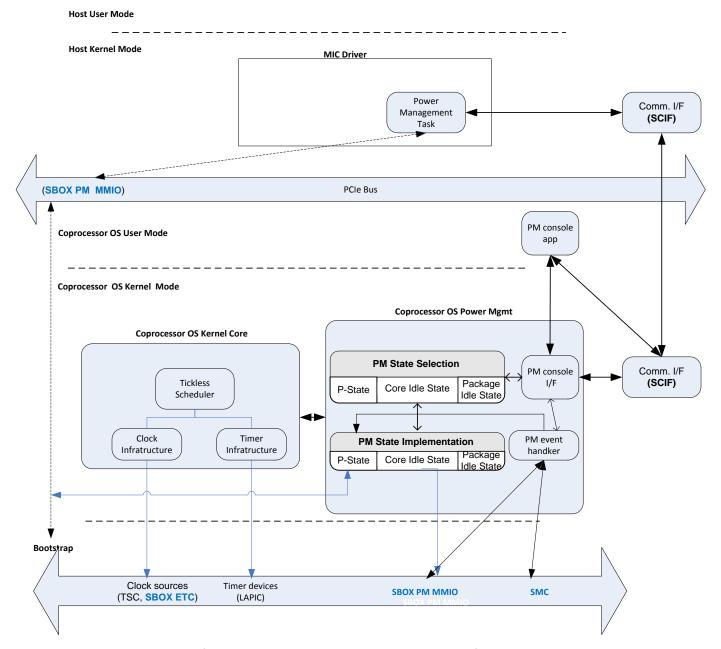

| _      | 3-1. Intel® Xeon Phi™ Coprocessor Power Management Software Architecture                         |     |

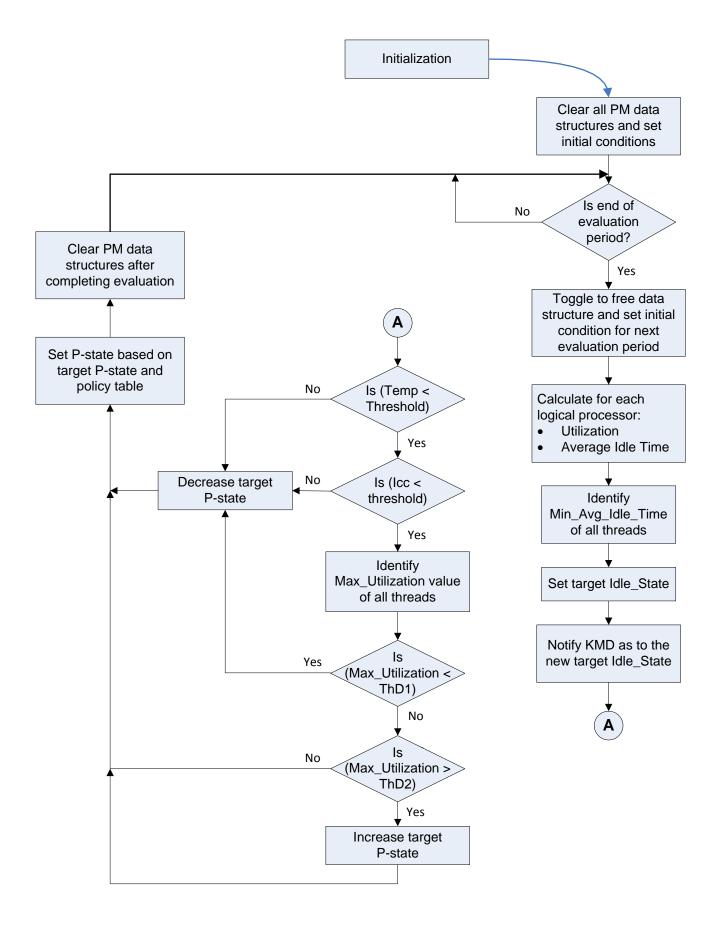

| _      | 3-2. Power Reduction Flow                                                                        |     |

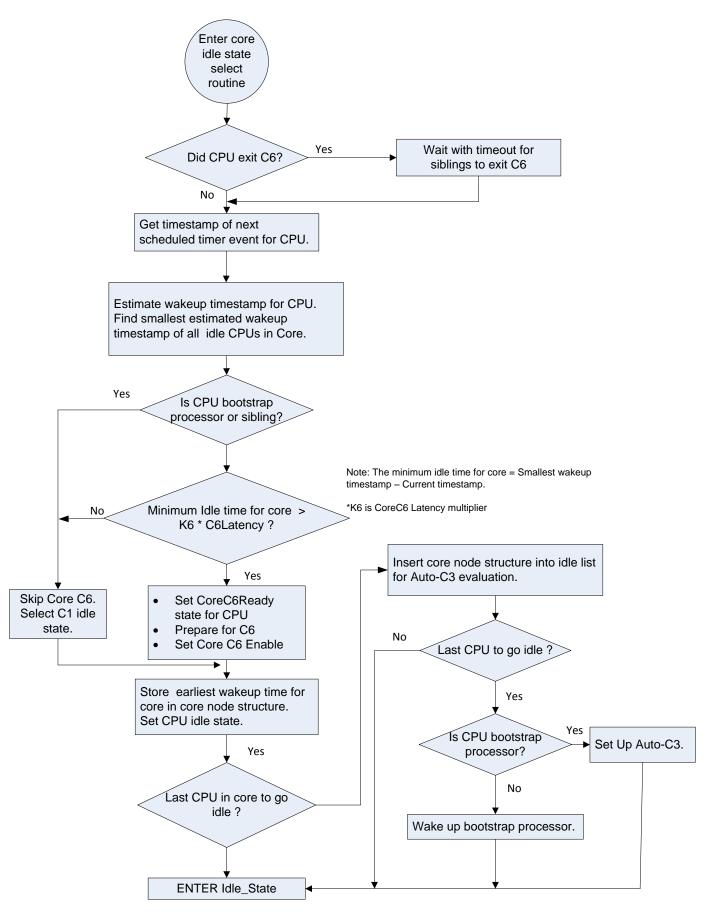

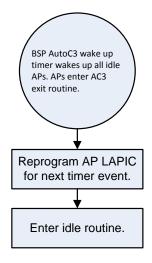

| -      | 3-3. Core C6 Selection                                                                           |     |

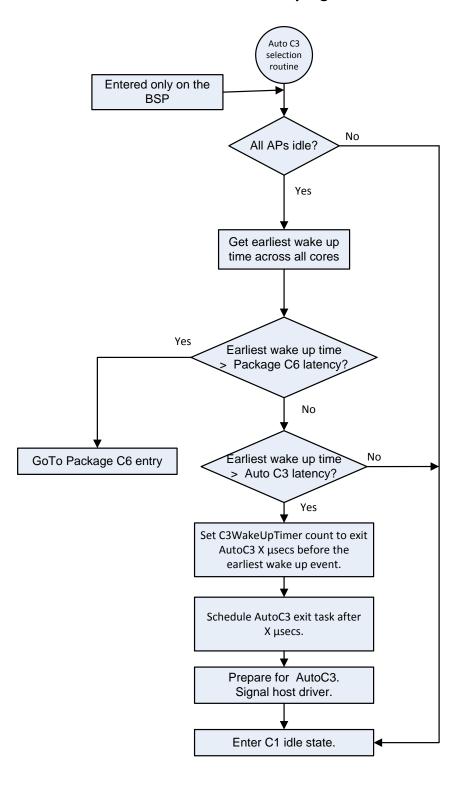

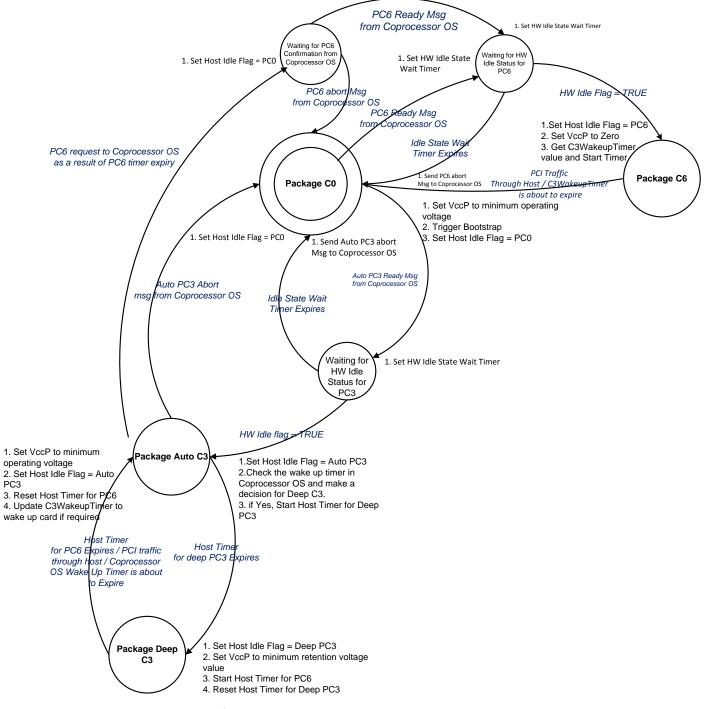

|        | 3-4. Package C-state Selection Flow                                                              |     |

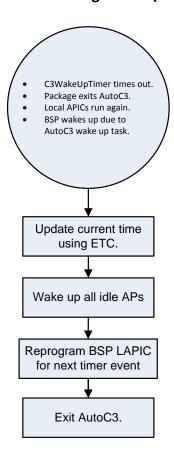

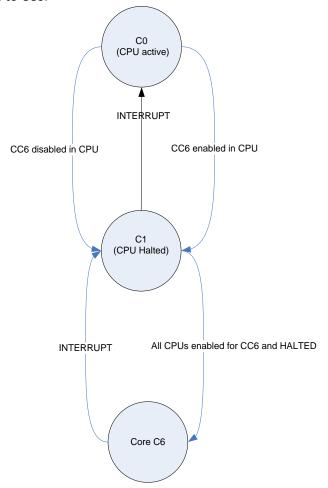

| _      | 3-5 CPU Idle State Transitions                                                                   |     |

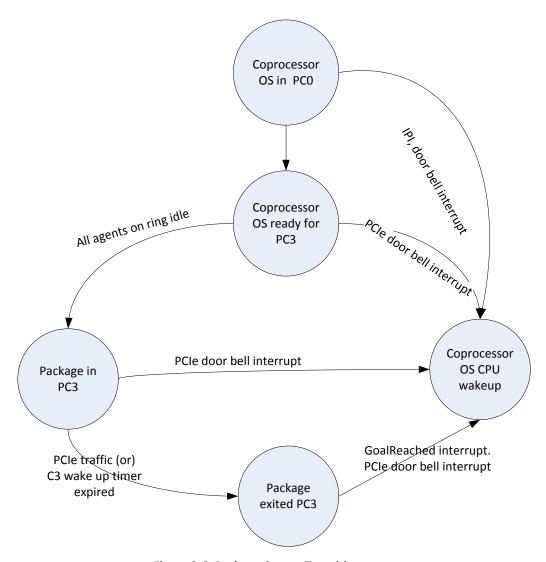

| _      | 3-6. Package C-state Transitions                                                                 |     |

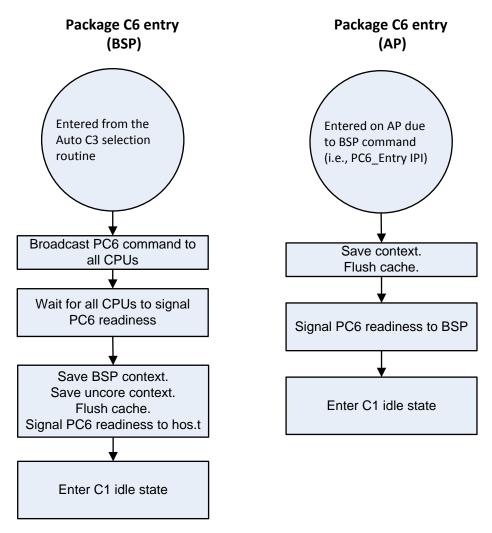

| _      | 3-7 Package C6 Entry and Exit Flow                                                               |     |

| _      | 3-8 Intel® MPSS Host Driver to Coprocessor OS Package State Interactions                         |     |

| _      | 5-1. SCIP Architectural Model                                                                    |     |

| _      | 5-1. Scir Architectural Model                                                                    |     |

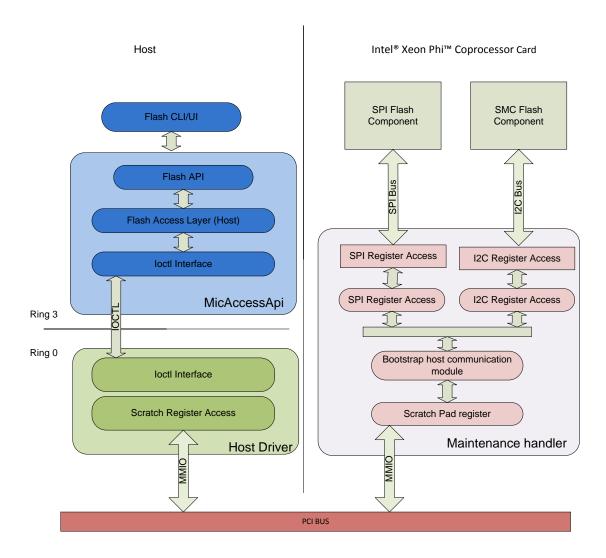

| •      | 5-3 MicAccessAPI Flash Update Procedure                                                          |     |

| _      | 5-4 Linux* Network Stack                                                                         |     |

| _      | 6-1 : A Scalar/Parallel Code Viewpoint of the Intel® MIC Architecture Enabled Compute Continuum  |     |

| iguid  | o 1. A scalary a railer code viewpoint of the inter-viile Architecture Enabled Compute Continuum | 123 |

| Figure 6-7. Compiling and Executing a MPI Application                                      |     |

|--------------------------------------------------------------------------------------------|-----|

| Figure 7-1: VPU Registers                                                                  | 135 |

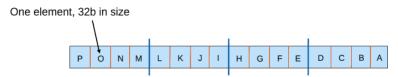

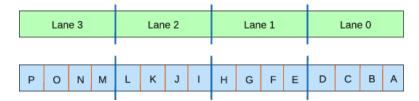

| Figure 7-2. Vector Organization When Operating on 16 Elements of 32-bit Data               | 139 |

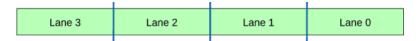

| Figure 7-3. Vector Register Lanes 30                                                       |     |

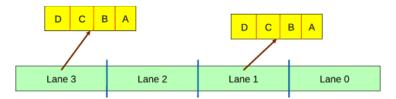

| Figure 7-4. Vector Elements DA Within a Lane                                               | 142 |

| Figure 7-5. Vector Elements PA Across the Entire Vector Register                           | 142 |

| Figure 7-6. Basic Vector Operation Without Write Masking Specified                         |     |

| Figure 7-7. Basic Vector Operation With a Write Masking Specified                          |     |

| Figure 7-8. Effect of Write Mask Values on Result                                          |     |

| Figure 7-9. A Native (Non-Optimal) Newton-Raphson Approximation Using a Write-Mask to Dete |     |

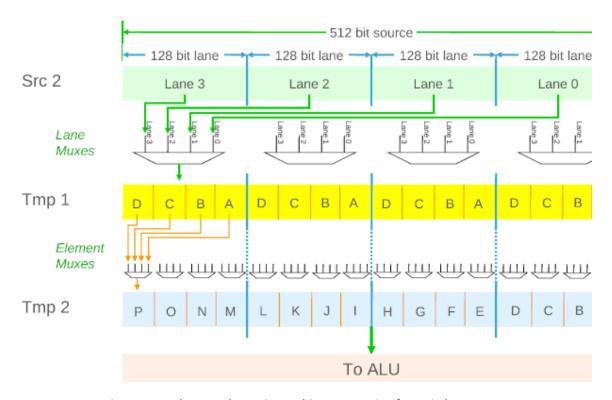

| Figure 7-10. Partial Microarchitecture Design for Swizzle Support                          | •   |

| Figure 7-11. The Complete Microarchitecture Design for Swizzle Support                     |     |

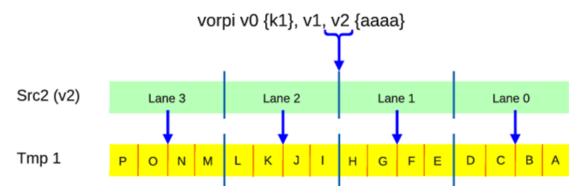

| Figure 7-12. Register-Register Swizzle Operation: Source Selection                         |     |

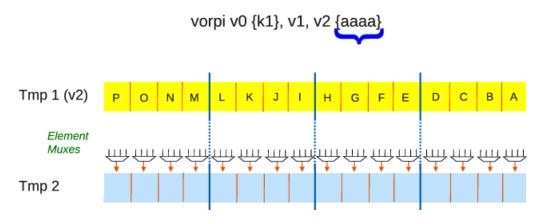

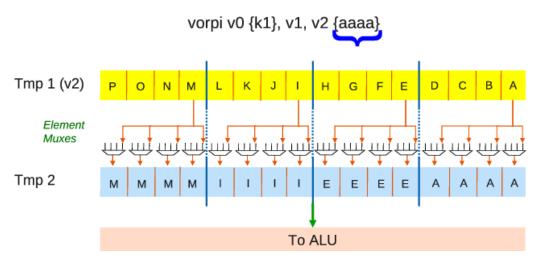

| Figure 7-13. Register-Register Swizzle Operation: Element Muxes                            |     |

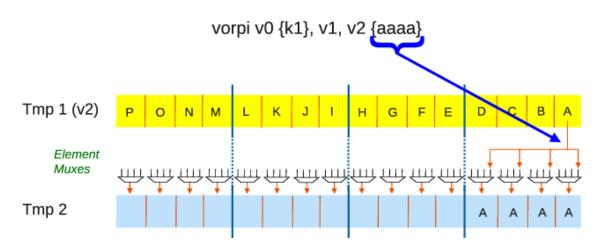

| Figure 7-15. Register-Register Swizzle Operation: Complete Swizzle Result                  |     |

| Figure 7-14. Register-Register Swizzle Operation: First Lane Completion                    |     |

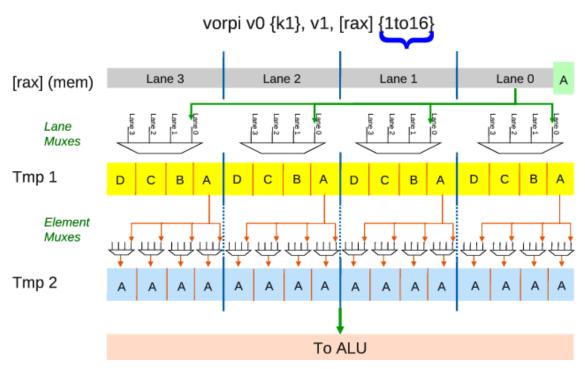

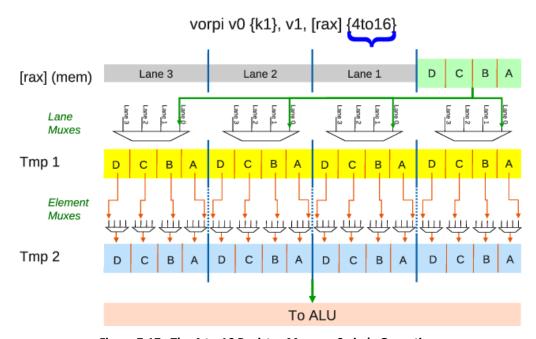

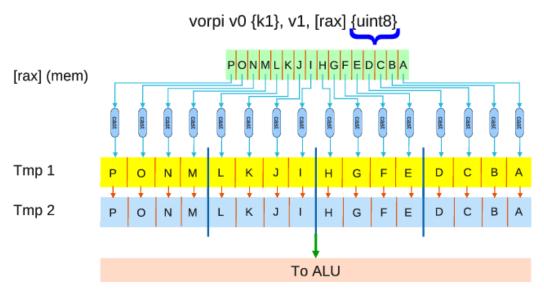

| Figure 7-16. The 1-to-16 Register Memory Swizzle Operation                                 |     |

| Figure 7-17. The 4-to-16 Register-Memory Swizzle Operation                                 |     |

| Figure 7-18. The uint8 Data Conversion Register-Memory Swizzle Operation                   |     |

| Figure 7-19. Trivial Implementation of a Horizontal Add Operation Within One Vector Lane   |     |

| Figure 7-20. Trivial Implementation of a 3x3 Matrix Cross-Product Within One Vector Lane   |     |

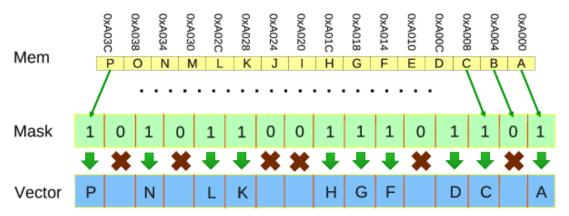

| Figure 7-21. The Behavior of the Vector Load Instruction With a Write Mask                 |     |

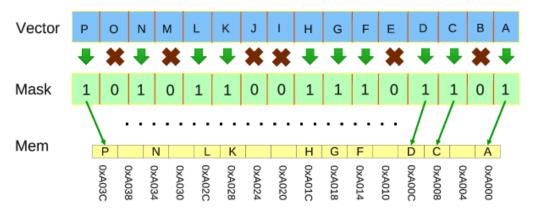

| Figure 7-22. The Behavior of the Vector Store Instruction With a Write Mask                |     |

| Figure 7-23. Compiler Extension to Force Memory Alignment Boundaries in C or C++ Tools     |     |

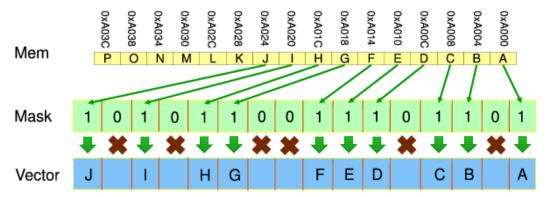

| Figure 7-24. The Behavior of the Vector Unpack Instruction                                 |     |

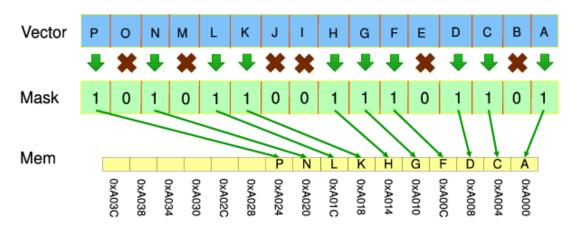

| Figure 7-25: The Behavior of the Vector Pack Instruction                                   |     |

| List of Tables                                                                             |     |

| Table 1-1. Related Industry Standards                                                      |     |

| Table 1-2. Related Documents                                                               | 11  |

| Table 2-1. Description of Coprocessor Components                                           | 16  |

| Table 2-2. L2 Cache States                                                                 | 20  |

| Table 2-3. Tag Directory States                                                            | 21  |

| Table 2-4. Cache Hierarchy                                                                 | 22  |

| Table 2-5. L1 and L2 Caches Characteristics                                                | 23  |

| Table 2-6. Supported and Unsupported Faults on Intel® Xeon Phi™ Coprocessor                | 24  |

| Table 2-7: Core PMU Instructions                                                           | 25  |

| Table 2-8. Core PMU Control Registers                                                      | 25  |

| Table 2-9. Examples of Base Address Ranges Based on Descriptor Ring Size                   | 31  |

| Table 2-10. Coprocessor Memory Map                                                         | 32  |

| Table 2-11. LSB Core Libraries                                                             |     |

| Table 2-12. Intel® MIC Architecture commands                                               | 50  |

| Table 2-13. Kernel to User Space Mappings                                                  | 50  |

| Table 2-14. SYSFS Nodes                                                                    | 51  |

| Table 2-15: Vendor Drivers Bypassing IB* Core for User-Mode Access                         | 55  |

| Table 2-16: Summary of Vendor Driver Characteristics                                       | 56  |

| Table 3-1. Routines Common to All Package Idle States                                      | 77  |

| Table 3-2 Package Idle State Behavior in the Intel® Xeon Phi™ Coprocessor                  | 78  |

| Table 3-3. Events and Conditions Handled by the Coprocessor OS                             |     |

| Table 3-4. Power Management Messages                                                       | 88  |

|                                                                                            |     |

| Table 3-5. Control and Error Reporting Registers                                              | 98  |

|-----------------------------------------------------------------------------------------------|-----|

| Table 3-6. MCi_CTL Register Description                                                       | 98  |

| Table 3-7. MCI_STATUS Register Description                                                    | 99  |

| Table 3-8. MCi_ADDR Register Description                                                      | 100 |

| Table 3-9. Machine Check Registers                                                            | 100 |

| Table 3-10. Sources of Uncore Machine-Check Events                                            | 103 |

| Table 3-11. SBox Machine Check Registers                                                      | 103 |

| Table 3-12. SBox Error Descriptions                                                           | 104 |

| Table 3-13. Correctable PCIe Fabric Error Signal                                              | 106 |

| Table 3-14. Uncorrectable PCIe Fabric Error Signal                                            | 106 |

| Table 3-15. GBox Errors                                                                       | 106 |

| Table 3-16. TD Errors                                                                         | 107 |

| Table 3-17. GBox Error Registers                                                              | 108 |

| Table 5-1 Summary of SCIF Functions                                                           |     |

| Table 5-2. MicAccessAPI Library APIs                                                          | 125 |

| Table 5-3. Intel® Xeon Phi™ Coprocessor Command Utilities                                     | 126 |

| Table 7-1 Bidirectional Up/Down Conversion Table                                              |     |

| Table 7-2 Throughput Cycle of Transcendental Functions                                        | 137 |

| Table 7-3. The Scale-and-Bias Instruction vfmadd233ps on 32-bit Data                          | 140 |

| Table 7-4. The vmovaps Instruction Support for Data Conversion and Data Replication Modifiers | 158 |

| Table 7-5. The Floating-Point Data Type Encodings Supported                                   | 159 |

| Table 7-6: Memory Alignment Requirements for Load and Store Operations                        | 160 |

| Table 7-7. L1 Prefetch Instructions                                                           | 164 |

| Table 7-8. L2 Prefetch Instructions                                                           | 165 |

| Table 7-9. Mask Manipulation Instructions                                                     | 165 |

| Table 7-10. Packed Typeless Instructions                                                      | 166 |

| Table 7-11. New Packed DP FP Instructions                                                     | 167 |

| Table 7-12. Packed Int32 Instructions                                                         | 168 |

#### 1 Introduction

#### 1.1 Programming Model

As with most computing systems, the Intel® Many Integrated Core (Intel® MIC) Architecture programming model can be divided into two categories: application programming and system programming.

#### 1.1.1 Application Programming

In this guide, application programming refers to developing user applications or codes using either the Intel® Composer XE 2013 or 3<sup>rd</sup> party software development tools. These tools typically contain a development environment that includes compilers, libraries, and assorted other tools.

Application programming will not be covered here; consult the Intel® Xeon Phi™ Coprocessor DEVELOPER'S QUICK START GUIDE for information on how to quickly write application code and run applications on a development platform including the Intel® Many Integrated Core Architecture (Intel® MIC Architecture). It also describes the available tools and gives some simple examples to show how to get C/C++ and Fortran-based programs up and running.

The development environment includes the following compilers and libraries, which are available at <a href="https://registrationcenter.intel.com">https://registrationcenter.intel.com</a>:

- Intel® C/C++ Compiler XE 2013 including Intel® MIC Architecture for building applications that run on Intel® 64 and Intel® MIC Architectures

- Intel® Fortran Compiler XE 2013 including Intel® MIC Architecture for building applications that run on Intel® 64 and Intel® MIC Architectures

Libraries for use with the offload compiler include:

- Intel® Math Kernel Library (Intel® MKL) optimized for Intel® MIC Architecture

- Intel® Threading Building Blocks

The development environment includes the following tools:

- Debugger

- Intel® Debugger for applications including Intel® MIC Architecture

- Intel® Debugger for applications running on Intel® Architecture (IA)

- .

- Profiling

- SEP enables performance data collection from the Intel® Xeon Phi<sup>™</sup> coprocessor. This feature is included as part of the VTune<sup>™</sup> Amplifier XE 2013 tool.

- Performance data can be analyzed using VTune™ Amplifier XE 2013

#### 1.1.2 System Programming

System programming here explains how to use the Intel® MIC Architecture, its low level APIs (e.g. SCIF), and the contents of the Intel® Many Integrated Core Architecture Platform Software Stack (MPSS). Detailed information on these low-level APIs can be found in Section 5 of this document.

#### 1.2 Section Overview

The information in this guide is organized as follows:

- Section 2 contains a high-level description of the Intel® Xeon Phi™ coprocessor hardware and software architecture.

- Section Error! Reference source not found. covers power management from the software perspective. It also covers virtualization support in the Intel® Xeon Phi™ coprocessor and some Reliability Accessibility and Serviceability (RAS) features such as BLCR\* and MCA.

- Section 4 covers Operating System support.

- Section 5 covers the low level APIs (e.g. SCIF) available with the Intel® Xeon Phi™ coprocessor software stack.

- Section 6 illustrates the usage models and the various operating modes for platforms with the Intel<sup>®</sup> Xeon Phi™ coprocessors in the compute continuum.

- Section 7 provides in-depth details of the Intel® Xeon Phi™ coprocessor Vector Processing Unit architecture.

- Glossary of terms and abbreviations used can be found in Section 8.

- References are collated in Section 9.

#### 1.3 Related Technologies and Documents

This section lists some of the related documentation that you might find useful for finding information not covered here.

Industry specification for standards (i.e., OpenMP\*, OpenCL\*, MPI, OFED\*, and POSIX\* threads) are not covered in this document. For this information, consult relevant specifications published by their respective owning organizations:

Technology Location

OpemMP\* <a href="http://openmp.org/">http://openmp.org/</a>

OpenCL\* <a href="http://www.khronos.org/opencl/">http://www.khronos.org/opencl/</a>

MPI <a href="http://www.mpi-forum.org/">http://www.mpi-forum.org/</a>

OFED\* Overview <a href="http://www.openfabrics.org/">http://www.openfabrics.org/</a>

**Table 1-1. Related Industry Standards**

You should also consult relevant published documents which cover the Intel® software development tools not covered here:

**Table 1-2. Related Documents**

| Document                                                  | Location                                      |

|-----------------------------------------------------------|-----------------------------------------------|

| Intel® Xeon Phi™ Coprocessor DEVELOPER'S QUICK START      | http://software.intel.com/en-us/mic-developer |

| GUIDE                                                     |                                               |

| Intel® Many Integrated Core Platform Software Stack       | http://software.intel.com/en-us/mic-developer |

| Intel® Xeon Phi™ Coprocessor Instruction Set Architecture | http://software.intel.com/en-us/mic-developer |

| Reference Manual                                          |                                               |

| An Overview of Programming for Intel® Xeon® processors    | http://software.intel.com/en-us/mic-developer |

| and Intel® Xeon Phi™ coprocessors                         |                                               |

| Debugging Intel® Xeon Phi™ Coprocessor: Command-Line      | http://software.intel.com/en-us/mic-developer |

| Debugging                                                 |                                               |

| Building Native Applications for Intel® Xeon Phi™         | http://software.intel.com/en-us/mic-developer |

| Coprocessor                                               |                                               |

| Programming and Compiling for Intel® Many Integrated      | http://software.intel.com/en-us/mic-developer |

| Core Architecture                                         |                                               |

| Document                                                 | Location                                      |

|----------------------------------------------------------|-----------------------------------------------|

| Intel® Xeon Phi™ coprocessor Micro-architecture Software | http://software.intel.com/en-us/mic-developer |

| Stack                                                    |                                               |

| Intel® Xeon Phi™ coprocessor Micro-architecture Overview | http://software.intel.com/en-us/mic-developer |

| Intel® MPI Library                                       | http://www.intel.com/go/mpi                   |

| Intel® MIC SCIF API Reference Manual for Kernel Mode     | http://intel.com/software/mic                 |

| Linux*                                                   |                                               |

| Intel® MIC SCIF API Reference Manual for User Mode       | http://intel.com/software/mic                 |

| Linux*                                                   |                                               |

## 2 Intel® Xeon Phi™ Coprocessor Architecture

This Section explains both the hardware and the software architecture of the Intel® Xeon Phi™ coprocessor. It covers the major micro-architectural features such as the core, the vector processing unit (VPU), the high-performance on-die bidirectional interconnect, fully coherent L2 caches, and how the various units interact. Particular emphasis is placed on the key parameters necessary to understand program optimization, such as cache organization and memory bandwidth.

#### 2.1 Intel® Xeon Phi™ Coprocessor Architecture

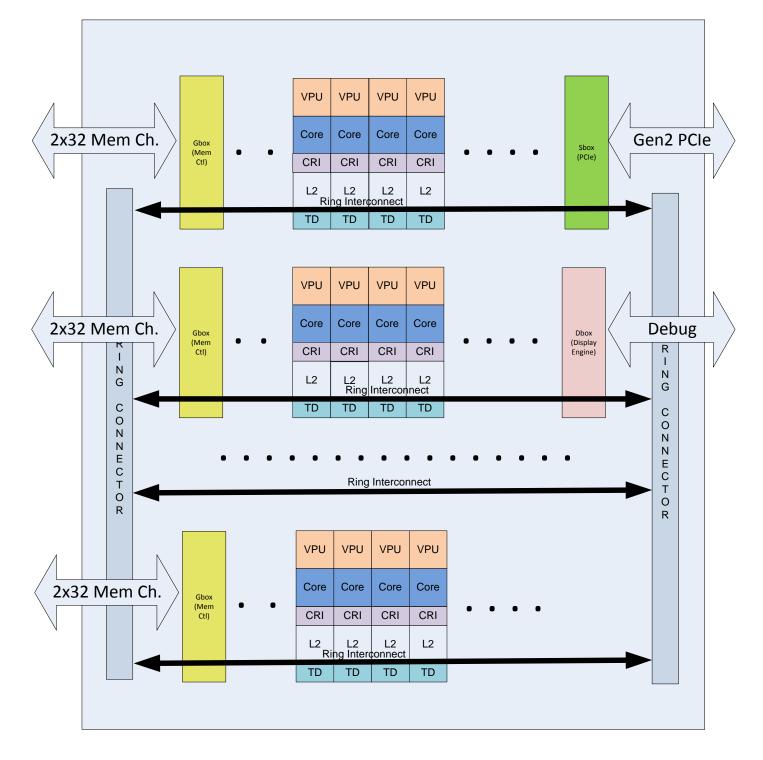

The Intel® Xeon Phi™ coprocessor comprises of up to sixty-one (61) processor cores connected by a high performance on-die bidirectional interconnect. In addition to the IA cores, there are 8 memory controllers supporting up to 16 GDDR5 channels delivering up to 5.5 GT/s, and special function devices such as the PCI Express\* system interface.

Each core is a fully functional, in-order core, which supports fetch and decode instructions from four hardware thread execution contexts. In order to reduce hot-spot contention for data among the cores, a distributed tag directory is implemented so that every physical address the coprocessor can reach is uniquely mapped through a reversible one-to-one address hashing function. This hashing function not only maps each physical address to a tag directory, but also provides a framework for more elaborate coherence protocol mechanisms than the individual cores could provide.

Each memory controller is based on the GDDR5 specification, and supports two channels per memory controller. At up to 5.5 GT/s transfer speed, this provides a theoretical aggregate bandwidth of 352 GB/s (gigabytes per second) directly connected to the Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessor.

At a high level, Intel® Xeon Phi™ coprocessor silicon is consists of up to 61 dual-issue in-order cores, where each core includes:

- 512 bit wide vector processor unit (VPU)

- The Core Ring Interface (CRI)

- Interfaces to the Core and the Ring Interconnect

- The L2 Cache (including the tag, state, data and LRU arrays) and the L2 pipeline and associated arbitration logic

- The Tag Directory (TD) which is a portion of the distributed duplicate tag directory infrastructure

- Asynchronous Processor Interrupt Controller (APIC) which receives interrupts (IPIs, or externally generated) and must redirect the core to respond in a timely manner.

- Memory controllers (GBOX), which access external memory devices (local physical memory on the coprocessor card) to read and write data. Each memory controller has 2 channel controllers, which together can operate two 32-bit memory channels.

- A Gen2 PCI Express\* client logic (SBOX), which is the system interface to the host CPU or PCI Express\* switch, supporting x8 and x16 configurations.

- The Ring Interconnect connecting all of the aforementioned components together on the chip.

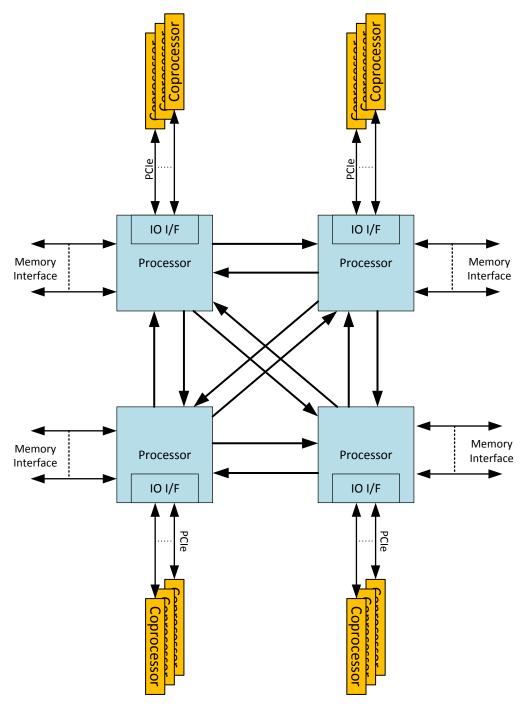

Figure 2-1. Basic building blocks of the Intel® Xeon Phi™ Coprocessor

| able 2-1 gives a high-level description of each component. |         |  |

|------------------------------------------------------------|---------|--|

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            |         |  |

|                                                            | Page 15 |  |

**Table 2-1. Description of Coprocessor Components**

| Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Core   | The processor core. It fetches and decodes instructions from four hardware thread execution contexts. It supports a 32-bit and 64-bit execution environment similar to those found in the Intel64® Intel® Architecture Software Developer's Manual, along with the Intel Initial Many Core Instructions It contains a 32KB, 8-Way set associative L1 Icache and Dcache, and interfaces with the CRI/L2 block to request access to memory. The core can execute 2 instructions per clock cycle, one on the U-pipe, and one on the V-pipe. The V-pipe cannot execute all instruction types, and simultaneous execution is governed by pairing rules. The core does not support Intel® Streaming SIMD Extensions (Intel® SSE) or MMX™ instruction execution. |

| VPU    | The Vector Processor Unit includes the EMU (extended math unit) and executes 16 single-precision floating point, 16 32bit integer operations per clock cycle, or 8 double-precision floating-point operations per cycle. Each operation can be a floating-point multiply-add, giving 32 single precision floating-point operations per cycle. The VPU contains the vector register file (32 registers per thread context), and can read one of its operands directly from memory, including data format conversion on the fly. Broadcast and swizzle instructions are also available. The EMU can perform base-2 exponential, base-2 logarithm, reciprocal, and reciprocal square root of single precision floating-point values.                         |

| L2/CRI | The Core-Ring Interface hosts the 512KB, 8-way, L2 cache and connects each core to an Intel® Xeon Phi™ coprocessor Ring Stop. Primarily, it comprises the core-private L2 cache itself plus all of the off-core transaction tracking queues and transaction / data routing logic. Two other major blocks also live in the CRI: the R-Unit (APIC) and the Tag Directory (TD).                                                                                                                                                                                                                                                                                                                                                                              |

| TD     | Distributed duplicate tag directory for cross-snooping L2 caches in all cores. The CPU L2 caches are kept fully coherent with each other by the TDs, which are referenced after an L2 cache miss. A TD tag contains the address, state, and an ID for the owner (one of the L2 caches) of the cache line. The TD that is referenced is not necessarily the one co-located with the core that generated the miss, but is based upon address (each TD gets an equal portion of the address space). A request is sent from the core that suffered the memory miss to the correct TD via the ring interconnect.                                                                                                                                               |

| GBOX   | The Intel® Xeon Phi™ coprocessor memory controller comprises three main units: the FBOX (interface to the ring interconnect), the MBOX (request scheduler) and the PBOX (physical layer that interfaces with the GDDR devices). The MBOX comprises two CMCs (or Channel Memory Controllers) that are completely independent from each other. The MBOX provides the connection between agents in the system and the DRAM I/O block. It is connected to the PBOX and to the FBOX. Each CMC operates independently from the other CMCs in the system.                                                                                                                                                                                                        |

| SBOX   | PCI Express* client logic: DMA engine, limited power management capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ring   | Ring Interconnect, including component interfaces, ring stops, ring turns, addressing, and flow control. Intel® Xeon Phi™ coprocessor has 2 each of these rings — one travelling each direction. There is no queuing on the ring or in the ring turns; once a message is on the ring it will continue deterministically to its destination. In some cases, the destination does not have room to accept the message and may leave it on the ring and pick it up the next time it goes by. This is known as bouncing.                                                                                                                                                                                                                                      |

| Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PBOX  | The PBOX is the analog interface component of the GBOX that communicates with the GDDR memory device. Besides the analog blocks, the PBOX contains the input/output FIFO buffers, part of the training state machines and mode registers to trim the analog interface. The analog interface consists of the actual I/O pads for DQs, Address and Command and the clocking structure. The PBOX also includes the GPLL which defines the clock domain for each PBOX and the respective MBOX/CBOX.                                                                                                                                                                                                                                                                                                                                                    |

| PMU   | Performance Monitoring Unit. This performance monitoring feature allows data to be collected from all units in the architecture, utilizing a P6-style programming interface to configure and access performance counters. Implements an Intel® Xeon Phi™ coprocessor SPFLT which allows user-level code to filter the core events that its thread generates. Does not implement some advanced features found in mainline IA cores (e.g. precise event-based sampling, etc.).                                                                                                                                                                                                                                                                                                                                                                       |

| Clock | The clock generation on Intel® Xeon Phi™ coprocessor supplies clocks to each of the four main clock domains. The core domain supports from 600 MHz to the part's maximum frequency in steps of 25 MHz Ratio changes in the core happen seamlessly and can be controlled through both software and internal hardware (using information from the thermal and current sensors on the card.) The GDDR supports frequencies that enable between 2.8 GT/s and the part's maximum frequency with a minimum step size of 50 MT/s. Intel® Xeon Phi™ coprocessors support frequency changes without requiring a reset. PCI Express* clock modes support both Gen1 and Gen2 operation. The external clock buffer has been incorporated into the Intel® Xeon Phi™ coprocessor die, and the clocks are sourced from two 100 MHz PCI Express* reference clocks. |

#### 2.1.1 Core

Each in-order execution core provides a 64 bit execution environment similar to that found in the Intel64® Intel® Architecture Software Developer's Guide, in addition to introducing support for Intel Initial Many Core Instructions. There is no support for MMX™ instructions, Intel Advanced Vector Extensions (Intel® AVX), or any of the Intel® Streaming SIMD Extensions (Intel® SSE). A full list of the instructions supported by the Intel® Xeon Phi™ coprocessor can be found in the following document (Intel® Xeon Phi™ Coprocessor Instruction Set Architecture Reference Manual (Reference Number: 327364)). New vector instructions provided by the Intel® Xeon Phi™ Coprocessor Instruction Set utilize a dedicated 512-bit wide vector floating-point unit (VPU) that is provided for each of the cores.

Each core is connected to a Ring Interconnect via the Core Ring Interface (CRI), which is comprised of the L2 cache control and the Tag Directory (TD). The Tag Directory contains the tags for a portion of the overall L2 cache. The Core and L2 Slices are interconnected on a ring based interconnect along with additional ring agents on the die. Each agent on the ring, whether a core/L2 Slice, memory controller, or the system (SBOX), implements a ring stop that enables requests and responses to be sent on the ring bus.

The core can execute 2 instructions per clock cycle, one on the U-pipe and one on the V-pipe. The V-pipe cannot execute all instruction types, and simultaneous execution is governed by pairing rules. Vector instructions can only be executed on the U-pipe.

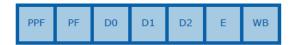

# **Core Pipeline**

| PPF | Thread picker<br>Instruction cache lookup<br>Prefetch buffer write           |    | Microcode control execution<br>Address generation<br>Data cache lookup<br>Register file read |  |

|-----|------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------|--|

| PF  |                                                                              |    |                                                                                              |  |

| D0  | Thread picker<br>Instruction rotate<br>Decode of 0f, 62, D6, REX<br>prefixes | Е  | Integer ALU execution<br>Retire/stall/exception<br>determination                             |  |

| D1  | Instruction Decode<br>CROM lookup<br>Sunit register file read                | WB | Integer register file write<br>Condition code (flag)<br>evaluation                           |  |

**Figure 2-2: Core Pipeline Components**

Figure 2-3: Intel® Xeon Phi™ Coprocessor Core Architecture

Most integer and mask instructions have a 1-clock latency, while most vector instructions have 4-clock latency with a 1 clock throughput. Dependent store- to-load latency is 4 clocks for simple vector operations. "Shuffles" and "Swizzles" increase this latency. The store-to-load penalty for the L1 is approximately 12 clocks. Kunit (data cache) bounces cause 2 dead clocks (bank conflicts, U-pipe/V-pipe conflicts with higher-priority replacements, invalidations). Prefix decodes are available with 0-cycle "fast": 62, c4, c5, REX, 0f, and a 2-cycle "slow": operand size 66, address size 67, lock, segment, REP.

#### 2.1.2 Instruction Decoder

One of the changes made to simplify the core was to modify the instruction decoder to be a two-cycle unit. While fully pipelined, the result of this change is that the core cannot issue instructions from the same hardware context in back-to-back cycles. That is, if in cycle N the core issued instructions from context 1, then in cycle N +1 the core can issue instructions from any context except context 1. This allows for a significant increase in the maximum core frequency, resulting in a net performance gain even for single-threaded SPEC\* benchmarks.

For maximum chip utilization, at least two hardware contexts or threads must be run on each core. Since the scheduler cannot issue instructions in back-to-back cycles from the same hardware context, running one thread on a core will result in, at best, 50% utilization of the core potential.

#### 2.1.3 Cache Organization and Hierarchy

The Level One (L1) cache accommodates higher working set requirements for four hardware contexts per core. It has a 32 KB L1 instruction cache and 32 KB L1 data cache. Associativity was increased to 8-way, with a 64 byte cache line. The bank width is 8 bytes. Data return can now be out-of-order. The L1 cache has a load-to-use latency of 1 cycle -- an integer value loaded from the cache can be used in the next clock by an integer instruction. Note, however, that vector instructions experience different latencies than integer instructions. The L1 cache has an address generation interlock with at least a 3-clock cycle latency. A GPR register must be produced three or more clocks prior to being used as a base or index register in an address computation. The register set-up time for base and index has the same 3-clock cycle latency.

Another new feature is the 512 KB unified Level Two (L2) cache unit. The L2 organization comprises 64 bytes per way with 8-way associativity, 1024 sets, 2 banks, 32GB (35 bits) of cacheable address range and a raw latency of 11 clocks. The expected idle access time is approximately 80 cycles. The L2 cache has a streaming hardware prefetcher that can selectively prefetch code, read, and RFO (Read-For-Ownership) cache lines into the L2 cache. There are 16 streams that can bring in up to a 4-KB page of data. Once a stream direction is detected, the prefetcher can issue up to 4 multiple prefetch requests. The L2 in Intel® Xeon Phi™ coprocessor supports ECC, and power states such as the core C1 (shuts off clocks to the core and the VPU), C6 (shuts off clocks and power to the core and the VPU), and the package C3 states. The replacement algorithm for both the L1 and L2 caches is based on a pseudo-LRU implementation.

The L2 cache is part of the Core-Ring Interface block. This block also houses the tag directory (TD) and the Ring Stop (RS), which connects to the interprocessor core network. Within these sub-blocks is the Transaction Protocol Engine which is an interface to the RS and is equivalent to a front side bus unit. The RS handles all traffic coming on and off the ring. The TDs, which are physically distributed, filter and forward requests to appropriate agents on the ring. They are also responsible for initiating communications with the GDDR5 memory via the on-die memory controllers.

In the in-order Intel® Pentium® processor design, any miss to the cache hierarchy would be a core-stalling event such that the program would not continue executing until the missing data were fetched and ready for processing. In the Intel® Xeon Phi™ coprocessor cores, a miss in the L1 or L2 cache does not stall the entire core. Misses to the cache will not stall the requesting hardware context of a core unless it is a load miss. Upon encountering a load miss, the hardware context with the instruction triggering the miss will be suspended until the data are brought into the cache for processing. This allows the other hardware contexts in the core to continue execution. Both the L1 and L2 caches can also support up to about 38 outstanding requests per core (combined read and write). The system agent (containing the

PCI Express\* agent and the DMA controller) can also generate 128 outstanding requests (read and write) for a total of 38\*(number of cores) + 128. This allows software to prefetch data aggressively and avoids triggering a dependent stall condition in the cache. When all possible access routes to the cache are in use, new requests may cause a core stall until a slot becomes available.

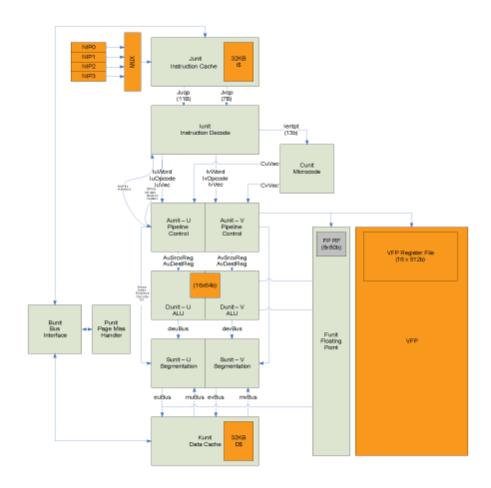

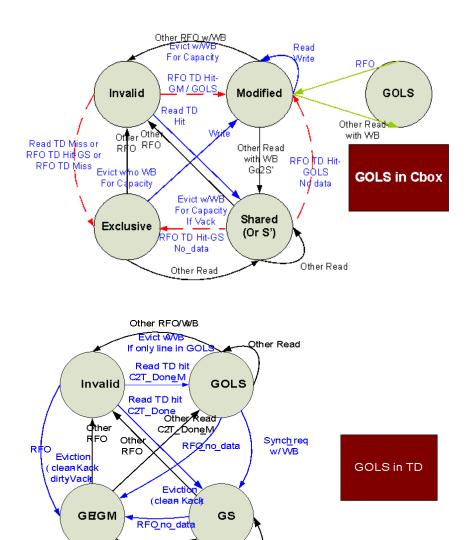

Both the L1 and L2 caches use the standard MESI protocol for maintaining the shared state among cores. The normal MESI state diagram is shown in Figure 2-4 and the cache states are listed in Table 2-2. L2 Cache States.

Figure 2-4: MESI Protocol

Table 2-2. L2 Cache States

| L2 Cache State | State Definition                                                                                                                                                      |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| М              | Modified. Cacheline is updated relative to memory (GDDR). Only one core may have a given line in M-state at a time.                                                   |  |  |

| Е              | Exclusive. Cacheline is consistent with memory. Only one core may have a given line in E-state at a time.                                                             |  |  |

| S              | Shared. Cacheline is shared and consistent with other cores, but may not be consistent with memory. Multiple cores may have a given line in S-state at the same time. |  |  |

| I I            | Invalid. Cacheline is not present in this core's L2 or L1.                                                                                                            |  |  |

To address potential performance limitations resulting from the lack of an O (Owner) state found in the MOESI protocol, the Intel® Xeon Phi™ coprocessor coherence system has an ownership tag directory (TD) similar to that implemented in many multiprocessor systems. The tag directory implements the GOLS3 protocol. By supplementing the individual core MESI protocols with the TD's GOLS protocol, it becomes possible to emulate the missing O-state and to achieve the benefits of the full MOESI protocol without the cost of redesigning the local cache blocks. The TD is also useful for controlling other behaviors in the Intel® Xeon Phi™ coprocessor design and is used for more than this emulation behavior. The modified coherence diagrams for the core MESI protocol and the tag directory GOLS protocol are shown in Figure 2-5.

Figure 2-5 Globally Owned Locally Shared (GOLS) Diagram

Other Read C2T\_Done Other Read

**Table 2-3. Tag Directory States**

| Tag Directory State | State Definition                                                                                                                                                                                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GOLS                | Globally Owned, Locally Shared. Cacheline is present in one or more cores, but is not consistent with memory.                                                                                           |

| GS                  | Globally Shared. Cacheline is present in one or more cores and consistent with memory.                                                                                                                  |

| GE/GM               | Globally Exclusive/Modified. Cacheline is owned by one and only one core and may or may not be consistent with memory. The Tag Directory does not know whether the core has actually modified the line. |

| GI                  | Globally Invalid. Cacheline is not present in any core.                                                                                                                                                 |

The tag directory is not centralized but is broken up into 64 distributed tag directories (DTDs). Each DTD is responsible for maintaining the global coherence state in the chip for its assigned cache lines. The basic L1 and L2 cache parameters are summarized in Table 2-4. Two unusual fields in this table are the Duty Cycle and Ports designations, which are specific only to the Intel® Xeon Phi™ coprocessor design. The L1 cache can be accessed each clock, whereas the L2 can only be accessed every other clock. Additionally, on any given clock software can either read or write the L1 or L2, but it cannot read and write in the same clock. This design artifact has implications when software is trying to access a cache while evictions are taking place.

Table 2-4. Cache Hierarchy

| Parameter     | L1            | L2            |

|---------------|---------------|---------------|

| Coherence     | MESI          | MESI          |

| Size          | 32 KB + 32 KB | 512 KB        |

| Associativity | 8-way         | 8-way         |

| Line Size     | 64 bytes      | 64 bytes      |

| Banks         | 8             | 8             |

| Access Time   | 1 cycle       | 11 cycles     |

| Policy        | pseudo LRU    | pseudo LRU    |

| Duty Cycle    | 1 per clock   | 1 per clock   |

| Ports         | Read or Write | Read or Write |

The L2 cache organization per core is inclusive of the L1 data and instruction caches. How all cores work together to make a large, shared, L2 global cache (up to 31 MB) may not be clear at first glance. Since each core contributes 512 KB of L2 to the total shared cache storage, it may appear as though a maximum of 31 MB of common L2 cache is available. However, if two or more cores are sharing data, the shared data is replicated among the individual cores' various L2 caches. That is, if no cores share any data or code, then the effective total L2 size of the chip is 31 MB. Whereas, if every core shares exactly the same code and data in perfect synchronization, then the effective total L2 size of the chip is only 512 KB. The actual size of the workload-perceived L2 storage is a function of the degree of code and data sharing among cores and thread.

A simplified way to view the many cores in Intel® Xeon Phi™ coprocessor is as a chip-level symmetric multiprocessor (SMP). Each core acts as a stand-alone core with 512 KB of total cache space, and up to 62 such cores share a high-speed interconnect on-die. While not particularly accurate compared to a real SMP implementation, this simple mental model is useful when considering the question of how much total L2 capacity may be used by a given workload on the Intel® Xeon Phi™ coprocessor card.

#### 2.1.4 Page Tables

The Intel® Xeon Phi™ coprocessor supports 32-bit physical addresses in 32-bit mode, 36-bit physical address extension (PAE) in 32-bit mode, and 40-bit physical address in 64-bit mode.

It supports 4-KB and 2-MB page sizes. It also supports the Execute Disable (NX) bit. But there is no support for the Global Page bit, unlike other Intel® Architecture microprocessors. On a TLB miss, a four-level page table walk is performed as usual, and the INVLPG instruction works as expected. The advantage of this approach is that there are no restrictions for mixing the page sizes (4 KB, 2MB) within a single address block (2MB). However, undefined behavior will occur if the 16 underlying 4-KB page-table entries are not consistent.

Each L1 data TLB (dTLB) has 64 entries for 4 KB pages and 8 entries for 2MB pages. Each core also has one instruction TLB (iTLB), which only has 32 entries for 4 KB pages. No support for larger page sizes is present in the instruction TLB. For L2, the 4-way dTLB has 64 entries, usable as second-level TLB for 2M pages or as a page directory entry (PDE) cache for

4K. TLBs can share entries among threads that have the same values for the following registers: CR3, CR0.PG, CR4.PAE, CR4.PSE, EFER.LMA.

| Tahla 2-5  | I1 and  | 12 Caches  | Characteristics |

|------------|---------|------------|-----------------|

| Table 2-5. | LI allu | LZ Caciles | CHALACTERISTICS |

|                    | Page Size | Entries | Associativity | Maps |

|--------------------|-----------|---------|---------------|------|

| L1 Data TLB        | 4K        | 64      | 4-way         | 256K |

| LI Dala ILD        | 2M        | 8       | 4-way         | 16M  |

| L1 Instruction TLB | 4K        | 32      | 4-way         | 128K |

| L2 TLB             | 4K, 2M    | 64      | 4-way         | 128M |

The Intel® Xeon Phi™ coprocessor core implements two types of memory: uncacheable (UC) and write-back (WB). The other three memory forms [write-through (WT), write-combining (WC), and write-protect (WP)] are mapped internally to microcontroller behavior. No other memory type is legal or supported.

#### 2.1.5 Hardware Threads and Multithreading

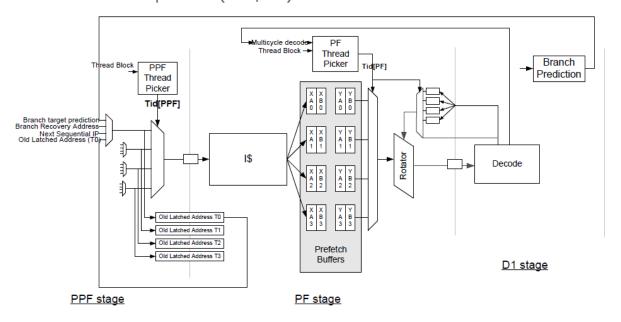

Figure 2-6 presents a high-level view of the major impacts for hardware multithreading support, such as architectural, pipeline, and cache interactions. This includes replicating complete architectural state 4 times: the GPRs, ST0-7, segment registers, CR, DR, EFLAGS, and EIP. Certain micro-architectural states are also replicated four times like the prefetch buffers, the instruction pointers, the segment descriptors, and the exception logic. "Thread specific" changes include adding thread ID bits to shared structures (iTLB, dTLB, BTB), converting memory stall to thread-specific flush, and the introduction of thread wakeup/sleep mechanisms through microcode and hardware support. Finally, the Intel® Xeon Phi™ coprocessor implements a "smart" round-robin multithreading.

# Multithreading

Time-multiplexed multithreading

Add two thread pickers (PPF, PF)

Figure 2-6. Multithreading Architectural Support in the Intel® Xeon Phi™ Coprocessor

Each of four hardware threads shown above in the grey shaded region has a "ready to run" buffer consisting of two instruction bundles. Since each core is capable of issuing two instructions per clock cycle, each bundle represents two

instructions. If the executing thread has a control transfer to a target that is not contained in this buffer, it will trigger a miss to the instruction cache, which flushes the context buffer and loads the appropriate target instructions. If the instruction cache does not have the control transfer point, a core stall will be initiated, which may result in performance penalties. In general, whichever hardware context issues instructions in a given clock cycle has priority for fetching the next instruction(s) from the instruction cache. Another significant function is the picker function (PF) that chooses the next hardware context to execute. The PF behaves in a round-robin manner, issuing instructions during any one clock cycle from the same hardware context only. In cycle N, if the PF issues instruction(s) from Context 3, then in cycle N + 1 the PF will try to issue instructions from Context 0, Context 1, or Context 2 – in that order. As previously noted it is not possible to issue instructions from the same context (Context 3 in this example) in back-to-back cycles.

#### 2.1.6 Faults and Breakpoints

The Intel® Xeon Phi™ coprocessor supports the fault types shown in Table 2-6 below. For complete details of fault behavior, please consult the (Intel® 64 and IA-32 Architectures Software Developer Manuals).

Breakpoint support required the widening of DRO-DR3 for Intel® 64 instruction compatibility and is now for 1, 2, 4, or 8 bytes. The length was not extended to support 16, 32, or 64 bytes. Also, breakpoints in the Intel® Xeon Phi™ coprocessor instructions occur regardless of any conditional execution status indicated by mask registers.

| Fault Type Supported |                                                  | Comments                                                                               |

|----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|

| #PF                  | Yes                                              | Page Fault                                                                             |

| #SS                  | Yes For non-canonical and referencing SS segment |                                                                                        |

| #GP                  | Yes                                              | Address is not canonical or not aligned to operand size                                |

| #UD                  | Yes                                              | If CRO.EM[2] = 1, or LOCK or REX prefix used; also triggered on IN or OUT instructions |

| #XF                  | No                                               | No unmasked exceptions in SIMD                                                         |

| #AC                  | No                                               | GP fault always takes priority                                                         |

| #NM No CR0.TS[3] = 1 |                                                  | CR0.TS[3] = 1                                                                          |

Table 2-6. Supported and Unsupported Faults on Intel® Xeon Phi™ Coprocessor

#### 2.1.7 Performance Monitoring Unit and Events Monitor

The Intel® Xeon Phi™ coprocessor includes a performance monitoring unit (abbreviated as PMU) like the original Intel® Pentium® processor core. Most of the 42 event types from the original Intel® Pentium® processor exist, although the PMU interface has been updated to reflect more recent programming interfaces. Particular Intel® Xeon Phi™ coprocessor-centric events have been added to measure memory controller events, vector processing unit utilization and statistics, local and remote cache read/write statistics, and more.

The Intel® Xeon Phi™ coprocessor comes with support for performance monitoring at the individual core level. Each core has four performance counters, four filtered counters, and four event select registers. The events supported for performance monitoring are a combination of the legacy Intel® Pentium® processor events and new Intel® Xeon Phi™ coprocessor-centric events. Each core PMU is shared amongst all four hardware threads in that core. The PMU in each core is responsible for maintaining the time stamp counter (TSC) and counts hardware events generated by the core or triggered by events arriving at the core. By default, events are counted for all hardware contexts in the core, but the filters may be set to count only specific hardware context events. The core PMU also receives events from co-located units, including the ring stop, the distributed tag directory, and the core-ring interface.

The Intel® Xeon Phi™ coprocessor switched to the Intel® Pentium® Pro processor style of PMU interface, which allows user-space (ring three) applications to directly interface with and use the PMU features via specialized instructions such as RDPMC4. In this model, Ring 0 still controls the PMU but Ring 3 is capable of interacting with exposed features for optimization.

Table 2-7 lists the instructions used by Ring 0 and Ring 3 code used to control and query the core PMU.

**Table 2-7: Core PMU Instructions**

| Instruction<br>Name | Description                                                                                                                               | Privilege<br>Mode<br>(CPL) | Thread-<br>Specific | Input                                                    | Output                                          |

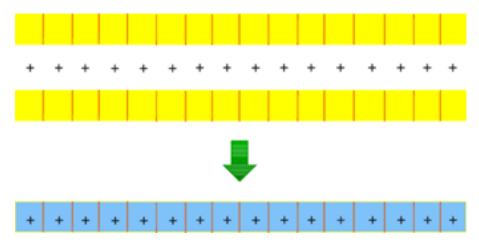

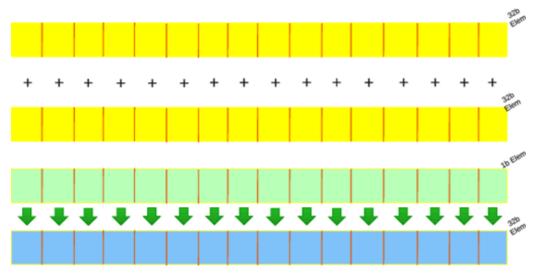

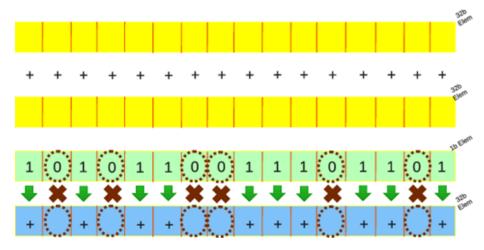

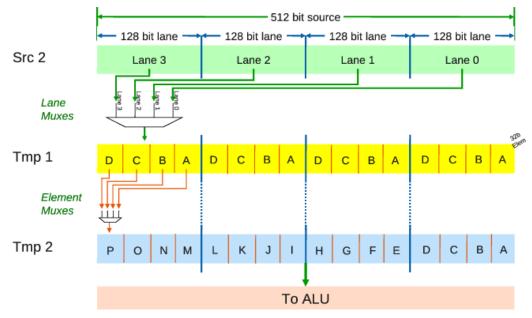

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|----------------------------------------------------------|-------------------------------------------------|