Last updated 2/22/21

These slides introduce VHDL based Register Files

Upon completion: You should be able design and use Register Files

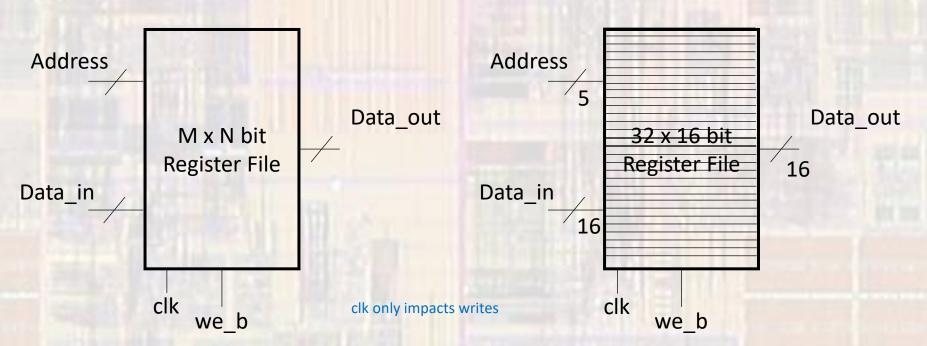

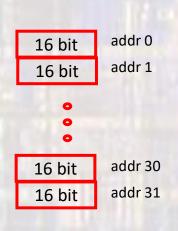

- Register File simple

- Group of n-bit registers

- Accessed via a multiplexor (address)

- Register File simple

- Output data (from reg at Address) always available

- Write requires we\_b low and clk ↑

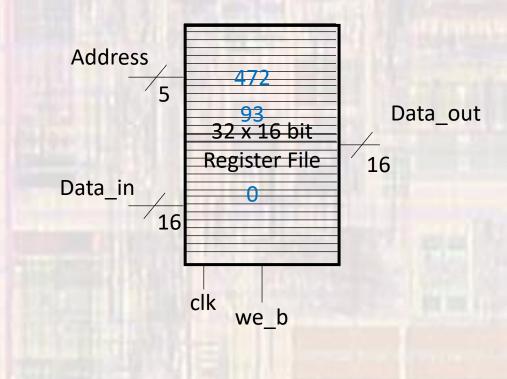

|         | we_b | addr | data_in | data_out |

|---------|------|------|---------|----------|

|         | 1    | 7    | 472     | ?        |

| clk ↑ → | 0    | 7    | 472     | ?        |

|         | 1    | 7    | 472     | 472      |

|         | 1    | 7    | 93      | 472      |

|         | 1    | 12   | 93      | ?        |

| clk ↑ → | 0    | 12   | 93      | 93       |

|         | 1    | 12   | 93      | ?        |

|         | 1    | 23   | 0       | ?        |

|         | 0    | 23   | 0       | 0        |

|         | 1    | 23   | 0       | 472      |

|         | 1    | 7    | 55      | 93       |

|         | 1    | 12   | 55      |          |

clk only required for writes, reads are asynchronous

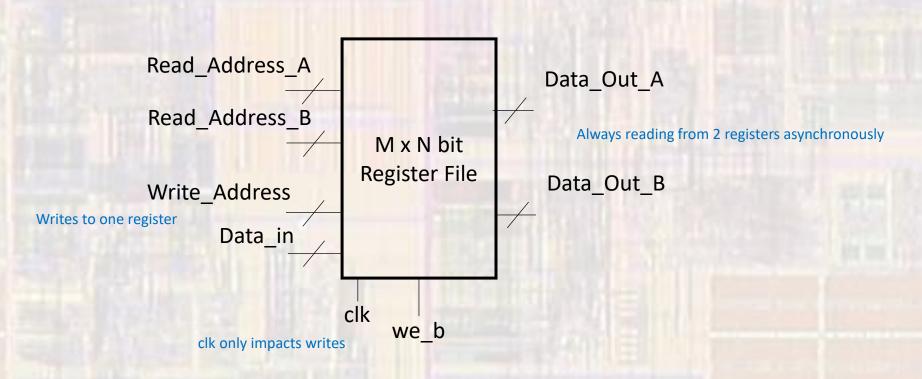

- Register File multi-port

- Group of n-bit registers

- Accessed via a multiplexor

- Can have multiple inputs and outputs

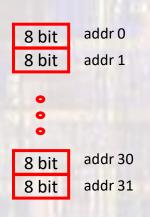

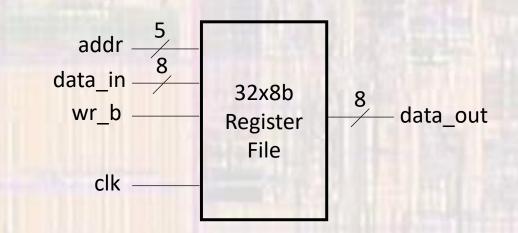

• 32 x 8 bit register file

• 32 x 8 bit register file

```

- reg_file_32x8b

- created by johnsontimoj

- 5/7/18

- rev 0

- Support for 32, 8 bit registers

- Support for 1 data outputs

- Support for 1 data input

- Inputs: clk, reg address, data in, we_bar

- Outputs: data out

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity reg_file_32x8b is

port (

i_clk:

in std_logic;

in std_logic_vector(4 downto 0); --32 registers

in std_logic_vector(7 downto 0); -- 8 bit data

i_addr:

i_data_in:

i_we_b:

in std_logic;

o_data_out:

out std_logic_vector(7 downto 0) -- 8 bit data

end entity;

```

#### • 32 x 8 bit register file

```

Create a new 'type'

The new 'type' is an array of std_logic_vector

```

```

arch tecture behavioral of reg_file_32x8b is

treate an "TYPE" for an array of 8 bit registers

type REG_FILE is array(0 to 31) of std_logic_vector(7 downto 0);

-- Create a signal of the array type

signal reg_32x8b: REG_FILE;

-- Special command to stop Quartus from inferring a RAM

-- Must also turn off assignments / settings / compiler settings/

-- adavanced settings (synthesis) / auto RAM replacement --> off

attribute ramstyle : string;

attribute ramstyle of reg_32x8b : signal is "logic";

Need the address as an integer to index the array.

begin

Address is SLV coming in – need to pass through

-- register logic

unsigned along the way

process(i_clk)

begin

if(rising_edge(i_clk)) then

if(i_we_b = '0') then

reg_32x8b(to_integer(unsigned(i_addr))) <= i_data_in;

end if:

end if:

end process;

-- output logic

process(all)

o_data_out <= reg_32x8b(to_integer(unsigned(i_addr)));

end process;

end behavioral:

```

**Numeric Std Conversions**

Numeric\_std.

Signed

Signed() Unsigned()

Unsigned

Function calls

To\_signed(,length)

To\_integer()

To\_integer()

To\_unsigned(,length)

Type conversions

Std\_logic\_vector()

Unsigned()

Signed()

Std logic 1164.

Arrays

Std logic vector

Std logic vector()

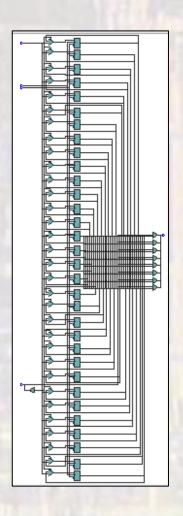

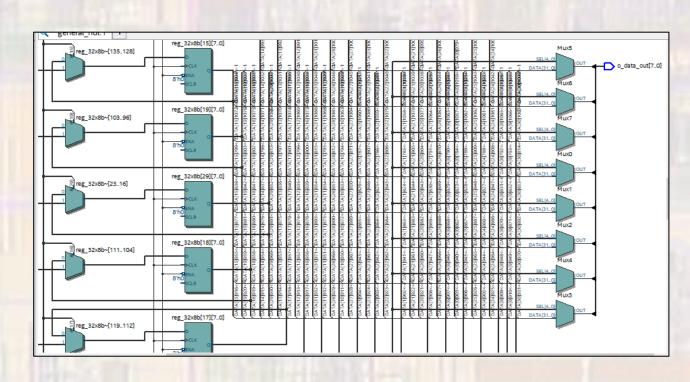

• 32 x 8 bit register file

• 32 x 8 bit register file - testbench

```

-- reg_file_32x8b_tb.vhdl

created: 3/18/18

-- by: johnsontimoj

-- rev: 0

-- testbench for 32 by 8 bit register file

-- of reg_file_32x8b.vhdl

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity reg_file_32x8b_tb is

-- no port entry - testbench

end entity;

architecture testbench of reg_file_32x8b_tb is

signal CLK: std_logic;

DATA_IN: std_logic_vector(7 downto 0);

ADDR: std_logic_vector(4 downto 0);

signal

signal

std_logic;

signal

WE_B:

DATA_OUT:std_logic_vector(7 downto 0);

constant PER: time := 20 ns;

```

```

-- Component prototype

component reg_file_32x8b is

i_clk:

in std_logic;

in std_logic_vector(4 downto 0); --32 registers

in std_logic_vector(7 downto 0); -- 8 bit data

i_addr:

i_data_in:

i_we_b:

out std_logic_vector(7 downto 0) -- 8 bit data

o_data_out:

):

end component:

begin

-- Device under test (DUT)

DUT: reg_file_32x8b

port map(

i_clk

=> CLK.

=> ADDR,

i_we_b

=> WE_B,

i_data_in => DATA_IN,

o_data_out => DATA_OUT

```

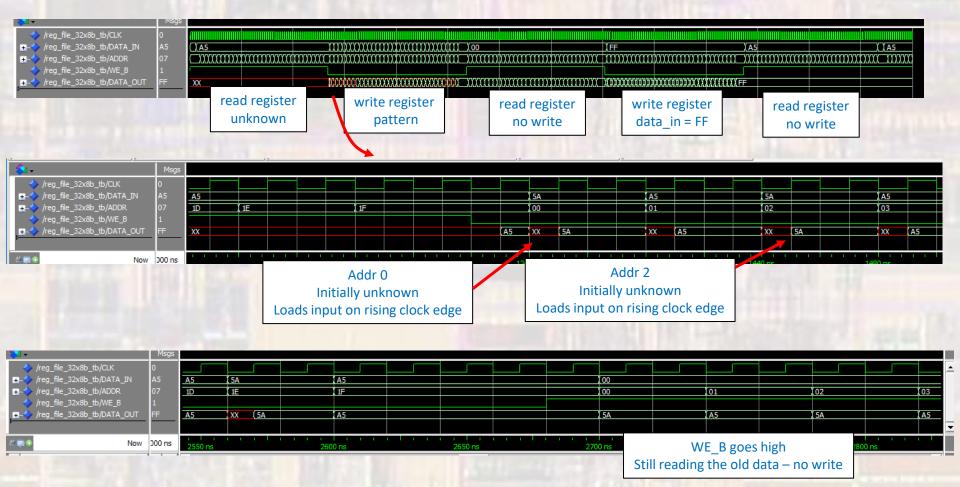

• 32 x 8 bit register file - testbench

```

-- Test processes

-- clock process

clock: process -- note - no sensitivity list allowed

CLK <= '0';

wait for PER/2;

infinite: loop

CLK <= not CLK; wait for PER/2;

end loop;

end process;

-- Reset process

-- no reset

-- Run Process

-- note - no sensitivity list allowed

run: process

-- initialize inputs

DATA_IN <= "00000000";

WE_B <= '1';

ADDR <= (others => '0');

-- read with no write prior - should be unknowns

wait for 2*PER;

WE_B <= '1';</pre>

wait for PER;

for i in 0 to 31 loop

ADDR <= std_logic_vector(to_unsigned(i, 5));

DATA_IN <= x"A5";

wait for 2*PER;

end loop;

-- write

WE_B <= '0':

wait for PER;

for i in 0 to 31 loop

ADDR <= std_logic_vector(to_unsigned(i, 5));

DATA_IN <= not DATA_IN; -- toggles A5 and 5A

wait for 2*PER;

end loop;

```

```

-- read

wait for 2*PER;

WE_B <= '1':

wait for PER;

for i in 0 to 31 loop

ADDR <= std_logic_vector(to_unsigned(i, 5));

DATA_IN <= x"00";

wait for 2*PER:

end loop;

-- read again to make sure write did not occur

-- overwrite with 1s

wait for 2*PER;

WE_B <= '0':

wait for PER;

for i in 0 to 31 loop

ADDR <= std_logic_vector(to_unsigned(i, 5));

DATA_IN <= x"FF";

wait for 2*PER;

end loop;

-- read again to make sure write did occur

wait for Ž*PER;

WE_B <= '1';

wait for PER;

for i in 0 to 31 loop

ADDR <= std_logic_vector(to_unsigned(i, 5));

DATA_IN <= x"A5";

wait for 2*PER;

end loop;

end process run;

-- End test processes

end architecture;

```

• 32 x 8 bit register file - verification

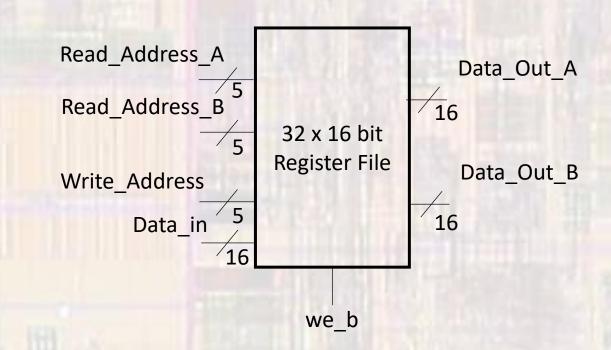

• 32 x 16 bit register file, 2 outputs

• 32 x 16 bit register file, 2 outputs

```

-- reg_file_32x16bx2.vhdl

-- created 3/18/18

-- tj

-- rev 0

-- 32 word by 16 bit register file with 2 outputs

-- Inputs: rstb, clk, addr_a, addr_b, data in, wr bar

-- Outputs: data out a, data out b

library ieee;

use ieée.std_logic_1164.all;

use ieee.numeric_std.all;

entity req_file_32x16bx2 is

generic (

constant ADDR_WIDTH : positive := 5;

constant MEM_DEPTH : positive := 32;

constant WORD_WIDTH : positive := 16

port (

i_clk:

in std_logic;

in std_logic_vector((ADDR_WIDTH - 1) downto 0);

in std_logic_vector((ADDR_WIDTH - 1) downto 0);

i_addr_a:

i_addr_b:

i_wr_addr:

in std_logic_vector((ADDR_WIDTH - 1) downto 0);

i_wr_b:

in std_logic;

in std_logic_vector((WORD_WIDTH - 1) downto 0);

i_data_in:

o_data_out_a: out std_logic_vector((WORD_WIDTH - 1) downto 0);

o_data_out_b: out std_logic_vector((WORD_WIDTH - 1) downto 0)

);

end entity;

```

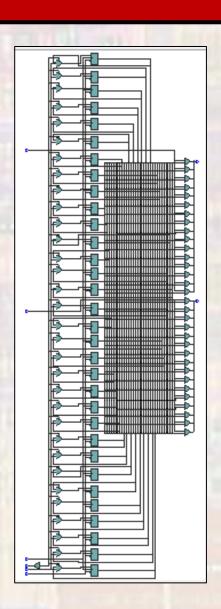

32 x 16 bit register file, 2 outputs

Create a new 'type'

The new 'type' is an array of std\_logic\_vector

```

architecture behavioral of reg_file_32x16bx2 is

-- Create an "TYPE" for an array of 1 bit registers

type REG_FILE is array(0 to (MEM_DEPTH - 1)) of std_logic_vector((WORD_WIDTH - 1) downto 0);

-- Create a signal of the array type

signal reg_32x16x2: REG_FILE;

-- Special command to stop Quartus from inferring a RAM

-- Must also turn off assignments / settings / compiler settings/

-- adavanced settings (synthesis) / auto RAM replacement --> off

attribute ramstyle : string;

attribute ramstyle of reg_32x16x2| : signal is "logic";

process(i_clk)

begin

if(rising_edge(i_clk)) then

if(i_wr_b = '0') then

reg_32x16x2(to_integer(unsigned(i_wr_addr))) <= i_data_in;

end if:

end process;

-- Output_logic

o_data_out_a <= reg_32x16x2(to_integer(unsigned(i_addr_a)));

o_data_out_b <= reg_32x16x2(to_integer(unsigned(i_addr_b)));

end architecture;

```

Need the address as an integer to index the array. Address is SLV coming in – need to pass through unsigned along the way

- 32 x 16 bit register file, 2 outputs testbench

- Normal clock process

- No reset process

- Read A and B outputs opposite directions(unknown)

- Write to all locations (1-0 pattern)

- Read A and B outputs opposite directions(1-0 pattern)

- Write to all locations (0-1 pattern)

- Read A and B outputs opposite directions(0-1 pattern)

- Exercise Write address and data but with no wr\_b

- Read A and B outputs opposite directions(no change)