### Trabajo Fin de Máster

Máster en Electrónica, Tratamiento de Señal y Comunicaciones

Implementación y análisis de SEU de un transmisor de comunicaciones inalámbricas para aplicaciones intra-satélite

Autor: Javier Barrientos Rojas Tutor: Hipólito Guzmán Miranda

Departamento de Ingeniería Electrónica Escuela Técnica Superior de Ingeniería Universidad de Sevilla

Sevilla, Noviembre 2015

### Trabajo Fin de Máster Máster en Electrónica, Tratamiento de Señal y Comunicaciones

Implementación y análisis de SEU de un transmisor de comunicaciones inalámbricas para aplicaciones intra-satélite

Autor:

Javier Barrientos Rojas

Tutor:

Hipólito Guzmán Miranda Profesor Ayudante Doctor

Departamento de Ingeniería Electrónica Escuela Técnica Superior de Ingeniería Universidad de Sevilla

Sevilla, Noviembre 2015

| Trabajo Fin de M<br>inalámbricas para | áster: Implementación y análisis de SEU de un transmisor de comunicaciones aplicaciones intra-satélite |

|---------------------------------------|--------------------------------------------------------------------------------------------------------|

| Autor:                                | Javier Barrientos Rojas                                                                                |

| Tutor:                                | Hipólito Guzmán Miranda                                                                                |

| El tribunal nombrad                   | lo para juzgar el Trabajo arriba indicado, compuesto por los siguientes miembros:                      |

| Presidente:                           |                                                                                                        |

|                                       |                                                                                                        |

| Vocales:                              |                                                                                                        |

|                                       |                                                                                                        |

| Secretario:                           |                                                                                                        |

|                                       |                                                                                                        |

| Acuerdan otorgar                      | le la calificación de:                                                                                 |

|                                       |                                                                                                        |

|                                       |                                                                                                        |

|                                       |                                                                                                        |

|                                       | Sevilla, Noviembre 2015                                                                                |

A mi mujer

## Agradecimientos

A todo el equipo de personas que forman parte del proyecto Edelweiss: Vicente, Patricio, Miguel Ángel y sobre todo a Hipólito con quien nunca dejo de aprender, agradecer la confianza depositada en mí y conseguir que trabajar en un proyecto de investigación se convierta en algo ameno y sencillo de realizar.

A mis padres por su apoyo incondicional.

A mi mujer por sus palabras de ánimo, su compañía en los buenos y malos momentos ha influido enormemente en la elaboración de este trabajo.

### Resumen

Uno de los inconvenientes más importantes en cuanto a embarcar sistemas de comunicaciones en satélites, es el excesivo peso que aportan a causa, en gran medida, del cableado necesario para su instalación. Una de las soluciones más atractivas que se estudian es la de emplear sistemas inalámbricos por motivos obvios. Este trabajo forma parte de un proyecto de investigación, en el que se trata de diseñar un sistema de comunicaciones inalámbrico de alta eficiencia. Para ello se realizan una serie de pruebas de inyección de fallos sobre el diseño, con el objeto de conocer la robustez estructural del sistema. Dicha característica representa la sensibilidad del diseño ante posibles ataques que pueda sufrir el sistema a causa de una radiación externa en un entorno hostil, como puede ser el caso de una aplicación inter-satelital.

# Índice

| Agradecimientos                                                | 6   |

|----------------------------------------------------------------|-----|

| Resumen                                                        | 7   |

| Índice                                                         |     |

| Índice de figuras                                              |     |

| Indice de tablas                                               | 12  |

| Capítulo 1 - Introducción                                      | 14  |

| 1.1. Marco del trabajo                                         | 15  |

| 1.2. Problemática                                              |     |

| 1.3. Efectos de la Radiación                                   | 17  |

| 1.3.1. Mecanismos Físicos de Daños                             | 17  |

| 1.3.2. Efectos de Eventos Únicos (SEE)                         | 18  |

| 1.3.2.1. Conmutación por Evento Único                          | 19  |

| 1.4. Sistemas Inalámbricos para Comunicaciones Intra-satélites | 19  |

| 1.4.1. Enlaces Inalámbricos Ópticos                            | 19  |

| 1.4.1.1. Enlaces Inalámbricos por Infrarrojos (IR)             |     |

| 1.4.2. Enlaces Inalámbricos por Radiofrecuencia                |     |

| 1.5. Robustez Estructural                                      | 22  |

| Capítulo 2 – Solución propuesta                                | 23  |

| 2.1. Comparativa entre ZigBee y Bluetooth                      |     |

| 2.1.1. Bluetooth                                               | 24  |

| 2.1.2. ZigBee                                                  |     |

| 2.1.3. Cuadro comparativo                                      |     |

| 2.2. Capa física del protocolo ZigBee                          |     |

| 2.3. Estructura del transmisor                                 |     |

| Capítulo 3 – Desarrollo del transmisor                         | 28  |

| 3.1. Diseño de la arquitectura hardware                        |     |

| 3.1.1. Consideraciones de implementación                       |     |

| 3.1.2. Implementación de la arquitectura                       |     |

| •                                                              |     |

| 3.1.2.1. FADAPT                                                |     |

| 3.1.2.2 BIT2SYMB                                               |     |

| 3.1.2.3. SYMB2CHIP                                             |     |

| 3.1.2.5. PULSE SHAPING                                         |     |

| 3.1.2.6. QDELAY                                                |     |

| 3.1.2.7. TOP TX.                                               | 2.5 |

| 3.2. Verificación funcional                            | 39 |

|--------------------------------------------------------|----|

| 3.2.1. Crosscheck con modelo Matlab                    | 40 |

| 3.2.2. Entorno de pruebas                              | 43 |

| 3.2.3. Code Coverage                                   | 46 |

| Capítulo 4 – Análisis de inyección de fallos           |    |

| 4.1. Herramienta de análisis                           |    |

| 4.2. Condiciones del test                              |    |

| 4.3. Modelos de comparación                            | 53 |

| 4.3.1. Clasificación de fallos                         | 54 |

| Capítulo 5 - Resultados                                | 56 |

| 5.1. Aspectos relativos a la FPGA                      | 57 |

| 5.2. Verificación funcional                            | 57 |

| 5.3. Sensibilidad ante SEU                             | 58 |

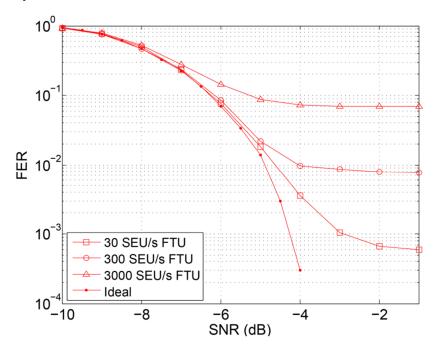

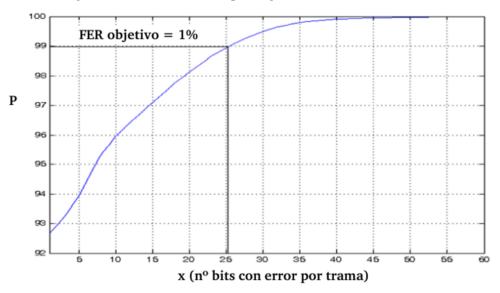

| 5.3.1. Curvas de ruido                                 | 61 |

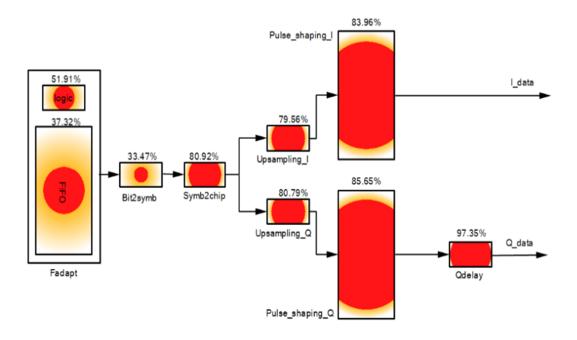

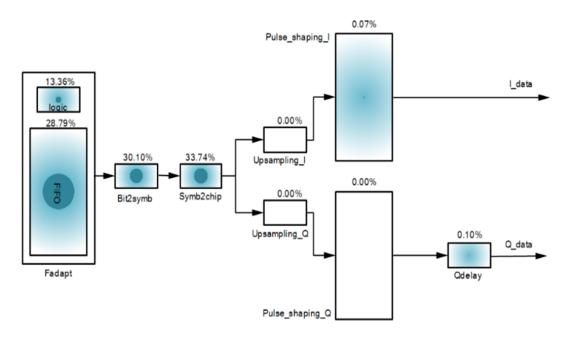

| 5.3.2. Zonas Calientes                                 |    |

| 5.4. Metodología de Endurecimiento                     | 64 |

| Capítulo 6 – Conclusiones y trabajos futuros           |    |

| 6.1. Acerca del diseño del transmisor                  |    |

| 6.2. Acerca de la verificación                         |    |

| 6.3. Acerca del modelo de comparación                  |    |

| 6.4. Acerca de los resultados obtenidos                |    |

| 6.5. Trabajos Futuros                                  | 68 |

| 6.5.1. Desarrollo e implementación del receptor        |    |

| 6.5.2. Prototipado del sistema completo sobre una FPGA |    |

| 6.5.3. Implementación ASIC                             |    |

| 6.5.4. Test de radiación                               | 69 |

| Referencias                                            | 71 |

# Índice de figuras

| Figura 2.1  | Esquema de bloques del transmisor ZigBee            | 2' |

|-------------|-----------------------------------------------------|----|

| Figura 3.1  | Esquema de la capa física del transmisor            | 30 |

| Figura 3.2  | Trama PPDU                                          | 3  |

| Figura 3.3  | Sobremuestreo para N=8                              | 34 |

| Figura 3.4  | Estructura del filtro conformador de onda           | 35 |

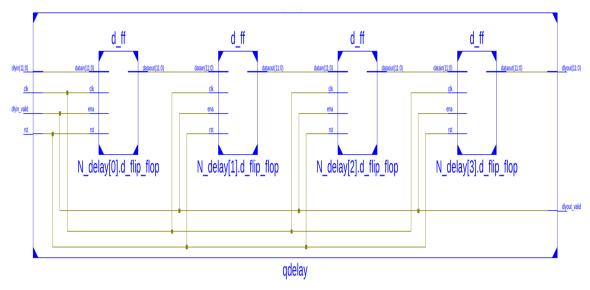

| Figura 3.5  | Estructura del bloque QDELAY                        | 30 |

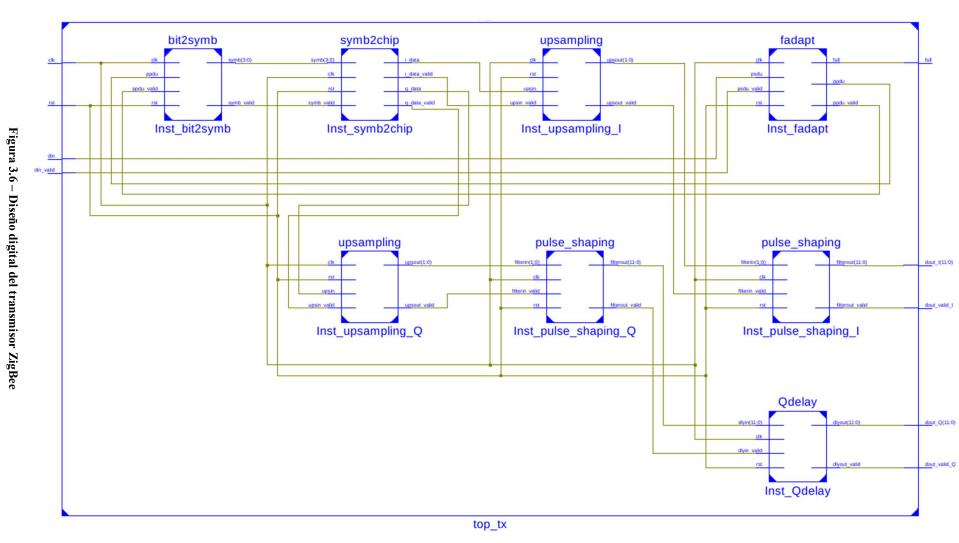

| Figura 3.6  | Diseño digital del transmisor ZigBee                | 38 |

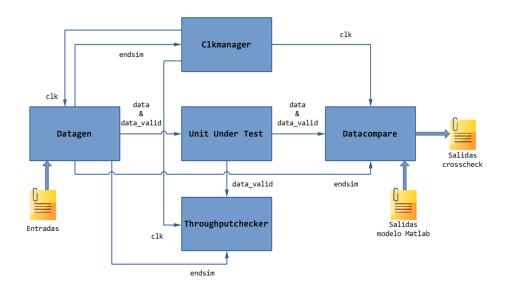

| Figura 3.7  | Esquema de un test bench básico                     | 43 |

| Figura 3.8  | Esquema de crosschecks                              | 43 |

| Figura 3.9  | Entorno de verificación con la herramienta CMake    | 44 |

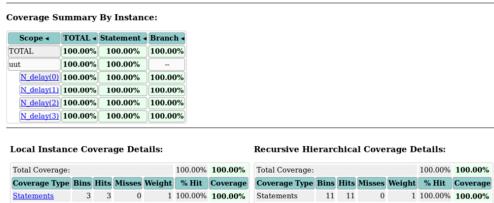

| Figura 3.10 | Resultado de Code Coverage para el bloque fadapt    | 47 |

| Figura 3.11 | Resultado de Code Coverage para el bloque bit2symb  | 41 |

| Figura 3.12 | Resultado de Code Coverage para el bloque symb2chin | 49 |

| Figura 3.13 | Resultado de Code Coverage para el bloque upsampling    | 48 |

|-------------|---------------------------------------------------------|----|

| Figura 3.14 | Resultado de Code Coverage para el bloque pulse_shaping | 48 |

| Figura 3.15 | Resultado de Code Coverage para el bloque qdelay        | 49 |

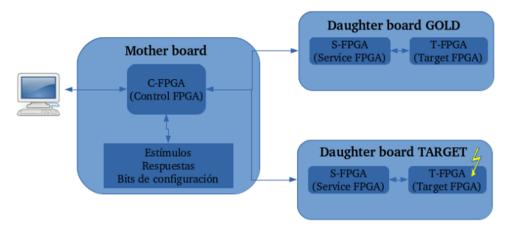

| Figura 4.1  | Arquitectura de la herramienta FTU2                     | 51 |

| Figura 4.2  | Nuevo modelo de comparación                             | 54 |

| Figura 4.3  | Esquema de análisis de fallos                           | 55 |

| Figura 5.1  | Curvas de FER para diferentes tasas de SEU              | 61 |

| Figura 5.2  | Función de distribución de tramas erróneas acumuladas   | 62 |

| Figura 5.3  | Aportación de tramas erróneas después de la transmisión | 63 |

| Figura 5.4  | Aportación de tramas erróneas después de la recepción   | 63 |

# Índice de tablas

| Tabla 1.1 | Clasificación de SEE                                         | 18 |

|-----------|--------------------------------------------------------------|----|

| Tabla 2.1 | Comparativa entre protocolos                                 | 25 |

| Tabla 2.2 | Especificaciones para la transmision en la banda de 2.4 GHz  | 26 |

| Tabla 3.1 | Valores del campo SFD                                        | 31 |

| Tabla 3.2 | Secuencias PN asociadas a cada símbolo                       | 33 |

| Tabla 3.3 | Coeficientes del filtro conformador de onda                  | 35 |

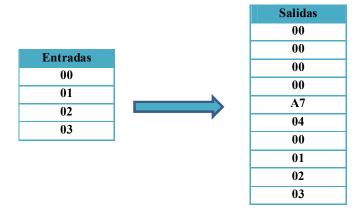

| Tabla 3.4 | Ejemplo de valores de entrada y salida para el bloque FADAPT | 40 |

| Tabla 4.1 | Clasificación de fallos                                      | 55 |

| Tabla 5.1 | Resultados de sensibilidad ante SEU                          | 59 |

| Tabla 5.2 | Sensibilidad ante SEU sobre el flujo de datos                | 60 |

## Capítulo 1

### Imtroducción

En este capítulo introductorio se explica la motivación del desarrollo del presente trabajo. Ubicado en el ámbito de las aplicaciones espaciales, se detallan los efectos negativos que producen los llamados Eventos Singulares sobre este tipo de aplicaciones y cómo pueden llegar a afectar a cualquier dispositivo electrónico. Terminando por analizar los principales protocolos para comunicaciones inalámbricas que se ajusten dentro de un sistema intra-satélite y definir el concepto de robustez estructural, parámetro que ayudará a entender la capacidad de endurecimiento del que dispone el diseño del transmisor sin emplear ninguna técnica de mitigación de fallos.

### 1.1. Marco del trabajo

El presente trabajo se desarrolla dentro del proyecto de excelencia de la Junta de Andalucía: "Edelweiss: Diseño de un sistema de comunicaciones inalámbricas intrasatélite de alta eficiencia" (P11-TIC-7095). Proyecto en el que uno de sus principales objetivos es diseñar un sistema de comunicaciones inalámbrico para aplicaciones espaciales y cuyo transmisor es el trabajo que se presenta en este documento.

El equipo de trabajo lo integran varias personas del Departamento de Ingeniería Electrónica de la Universidad de Sevilla y el alumno plasma aquí su contribución con el diseño digital del hardware del transmisor y el sistema de verificación que se emplea para cotejar y validar los resultados obtenidos.

### 1.2. Problemática

El proyecto Edelweiss trata de solventar algunos de los principales problemas que afectan al encarecimiento de cualquier tipo de misión espacial que conlleve el lanzamiento de un satélite sea cual sea su función y la órbita en la que vaya a situarse; a saber: peso, consumo de potencia disponible, ensamblaje e integración de equipos, así como el esfuerzo que se realiza en términos de verificación.

Este tipo de misiones están sujetas a fuertes restricciones de consumo, peso y fiabilidad y tratando de que el conjunto sea económicamente factible para poder ser realizada. Los diferentes dispositivos e instrumentos que se instalan en un satélite, se comunican mediante cableado y este hecho aumenta tanto el peso como la complejidad de la carga útil total, contribuyendo negativamente en el coste de la misión.

La idea de la eliminación del cableado en los satélites no se puede considerar novedosa pero sí el desarrollo de técnicas y su implementación en misiones lanzadas como ensayos o demostradores tecnológicos. Este es el caso, por ejemplo, del satélite Optos lanzado a finales del año 2013 y desarrollado por el INTA, que entre sus principales experimentos a realizar durante la misión, contempla el uso de un sistema de comunicaciones a bordo basado en óptica difusa con el objeto de eliminar el cableado interno [Ref. 1.1].

Otra problemática asociada, de manera general a cualquier dispositivo que vaya a funcionar tanto en las diferentes capas que conforman la atmósfera terrestre como en el espacio exterior, son los **efectos de la radiación** sobre los circuitos electrónicos. Se trata de fenómenos físicos complejos que se producen tras la posible colisión entre partículas provenientes de la radiación y las partículas que componen la estructura molecular de un componente electrónico (principalmente sobre transistores).

Es la atmósfera la que actúa como una pantalla protectora que retiene la mayor parte de esta radiación y los rayos UV que inciden sobre el planeta. Las fuentes de radiación son diversas, entre las principales se pueden destacar las siguientes:

- Protones y electrones atrapados en los cinturones de Van Allen.

- 🔀 El sol como fuente de dos importantes fenómenos:

- o Iones pesados atrapados en la magnetosfera a causa del viento solar.

- o Iones pesados y protones procedentes de llamaradas solares.

- Rayos cósmicos, cuya composición es aproximadamente de un 85% protones, 14% partículas alfa y un 1% de iones pesados.

Existen numerosos estudios sobre cada una de las diferentes fuentes de radiación ya nombradas. Se conocen como anillos de radiación (llamados cinturones de Van Allen), a dos grandes zonas circundando el planeta Tierra compuestos principalmente por electrones y protones atrapados [Ref. 1.2]. Se ha comprobado que para el anillo interior se alcanza una energía no superior a los 5 MeV y que en el anillo exterior se pueden alcanzar hasta los 7 MeV, la mayoría de iones que componen estos anillos son ligeros y de baja penetración [Ref. 1.3].

El sol es la mayor fuente de radiación que afecta al planeta Tierra, y destacan dos fenómenos principalmente. En primer lugar, las llamaradas solares son fuertes explosiones capaces de liberar una altísima cantidad de energía en forma de calor; estas explosiones provocan la aceleración de electrones, protones e iones pesados a velocidades cercanas a la de la luz [Ref. 1.4]. En segundo lugar, el viento solar que se forma a partir de la expulsión de electrones de la corona solar, formándose un plasma que contiene protones en su mayor parte y un pequeño porcentaje de iones pesados.

Los cambios producidos en la densidad o la velocidad del viento solar provocan perturbaciones sobre la magnetosfera terrestre y dan origen a tormentas magnéticas que pueden afectar a satélites en órbita [Ref. 1.5]. Para terminar, cabe resaltar la influencia de los rayos cósmicos como otra fuente importante de radiación, ya que contienen núcleos de iones pesados de muy alta energía [Ref. 1.6].

El problema de los efectos de la radiación no es algo exclusivo a sistemas que funcionan en órbitas alrededor del planeta Tierra o en el espacio exterior. La evolución tecnológica que se viene desarrollando en los últimos años da como lugar a la fabricación de dispositivos microelectrónicos cada vez más rápidos y más pequeños.

Como consecuencia de esta evolución, se concentran un mayor número de transistores en una porción de silicio del orden de mm² y esta reducción de tamaño disminuye el valor de la energía necesaria para producir fallos en la electrónica, lo que conlleva a que sean mucho más sensibles a la radiación. Aunque estos efectos se encuentran en menor medida a nivel del mar que fuera de la atmósfera, pero es un factor a tener en cuenta ya que puede provocar fallos en los circuitos y es algo que debe evitarse en sistemas aeronáuticos o de automoción, así como militares. Por ello, se están desarrollando técnicas de protección de los dispositivos electrónicos ante radiación para uso a nivel del mar, ya que la microelectrónica se encuentra en multitud de lugares, transportes y objetos cotidianos.

### 1.3. Efectos de la Radiación

Una vez planteada la motivación del presente trabajo, en este apartado se trata de desarrollar con algo más de detalle cuáles son los efectos que la radiación puede llegar a provocar en un circuito electrónico, resaltando aspectos como por ejemplo si dichos efectos son totalmente destructivos o no y si existen técnicas para mitigarlos.

El estudio de la radiación ha dado lugar a diferenciar entre dos grandes categorías según sea el tipo de daño que provoca sobre un determinado circuito electrónico. Por un lado, este tipo de efectos se tratan de modelar de alguna forma para comprender mejor su naturaleza y poder desarrollar técnicas para mitigarlos. La idea de modelar este tipo de fenómenos físicos tan complejos entre la interacción de partículas provenientes de la radiación y la estructura molecular de un dispositivo electrónico no es sencilla, por ello se intentan modelar ciertos parámetros circuitales (tensión, corriente o carga en ciertos nodos) ya que resulta más sencillo plantear de esta manera el cómo afectan los modelos de error sobre un diseño de un circuito electrónico.

Estos modelos se suelen hacer en el dominio digital, principalmente para simplificar el problema y además aprovechar las capacidades de los simuladores de lógica digital y emuladores hardware mediante el uso de las FPGA. Por otro lado, algunos de estos errores provocados por la radiación pueden llegar a destruir físicamente partes del circuito. Los principales motivos que diferencian a las dos categorías de errores debidos a la radiación se detallan a continuación:

- Errores Físicos (*Hard Errors*) Pueden llegar a destruir físicamente ciertas partes de la estructura de un dispositivo electrónico y además es imposible poder modelarlo y solventarlo de manera digital.

- Errores Lógicos (*Soft Errors*) Es posible hacer un modelo digital de su comportamiento y con ello poder analizarlos y hallar estrategias para mitigarlos.

### 1.3.1. Mecanismos Físicos de Daños

Existen tres grupos donde se diferencian claramente cuáles son los mecanismos o la naturaleza de los daños provocados sobre un circuito electrónico debido a la radiación.

### Osis Ionizante Total - TiD (del inglés *Total ionizing Dose*)

Produce errores del tipo físico ya que tiene un efecto acumulativo sobre el circuito al que ataca; es decir, se trata de una ionización a largo plazo que provoca cambios en la tensión umbral de transistores MOS debido a cargas atrapadas entre el óxido y el semiconductor y que a su vez pueden escapar por efecto túnel degradando las prestaciones del dispositivo. También genera corrientes de fuga o 'leakage' entre difusiones vecinas de tipo N, lo que puede llevar a un incremento del consumo del transistor MOS.

### Daño por Desplazamiento – DD (del inglés Displacement Damage)

Produce cambios en la estructura cristalina del material semiconductor tales como un aumento de recombinación de pares e-h, agotamiento de portadores minoritarios y un empeoramiento de las propiedades analógicas de las uniones semiconductoras afectadas; degenerando las propiedades del dispositivo. Los transistores bipolares y dispositivos ópticos son más sensibles a este mecanismo de daño ya que son dependientes de los portadores minoritarios en sus regiones de base y a causa de la recombinación sufren pérdidas de ganancia del transistor.

### **Efectos de Eventos Únicos** - SEE (del inglés *Single Event Effects*)

A diferencia de los mecanismos anteriores que se caracterizan por una acumulación gradual debida a la radiación, estos errores son transitorios y bien localizados, ocasionados por impactos de partículas ionizantes sobre ciertas partes de un circuito. En este caso, son los dispositivos digitales los más afectados ya que pueden provocar cambios de valor en registros y provocar respuestas no esperadas en el sistema implementado. Este tipo de errores es el que se va a emular en este trabajo utilizando una herramienta de inyección de fallos propia, para analizar la robustez del transmisor que se va a diseñar.

### 1.3.2. Efectos de Eventos Únicos (SEE)

Estos daños son los más comunes en dispositivos digitales y sus efectos pueden ser: aumento del consumo, pérdida de funcionalidad (crear situaciones de bloqueo), en general, una degradación de los parámetros del dispositivo y sobre todo la propagación de bits erróneos en memorias y lógica digital. Dentro de este grupo se incluyen varios tipos de efectos que a su vez se dividen según su naturaleza sea de errores tipo físico o lógico. No es objeto de este trabajo describir de manera detallada cada uno de los efectos que existen en esta categoría y por ello, en la tabla 1.1 se muestra un resumen donde se clasifican, según su naturaleza, dejando como único efecto a analizar los de tipo SEU, ya que son los que van a formar parte en el desarrollo de este trabajo.

| Efecto                            | Naturaleza |

|-----------------------------------|------------|

| SEL<br>Single Event Latchup       | Físico     |

| SEGR<br>Single Event Gate Rupture | Físico     |

| SEB<br>Single Even Burnout        | Físico     |

| SEU<br>Single Event Upset         | Lógico     |

| MBU<br>Multi Bit Upset            | Lógico     |

| SET Single Event Transient        | Lógico     |

| SEMU<br>Single Event Multi Upset  | Lógico     |

Tabla 1.1 - Clasificación de SEE

### 1.3.2.1. Conmutación por Evento Único

Conocido como SEU (del inglés *Single Event Upset*), provoca un cambio de estado (o nivel lógico: de '0' a '1', o de '1' a '0') de un elemento biestable. Dicho cambio se produce por el impacto de una única partícula ionizante o bien por reacciones nucleares producidas por un único protón. No todas las regiones del biestable son sensibles como para que el impacto de la partícula ionizante produzca un cambio de estado, solamente los drenadores de los transistores que se encuentran cortados pueden acarrear que dicho efecto se lleve a cabo, se denominan nodos sensibles. El impacto de la radiación en estos nodos sensibles genera pares e-h que inducen un pulso de corriente instantánea de duración del orden de picosegundos. La carga generada por la partícula ionizante es recogida por la estructura del biestable y si dicha carga es superior a la denominada carga crítica  $Q_c$  (valor de carga media necesaria para cambiar el estado del biestable), entonces el estado lógico del biestable cambia.

Al ser de naturaleza lógica, lo que produce son errores transitorios que no llegan a destruir fisicamente un dispositivo electrónico y además puede ser modelado de manera digital. El modelo básico que se emplea para estudiar este tipo de efecto es el denominado **Bit-Flip**, que representa un cambio o inversión del valor lógico de una celda de memoria; es decir, cambios de '0' a '1', o de '1' a '0', teniendo en cuenta que dicho cambio se produce en un instante único y determinado de tiempo.

### 1.4. Sistemas Inalámbricos para Comunicaciones Intra-satélites

Como se indica al comienzo del capítulo, el presente trabajo muestra el diseño de un transmisor que forma parte de un sistema de comunicaciones inalámbricas para aplicaciones intra-satélites. En este punto se pretende mostrar una visión de los principales sistemas de este tipo aplicados a satélites, algunos de ellos ya han sido embarcados en alguna misión y otros se encuentran en fase de investigación ya que uno de los principales problemas que se encuentran para poder ser instalados y que funcionen de forma autónoma, es el hecho de que a día de hoy falta por desarrollarse una tecnología de pilas o baterías para espacio capaces de dar la potencia necesaria a este tipo de sistemas inalámbricos para su correcto funcionamiento. En el capítulo 2 se realiza una comparativa entre los diferentes sistemas que se describen a continuación, con la idea de establecer los motivos del protocolo de comunicaciones elegido para desarrollar el proyecto Edelweiss.

### 1.4.1. Enlaces Inalámbricos Ópticos

Esta tecnología bautizada por el INTA (Instituto Nacional de Técnica Aeroespacial) como OWLS (*Optical Wireless Links for intra-Satellite communications*), busca una comunicación intrasatelital sin cables basada en una transmisión óptica de la información pero sin emplear la fibra óptica como elemento de conexión si no utilizando sólo emisores y detectores ópticos transmitiendo en el espacio abierto. El inicio de esta tecnología data del año 1999 cuando el INTA la propuso como solución

de la interconexión de micro y nano sistemas en el interior de las plataformas espaciales. El primer sistema con tecnología OWLS en vuelo tuvo lugar en 2004 con el lanzamiento por parte del INTA del satélite NANOSAT 01; más recientemente en septiembre de 2007, se lanzó una cápsula espacial llamada FOTON M-3, dentro de la cual se encuentra un experimento del INTA (propuesto por la Agencia Espacial Europea) denominado FOTON-OWLS con el fin de optimizar este tipo de comunicaciones sin cables y así aligerar el peso en la medida de lo posible [Ref. 1.7].

### 1.4.1.1. Enlaces Inalámbricos por Infrarrojos (IR)

Una de las tecnologías, dentro de las ópticas, que se plantean es el uso de los enlaces IR como una vía complementaria a la RF (*Radio Frequency*). Entre sus ventajas destacan que no es necesaria una alineación entre transmisores y receptores, se pueden alcanzar altas tasas de datos, el espectro IR no está sujeto a regulaciones gubernamentales de ningún tipo, no se ve afectada por EMI (*Electro Magnetic Interference*) y además es una tecnología de bajo coste.

Es precisamente la inmunidad a EMI la que hace mejor esta tecnología frente a la RF en cuanto a la comunicación de datos dentro de un satélite [Ref. 1.8]. El desafio se centra en la investigación de diferentes puntos con idea de poder desarrollar este tipo de sistemas e implementarlos en alguna misión o experimento espacial:

- ❖ Cobertura completa del satélite: La distribución de la carga dentro de un satélite puede crear zonas sombreadas que dificulten la comunicación con algún receptor. Se precisa investigar sobre repetidores que permitan salvar estas zonas y así obtener una cobertura completa. Estos repetidores deben de ser muy robustos y permitir varios caminos redundantes para asegurar las comunicaciones entre cualquier transmisor y transmisor colocados dentro del satélite. A su vez, deben de ser elementos de bajo coste y de fácil instalación.

- Redes difusas de baja-media velocidad: Como se ha comentado, esta tecnología no necesita de ningún tipo de alineación entre transmisor y receptor gracias a que usa enlaces de naturaleza difusa. Por tanto, se precisa de una red con topología difusa y con ello el desarrollo tanto de un hardware como un software aptos para este tipo de comunicaciones. Además se necesita disponer de un protocolo de comunicaciones para manejar los diferentes nodos, ya sean equipos terminales o repetidores.

- Enlaces de alta velocidad: Para el caso en el que haya enlaces con líneas de visión directa, se usan diodos tipo láser disponible hoy día en el mercado, se pueden conseguir tasas de datos del orden de decenas de Gbps. Se necesitan desarrollar tanto el hardware como el software para implementar las aplicaciones de transferencia de datos.

- ❖ Integración en el entorno espacial: Un sistema IR debe cumplir con dos aspectos principalmente para ser instalado en un satélite y soportar las

situaciones extremas que se dan en un torno tan hostil como es el espacio exterior. Por un lado, evitar en la medida de lo posible la necesidad de tener partes mecánicas asociadas al sistema IR. Para ello se emplean circuitos electrónicos y optoelectrónicos integrados en el mismo equipo de comunicaciones, y al tratarse de un sistema inalámbrico se evitan los cables y sus problemas de conexionado. Y por otro lado, se desea que sea un sistema de bajo consumo de potencia por lo que es preferible que se desarrollen circuitos optoelectrónicos de muy baja potencia.

Selección de componentes y su certificación para espacio: Todo el hardware necesario para un sistema de comunicaciones inalámbrico IR debe hacerse usando COTS (Components Off The Shelf). Esto implica que una vez se tengan desarrollados los emisores y receptores para este tipo de enlaces, es necesario diseñar y llevar a cabo su correspondiente certificación para espacio y así disponer de unos dispositivos aptos para embarcarlos en vuelo.

La ESA (*European Space Agency*) desarrolló un estudio junto con un demostrador en el año 2000, en el que se disponía de dos redes IR trabajando de forma simultánea. Una de las redes comunicaba una unidad central con varios sensores empleando un canal inalámbrico IR de baja velocidad (tasa de datos de 19200 bps). La otra red establecía una conexión punto a punto de alta velocidad para transmitir una señal de video analógico (modulada a una frecuencia cercana a los 500 MHz).

Este experimento demostró que es posible la comunicación en este tipo de sistemas inalámbricos y que están disponibles enlaces de gran ancho de banda para esta tecnología [Ref. 1.9].

### 1.4.2. Enlaces Inalámbricos por Radiofrecuencia

El empleo de tecnologías RF (*Radio Frequency*) en sistemas de comunicaciones para espacio puede dar solución a ciertas aplicaciones mediante el uso de motas inalámbricas, como por ejemplo, la recopilación de telemetría en general.

Los protocolos inalámbricos COTS que se han investigado, diferencian su uso entre dos ámbitos. Por una parte, las comunicaciones intrasatelitales, donde destacan ZigBee (IEEE 802.15.4) [Ref. 1.10] y Bluetooth (IEEE 802.15.1) [Ref. 1.11]; y por otra parte, las comunicaciones intersatelitales donde encajan los protocolos WiFi (IEEE 802.11) [Ref. 1.12] y WiMax (IEEE 802.16) [Ref. 1.13].

Para el proyecto Edelweiss, se necesita un protocolo de comunicaciones intrasatélite, por tanto se dispone de dos alternativas: ZigBee y Bluetooth.

Los principales criterios de selección para un protocolo inalámbrico para comunicaciones intra-satelitales son: robustez ante fallos provocados por radiación e interferencias externas, poder dar soporte a varios nodos, tasas de datos aceptables, requerimientos de potencia asumibles y en la medida de lo posible minimizar el coste y una sencilla instalación.

En el siguiente capítulo se desarrolla una mejor comparativa entre estas dos opciones y se dan los motivos para la elección de uno de ellos para el desarrollo del presente trabajo.

### 1.5. Robustez Estructural

El concepto de robustez estructural, SR en adelante (del inglés *Structural Robustness*), es la medida más común para determinar la eficiencia frente a los efectos de la radiación (tipos SEE principalmente) sobre la estructura de un sistema genérico. Otra manera de definirlo es la capacidad que tiene un sistema para auto regenerar su comportamiento ante un fallo tipo SEU. Todo sistema se puede caracterizar mediante un valor conocido como AVF (del inglés *Architectural Vulnerability Factor*), definido como la probabilidad de que un fallo en una zona concreta dentro de un circuito pueda dar como resultado un error. Este parámetro es muy interesante en estudios para espacio porque es lógico pensar que la capacidad que tiene un protocolo de comunicaciones inalámbrico de corregir errores de bit, puede ser de ayuda para mitigar los efectos tipo SEU. Por tanto, se precisa calcular el AVF de un circuito mediante un ensayo de inyección de fallos sobre una versión no mitigada del mismo para conocer la SR del sistema.

Más adelante se mostrará como el protocolo de comunicaciones seleccionado tiene una robustez inherente a su arquitectura, que le hace ser capaz de corregir muchos de los errores en la señal recibida causados tanto por las interferencias en el canal de comunicaciones como por fallos inducidos en el propio transmisor.

# Capítulo 2

# Solución Propuesta

Vista las diferentes opciones que se emplean o investigan a día de hoy para disponer de comunicaciones inalámbricas intra-satelitales, en este capítulo se trata de justificar el protocolo seleccionado en la solución propuesta. Mostrando al final la arquitectura, a nivel de bloques, de dicha solución cuyo desarrollo se describe en el siguiente capítulo.

### 2.1. Comparativa entre ZigBee y Bluetooth

Tal y como se ha comentado en el capítulo anterior, el presente trabajo forma parte de un sistema de comunicaciones inalámbricas para aplicaciones intra-satelitales y es en este ámbito donde ZigBee y Bluetooth se encuentran como los principales protocolos que se han investigado hasta ahora para su posible uso en misiones espaciales. Lo que se plantea en este punto es justificar el por qué se ha decidido por uno de los dos, antes de entrar en el diseño del transmisor, ya que las propias estructuras de los diferentes módulos que los componen dependen totalmente del protocolo seleccionado.

Ambos protocolos tienen ciertos aspectos en común, pertenecen a la categoría del IEEE 802.15 redes inalámbricas de área personal o WPAN (*Wireless Personal Area Network*) y trabajan en la banda de frecuencia de 2.4 GHz (aunque ZigBee puede trabajar en otras bandas también, esta es la más usual por tener licencia de libre uso a nivel mundial). Se detallan a continuación las principales características de cada uno de estos protocolos, con idea de tener posteriormente un cuadro comparativo donde mostrar las razones por las cuales se realiza la elección del que resulta más adecuado al proyecto de investigación que se va a realizar.

### 2.1.1. Bluetooth

Este protocolo de comunicaciones, definido en el estándar IEEE 802.15.1 aunque el organismo que gestiona las evoluciones del protocolo y la certificación de equipos es el denominado *Bluetooth Special Interest Group* (B-SIG), posibilita la transmisión de datos y de voz entre diferentes dispositivos mediante un enlace RF (*Radio Frequency*) en la banda de los 2.4 GHz. La técnica de modulación empleada es la de salto en frecuencia con espectro expandido o FHSS (del inglés, *Frequency Hopping Spread Spectrum*); entre sus principales características cabe resaltar su alta tasa de velocidad de transmisión (hasta 1 Mbit/s) y el rango de distancias de separación entre los dispositivos (de 1 a 100 metros).

Bluetooth está concebido para ser utilizado de manera exclusiva en redes de tipo Ad hoc, redes descentralizadas enfocadas a una comunicación equipo a equipo donde cada mota participa en el encaminamiento mediante el reenvío de la información hacia otras motas. Son un tipo de redes muy fáciles de implementar y la adhesión de una nueva mota es tan simple como situarla dentro del rango de alcance de la red. Por el contrario, aunque su ancho de banda permite transmitir una mayor cantidad de datos con respecto a ZigBee, como consecuencia emplea un mayor consumo de energía, elemento crítico en aplicaciones espaciales.

### **2.1.2. ZigBee**

Esta tecnología fue diseñada por la Alianza ZigBee, está basada en el estándar IEEE 802.15.4 pero modificado para poder funcionar también en redes con tipología 'mesh' (mallado). Se trata de un protocolo de comunicaciones inalámbrico pensado para establecer comunicaciones a baja velocidad entre dos o varios dispositivos (llegándose a poder formar redes con cientos de dispositivos comunicándose entre sí).

La Alianza ZigBee<sup>1</sup> está formada por cientos de compañías que tratan de encontrar una solución a la necesidad de disponer de un estándar para comunicaciones a baja velocidad pero con un bajo coste de implementación y que además los dispositivos involucrados en la red requieran muy bajo consumo. Algunas de las compañías involucradas en esta alianza son Philips, LG, Texas Instruments, ARM, Schneider, Cisco, Siemens y varias empresas españolas como Indra, que ha entrado recientemente<sup>2</sup>.

Entre sus principales características cabe resaltar que su velocidad de transmisión se mueve entre 25-250 kbps, trabaja en la frecuencia de 2.4 GHz (aunque también puede trabajar en las frecuencias de 868 MHz y 915 MHz), es un protocolo asíncrono half dúplex, emplea una modulación de espectro expandido de secuencia directa (DSSS, del inglés *Direct Sequence Spread Spectrum*), soporta redes tipo *mesh*, punto a multipunto y árbol, está pensado para que disponga de dispositivos que trabajan en modo de bajo consumo alargando la duración de sus baterías, es un protocolo fiable ya que la red se organiza y puede repararse de forma automática (las tramas de datos se encaminan de forma dinámica) y por último destacar que es un protocolo seguro ya que permite implementar técnicas de autenticación y encriptación.

Desde el punto de vista de aplicación, como protocolo para un sistema de comunicaciones embarcado en un satélite, resulta una opción muy atractiva por su versatilidad, simplicidad de implementación y sobre todo su bajo consumo.

### 2.1.3. Cuadro comparativo

Se pasa a mostrar en la tabla 2.1 una comparación entre ambos protocolos para seguidamente detallar cuál es la opción elegida para emplear en el desarrollo de este trabajo.

| Protocolo                         | Bluetooth  | ZigBee                       |

|-----------------------------------|------------|------------------------------|

| Estándar                          | 802.15.1   | 802.15.4                     |

| Tasa de transmisión máxima (kbps) | 1000       | 250                          |

| Rango de transmisión (m)          | 1-100      | 1-100                        |

| Nº de nodos en la red             | hasta 10   | ilimitado (2 <sup>6+</sup> ) |

| Vida media de baterías (días)     | 1-10       | 100-1000+                    |

| Tiempo típico de acceso a la red  | 3 segundos | 30 milisegundos              |

| Mejor característica              | Coste      | Seguridad, Consumo,<br>Coste |

Tabla 2.1 – Comparativa entre protocolos

\_

<sup>&</sup>lt;sup>1</sup> Para más información, acudir a su web: http://www.zigbee.org/

<sup>&</sup>lt;sup>2</sup> Nota de prensa a fecha de 14 de Octubre de 2015:

http://www.indracompany.com/noticia/indra-se-adhiere-zigbee-alliance-impulsar-desarrollo-estandares-comunicaciones-iot

A la vista del cuadro comparativo, teniendo en cuenta que la velocidad de transmisión no es un requisito crítico en una red de sensores inalámbricos que se pueda embarcar en un satélite, se establece que el protocolo seleccionado es ZigBee. Básicamente las características de bajo consumo y su versatilidad para formar diferentes tipos de redes con múltiples dispositivos, convierten a este protocolo en una solución muy adecuada al problema de implementar un sistema de comunicaciones inalámbrico para aplicaciones intra-satelitales.

### 2.2. Capa física del protocolo ZigBee

ZigBee como cualquier otro protocolo de comunicación, posee una torre de protocolos con la cual se pueden desarrollar todo tipo de aplicaciones a nivel de usuario que funcionen bajo una transmisión radio compatible con el estándar ZigBee. En este trabajo sólo se va a implementar la capa física ya que sólo resulta de interés el hecho de poder transmitir una trama y analizar si el receptor es capaz de recuperar la información de usuario aun cuando la trama ha sufrido ataques mediante una inyección de fallos.

Las funciones de la capa física del estándar 802.15.4 son:

- Activación y desactivación del transmisor/receptor

- Os Detección de energía dentro de cada canal específico

- CCA (Copying Collision Avoidance) para CSMA (Carrier Sense Multiple Access)

- Selección de la frecuencia de canal

- C3 Transmisión y recepción de datos

En el estándar también se proporcionan las especificaciones para la transmisión en las distintas bandas de frecuencia donde puede trabajar. Se muestra en la tabla 2.2 dichas especificaciones centradas en la frecuencia de 2.4 GHz ya que es la que resulta de mayor interés (es la más utilizada por ser común en la normativa europea y americana).

| Frecuencia<br>capa física | Banda de<br>frecuencia | Parámetros de espectro<br>expandido |            | Parámetros del flujo de datos |                                    |                 |

|---------------------------|------------------------|-------------------------------------|------------|-------------------------------|------------------------------------|-----------------|

| (MHz)                     | (MHz)                  | Tasa de chips<br>(kchips/s)         | Modulación | Tasa de<br>bit<br>(kbps)      | Tasa de<br>símbolo<br>(ksimbolo/s) | Símbolos        |

| 2450                      | 2400-<br>2483,5        | 2000                                | O-QPSK     | 250                           | 62,5                               | 16<br>ortogonal |

Tabla 2.2 – Especificaciones para la transmisión en la banda de 2,4 GHz

### 2.3. Estructura del transmisor

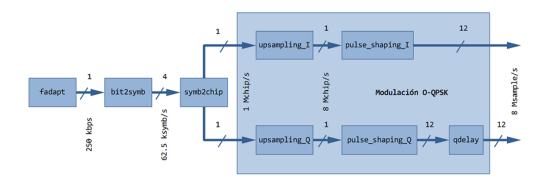

Antes de que se detallen todos los bloques que conforman el diseño digital del transmisor ZigBee en el siguiente capítulo, se muestra en la figura 2.1 un diagrama con la estructura que se va a implementar. Se indica también el ancho de los buses del flujo de datos (en número de bits) y las tasas de transmisión que han de cumplirse según establece el estándar 802.15.4 a lo largo de la etapa del transmisor.

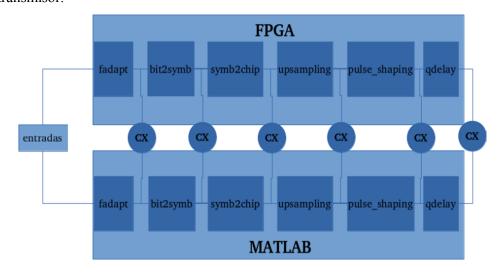

Figura 2.1 – Esquema de bloques del transmisor ZigBee

Queda presentada la solución propuesta para diseñar un transmisor inalámbrico preparado para funcionar siguiendo el protocolo de comunicación ZigBee. En los siguientes capítulos se detalla todo el proceso de diseño de los bloques que forman el transmisor así como las técnicas de verificación que se han empleado con el objeto de asegurar un diseño que cumpla con los requisitos de transmisión de señal de la capa física del protocolo ZigBee (capítulo 3). Seguidamente, se realizan pruebas de inyección de fallos sobre el diseño para conocer la robustez estructural del transmisor y del propio sistema inalámbrico completo (capítulo 4). Finalmente, se muestran los resultados obtenidos tras realizar las pruebas de inyección de fallos (capítulo 5) y se expresan las conclusiones que se extraen tras analizar todos los resultados así como se describen los trabajos futuros que pueden realizarse a raíz de los resultados que ofrece este trabajo (capítulo 6).

## Capítulo 3

### Desarrollo del Transmisor

Este capítulo se considera el más relevante ya que en él se justifica, describe y detalla el diseño del transmisor inalámbrico, elemento principal del desarrollo del presente trabajo. Se contemplan aspectos como el diseño a alto nivel del transmisor, las principales consideraciones establecidas para su implementación y una primera prueba de verificación a nivel funcional.

### 3.1. Diseño de la arquitectura hardware

El diseño del transmisor, en referencia al hardware que implementa la capa física del protocolo ZigBee, consta de ciertos módulos que forman la arquitectura del transmisor mostrada en el capítulo anterior y que se describen en el presente capítulo, pero para este trabajo se han diseñado además una serie de librerías propias con el fin de realizar una verificación funcional del propio transmisor. Dicha verificación, la cual se detalla en este capítulo, realiza una comparación de salidas o *crosscheck* entre el funcionamiento de cada bloque del transmisor comparando un modelo en Matlab y el diseño en VHDL.

Hay que indicar que tanto dichas librerías de verificación como el entorno de pruebas no han sido desarrolladas por el alumno exclusivamente, aunque sí ha colaborado en el estudio inicial y parte de las etapas de desarrollo y pruebas de dichas librerías junto con otros participantes del proyecto Edelweiss.

### 3.1.1. Consideraciones de implementación

Antes de comenzar a describir los diferentes módulos que conforman el diseño hardware del transmisor, es importante destacar ciertas consideraciones que se han tenido en cuenta antes de realizar el trabajo. Estos requisitos simplemente ayudan a que el código en VHDL sea más legible y aporta una mayor facilidad a la hora de realizar futuras modificaciones si fueran necesarias. Además, el primer requisito que se expone es obligatorio para tener un control total en el proceso de inyección de fallos como se verá en el capítulo 4.

- No se instanciará ningún módulo propiedad de Xilinx. El empleo de primitivas de Xilinx hace que dichos módulos sean 'cajas negras' en el diseño, impidiendo la observación de sus registros y su estructura interna. Con ello se pierde control a la hora de inyectar fallos en dichas primitivas y en este trabajo se busca tener una total transparencia en el 100% del diseño en cuanto a observación de registros principalmente. Por tanto, cada módulo se implementa con un código VHDL propio. Lo que se trata de conseguir es prototipar un futuro ASIC y por ello es incompatible el uso de cualquier primitiva de código cerrado desarrollada por terceros.

- Las máquinas de estado siempre considerarán una evolución segura a través de la sentencia 'when others =>' en la lógica de decodificación de estados. Esto evita posibles situaciones de bloqueo y poder volver a un estado conocido.

- Todas las declaraciones de componentes, de tipos de datos y de aquellas constantes que sean comunes a varios módulos se agruparán en un mismo 'package' VHDL común a todo el proyecto. En este trabajo hay una para los bloques del diseño digital del transmisor ZigBee denominada 'edelweiss\_common', y otra para los módulos empleados en los tests de verificación denominada 'vhdl\_verification'.

- Para tener una implementación aislada de la capa física hay que generar previamente unas tramas de unidades de datos de servicio, las denominadas como 'PSDU' (*Physical Service Data Unit*), que emulan la información proveniente de capas superiores. Con este fín, parte del equipo del proyecto ha desarrollado un bloque denominado 'datagen', el cual recibe como parámetros de entrada el número de PSDUs a generar y la longitud en bytes la propia PSDU. Este bloque proporciona como salida una secuencia de bits que se leen de un fichero especificado mediante un *generic* en la entidad del bloque.

- El esquema del transmisor ZigBee visto en el capítulo anterior muestra una serie de tasas de transmisión de datos entre distintos bloques que hay que cumplir para que funcione el protocolo de comunicación de manera correcta. En concreto hay tres cambios de tasas dentro del esquema y por ello hay tres bloques que deben incorporar un mecanismo que sea capaz de gestionar el flujo de bits para alcanzar la tasa necesaria a la salida. Con este fin, se han implementado unos contadores (en los bloques afectados) que según un parámetro denominado *THROUGHPUT*<sup>3</sup>, llevan la cuenta de los ciclos de reloj necesarios para ofrecer un flujo de datos a la salida con la tasa de bits que le corresponde. El hecho de que sea parametrizable, permite adaptar de una forma sencilla los bloques desarrollados, a diferentes frecuencias de reloj y tasas de datos.

### 3.1.2. Implementación de la arquitectura

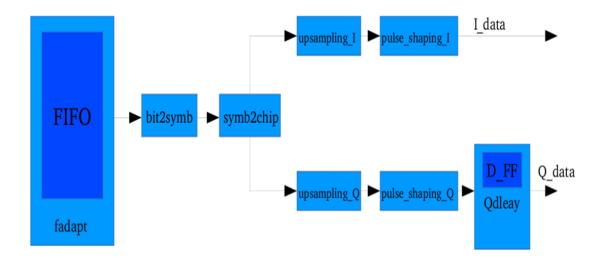

Este apartado detalla el principal trabajo que ha desarrollado el alumno. Se describen todos los módulos que implementan la capa física del transmisor. Para visualizar con una mayor claridad el sistema a diseñar, se muestra a continuación el esquema de bloques completo:

Figura 3.1 - Esquema de la capa física del transmisor

30

<sup>&</sup>lt;sup>3</sup> Se define el *throughput* como el número de ciclos de reloj tras los cuales el bloque da una nueva salida.

#### 3.1.2.1. FADAPT

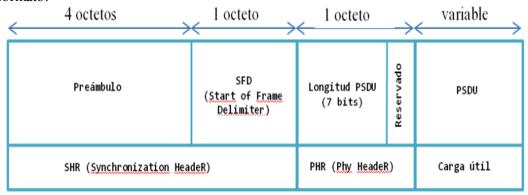

Este bloque se encarga de la conformación de la trama de datos de la capa física, denominada como '**PPDU**' (*Physical Protocol Data Unit*). La trama sigue el siguiente formato:

Figura 3.2 – Trama PPDU

La trama comienza con cuatro octetos con todos sus bits puestos a valor '0' lógico, formando el preámbulo y a continuación un octeto indicador de comienzo de trama o SFD. El valor del campo SFD se corresponde con el valor 'A7' en hexadecimal tal y como se muestra en la siguiente tabla:

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

| Valor | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

Tabla 3.1 – Valores del campo SFD

Con esto se tiene completa la cabecera de sincronización o SHR. Posteriormente, se encuentra la cabecera de la capa física o PHR formada por un único octeto que consta de 7 bits que indican el tamaño de la trama de datos de servicio o '**PSDU**' (*Physical Service Data Unit*) en octetos, más un bit reservado. Finalmente se transmite la carga útil proveniente de las capas superiores cuya información viene integrada en la PSDU.

La manera en la que funciona este bloque es sencilla. Contiene un bloque que trabaja como una FIFO y almacena los datos de la PSDU que van llegando a la entrada del sistema. Una vez la FIFO empieza a llenarse de datos, se pone en marcha una máquina de estados que va formando la trama campo a campo de manera que a la salida ofrece al siguiente bloque tanto la trama PPDU como una señal de dato válido. Esta señal funciona como una especie de habilitación y se ha diseñado todo el sistema de manera que un bloque no comienza a funcionar hasta que recibe la habilitación del bloque que le precede.

Se detalla a continuación tanto la descripción de la entidad en VHDL del bloque FADAPT como de la FIFO:

```

entity fadapt is

generic(

PSDU_LENGTH: integer := 127; -- PSDU length (bytes)

THROUGHPUT: integer := 416 -- clock cycles to reach valid data

);

port(

```

```

clk: in std_logic; -- Clock input

rst: in std_logic; -- Active high reset

psdu: in std_logic; -- Data input

psdu_valid: in std_logic; -- Data input is valid

ppdu: out std_logic; -- Data output

ppdu_valid: out std_logic; -- Data output is valid

full: out std_logic -- FIFO full flag

end fadapt;

entity fifo is

generic (

port (

-- Clock input

clk: in std_logic;

-- Active high reset

in std logic;

rst:

WriteEn: in std logic;

-- Write enable signal

DataIn: in std_logic_vector(DATA_WIDTH-1 downto 0); -- Data input bus

ReadEn: in std_logic; -- Read enable sign

-- Read enable signal

DataOut: out std_logic_vector(DATA_WIDTH-1 downto 0); -- Data output bus

empty: out std_logic;

full: out std_logic

-- FIFO empty flag

-- FIFO full flag

);

end fifo;

```

#### 3.1.2.2. **BIT2SYMB**

Este bloque funciona como un registro con entrada serie y salida paralelo. Su trabajo consiste en ir agrupando los bits provenientes de la PPDU de cuatro en cuatro y así obtener los diferentes símbolos que se utilizan en este sistema de transmisión.

Consta principalmente de un contador y una máquina de estados que comienzan a funcionar en cuanto recibe un primer dato. Se forman símbolos de cuatro bits que se envían al siguiente bloque junto con su correspondiente señal de símbolo válido. Se detalla a continuación tanto la descripción de la entidad en VHDL del bloque BIT2SYMB:

#### 3.1.2.3. **SYMB2CHIP**

Como ya se ha comentado, el protocolo ZigBee emplea la técnica de espectro expandido para realizar la transmisión de información. Uno de los métodos para generar una señal con esta característica consiste en asignar una secuencia pseudoaleatoria o PN (*Pseudo Noise*) a cada uno de los símbolos a transmitir.

Para este trabajo, se tienen 16 símbolos diferentes y a cada uno de ellos se le va a aplicar una secuencia PN de 32 bits tal y como se indica en la siguiente tabla:

| Nº símbolo | Símbolo binario (b0, b1, b2, b3) | Secuencia de expansión<br>[0,, 31] |

|------------|----------------------------------|------------------------------------|

| 0          | 0000                             | 11011001110000110101001000101110   |

| 1          | 1000                             | 11101101100111000011010100100010   |

| 2          | 0100                             | 00101110110110011100001101010010   |

| 3          | 1100                             | 00100010111011011001110000110101   |

| 4          | 0010                             | 01010010001011101101100111000011   |

| 5          | 1010                             | 00110101001000101110110110011100   |

| 6          | 0110                             | 11000011010100100010111011011001   |

| 7          | 1110                             | 10011100001101010010001011101101   |

| 8          | 0001                             | 10001100100101100000011101111011   |

| 9          | 1001                             | 10111000110010010110000001110111   |

| 10         | 0101                             | 01111011100011001001011000000111   |

| 11         | 1101                             | 01110111101110001100100101100000   |

| 12         | 0011                             | 00000111011110111000110010010110   |

| 13         | 1011                             | 01100000011101111011100011001001   |

| 14         | 0111                             | 10010110000001110111101110001100   |

| 15         | 1111                             | 11001001011000000111011110111000   |

Tabla 3.2 – Secuencias PN asociadas a cada símbolo

Este bloque también se encarga de dividir la señal de información en dos flujos de bits, es decir; a partir de la recepción de los símbolos a la entrada, genera a la salida una componente en fase y una componente en cuadratura de la señal de información, denominadas como *chips*. El método empleado consiste en asignar los valores pares de la secuencia de expansión correspondiente (se numera al bit menos significativo con el 0 y al más significativo con el 31) a la componente en fase (I) y los impares a la componente en cuadratura (Q). El criterio que se ha establecido para el orden de la transmisión de los bits (*endianness*) es que el primer byte transmitido es el byte menos significativo y dentro de cada byte, el primer bit transmitido es el bit menos significativo.

Básicamente, el funcionamiento de este bloque está dirigido por una única máquina de estados que va asignando cada uno de los bits de la secuencia PN, que corresponde al símbolo que recibe a la entrada, a los chips de salida y así formar los flujos de bits de las componentes de fase y cuadratura. La descripción de la entidad en VHDL es la siguiente:

```

entity symb2chip is

generic (

THROUGHPUT: integer := 104

-- clock cycles to reach valid data

port (

in std_logic;

-- Clock input

clk:

-- Active high reset

in std logic;

rst:

symb: in std_logic; -- Data input bus symb_valid: in std_logic; -- Data output (ph

-- Data input is valid

-- Data output (phase)

i_data_valid: out std_logic;

-- Data output is valid (phase)

out std logic;

-- Data output (quadrature)

q data:

q_data_valid: out std logic

-- Data output is valid (quadrature)

) :

end symb2chip;

```

#### 3.1.2.4. UPSAMPLING

Este bloque es el primero de los tres que conforman el proceso de modulación O-QPSK de la señal a transmitir. La tarea de este bloque es sobremuestrear las señales de entrada (componentes en fase y cuadratura) aplicando tantas muestras como coeficientes se empleen en el filtro de conformación de onda. Para este trabajo se ha decidido optar por una tasa de sobremuestreo de N=8, con lo que se aumenta x8 la tasa de transmisión de las señales a la salida. Como la señal de transmisión puede tener tres posibles valores [-1, 0, +1], la salida de este bloque viene dada por dos bits.

De manera gráfica, se muestra a continuación el proceso de sobremuestreo que se realiza en este bloque:

Figura 3.3 – Sobremuestreo para N=8

El diseño en VHDL consta de una máquina de estados que convierte un '1' lógico a la entrada como '01' (valor +1 de la señal de transmisión) y un '0' lógico como '11' (valor -1 de la señal de tansmisión). A su vez, un contador controla el número de ciclos de reloj necesarios para ir rellenando con muestras a cero ('00') con el fin de introducir el sobremuestreo que se ha definido. La entidad en VHDL de este bloque es la siguiente:

```

entity upsampling is

generic (

THROUGHPUT: integer := 13;

-- clock cycles to reach valid data

N:

integer := 8

-- number of samples

port(

in std_logic;

in std_logic;

-- Clock input

clk:

-- Active high reset

rst:

upsin: in std_logic;

upsin_valid: in std_logic;

upsout:

-- Data input

-- Data input is valid

out std logic vector(1 downto 0); -- Data output bus

upsout_valid: out std_logic

-- Data output is valid

end upsampling;

```

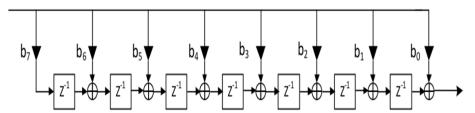

#### 3.1.2.5. PULSE SHAPING

El filtro conformador de onda, diseñado por parte del equipo que se encarga del entorno en Matlab, se conoce como *half-sine*. Contiene ocho etapas (por este motivo se utiliza una tasa de sobremuestreo de N=8) y se aplica de forma paralela tanto al flujo de entrada de la componente en fase (I) como en cuadratura (Q).

Todos los coeficientes son valores positivos y para una ganancia en DC normalizada y tasa de sobremuestreo de N=8, se han obtenido los siguientes valores:

| Coeficiente                                | <b>b</b> 0 | <b>b1</b> | <b>b2</b> | <b>b3</b> | b4     | <b>b</b> 5 | <b>b6</b> | <b>b</b> 7 |

|--------------------------------------------|------------|-----------|-----------|-----------|--------|------------|-----------|------------|

| Valor natural                              | 0          | 0.0761    | 0.1405    | 0.1840    | 0.1988 | 0.1840     | 0.1405    | 0.0761     |

| Valor cuantizado<br>en 8 bits<br>[0,, 255] | 0          | 98        | 180       | 236       | 255    | 236        | 180       | 98         |

Tabla 3.3 - Coeficientes del filtro conformador de onda

El valor cuantizado se obtiene al asignar con el valor 255 al máximo coeficiente y el resto se calcula de forma proporcional. La estructura hardware que representa el funcionamiento de este filtro se representa en la siguiente figura:

Figura 3.4 – Estructura del filtro conformador de onda

La finalidad de este filtro es cumplir con las especificaciones del estándar establecidas con la máscara de transmisión. Estas especificaciones definen una limitación de potencia transmitida fuera de los límites de la banda de frecuencias definida para cada canal. La conformación de la onda hace que los lóbulos laterales de la señal queden lo suficientemente atenuados para no afectar a los canales adyacentes.

Visto el diseño del filtro desde el punto de vista del procesamiento de señal mediante Matlab, en el dominio digital, el diseño en VHDL resulta más sencillo de realizar. Como los posibles valores de las entradas se encuentran en el conjunto [-1, 0, +1], los multiplicadores que aparecen en la estructura hardware del filtro (ver figura 3.4) se convierten en un sencillo bloque lógico que cambia el signo del coeficiente en el caso de que la entrada sea -1, mantiene el valor del coeficiente en el caso de que la entrada sea 1 o simplemente da un resultado nulo para el resto de los casos. De esta manera se simplifica el diseño y se optimizan recursos de la FPGA donde se vaya a implementar. El resto de elementos son sumadores y registros que retrasan las muestras un ciclo tal y como se indica en el esquema de la figura 3.4. Este es el segundo bloque que forma parte de la modulación O-QPSK cuya entidad en VHDL es la siguiente:

```

entity pulse shaping is

port (

clk:

in std logic;

-- Clock input

rst:

in std logic;

-- Active high reset

in std_logic_vector(1 downto 0); -- Data input bus

filterin:

filterin valid: in std_logic;

-- Data input is valid

out std logic vector(11 downto 0);-- Data output bus

filterout:

filterout valid: out std logic

-- Data output is valid

end pulse shaping;

```

### 3.1.2.6. **QDELAY**

Se trata del tercer y último bloque que forma la modulación O-QPSK y el motivo de su uso viene dado como consecuencia del empleo de una modulación QPSK. Dicha modulación puede tomar cuatro valores de la fase a la vez para construir un símbolo de la constelación permitiendo que la fase de la señal salte hasta 180°. Estos saltos abruptos de fase en las componentes I y Q dan como resultado fuertes variaciones de su envolvente y hace que sea necesaria la inclusión de amplificadores con altas prestaciones de linealidad.

En la práctica se emplea una variante de la modulación QPSK que introduce una compensación o desviación de la sincronización entre las componentes en fase y cuadratura. Esta compensación se consigue retrasando a una de las componentes (en este trabajo se ha decidido por retrasar la componente compleja, Q) por medio periodo que equivale a un retraso de 4 muestras ya que se realiza un sobremuestreo de 8.

Gracias a esto, con la modulación O-QPSK se evitan las transiciones de 180° ya que ambas componentes nunca cambian a la vez, así se consigue una envolvente con menores variaciones que requiere unos requisitos de linealidad inferiores que en el caso de la QPSK.

El diseño en VHDL de este bloque se compone de la generación de cuatro instancias de un bloque básico de registro denominado d\_ff (flip-flop tipo D). De esta manera las muestras que forman la componente en cuadratura van pasando por este bloque que consigue el retraso de 4 muestras necesario para la modulación O-QPSK tal y como se ha indicado.

Se muestra a continuación un esquemático que muestra la composición de este bloque:

Figura 3.5 – Estructura del bloque QDELAY

Las entidades en VHDL que forman parte de este bloque son dos, por un lado el propio quelay y por otro el módulo básico de registro d ff:

```

entity qdelay is

generic (

INPUT_WIDTH: integer := 12; -- Input data width

OUTPUT WIDTH: integer := 12; -- Output data with

integer := 4 -- Number of samples to delay

):

port(

-- Clock input

clk:

in std logic;

rst: in std_logic; -- Active high re

dlyin: in std_logic_vector((INPUT_WIDTH-1) downto 0); -- Data input bus

-- Active high reset

dlyin valid: in std logic;

-- Data input is valid

dlyout: out std_logic_vector((OUTPUT_WIDTH-1) downto 0);-- Data output bus

dlyout valid: out std logic

-- Data output is valid

end qdelay;

entity d_ff is

generic (

DATA_WIDTH: integer:= 12 -- Input/output data width

port (

clk: in std_logic; -- Clock input

rst: in std_logic; -- Active high reset

datain: in std_logic_vector((DATA_WIDTH -1) downto 0); -- Data input bus

rstd_logic; -- Input enable

dataout: out std_logic_vector((DATA_WIDTH -1) downto 0) -- Data output bus

end d_ff;

```

#### 3.1.2.7. TOP TX

Finalmente, el diseño del transmisor ZigBee en VHDL incluye a todos los bloques ya descritos dentro de un módulo denominado 'top\_tx', cuyo esquema general se muestra en la siguiente figura:

Como últimos datos a destacar sobre el diseño digital que se ha desarrollado, se muestra a continuación un resumen sobre la ocupación y frecuencia máxima de trabajo que se obtiene al implementar el diseño sobre una FGPA, en concreto es un modelo de la familia Virtex 5 (5vfx70tff1136-1) del fabricante Xilinx.

#### Device utilization summary:

| Selected Device: 5vfx70tff1136-1 | Selected | Device: | 5vfx70tff1136-1 |

|----------------------------------|----------|---------|-----------------|

|----------------------------------|----------|---------|-----------------|

| Slice Logic Utilization:            |     |        |       |     |

|-------------------------------------|-----|--------|-------|-----|

| Number of Slice Registers:          | 389 | out of | 44800 | 0%  |

| Number of Slice LUTs:               | 480 | out of | 44800 | 1%  |

| Number used as Logic:               | 480 | out of | 44800 | 1%  |

| Slice Logic Distribution:           |     |        |       |     |

| Number of LUT Flip Flop pairs used: | 533 |        |       |     |

| Number with an unused Flip Flop:    | 144 | out of | 533   | 27% |

| Number with an unused LUT:          | 53  | out of | 533   | 9%  |

| Number of fully used LUT-FF pairs:  | 336 | out of | 533   | 63% |

| IO Utilization:                     |     |        |       |     |

| Number of IOs:                      | 31  |        |       |     |

| Number of bonded IOBs:              | 31  | out of | 640   | 4%  |

| Specific Feature Utilization:       |     |        |       |     |

| Number of BUFG/BUFGCTRLs:           | 1   | out of | 32    | 3%  |

#### <u>Timing Summary:</u>

Speed Grade: -1

Minimum period: 8.122ns (Maximum Frequency: 123.122MHz)

Minimum input arrival time before clock: 4.336ns Maximum output required time after clock: 3.389ns Maximum combinational path delay: No path found

## 3.2. Verificación funcional

Una vez descrito el diseño digital del transmisor ZigBee desarrollado por el alumno, se pasa a detallar el procedimiento que se ha seguido para comprobar que cada uno de los bloques funciona de manera correcta. Como ya se ha indicado anteriormente, este trabajo forma parte de un proyecto en el que intervienen varias personas. Por un lado, un grupo dedicado al desarrollo del procesamiento de señal y modelado en Matlab del transmisor ZigBee, donde se ha analizado el espectro de la señal y comprobar que la señal O-QPSK transmitida cumple con las especificaciones del protocolo de comunicación. Por otro lado, un grupo de personas encargadas de desarrollar y testear el mismo transmisor empleando una codificación VHDL, con el objeto de tener un diseño digital al que poder realizar una prueba de inyección de fallos y analizar los resultados que se obtengan.

El alumno ha formado parte del grupo referente al ámbito digital donde su tarea principal ha sido el desarrollo del transmisor que se ha descrito en este capítulo pero también ha colaborado en el proceso de elaboración de tests con los que se ha

conseguido tener un diseño que funciona correctamente gracias al método de *crosscheck* que se ha utilizado y que se explica a continuación.

#### 3.2.1. Crosscheck con modelo Matlab

El procedimiento que se ha seguido para tener un diseño digital que se comporte de igual manera que el modelo en Matlab, consiste en introducir a cada bloque por separado un mismo fichero de entradas conocidas (al modelo en Matlab y al diseño en VHDL implementado en la FPGA). El modelo en Matlab responde con unas salidas que se guardan en un archivo de texto (son valores en formato hexadecimal). Para el diseño digital se realizan una serie de *test benches*, los cuales contienen siempre a la unidad bajo test o UUT (*Unit Under Test*) y cuatro entidades no sintetizables que realizan la función de *crosscheck* según el archivo de salidas que el modelo Matlab ofrece para cada bloque.

Tabla 3.4 – Ejemplo de valores de entrada y salida para el bloque FADAPT

Las entidades no sintetizables que se han desarrollado en VHDL con objeto de poder realizar el *crosscheck* de las salidas del modelo en Matlab son las siguientes:

**C1kmanager:** Este módulo simplemente se encarga de dar ciclos de reloj al simulador mientras el test se realiza y deja de dar ciclos cuando se activa una señal de entrada denominada '**endsim**', cuyo significado es que la librería que genera las entradas ha terminado de enviar todos los datos y por tanto, debe de finalizar el test y la simulación. También se encarga de manejar el *reset* global del sistema.

La entidad en VHDL de este módulo es la siguiente:

```

entity clkmanager is

generic (

-- Period of generated clock

time

:= 10 ns;

CLK PERIOD:

-- Reset polarity

std logic := '0';

RST ACTIVE VALUE:

-- Number of cycles that reset will be asserted at the beginning of the simulation

integer := 10

RST CYCLES:

);

-- clk stops changing when endsim='1', which effectively stops the simulation

endsim:

in std logic;

```

```

-- Generated clock

clk:

-- Generated reset

rst:

out std_logic;

out std_logic

);

end clkmanager;

```

CS Datagen: Este módulo se encarga de generar los datos de entrada a cada bloque. Realiza varias funciones, es un manejador de archivos que va leyendo los valores de entrada y los pasa al simulador para que pueda trabajar con ellos, puede comprobar que los datos de entrada se encuentran entre un conjunto de valores válidos y da error si no es así y además se encarga de activar la señal de fin de simulación al resto de módulos cuando termina de enviar el último dato. También es capaz de serializar los datos que lee del fichero de entrada. La entidad en VHDL es la siguiente:

```

entity datagen is

generic (

boolean := false;

-- Print debug info

-- Print all internal details

boolean := false;

-- File where data is stored

STIMULI FILE: string := "../test/datagen test.txt";

-- Maximum hex chars for each input data

STIMULI NIBBLES: integer := 2;

-- Width of generated data

integer := 8;

DATA WIDTH:

-- Output one valid data each THROUGHPUT cycles

integer := 0;

THROUGHPUT:

-- Output value when data is not valid

datagen invalid data := unknown;

INVALID DATA:

-- Number of cycles between last data and assertion of endsim

CYCLES AFTER LAST VECTOR: integer := 10

);

port (

-- Align generated data to this clock

in std logic;

-- Active high, tells datagen it can assert valid. Use for control-flow

can_write: in std_logic;

-- Generated data

out std logic vector (DATA WIDTH-1 downto 0);

data:

-- Active high, indicates data is valid

valid: out std logic;

-- Active high, tells the other sim processes to close their open files

endsim: out std_logic

end datagen;

```

CS Datacompare: Este es el módulo encargado de hacer la comparación entre las salidas de ambos modelos. Por un lado lee las salidas del archivo que se ha obtenido del modelo en Matlab y por otro lado se va comparando línea a línea con el resultado que da la simulación del diseño en VHDL. Si existe alguna discrepancia, se detiene la simulación y se da un mensaje de error indicando el valor que se ha obtenido y cuál era el valor esperado.

Se ha desarrollado de esta manera en lugar de volcar las salidas a un fichero porque al comparar dichas salidas en tiempo de simulación, pueden ser detectados los errores mientras se ejecuta la simulación del bloque en cuestión. De esta manera se pueden obtener mensajes de error en el log del simulador justo en el instante en el que se detecta una discrepancia o error entre las salidas.

Esto permite una mayor facilidad y control de depuración del funcionamiento de los bloques, ya que se pueden ver los estados internos del circuito a la vez que se detectan los errores. Si esto se hiciera volcando las salidas a un fichero, toda la comparación es *offline*. De esta manera se han ido encontrando a lo largo de la etapa de diseño algunos errores, principalmente en el código VHDL, aunque en algunos casos también han sido detectados errores en el modelo en Matlab y así se ha llegado a obtener un transmisor ZigBee totalmente funcional en ambos modelos. La entidad en VHDL es la siguiente:

```

entity datacompare is

generic (

-- Allow to separate messages from different instances in SIMULATION

SIMULATION LABEL: string := "datacompare";

-- Print all internal details

VERBOSE: boolean := false;

-- Print debug info

boolean := false;

DEBUG:

-- File where data is stored

GOLD OUTPUT FILE: string := "../test/datacompare test.txt";

-- Maximum hex chars for each output data

GOLD OUTPUT NIBBLES: integer := 2;

-- Width of generated data

DATA WIDTH:

integer := 8

);

port (

-- Align generated data to this clock

clk:

in std logic;

-- Generated data

in std logic vector (DATA WIDTH-1 downto 0);

data:

-- Active high, indicates data is valid

valid: in std logic;

-- Active high, tells the process to close its open files

endsim:

in std logic

);

end datacompare;

```

**CSS Throughputchecker:** Esta entidad es la encargada de supervisar que las señales de dato válido se activan según la tasa de transmisión de datos esperada en cada bloque. Es básicamente un contador de ciclos de reloj que compara si en el momento en el que corresponda se activa la señal de dato válida. Su entidad en VHDL es la siguiente:

```

entity throughputchecker is

generic (

-- To separate messages from different instances in SIMULATION

SIMULATION LABEL: string := "throughputchecker";

-- Print debug info (developers only ;)

boolean := false;

-- Wait cycles between valid data. Also know as throughput

THROUGHPUT: integer := 0

);

-- Align generated data to this clock

in std logic;

-- Active high, indicates data is valid

valid: in std logic;

-- Active high, tells the process that last data from datagen was sent

endsim:

in std logic

end throughputchecker;

```

Antes de conocer el entorno de pruebas que se ha empleado, se muestra en la figura 3.7 un esquema básico de *test bench* con la idea de conocer mejor a lo que en el entorno de pruebas se define como CX (*crosscheck*).

Figura 3.7 – Esquema de un test bench básico

## 3.2.2. Entorno de pruebas

De manera más gráfica, se muestra a continuación dónde se han realizado los diferentes puntos de verificación a lo largo del desarrollo del diseño digital del transmisor.

Figura 3.8 - Esquema de crosschecks

Como se puede observar, se aplica un mismo fichero de entrada a ambos modelos y se realiza un *crosscheck* de las salidas de cada bloque, siendo la salida de un bloque la propia entrada al bloque siguiente. No se desarrolla un nuevo bloque hasta que el anterior ofrece un resultado de test positivo.

Este esquema es el que ha seguido el alumno durante la etapa de diseño del transmisor en VHDL, implementando el código en la FPGA ya mencionada anteriormente (Virtex 5: xc5vfx70tff1136-1) y verificando que los *test benches* para cada bloque dan los resultados esperados (no se producen errores y el número de datos correctos es mayor que cero).

Hay que destacar que todo el sistema de verificación que se ha descrito se ha desarrollado con herramientas de CMake (en un entorno Linux) para automatizar todo el proceso. Es decir, a partir de los ficheros fuente (.vhd) que forman el diseño digital, y mediante la ejecución de un comando llamado 'cmake' se crea todo el proyecto ISE (herramienta de síntesis del código VHDL y rutado para la FPGA objetivo), se crean los archivos de simulación para cada bloque y ejecutando el comando 'make test' se ejecutan todos los *test benches* de manera automática. Se muestra a continuación una captura de este entorno de verificación que se ha desarrollado por parte del grupo dedicado al diseño digital del transmisor.

```

sim_exec_tb_d_ff_3x127byte

test_qdelay_32bit.log

sim_exec_tb_fadapt_32bit

sim_exec_tb_fadapt_3x127byte

sim_exec_tb_fifo_32bit

test_qdelay_3x127byte.log

test_symb2chip_32bit.log

test_symb2chip_3x127byte.log