### **Advanced Silicon Interposer** for High density and High Integration **Electronic Packages**

Satoru Kuramochi<sup>1,</sup>, Sumio Koiwa<sup>1,</sup>, Takamasa Takano<sup>1,</sup> Miyuki Akazawa<sup>1,</sup> Hiroshi Mawatari<sup>1,</sup>, Kousuke Suzuki<sup>1,</sup>, Yoshitaka Fukuoka<sup>2</sup>

icle-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 <sup>1</sup>Dai Nippon Printing Co., Ltd., 2 Weisti(Worldwide Electronic Integrated Substrate Technology Ing)

Downloaded from http://m

1, Background

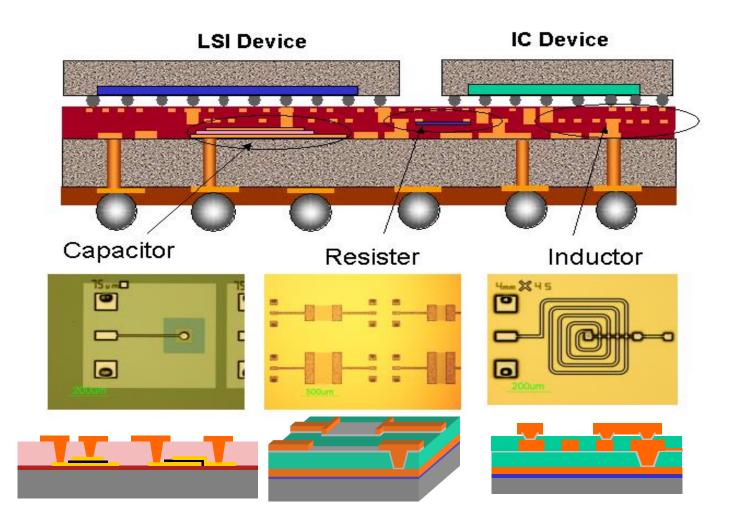

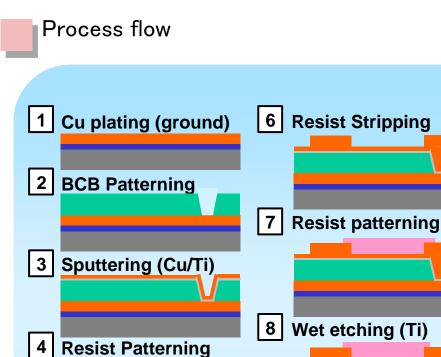

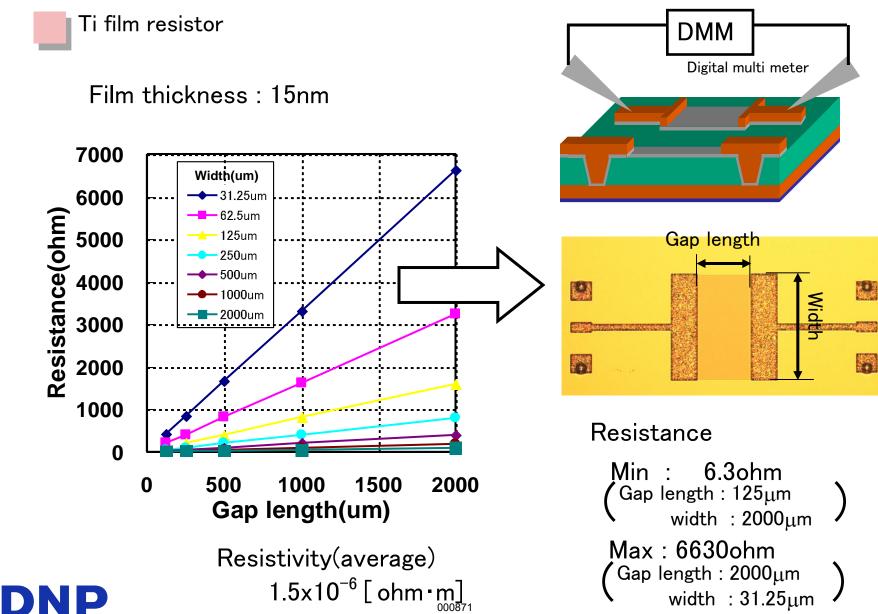

## 2, Embedded passives

## 3, Si interposer with passives

## 4, Summary

Downloaded from http://meridiar

icle-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

### Technical Conference on Device Packaging | March 16-19, 2015 | Fountain Hills, AZ USA

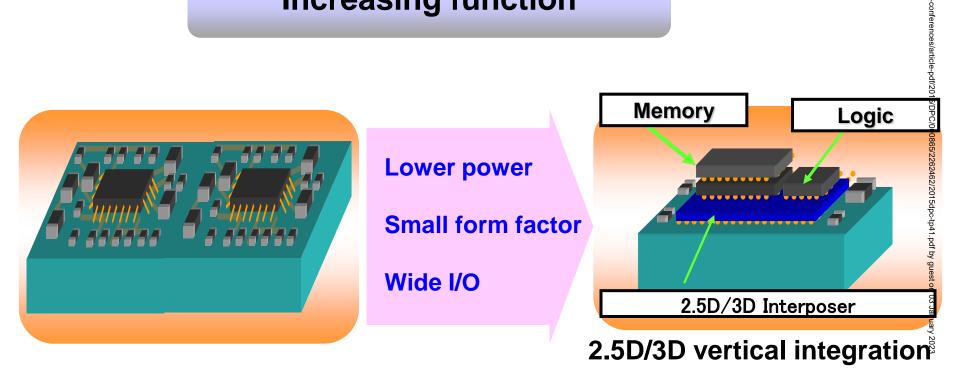

### **Electronic products:**

**Smaller and lighter**

### **Increasing function**

Downloaded from http://meridian.allenpress.com/imaps-

### Concept of development

## 1, Background

## 2, Embedded passives

## 3, Si interposer with passives

## 4, Summary

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

Resistor Layer Cu Wiring (Cr,Ti) (Plating

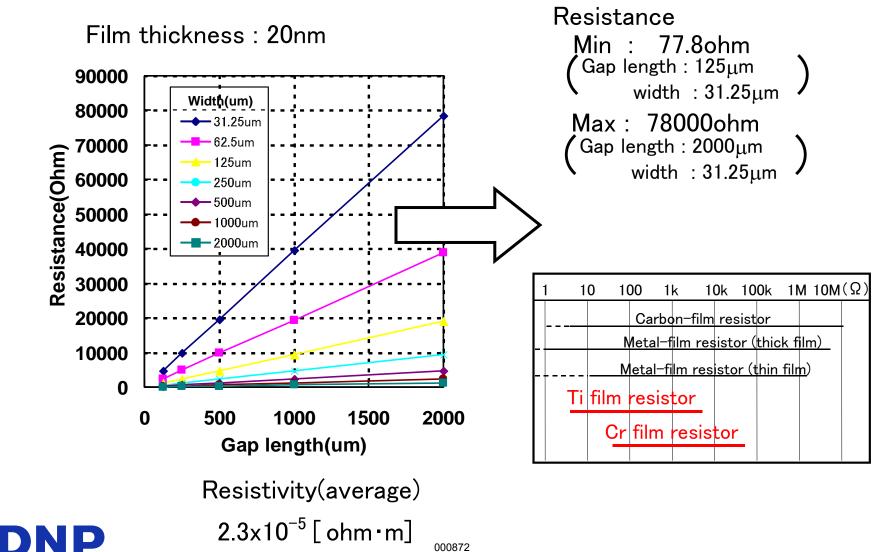

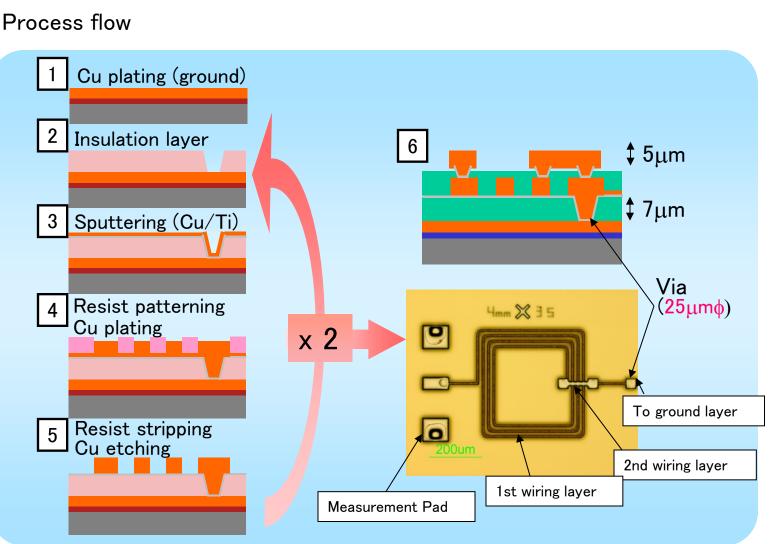

Adhesion and barrier layer in sputter semi-additive process is applied as resistor.

Both resistor and wiring can be produced in the <u>same</u> process step.

5

Cu Plating (wiring)

**Resist Stripping**

Cu etching

9

Cr film resistor

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

#### TEG pattern

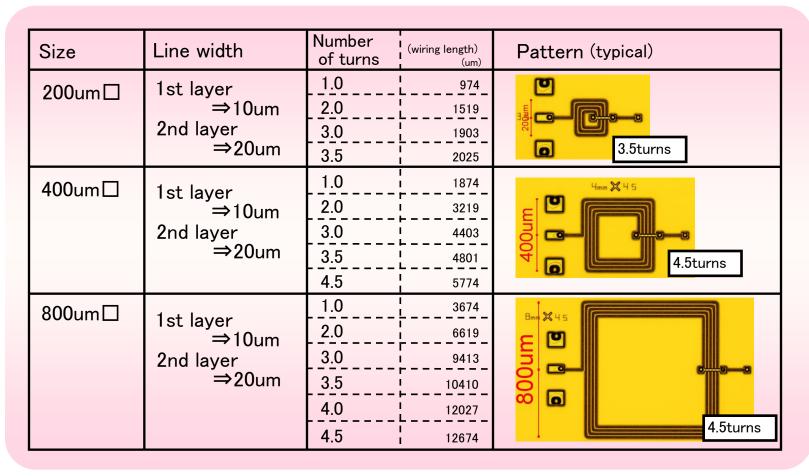

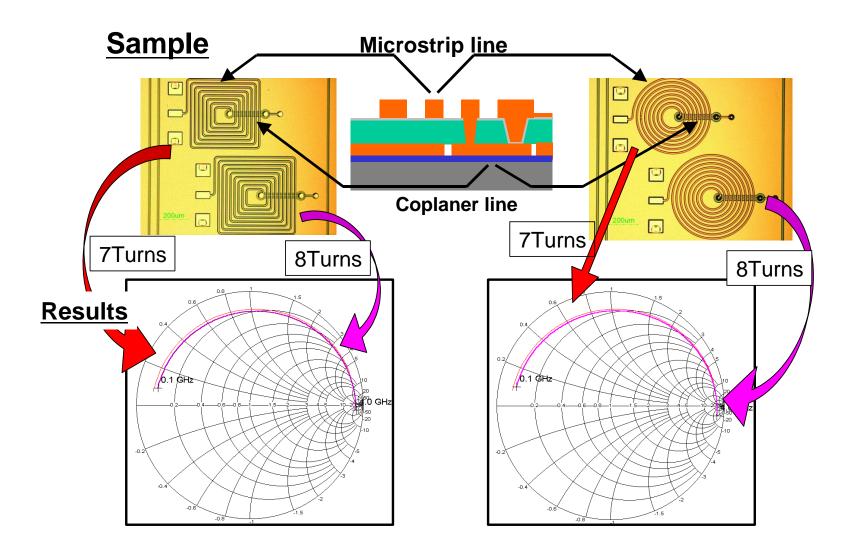

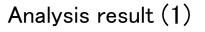

The variety of the fabricated spiral inductors are total 15 patterns

DNP

with changing size ,number of turns and wiring length.

Frequency vs. Inductance (calculated from S11 smith chart)

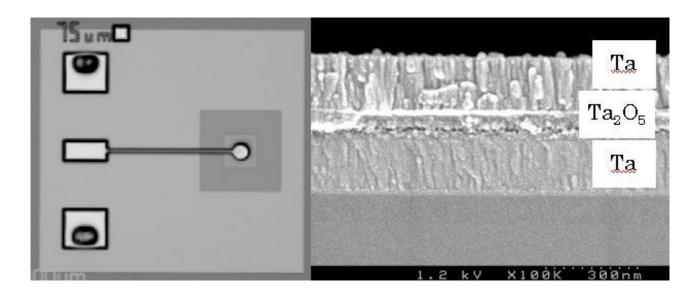

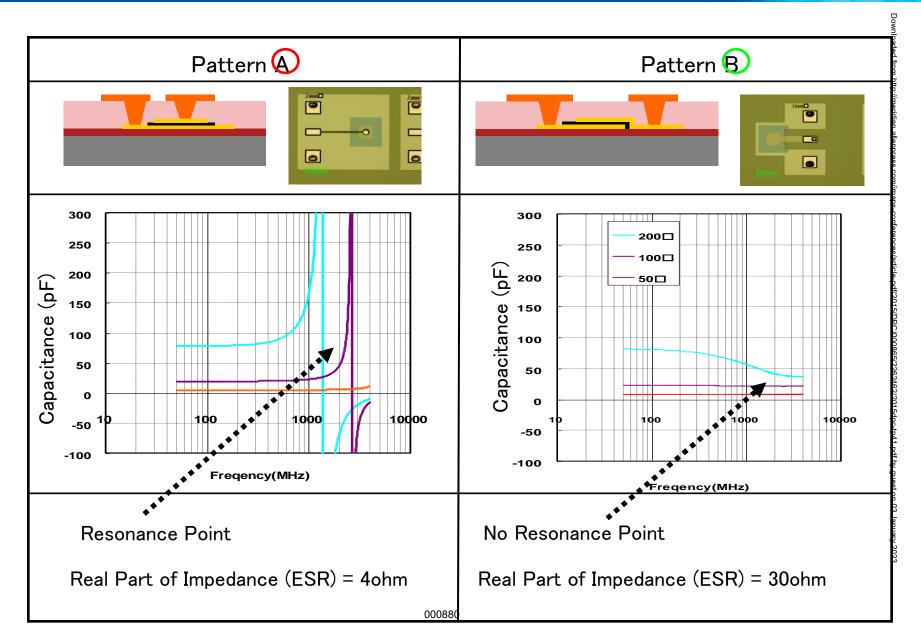

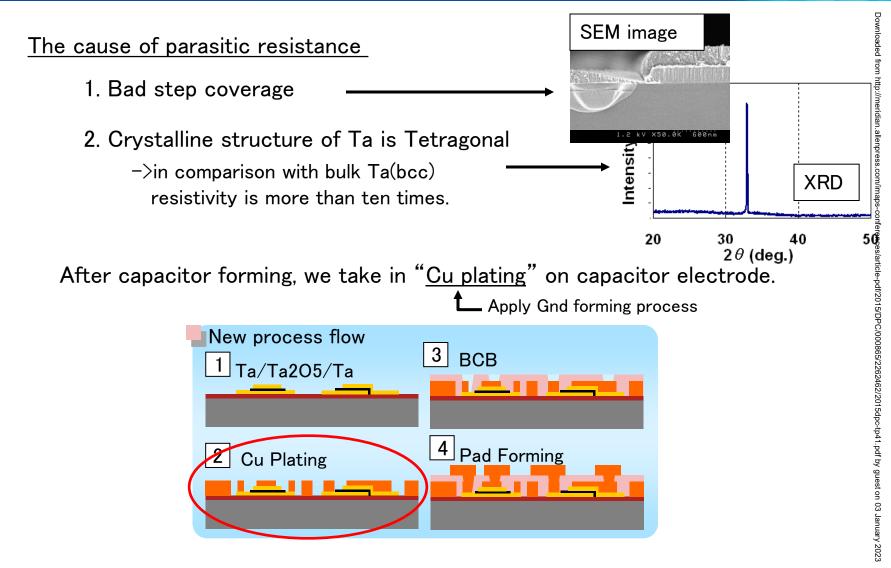

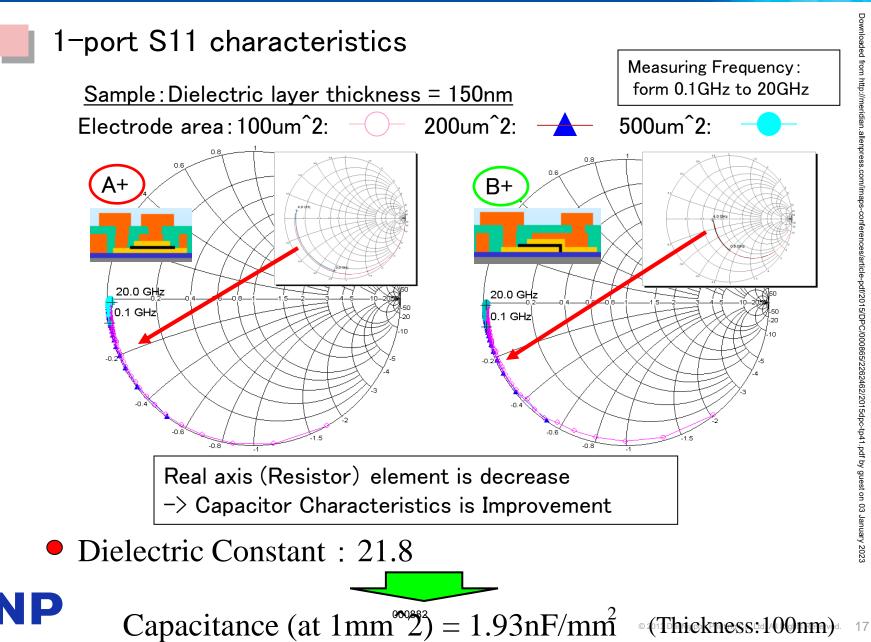

#### **Process flow** Α 4 Sputter (Top electrode) Wafer (SiO<sub>2</sub>/Si) .1 തത 0 5 Insulation layer 2 Sputter (Bottom electrode) 0 В Sputter semi-additive 6 .| 🗑 🗖 🗌 copper plating 3 Anodic oxidation pattern A pattern 3

.1 തത 0

0

0

0

•

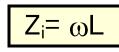

Formation process of  $Ta_2O_5$  film

#### Anodic oxidation

advantages: The oxidized film is stoichiometric (Ta/O=2/5)

The thickness is good repeatability

because the thickness is controlled by applied voltage

The equipment is simple and low price because vacuum equipment is not used

| Thickness[nm] | Size      | Capacitance[pF]   | Resonance  |

|---------------|-----------|-------------------|------------|

|               |           | (1GHz)            | Point[GHz] |

| 110           | 50um^2    | 4.8               | >4GHz      |

|               | 100um^2   | 19.5              | 2.58       |

|               | 200um^2   | 78.4              | 1.38       |

| 137           | 50um^2    | 3.9               | >4GHz      |

|               | 100um^2   | 15.9              | 2.97       |

|               | 200um^2   | 64.0              | 1.45       |

| 182           | 50um^2    | 2.9               | >4GHz      |

|               | 100um^2   | 11.9              | 3.27       |

|               | 200um_027 | <sub>9</sub> 48.2 | 1.76       |

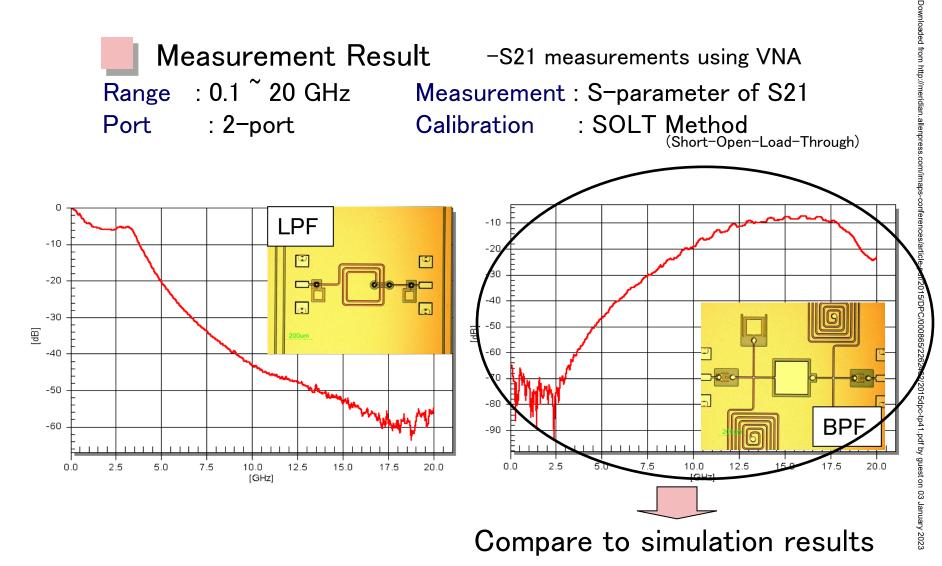

The Characteristic of Individual passive components could be measured.

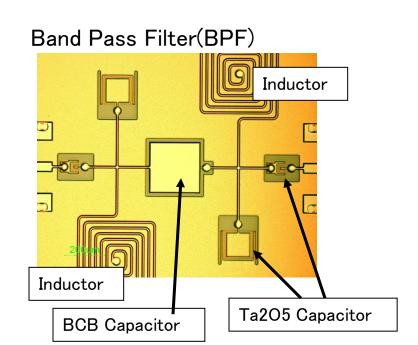

Trial production of integrated LC filter

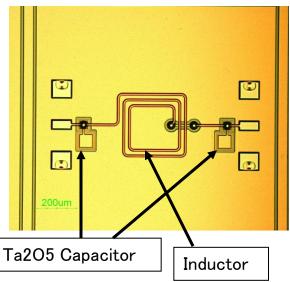

### Sample Picture

Low Pass Filter(LPF)

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

DNP

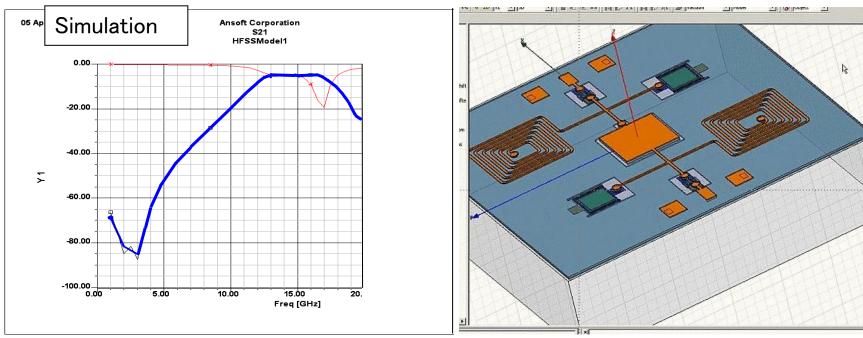

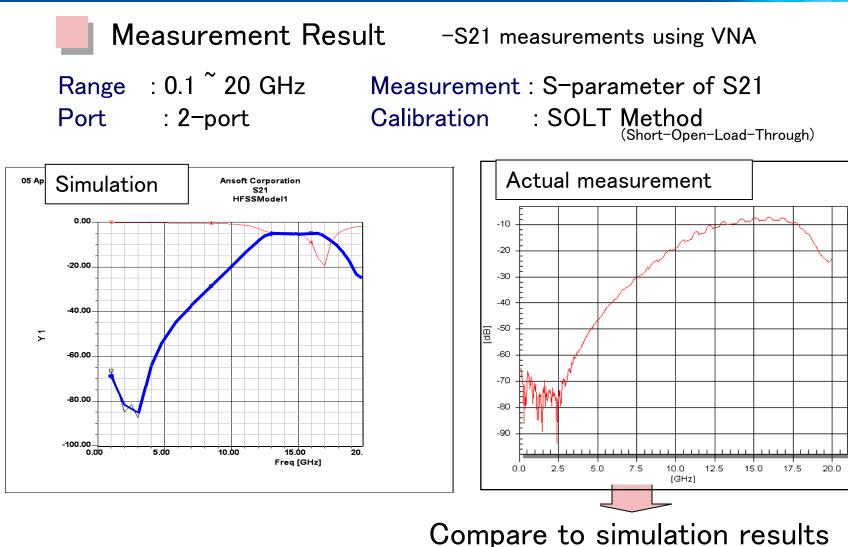

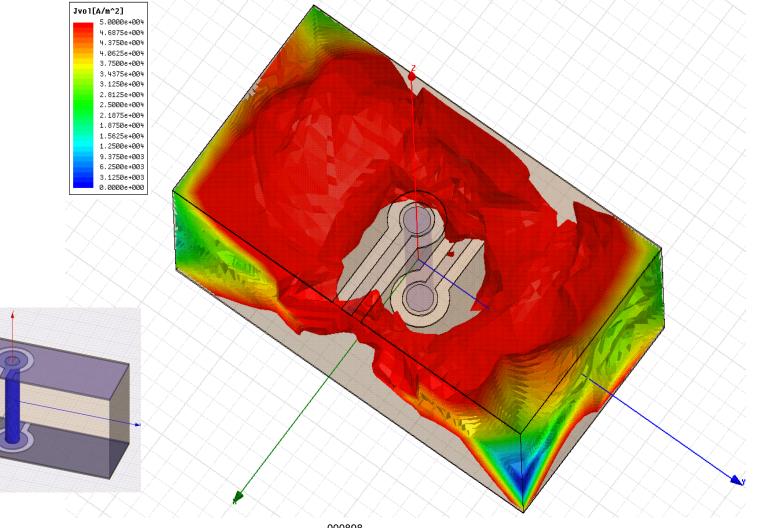

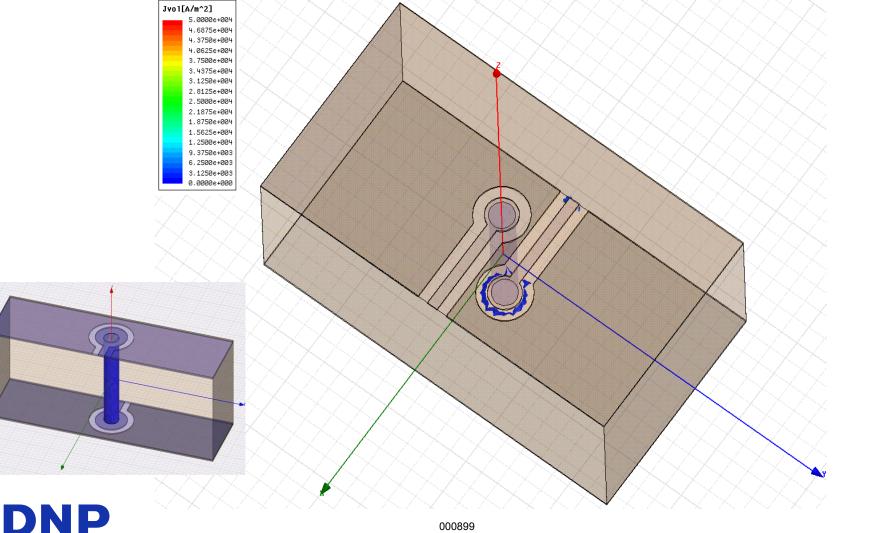

#### Simulation Result

#### Simulator: 3D Electromagnetic-Field Simulator (FEM) [ansoft HFSS]

The result is in good agreement with actual measurement.

$\rightarrow$ Our simulation is able to use for filter design

## 1, Background

## 2, Embedded passives

## 3, Si interposer with passives

## 4, Summary

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

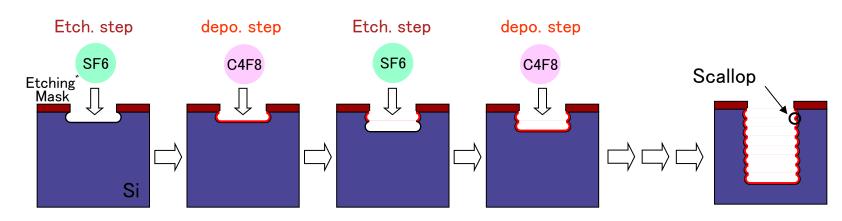

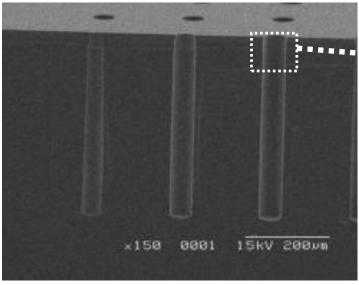

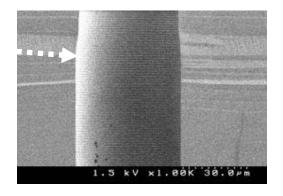

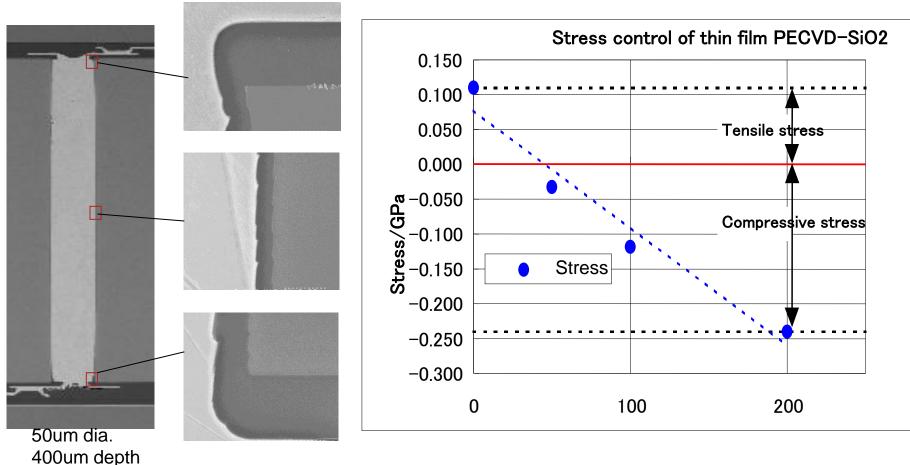

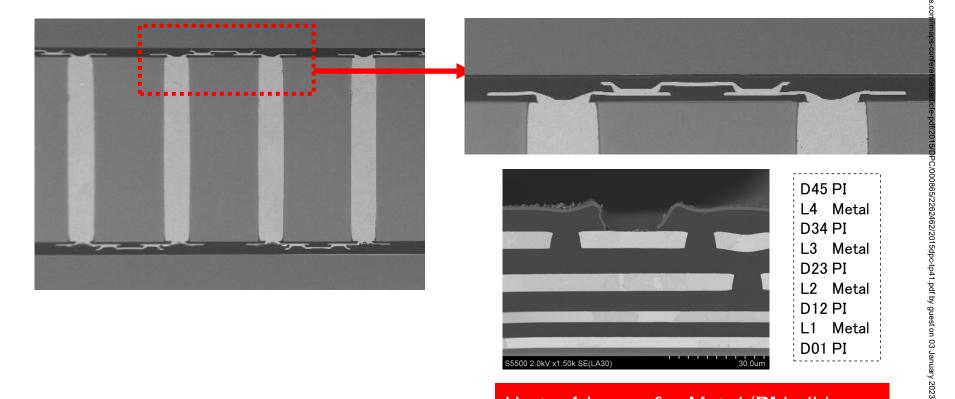

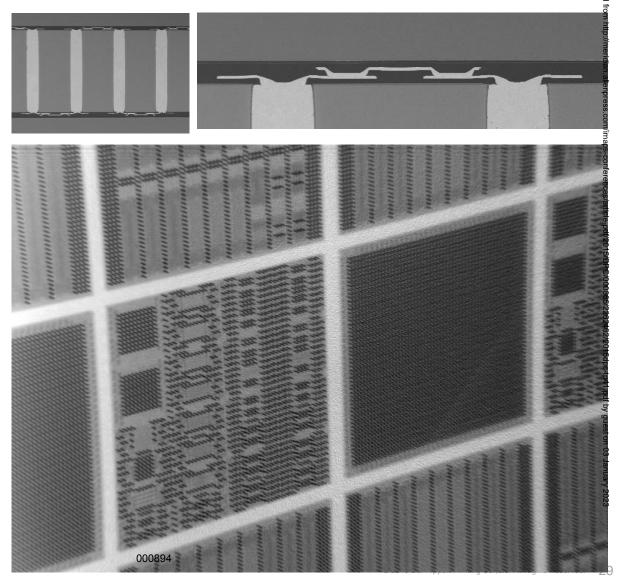

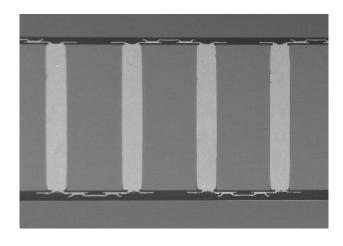

### **Deep-RIE Bosch Process**

#### Straight and smoth surface hole

000888

### **Coverage oxicide of inner holes**

#### -Using PECVD for low stress process-

icle-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 202 24

Downloaded from http://meridia

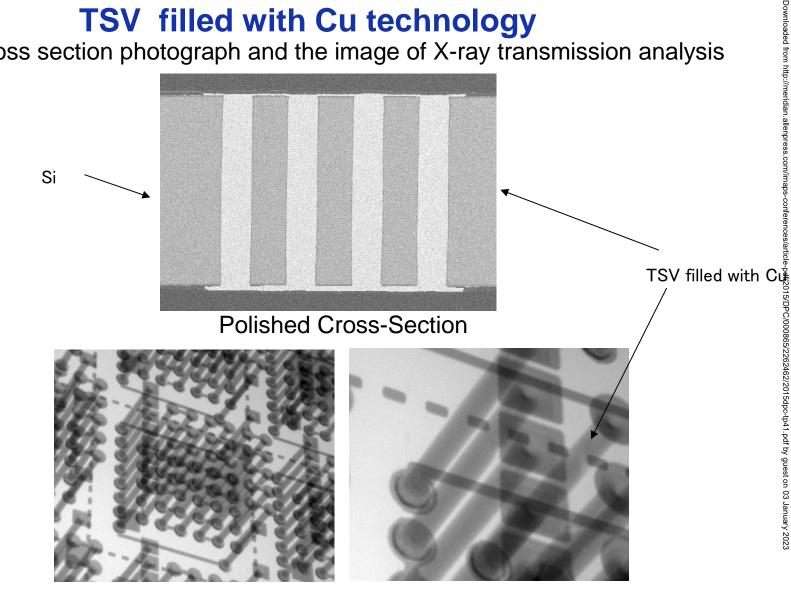

### **TSV** filled with Cu technology

The cross section photograph and the image of X-ray transmission analysis

#### Example of optimized PPR method Condition B

Condition A

Void remain in the cupper plug.

no voids in the cupper through plug.

# Good filling characteristic is obtained by process control with liquid flow and ion delivery and current density in the hole

### **RDL (Re-Distribution Layer)**

RDL consists of fine wiring layer formed by SAP(sputter semi-additive process) Double sided dielectric layer PI formed by the photo-via process

Up to 4 layers for Metal/PI build up

Downloaded from http://meridiar

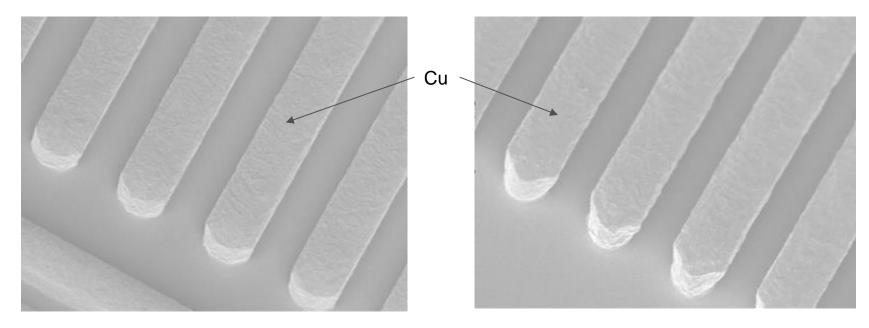

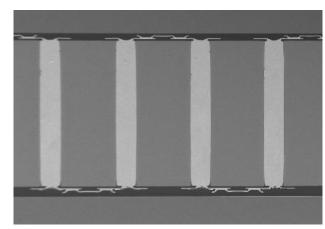

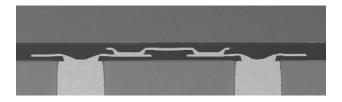

### Fine Cu wiring fabricated by SAP(semi-additive process)

#### L/S=5um/5um

L/S=3um/3um

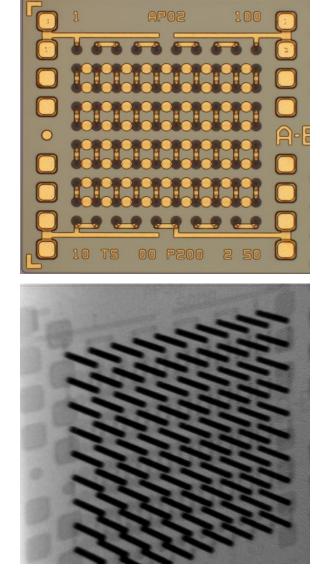

### **Demonstrated Test Element Group (TEG)**

Download

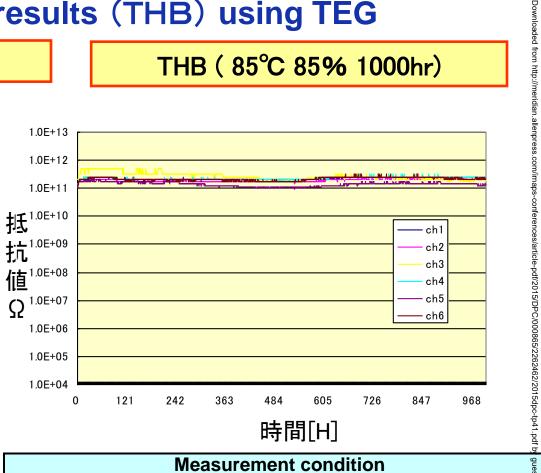

### **Reliability test results (THB) using TEG**

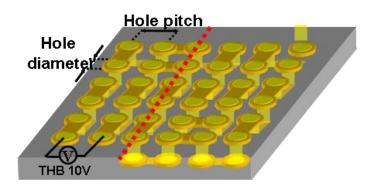

#### The schematic view of Sample

THB (85°C 85% 1000hr)

| Measurement condition |      |                |        |  |

|-----------------------|------|----------------|--------|--|

| Temperature           | 85°C | Hole diameter  | 50um   |  |

| Humidity              | 85%  | Hole pitch     | 200um  |  |

| Additive V            | 10V  | Number of Hole | 100x2  |  |

| Measurement V         | 10V  | Time           | 1000hr |  |

000895

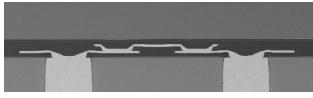

### **Reliability test results (TCT)**

Double side thick polymer insulator that buffers the stress created by CTE mismatch

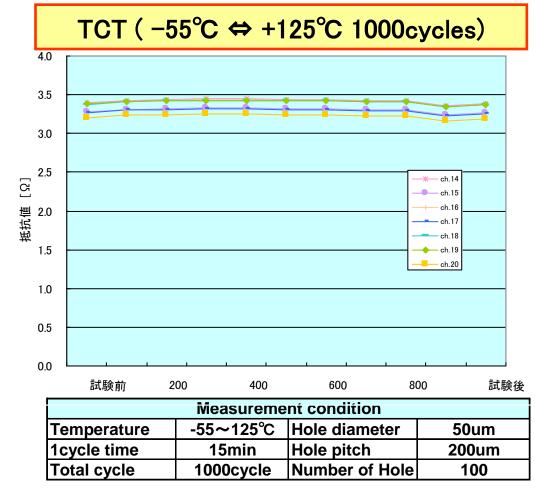

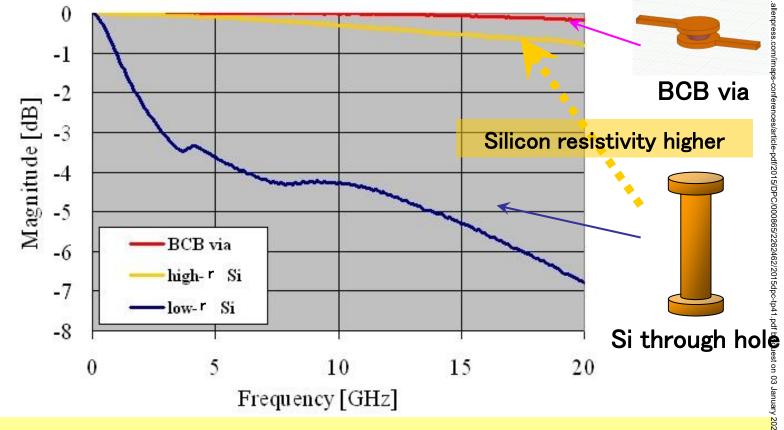

### Signal integrity for high frequency

Insertion loss (S<sub>21</sub>) Measured result

**DNP** Reducing the loss of Sinthrough hole is very important !

## 3D-electromagnetic field simulation low resistivity ( $\rho$ ) silicon whose volume resistivity is 1.5 $\Omega$ ·c m

allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023.

#### 3D-electromagnetic field simulation high resistivity ( $\rho$ ) silicon whose volume resistivity is 4000 $\Omega$ c m

.allenpress.com/imaps-conferences/article-pdf/2015/DPC/000865/2262462/2015dpc-tp41.pdf by guest on 03 January 2023

### Signal integrity for high frequency

Reduced insertion loss Insertion loss (S<sub>21</sub>) Measured result

High reisttivity Si enable to decrease the insertion loss of Si though hole 000900

DN

DNP

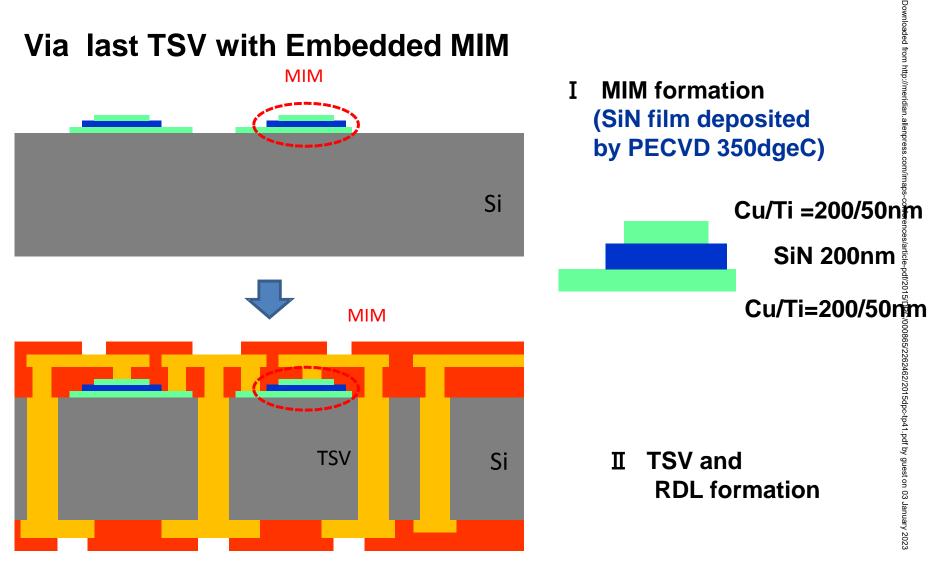

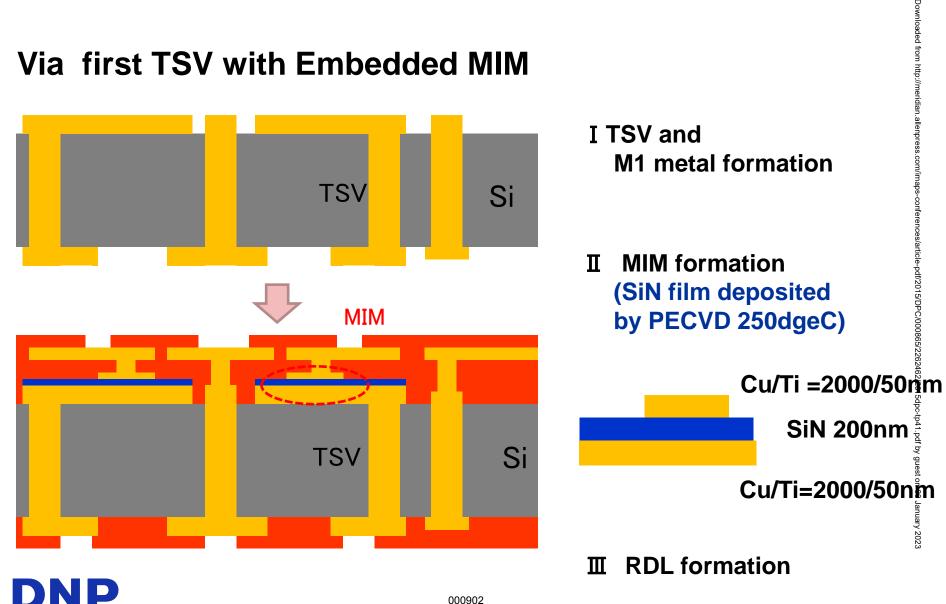

### Via first TSV with Embedded MIM

© 2013 Dai Nippon Printing Co.,Ltd. All Rights Reserved. 37

000902

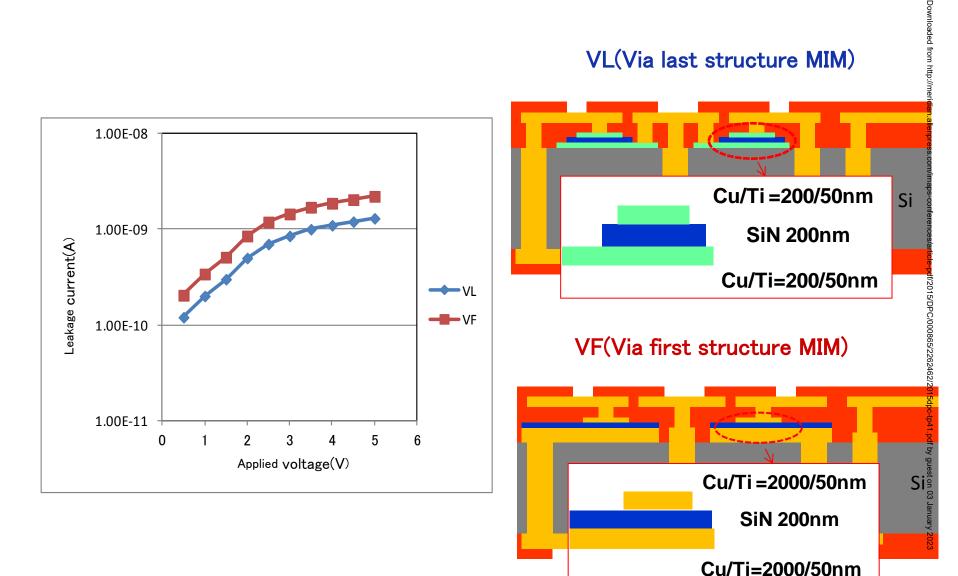

Downloaded from http://me 35 30 Si ε r= 7.3 SiN 25 PECVD 350dgeC Capacitance(nF) 20 lf/2015/DPC/000865/2262462/ VL 15 ε r= 6.2 - VF VF(Via first structure MIM) 10 5 0 f by guest on 03 January 2 0 20 40 60 80 100 MiM Size (mm2) SiN PECVD 250dgeC

### DNP

VL(Via last structure MIM)

000903

VL(Via last structure MIM)

DNP

Embedded passive devices was fabricated on Si substrate

- The measurement result of integrataed passive device was compared with simulation result.

- Thin film SiN capacitor as embedded passive device was built in surface of TSV interposer by two types method.

- The capacitance and leakage current of capacitor was compared with two types method. Capacitance of Via last MIM is higher than Via first MIM.

Summarty

3223 dpc-tp41.pdf by guest on 03 January