EE120A Logic Design Department of Electrical Engineering University of California – Riverside

Laboratory #7 EE 120 A

# LABORATORY # 7 LAB MANUAL

# **Register File Design**

# Objectives

- **1.** Design of register files, synthesis and implementation;

- **2.** Emulation of register file performance

# Equipment

- PC or compatible

- Digilent's Basys Spartan-3E FPGA Evaluation Board

# Software

- Xilinx ISE Design Software Suite 10.1

- ModelSim XE III modeling software

- Digilent's Adept ExPort Software

# Parts

• N/A

#### **Background – Register Files**

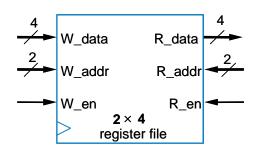

A typical datapath has multiple registers. The construction of a bus system with a large number of registers requires different techniques. A set of registers having common operations performed on them maybe organized into a register file<sup>\*</sup>. A block diagram of a 2x4 register file is shown in **Figure L7-1**. Note that in general a

register file is denoted as  $2^m \ge n$ , where *m* is the number of register address bits and *n* is the number of bits per register. In our case it is better to use a notation  $2^2 \ge 4$  register file<sup>†</sup>.

Register files have a memory-like behavior. However, they are very different from memories like SRAM, ROM, etc. as will be explained in more

Figure L7-1. Block Diagram of a 2x4 Register File

detail in class. They are generally used as <u>fast temporary storage</u>. Brief comparative properties are outlined in **Table L7-1** below.

| Register File                           | Memory (SRAM)                         |

|-----------------------------------------|---------------------------------------|

| <i>m n</i> -bit storage words           | <i>m n</i> -bit storage words         |

| Few words (<256), many ports,           | Many words (>1024), few ports,        |

| dedicated read/write ports, so that     | shared read/write ports. Read         |

| read and write operations <u>can</u> be | and write operations <u>cannot</u> be |

| done simultaneously.                    | done simultaneously.                  |

| Writing to a register takes just one    | Writing to a register can take        |

| clock cycle. Read op doesn't require    | many clock cycles. Read op            |

| a clock or additional control inputs.   | requires a clock and other CTRL.      |

| Logically Static Content                | Logically Dynamic Content             |

| Synchronous                             | Different implementations but         |

|                                         | mostly asynchronous <sup>*</sup>      |

Table L7-1. Register Files vs. SRAM Memory

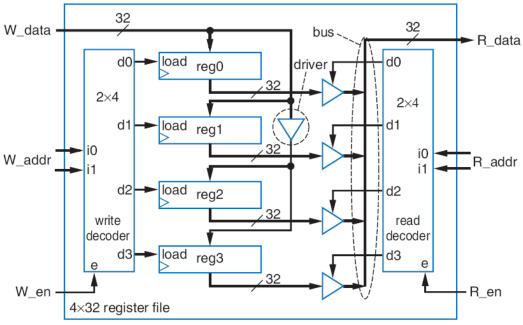

An example of a  $2^2 \times 5$  (or  $4 \times 32$ ) register file architecture was given in **Lecture 17** and is provided here for convenience in Figure L7-2.

<sup>\*</sup> See Lecture 17 on the mirror display application

<sup>&</sup>lt;sup>†</sup> Both notations can be used but the latter is preferred

<sup>&</sup>lt;sup>‡</sup> For an application developer it does sometimes contain circuitry that makes it look like synchronous.

Figure L7-2. Implementation of a 2<sup>2</sup> x 5 Register File

In summary, a register file is faster and more flexible. However, due to the circuit size of a FF (flip-flop), a register file is feasible only for small storage. Note that a register file is a typical design component of any CPU.

### **Specification**

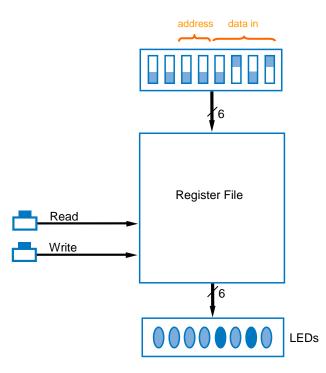

In this FPGA application development assignment, we will implement a  $2^2 \times 4$  register file and emulate its performance on the Digilent's Basys Board.

Figure L7-3. Register File and Basys Board implementation hint

The application functions as follows:

- 2 address switches provide the address (4 registers);

- 4-bit bytes ("data in") will be written into the register file when "Write" button is pressed. LED's should not react to this operation;

- 4-bit bytes will be read out when a "Read" button is pressed: 4 rightmost LED's will indicate the value and the following two LED's will show the address indicated by the address switches.

### **Demonstration**

Demostrate that the application performs according to specs.

### **Procedures**

- 1. Xilinx ISE Design and Synthesis environment;

- 2. Creation of Configuration files;

- 3. Usage of Adept ExPort download software;

### **Presentation and Report**

Must be presented according to the general  $\tt EE120A$  lab guidelines posted in iLearn.

### Prelab

- 1. Review Lectures 16, 17;

- 2. Try to answer all the questions, prepare logic truth tables, do all necessary computations