Home » Posts tagged 'big.LITTLE Processing'

Tag Archives: big.LITTLE Processing

Eight-core MT6592 for superphones and big.LITTLE MT8135 for tablets implemented in 28nm HKMG are coming from MediaTek to further disrupt the operations of Qualcomm and Samsung

Updates

Update: The Power of 8: MediaTek True Octa-Core [mediateklab YouTube channel, July 29, 2013]

Update: MT6592—The world’s first true octa-core SOC with scalable eight-core processing [product page, March 13, 2014]

Overview

MediaTek MT6592 is the world’s first heterogeneous computing SOC with scalable eight-core processing for superior multi-tasking, industry-leading multimedia features and excellent performance-per-watt. Based on 28nm HPM (High-Performance Mobile) process technology, MT6592 has eight CPU cores, each capable of clock speeds up to 2GHz.

Features

- ARM® Cortex®-A7 processor (1.7GHz or 2GHz)

- 28nm HPM process technology

- MAGE 3D graphics engine

- UMTS / HSPA+ R8 / TD-SCDMA / EDGE / LTE

- 801.11a/b/g/n, Bluetooth, GPS, FM tuner

- 16MP camera image signal processor

- Full HD H.265 / VP9 and Ultra HD H.264 video playback

- ARM Mali™ GPU (700MHz)

- MediaTek ClearMotion™ video enhancement

Update: [€147.18] Cubot X6 OctaCore MT6592 Phone Ultimate Slim Design 5″ OGS HD Retina [arif rachman YouTube channel, March 1, 2014]

Cubot X6 OctaCore MT6592 Ultimate Slim Design

Please follow the link below to see the full specification

http://bit.ly/CubotX6This is the latest phone from Cubot. Well.. the phone has the latest MT6592 1.7GHz processor. 28nm process, with quad core mali 450 GPU. Frequency is up to 700MHz. It supports full HD video with wide screen decoding format.

The true eight core processor can run simultaneously through advanced scheduling algorithm, dynamic temperature control and power management technology to optimize workload distribution to each core. When handling multiple tasks and heavy duty needs, achieve the peak performance of full eight core. At light load, you can turn off the core, the ultimate energy saving idle. It means substantial increase in cell phone battery life.

The Mali 450 graphics processor, overall performance is up to twice of the previous Mali 400. It supports full-HD 60fps. The triangles per second and render is 152M 2.8G pixels. Should be easy to run 3D games, smooth playback of 1080 HD videos. It also has a built in powerful MAGE 3D engine.

The front camera is 5 mega pixels while the back camera is 8 mega pixels. The camera is equipped with five pieces of high precision glass structure, which can effectively filter infrared blue glass. This is to achieve the level of professional SLR camera. Far better than ordinary lenses. The phone uses Sony sensor with latest 13Mega-Pixel CMOS Image Sensor.

In a week, the phone will be available at banggood for only $184.99 with free shipping worldwide! That’s an octa core phone below 200$ price tag! Not cheap enough?

Leave your email to get referred and get 10$ discount! Cheapest price out there!

Please follow the link below to see the full specification

http://bit.ly/CubotX6

IllusionMage [Wikipedia, excerpted on March 15, 2014]

IllusionMage is a paid for 3D modeling, animation, and rendering software packages comprising the core engine of Blender, an open-source, 3D software suite, and bundled with materials related to Blender.

Other names this bundle has gone under are IllusionMage3D, 3DMagix, and 3DMagixPro.[1]

All materials and software included are freely available from other sources. The marketing of this program includes images that were stolen from other sources, often created with competing 3D applications. The image of the alleged creator of the software, Seth Avery, is a random stock photo.[2]

Criticism

IllusionMage has come under fire by many prominent Blender news sites and figures, including Ton Roosendaal, the founder of the Blender Foundation[3][4]

Related

“Illusion Mage & 3D Magix Pro (affiliate) domain names” Topic: Illusion Mage & 3D Magix Pro *is* a scam. KatsBits Forum. Retrieved 2 October 2011.

“Handsome young man isolated over white”. Laflor Photography via iStockPhoto. Retrieved 8 May 2012.

January 2011 Blender Foundation Press Release

“3DMagix and IllusionMage, scam or open source leeches?”. BlenderNation. Retrieved 30 September 2011.

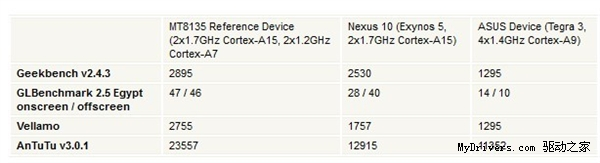

Update: 联发科平板四核心MT8135 官方成绩曝光 (MediaTek MT8135 quad-core tablet exposure Official Results) [ 驱动之家 (MyDrivers.com), July 29, 2013]

Update: MediaTek’s Quad-core Tablet SoC MT8135 : Performance Benchmark [mediateklab YouTube channel, July 19, 2013]

Update: MediaTek Introduces Industry Leading Tablet SoC, MT8135 [press release, July 29, 2013]

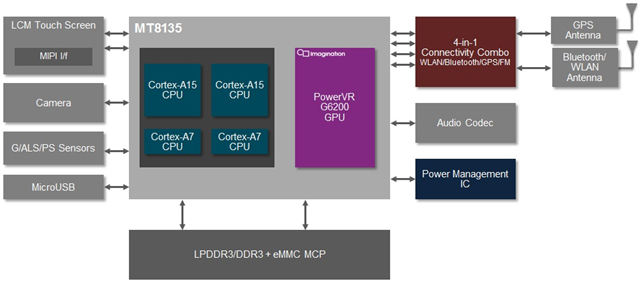

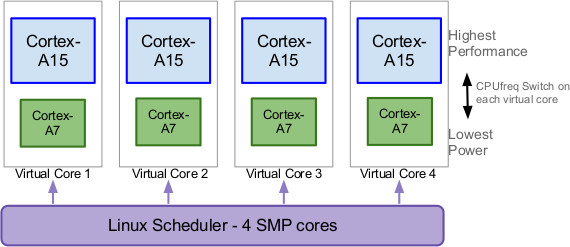

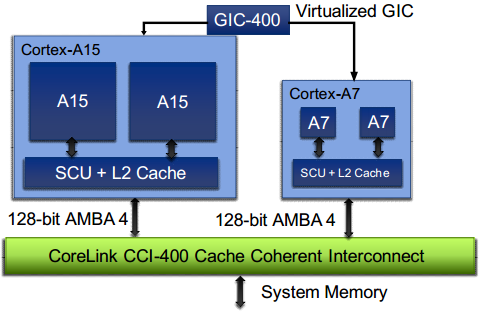

TAIWAN, Hsinchu – July 29, 2013 – MediaTek Inc., (2454: TT), a leading fabless semiconductor company for wireless communications and digital multimedia solutions, today announced its breakthrough MT8135 system-on-chip (SoC) for high-end tablets. The quad-core solution incorporates two high-performance ARM Cortex™-A15 and two ultra-efficient ARM Cortex™-A7 processors, and the latest GPU from Imagination Technologies, the PowerVR™ Series6. Complemented by a highly optimized ARM® big.LITTLE™ processing subsystem that allows for heterogeneous multi-processing, the resulting solution is primed to deliver premium user experiences. This includes the ability to seamlessly engage in a range of processor-intensive applications, including heavy web-downloading, hardcore gaming, high-quality video viewing and rigorous multitasking – all while maintaining the utmost power efficiency.

In line with its reputation for creating innovative, market-leading platform solutions, MediaTek has deployed an advanced scheduler algorithm, combined with adaptive thermal and interactive power management to maximize the performance and energy efficiency benefits of the ARM big.LITTLE™ architecture. This technology enables application software to access all of the processors in the big.LITTLE cluster simultaneously for a true heterogeneous experience. As the first company to enable heterogeneous multi-processing on a mobile SoC, MediaTek has uniquely positioned the MT8135 to support the next generation of tablet and mobile device designs.

“ARM big.LITTLE™ technology reduces processor energy consumption by up to 70 percent on common workloads, which is critical in the drive towards all-day battery life for mobile platforms,” said Noel Hurley, vice president, Strategy and Marketing, Processor Division, ARM. “We are pleased to see MediaTek’s MT8135 seizing on the opportunity offered by the big.LITTLE architecture to enable new services on a heterogeneous processing platform.”

“The move towards multi-tasking devices requires increased performance while creating greater power efficiency that can only be achieved through an optimized multi-core system approach. This means that multi-core processing capability is fast becoming a vital feature of mobile SoC solutions. The MT8135 is the first implementation of ARM’s big.LITTLE architecture to offer simultaneous heterogeneous multi-processing. As such, MediaTek is taking the lead to improve battery life in next-generation tablet and mobile device designs by providing more flexibility to match tasks with the right-size core for better computational, graphical and multimedia performance,” said Mike Demler, Senior Analyst with The Linley Group.

The MT8135 features a MediaTek-developed four-in-one connectivity combination that includes Wi-Fi, Bluetooth 4.0, GPS and FM, designed to bring highly integrated wireless technologies and expanded functionality to market-leading multimedia tablets. The MT8135 also supports Wi-Fi certified Miracast™ which makes multimedia content sharing between devices remarkably easier.

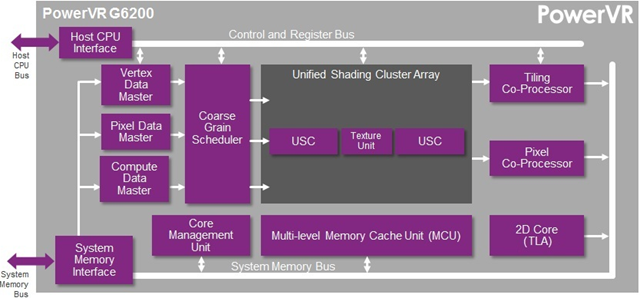

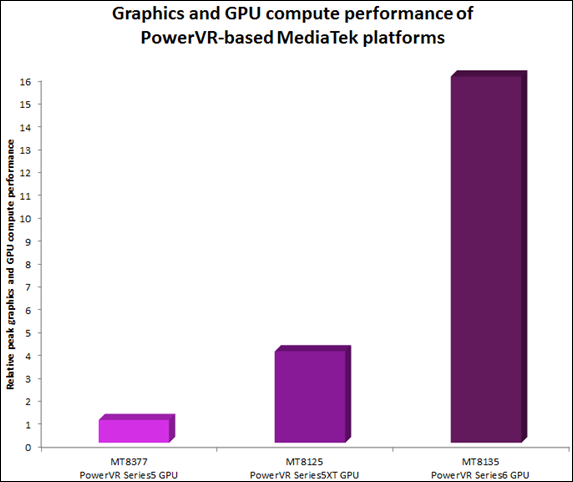

In addition, the tablet SoC boasts unprecedented graphics performance enabled by its PowerVR™ Series6 GPU from Imagination Technologies. “We are proud to have partnered with MediaTek on their latest generation of tablet SoCs” says Tony King-Smith, EVP of marketing, Imagination. “PowerVR™ Series6 GPUs build on Imagination’s success in mobile and embedded markets to deliver the industry’s highest performance and efficient solutions for graphics-and-compute GPUs. MediaTek is a key lead partner for Imagination and its PowerVR™ Series6 GPU cores, so we expect the MT8135 to set an important benchmark for high-end gaming, smooth UIs and advanced browser-based graphics-rich applications in smartphones, tablets and other mobile devices. Thanks to our PowerVR™ Series6 GPU, we believe the MT8135 will deliver five-times or more the GPU-compute-performance of the previous generation of tablet processors.”

“At MediaTek, our goal is to enable each user to take maximum advantage of his or her mobile device. The implementation and availability of the MT8135 brings an enjoyable multitasking experience to life without requiring users to sacrifice on quality or energy. As the leader in multi-core processing solutions, we are constantly optimizing these capabilities to bring them into the mainstream, so as to make them accessible to every user around the world,” said Joe Chen, GM of the Home Entertainment Business Unit at MediaTek.

The MT8135 is the latest SoC in MediaTek’s highly successful line of quad-core processors, which since its launch last December has given rise to more than 350 projects and over 150 mobile device models across the world. This latest solution, along with its comprehensive accompanying Reference Design, will like their predecessors fast become industry standards, particularly in the high-end tablet space.

Update: Optimized big. LITTLE – MediaTek [MediaTek, July 29, 2013]

Multi-core system-on-chip (SoC) design has brought tremendous benefits to mobile device users by offering seamless engagement in rigorous multitasking. To overcome the issue with high energy consumption and thermal readings, MediaTek is deploying an advanced scheduler algorithm, combined with adaptive thermal and interactive power management to maximize the performance and energy efficiency benefits of the ARM big.LITTLE™ architecture. The technology will allow applications software to simultaneously access all the processors in the big.LITTLE™ cluster for a true heterogeneous experience, activating both of its CPU clusters concurrently for extreme performance.

Optimized big. LITTLE™

ARM big.LITTLE™ processing is designed to address the energy and thermal issues associated with multi-core system-on-chip (SoC) solutions. It allows for the creation of dual-cluster SoCs, with one more powerful (big) cluster for processing intensive tasks and a less powerful (LITTLE) cluster for executing routine functions. MediaTek is among the first SoC designers to have adopted this ground-breaking technology. Unlike its counterparts, however, the company has done so in a manner that affords device users the utmost energy and thermal efficiency rates.

Enabling Heterogeneous Multi-Processing

Of the three big.LITTLE™ software models that can be integrated, for example, MediaTek chose the Heterogeneous Multi-Processing [developed and named by ARM as Global Task Scheduling (GTS), also known earlier as big.LITTLE MP, see in the last section of this post in detail] approach, which unlike the other two methods – Cluster- [as was implemented in Galaxy S4 by Samsung with Exynos 5 SoC having 4xA7+4xA15 configuration] and CPU-Migration [IKS (In Kernel Switcher) developed by Linaro, see in the last section of this post in detail] – allows for individual cores to be activated as and when needed for maximum efficiency.

However, use of the most versatile model isn’t MediaTek’s only advantage. In line with its reputation for creating innovative, market-leading platform solutions, MediaTek has deployed an advanced scheduler algorithm, combined with adaptive thermal and interactive power management to maximize the performance and energy efficiency benefits of the ARM big.LITTLE™ architecture.

The technology will allow applications software to simultaneously access all the processors in the big.LITTLE™ cluster for a true heterogeneous experience, activating both of its CPU clusters concurrently for extreme performance.

In comparison, the current octa-core SoC solution, utilizes one of the more inferior big.LITTLE™ software models. As a result, the processor is not as efficient as it otherwise might be.

As the first company to enable Heterogeneous Multi-Processing on a mobile SoC in the form of its MT8135 Reference Design, MediaTek is uniquely positioned to support the next wave of tablet and mobile devices.

Update: Optimized ARM big.LITTLETM – MediaTek Enables ARM big.LITTLETM Heterogeneous Multi-Processing Technology in Mobile SoCs [MediaTek Position Paper in PDF, July 29, 2013]

MediaTek MT8135 brings PowerVR Series6 GPUs to a mobile device near you [With Imagination Blog, July 29, 2013]

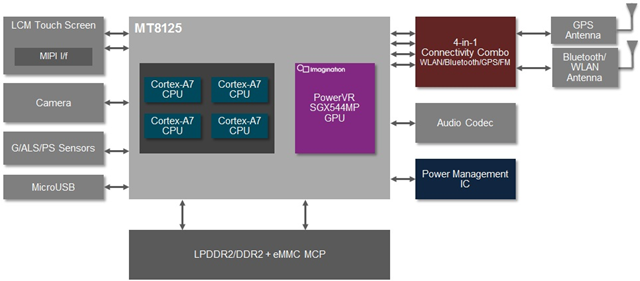

Over the years, our close partnership with MediaTek has resulted in the release of some very innovative platforms that have set important benchmarks for high-end gaming, smooth UIs and advanced browser-based graphics-rich applications in smartphones, tablets and other mobile devices. Two recent examples include:

- MT8125/MT8389, an extension of MediaTek’s highly successful quad-core portfolio which integrates power-efficient PowerVR Series5XT graphics that deliver compelling multimedia features and sophisticated user experiences

- MT8135, the first in a series of PowerVR Series6-based mobile chipsets that are due to be announced in the second half of this year

MediaTek has been steadily establishing itself as an important global player for consumer products like smartphones, tablets and smart TVs, with a strong foothold in Latin America and Asia, and a rapidly growing presence in Europe and North America. Earlier this year, MediaTek introduced MT8125, one of their most successful tablet chipsets for high-end multimedia capabilities.

While MT8125 has been extremely popular with OEMs including Asus, Acer or Lenovo, MT8135 has the potential to consolidate Mediatek’s existing customer base and open up exciting new opportunities thanks to the advanced feature set provided by Imagination’s PowerVR ‘Rogue’ architecture.

MT8135 is a quad-core SoC that aims for the middle- to high-end tier of the tablet OEM market. It supports a 4-in-1 connectivity package that includes Wi-Fi, Bluetooth 4.0, GPS and FM radio, all developed in-house by MediaTek. Miracast is another important addition to the multimedia package, enabling devices using MT8135 to stream high-resolution content more easily to compatible displays, over wireless networks.

MT8135 incorporates a PowerVR G6200 GPU [from the block diagram corresponds to the PowerVR G6230] from Imagination that enables advanced mobile graphics and compute applications for the mainstream consumer market, including fast gaming, 3D navigation and location-based services, camera vision, image processing, augmented reality applications, and smooth, high-resolution user interfaces.

As MT8135-powered mobile devices start appearing in the market, developers will have access to new technologies and features introduced by our PowerVR Series6 family such as:

- our latest-generation tile based deferred rendering (TBDR) architecture implemented on universal scalable clusters (USC)

- high-efficiency compression technologies that reduce memory bandwidth requirements, including lossless geometry compression and PVRTC/PVRTC2 texture compression

- scalar processing to guarantee highest ALU utilization and easy programming

Thanks to the PowerVR G6200 GPU inside the MT8135 application processor, MediaTek brings high-quality, low-power graphics to unprecedented levels by delivering up to four times more ALU horsepower compared to MT8125, its PowerVR Series5XT-based predecessor. PowerVR G6200 fully supports a wide range of graphics APIs including OpenGL ES 1.1, 2.0 and 3.0, OpenGL 3.x, 4.x and DirectX 10_1, along with compute programming interfaces such as OpenCL 1.x, Renderscript and Filterscript.

By partnering up with Imagination, MediaTek has access to our industry-leading PowerVR graphics, worldwide technical support, and a strong ecosystem of Android developers capable of making the most of our technology. We look forward to shortly seeing our brand-new PowerVR Series6 GPUs in the hands of millions of consumers, and see MediaTek as one of our strategic partners for our latest generation PowerVR GPUs moving forward.

End of Updates

This report consists of the following parts:

- The latest MediaTek roadmap, high-end and OS strategy

- News reports about MT6592 and its first application

Update: MediaTek True Octa [MediaTek, July 23, 2013]

Efficient video playback:

Efficient video playback:

When on decoding mode, the battery used for decoding HEVC (H.265) FHD video

can be reduced by up to 18 percent compared to current quad-core solutions

(from MediaTek True Octa-Core Position Paper [MediaTek, July 23, 2013])- What is new vs. my earlier The state of big.LITTLE processing [‘Experiencing the Cloud’, April 7, 2013] report

For the preceding smartphone SoC in the current roadmap see MediaTek MT6589 quad-core Cortex-A7 SoC with HSPA+ and TD-SCDMA is available for Android smartphones and tablets of Q1 delivery [‘Experiencing the cloud’, Dec 12, 2012]. For smartphone SoCs before that see Boosting the MediaTek MT6575 success story with the MT6577 announcement – UPDATED with MT6588/83 coming early 2013 in Q42012 and 8-core MT6599 in 2013 [‘Experiencing the cloud’, June 27, July 27, Sept 11-13, Sept 26, Oct 2, 2012]. Note that MT6588 was renamed MT6589 when was launched, as MT6599 would be renamed MT6592 now.

The latest MediaTek roadmap, high-end and OS strategy

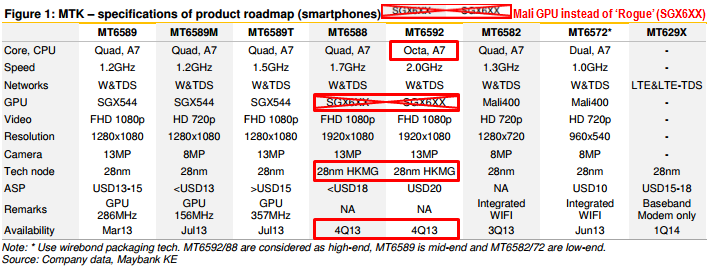

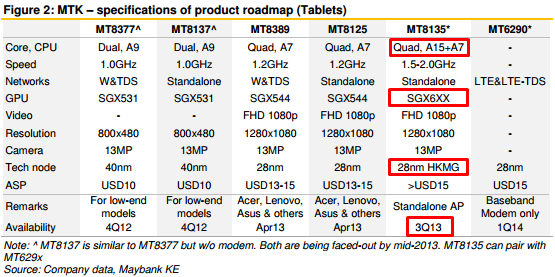

Maybank Kim Eng just published in its MediaTek Closing In Fast [July 17, 2013] report the following two SoC roadmaps:

GPU for MT6592 smartphone SoCs (and presumably for MT6588 as well) will be Mali according to Zhu Shangzu (朱尚祖), MediaTek Global Smartphone General Manager in the [Part 2] MediaTek to push 8 small cores, the mystery [ESM 国际电子商情 (International Electronic Business), July 18, 2013] exclusive interview.

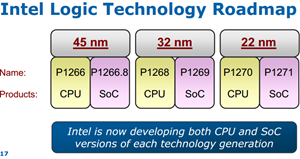

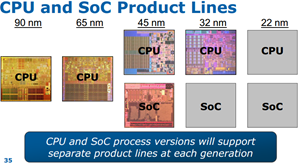

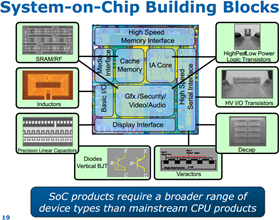

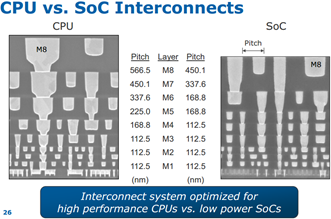

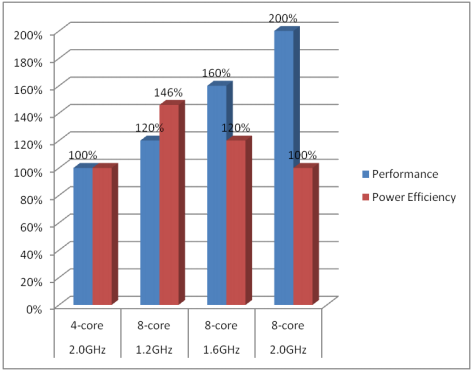

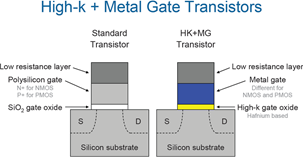

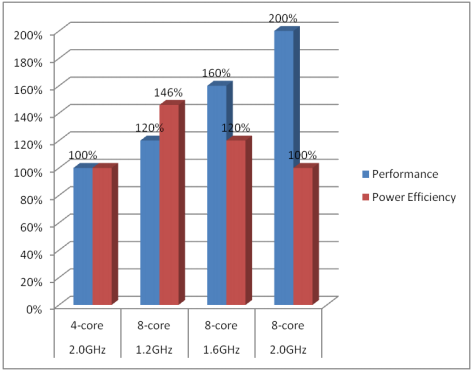

According to 28nm Technology [TSMC, June 21, 2011] description: The 28nm technology node of the TSMC foundry (which is used for manufacturing by MediaTek) has a high performance (HP) process as the first option to use high-k metal gate (HKMG) process technology. The 28nm low power with high-k metal gates (HPL) technology, as the second option, adopts the same gate stack as HP technology while meeting more stringent low leakage requirements with a trade of performance speed. Explanation: From about 10 µm (1971) to below 0.1 µm (100 nm) conventional silicon oxynitride as the gate insulator with polysilicon gate, so called poly/SiON gate stack, was used for CMOS technology. It was typically possible to scale down to 45 nm (2008), only TSMC was able to scale it down further to 28 nm in which most of the current 28nm SoCs from TSMC are produced.  While Intel (and IBM) had to introduce high-K dielectric as the gate insulator with metal gate, so called High-k / Metal Gate stack, for the performance of their 45 nm products in 2008 (in order to continue with the Moore’s law in their realm) as you could see on the right (taken from Life With “Penryn” [DailyTech, Jan 27, 2007] interview with Mark Bohr, Intel Senior Fellow, and Steve Smith, Intel Vice President DEG Group Operations), TMSC could introduce that only on the 28nm node as described above. The HKMG based 28nm SoCs are much higher performance (or higher performance still with low power by HPL) as you could see from the 2GHz clockrate of the MT6592 (above) or MT8315 (below) vs. that of the convential poly/SiON counterparts, MT6589 and MT8389 with 1.2GHz.

While Intel (and IBM) had to introduce high-K dielectric as the gate insulator with metal gate, so called High-k / Metal Gate stack, for the performance of their 45 nm products in 2008 (in order to continue with the Moore’s law in their realm) as you could see on the right (taken from Life With “Penryn” [DailyTech, Jan 27, 2007] interview with Mark Bohr, Intel Senior Fellow, and Steve Smith, Intel Vice President DEG Group Operations), TMSC could introduce that only on the 28nm node as described above. The HKMG based 28nm SoCs are much higher performance (or higher performance still with low power by HPL) as you could see from the 2GHz clockrate of the MT6592 (above) or MT8315 (below) vs. that of the convential poly/SiON counterparts, MT6589 and MT8389 with 1.2GHz.

Complementary post reminder: H2CY13: Upcoming next-gen Nexus 7, the ASUS MeMO Pad HD 7 “re-incarnation” at reduced by $50 price, dual/quad-core mid-range tablets from white-box vendors starting from $65 [‘Experiencing the Cloud’, July 5, 2013] in which there is plenty of information regarding the non high-end tablet SoCs, from MediaTek (MediaTek MT8125, MediaTek MT8377 and MediaTek MT8389) as well as competition from Allwinner and Rockchip. The pre-eminent ASUS MeMO Pad™ HD 7 described in detail there is using the MT8125 SoC, while the new Nexus 7 (to be announced before the ending of July) the Qualcomm Snapdragon 600 Quad Core SoC. In that sense we got with that post not only a complete H2 competitive tablet market picture for mid-range but some information regarding the new Qualcomm high-end as well.

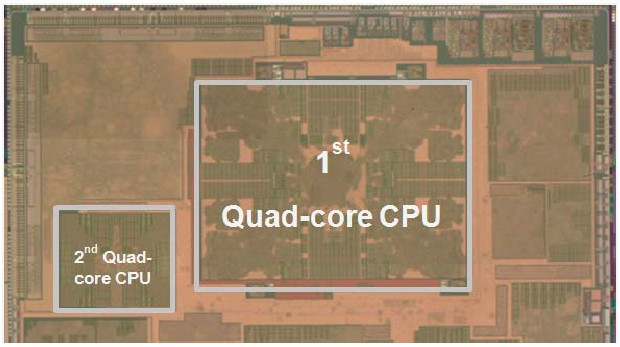

For the upcoming MT8135 tablet SoC it is known from the part 3 of the Zhu Shangzu interview that the quad-core configuration will be 2xA15+2xA7, which means a big.LITTLE architecture and quite probably the already mature ‘In Kernel Switcher’ (IKS) scheduler initially GTS with MediaTek’s “advanced scheduler algorithm, combined with adaptive thermal and interactive power management” and called Heterogeneous Multi-Processing (HMP) by MediaTek (see in the updates in front of the original post). But as As ARM already decided on the architecture of the other, more general ‘Global Task Scheduling’ (GTS) solution (see much below) I would assume that the proper hardware underpinnings for GTS will already be built in (unlike in the Samsung’s Exynos 5 SoC released before), so when the scheduler software will be mature enough it will run well on MT8135. The inclusion of just two cores of each (unlike in Exynos 5) is a very strong proof-point of that. As far as the GPU is concerned we know from Zhu Shangzu interview that an Imagination GPU will be used, therefore I will leave the next-generation SGX6XX (PowerVR Series6 or ‘Rogue’) indication in the above table. Update: It is the PowerVR G6200 GPU [from the block diagram corresponds to the PowerVR G6230] as you could see from Imagination block post published on the MT8135 announcement (July 29), and included here in front of the original post.

with the following commentary:

Strong fundamentals intact. Having exceeded its 2Q13 guidance so significantly, we believe MTK will continue to ride the strong momentum in 3Q13, perhaps growing its revenue by low-to-mid-teens QoQ or 30% YoY to chalk up another record high of TWD36-38b [US$1.2-1.27B]. Importantly, a better product mix and cost structure would help lift its profitability to ±44%. We expect MTK to ship 70-72m units of smart devices, up 25-30% QoQ, with quad-core APs and tablets making up nearly 50% of total shipment. The benefits of operating leverage should drive OPM past 20%, the highest since 3Q10. MTK is set to report its 2Q13 results in late July or early August and we forecast net profit of TWD6.8b [US$227M] (EPS: TWD5.02; Street: TWD6.3b), up over 80% QoQ and 100% YoY. GM is also likely to meet the high end of its guidance, ie, 43.5%, on richer mix and improved cost structure. Reported revenue of TWD33.3b, up almost 40% QoQ and 42%YoY, is already well ahead of guidance (TWD30-32b). However, we cut our FY13/14 earnings forecasts by 3% each to factor in the delay in merger with MStar and potential inventory correction in 4Q13/1Q14. MTK remains a key BUY in our tech space.

Closing in fast on QCOM. MTK has spared no efforts to enhance its smart device portfolio since 2H12 and further signs of acceleration are evident. It is introducing two high-end APs in 4Q13 – MT6588 and MT6592 – using 28nm HKMG and advanced graphic features. While the former is a quad-core AP operating at 1.7GHz, the latter is capable of running at 2GHz (when all eight core engines are turned on). In the absence of full details, we estimate MT6592 may perform closer to Qualcomm Snapdragon 600 AP (used in Galaxy S4 and HTC One), while MT6588 should outshine Snapdragon 400. MTK has won several international OEMs with MT6589 and with MT6588/6592, its chances of penetrating tier-1 OEMs have increased significantly. In addition, it will sample its high-end 4G/LTE/LTE-TDSCDMA modem chipset in anticipation of the launch of 4G network in China later this year. As for tablets, MTK’s latest APs MT8125/8389 were well-received and it is set to deliver the high-end MT8135 (big.Little design) in 3Q13. We expect its smartphone/tablet shipments to reach 200-225m/25m units in 2013.

In the same part of the interview Zhu Shangzu explained MediaTek’s high-end strategy as follows (as translated by Google and Bing with manual edits):

… I think the future of high-end smartphones innovation will focus on the expansion of big screen multimedia applications, and this is our direction. …

Judging from the current situation, customers of high-end flagship phones are still using the products of the competitors, but there is flagship in our quad-core case as well, and OPPO, Vivo and GiONEE and other quad-core phones are also very popular. Our next goal is to get the customers of flagship machines using our platform via helping customers to achieve stronger performance on the big screen multimedia.

Therefore, the 8-core MT6592 can be regarded as our first bugle call for moving towards the high-end market. Our mission is that one day customers can also recognize MediaTek as doing high-end flagship products. MT6592 is the first step, strictly speaking, it is not the most high-end platform, next we will move step by step towards the higher end.

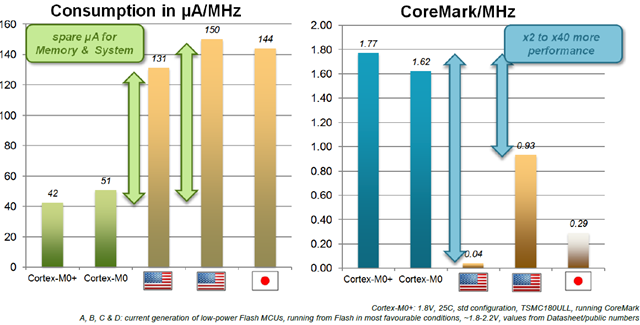

Q: Why will MediaTek use eight small A7 cores as a generation of high-end platform, but did not choose to use four large A15 cores or four big and four small ones as a way to achieve the goal? This is also a question for the industry as there are many controversial issues with this.

For power, or performance per watt, we did a lot of investigation. Eight A7 cores is currently the best solution, and as through a process we designed to boost peak frequency of the A7 to 1.9-2Ghz, performance is also very strong.

Currently we chose a small core, because under the existing process, the larger the chip die size, the larger is the standby leakage, resulting in higher standby power consumption. For example, the A15 is the strongest core currently, but not in run-time power cosumption. Even if its frequency is pushed down to very low levels, there is still a larger leakage. Therefore, the larger is the area of a single-core, the larger is the overhead energy efficiency, and as long as the poweris on, there will be a greater leakage.

In addition, the 8-core CPU is just one aspect of improving the mobile multimedia experience. In fact, as we have been doing MediaTek digital TV for a long time, we will extend that digital TV competency here – some strong move for the smartphones. This is what other platform vendors can not do. In the 6592, for example, the latest HEVC codec will be integrated. [HEVC is a video compression standard, a successor to H.264/MPEG-4 AVC]

…

Although our MT6592 GPU is also using a ‘Deluxe’ Mali quad-core GPU, but in order for content developers to achieve better compatibility, our HEVC is a software solution via the 8-core CPU, it is not using a GPU- based software solution. Because there are some strong content developers who will use their own HEVC decode. Currently the ‘Deluxe’ quad-core GPU on 6592 is mainly used to perform large-scale games and to do some advanced UI.

[Part 3] How to plan the future in the tablet market?

Q: I do note that the MT6592 is now using a quad-core Mali GPU, while before the MediaTek mainstream used Imagination GPU. How would you rate these two companies’ products?

The Imagination company has been doing GPUs long time in its history, the architecture design is beautiful, more artistic. The initial architecture of Mali [from ARM] would be more rough, and therefore area and power consumption will be worse. But after nearly three years of time, Mali has made a lot of progress, both are learning from each other, and by now the levels of these two are equal. The future perspective is that ARM’s overall resources are somewhat more fully available.

Q: This year we have seen MediaTek to attack the tablet market, what is the plan for the future in the tablet market?

A: Our current strategy is to carry out a mobile phone product line extension.

At the end of July the launch of a tablet chip is expected: the MT8135, with 2xA15 +2xA7, still using an Imagination GPU [Update: It is the PowerVR G6200 GPU (from the block diagram corresponds to the PowerVR G6230) as you could see from Imagination block post published on the MT8135 announcement (July 29), and included here in front of the original post], and mainly targeting the high-end tablet market. A small reminder, our MT6572 is not suitable for tablet computers as the original definition did not take into account the application of flat-screen.

…

[Part 6] If Google Android OS will be converged how MediaTek will respond?

Q: There is also a very large concern, as the industry is worried that after doing their own hardware next year (e.g. Xphone, watches, glasses, etc.) whether Google will close the Android OS, i.e. to do a Pure Android later on, and don’t let OEMs to change it? MTK will also have a very big impact, what do you think? What is the MTK attitude on other free OS’s?

A: If Google OS will be closed and converged that will have a huge impact on us. But from what we observe and communicate with Google, they will not close the OS or converge it. Google’s profitability does not depend on OS, he is relying on the service for profit. By doing hardware Google also aims to promote his services, he is very happy to use someone else’s machine on their home services.

Of course, we will also be prepared, as we comprehesively examine and take into account the prevailing factors. We will use Windows as a second priority, while using Firefox [OS] and HTML5 as a secondary backup, by keeping track of them. Because we judge that the [Android] OS convergence from Google profitability point of view is very low, therefore our vote for these two emerging open OS’s is in the ‘not so urgent’ category, in addition to and outside of Android. The other focus is again on Windows Phone 8. For the moment, however, WP8 hardware configuration requirements are still higher (mainly memory), power consumption – after optimizing the gap with Android – is not too large.

…

News reports about MT6592 and its first application

Update: MediaTek True Octa [MediaTek, July 23, 2013]

Update: MediaTek True Octa [MediaTek, July 23, 2013]

Efficient video playback:

Efficient video playback:

When on decoding mode, the battery used for decoding HEVC (H.265) FHD video

can be reduced by up to 18 percent compared to current quad-core solutions

(from MediaTek True Octa-Core Position Paper [MediaTek, July 23, 2013])

July 18 this information appeared on the English http://en.v5zn.com/ website of the related smartphone vendor as well: MediaTek MT6592’s first eight-core mobile phone exposure makes you believe [July 15, 2013] as translated by Google and Bing with manual edits

MediaTek so-called true eight-core processor MT6592 was announced not long ago, it is expected the first models equipped with processors to surface. It broke the news, that the domestic mobile phone manufacturer brand named after the 19th-century French writer Jules Verne [凡尔纳] has been determined to launch a flagship model “V8” quipped with the MT6592 processor.

Verne’s current main product is the “V5” model, equipped with a quad-core MediaTek MT6589, and a 5-inch 720p OGS full lamination screen, 1GB of RAM, 4GB storage, 8-megapixel back-illuminated camera, 2400 mAh Battery, with a list price of 999 yuan [$166].

V8 has not yet announced the exact configuration bit it is estimated to have about 5.5 inch 1080p screen, 2GB RAM, 32GB storage, 13 million pixels Sony stacked camera, higher capacity battery, etc., without these natural shot himself embarrassed flagship.

It looks like that cooperation between MediaTek and the domestic Shanzhai vendors remains close. As MT6589 has rocked the Main Street, MT6592 will soon become a standard, and “an eight-core” promotion will be overwhelming.

Incidentally recap: MT6592 uses eight Cortex-A7 architecture cores, clocked at up to 2.0GHz, with TSMC 28nm manufacturing, Antutu run is known as close to 30,000, but the graphics core has not been confirmed,

PowerVR SGX 544MP4/554MP4 are likely[it will be Mali, as communicated by MediaTek, see above].The marketing of the processor has begun to customers, but mass production will be in November, so if recent high profile publicity is to be fulfilled, certainly we will have a large sale early next year.

Company introduction [Jules Verne mobile phone, January 16, 2013] as translated by Google and Bing with manual edits

Shenzhen MINDRAY Platinum Communication Technology Ltd. is is specialized in products development, production, sales and service of intelligent mobile terminals of high-tech companies. Under the “Jules Verne VOWNEY” brand the company is to create a mobile intelligent terminal brand.

MINDRAY Platinum company with “intelligent life” as the brand mission, is to “enhance the user experience, to help people grasp the development opportunities” as the goal, trying to make Jules Verne a trustworthy, continuous innovation and smart moves life guide. Every effort, just as long as you!

Jules Verne mobile phone network direct sales, stripping agents layers, increases direct benefits to consumers. We are committed to allow more consumers to have a better quality of life with an intelligent terminal.

The “Jules Verne VOWNEY ” brand aspires to be able to improve the quality of life for mobile users intelligent terminal INITIATIVE persons.

is to become quality of life can improve the user moves Smart The Terminal Guide. Lead you into “Slide 5.0”.

“Verne VOWNEY “brand aspires to be able to improve the quality of life for mobile users intelligent terminal INITIATIVE persons. I lead you into the “Slide 5.0″era.

Brand interpretation

Jules Verne: a derivative of intelligent life???

English explanation : VOWNEY

V : value— Value

O : opportunity— Opportunity

W : worth— It is worth

N : new— New

E : e— Mobile Internet

Y : you— YouJules Verne is to ” create a new life guided smart” as the goal, and strive to become a trusted, sustainable and innovative mobile phone brand, all efforts, just because of you!

Mediatek MT6592 8 core processors coming by the end of July! [Gizchina.com]

Reports out of Taiwan state that Mediatek will launch the MT6592 8-core processor by the end of July.

There was word that Mediatek were working on an 8 core chipset late last year, but like many we believed it had been placed on the back burner while they prepared their LTE chip. This seems to be wrong though as sources in Taiwan claim that Mediatek’s 8-core processor will arrive before the end of this month!

The MT6592 chip will be made up of 8 Cortex-A7, 28nm processor clocked at a frequency of up to 2Ghz! Early tests have the 8 core MT6592 scoring up to 30,000 points in Antutu which is more than Samsung’s 8 core Exynos 5410 processor.

The first batch of these new processors will be ready for manufacturers to begin development by the end of July, while Mediatek are preparing full-scale manufacture for November!

If everything goes to plan we can expect powerful 8 core phones from Tier 1 Chinese phone manufacturers by December!

MediaTek to launch true 8-core, 2GHz MT6592 chipset in November? [Engadget, July 2, 2013]

Samsung may already have its 8-core Exynos 5 Octa offering, but the original “big.LITTLE” implementation means only up to four cores work together at any time — either the Cortex-A15 quartet or its lesser Cortex-A7 counterpart. In other words, we’d rather rename the chipset range to something like “Exynos 5 Quad Dual.” But according to recent intel coming from Taipei and Shenzhen, it looks like Taiwan’s MediaTek is well on its way to ship a true 8-core mobile chipset in Q4 this year.

The first mention of this 2GHz, Cortex-A7 MT6592 chip came from UDN earlier today. The Taiwanese publication claims MediaTek started introducing its first octa-core product to clients last week, and it’s expected to enter mass production using TSMC’s 28nm process in November. The first mobile devices to carry this hot piece of silicon may hit the market in early 2014 — hopefully just in time for the Chinese New Year shopping rush.

UDN adds that the MT6592 scored close to 30,000 on AnTuTu, which is pretty high but still some distance behind Qualcomm’s 2.2GHz quad-core Snapdragon 800. Of course, chances are MediaTek’s offering will be much cheaper, as evidenced by all the affordable MediaTek-powered devices in China these days.

In a separate article from last week, UDN pointed out that judging by over a hundred job openings released by MediaTek last month, the company is clearly putting an emphasis on 4G LTE technology, alongside GPU and Android development. The publication also quoted chairman Tsai Ming-kai saying he will launch an LTE solution in Q4 this year, by which point MediaTek will only be one or two years behind its competitors.

The second piece of info came from HQ Research analyst Pan Jiutang, who posted an alleged spy shot of MediaTek’s upcoming roadmap (pictured left). There the octa-core MT6592 is listed with a clock speed of 1.7GHz to 2GHz, along with 1080p 30fps video decoding support. There’s also a quad-core 1.7GHz MT6588 accompanying its octa-core sibling in the same period on the timeline, though it appears to be just a faster version of the current 1.2GHz MT6589.

For the sake of phone manufacturers, both new chipsets will apparently be pin-to-pin compatible with the quad-core 1.3GHz MT6582 due Q3 this year, thus lowering R&D costs. Better yet, the roadmap also states that the MT6290 LTE modem — as teased by Tsai above — will be compatible with these three chipsets.

With MediaTek quickly catching up ahead of China’s eventual TD-LTE launch, Qualcomm will need to tread carefully to keep its Chinese QRD partners happy.

[Thanks, Ryan!]

Update: It’s worth noting that ARM’s eventual “big.LITTLE MP” implementation will allow all eight cores to run simultaneously, but the Exynos 5 Octa currently doesn’t support this. Thanks, UncleAlbert!

SOURCE: Sina Weibo (login required), UDN (1), (2)

What is new vs. my earlier

The state of big.LITTLE processing [‘Experiencing the Cloud’, April 7, 2013] report

Power scheduler design proposal [by Morten Rasmussen from ARM on Linux kernel mailing list, July 9, 2013]

This patch set is an initial prototype aiming at the overall power-aware scheduler design proposal that I previously described <http://permalink.gmane.org/gmane.linux.kernel/1508480>.

The patch set introduces a cpu capacity managing ‘power scheduler’ which lives by the side of the existing (process) scheduler. Its role is to monitor the system load and decide which cpus that should be available to the process scheduler. Long term the power scheduler is intended to replace the currently distributed uncoordinated power management policies and will interface a unified platform specific power driver obtain power topology information and handle idle and P-states. The power driver interface should be made flexible enough to support multiple platforms including Intel and ARM.

This prototype supports very simple task packing and adds cpufreq wrapper governor that allows the power scheduler to drive P-state selection. The prototype policy is absolutely untuned, but this will be addressed in the future. Scalability improvements, such as avoid iterating over all cpus, will also be addressed in the future.

Thanks,

Morten

From <http://permalink.gmane.org/gmane.linux.kernel/1508480>

…

+-----------------+ | | +----------+ current load | Power scheduler |<----+ cpufreq | +--------->| sched/power.c +---->| driver | | | | +----------+ | +-------+---------+ | ^ | +-----+---------+ | | | | | | available capacity | Scheduler |<--+----+ (e.g. cpu_power) | sched/fair.c | | | +--+| +---------------+ || ^ || | v| +---------+--------+ +----------+ | task load metric | | cpuidle | | arch/* | | driver | +------------------+ +----------+…

Linux Kernel News – June 2013 [by Shuah Khan in Linux Journal , July 9, 2013]

As always the Linux kernel community has been busy moving the Linux mainline to another finish line and the stable and extended releases to the next bump in their revisions to fix security and bug fixes. It is a steady and methodical evolution process which is intriguing to follow. Here is my take on the happenings in the Linux kernel world during June 2013.

Mainline Release (Linus’s tree) News

Linus Torvalds released Linux 3.10. You can read what Linus Torvalds had to say about this release in his release announcement athttp://lkml.indiana.edu/hypermail/linux/kernel/1306.3/04336.html

Two notable features in this release are improved SSD caching and better Radeon graphics driver Power Management.

…

Power efficient scheduling design

Ingo Molnar (Red Hat, x86 maintainer), Morten Rasmussen (ARM, power mgmt.), Priti Murthy (IBM, scheduler), Rafael Wysocki (Intel, Linux PM, and Linux ACPI maintainer) and Arjan van de Ven discussed the proposed power-aware or power-efficient scheduler design and what’s the best way to integrate it into the kernel.

Power management and the ability to balance performance and power efficiency is important and complex. It is not just about scheduler or cpus. It spans I/O devices that transition into lower-power states and how costly it is to bring them back to fully active state when needed. There is latency involved in these transitions. As always, Linux developers reach consensus to solve complex problems such as these and come up with path to get to the goal taking small steps towards that goal. Here is another example of that process at work.

Power-efficient scheduler work has been active for a few months now. Several RFC patches have been floated and discussed. This work is being pursued very actively in x86 space by IBM and in ARM space by ARM. The premise is that, if scheduler could pack tasks on a few cores and keep these cores fully utilized and, transition other cores to low power states, when the scheduling goal is power savings over performance. In other words, instead of keeping all the cores active, scheduler could consolidate tasks on a few cores and transition other cores to low-power states for better power efficiency.

It is easier said than done. Scheduler is at a higher level and would not be the best judge of making decisions on transitioning CPUs to idle states and deciding on the ideal frequency they should be running at. These decisions are better left to platform drivers that have the specific knowledge of the platform and architecture as they are complex and very hardware specific. In other words, power aware scheduler tuned to run well on x86 platforms will not work as well or could fail miserably on ARM platforms.

Scheduler has to accomplish load balancing as well as power balancing in a way to meet performance and power goals and do it well on all platforms. A generic scheduler doesn’t have to control and drive low-power state decisions on a platform. However, the goal of power-efficient scheduler is to set higher level abstracted policies that would work on all platforms. After a long and productive discussion, there is a consensus and here is the summary:

- A new kernel configuration option CONFIG_SCHED_POWER to enable/disable the power scheduler feature. Power scheduler is totally inactive, when CONFIG_SCHED_POWER is disabled, and fully active when CONFIG_SCHED_POWER is enabled. The important goal is evolving the power scheduler feature without disrupting and destabilizing the current scheduler.

- Work on a generic power scheduler with hardware and platform abstractions that will work well on big little ARM, x86, and other platforms. Avoid platform specific power policies that could lead to duplication of functionality in platform specific power drivers.

Please check the Linux Foundation site for presentations made at the Linux Collaboration Summit back in April 2013 on this topic. Here is the link to Jonathan Corbet’s blog on this topic.

http://www.linux.com/news/featured-blogs/200-libby-clark/715486-boosting……

From: big.LITTLE Software Update [by George Grey on Linaro Blog, July 10, 2013]

There are also two software models now available, that ARM and Linaro have developed to enable control of workloads, performance, and power management on big.LITTLE SoCs.

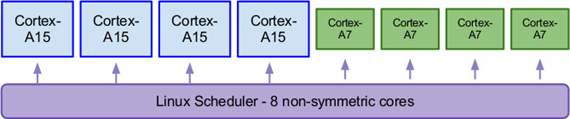

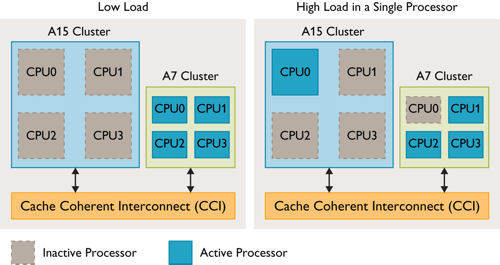

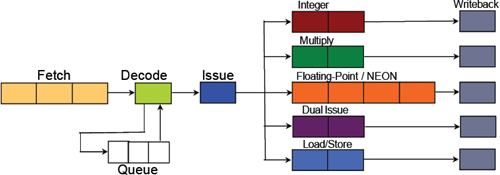

The first is the IKS [In Kernel Switcher, also known as CPU Migration]software, developed by Linaro, that treats each pair of Cortex-A7 and Cortex-A15 cores as a single ‘virtual’ core. On a multicore SoC each pair is treated as 1 of n virtual symmetric cores by the Linux kernel.

Core Software Configuration for IKS (4+4)

Using existing mechanisms in the Linux kernel for each pair the cpufreq driver controls whether the Cortex-A7 is active (for low power) or the Cortex-A15 is active (for maximum performance). Overall maximum performance and throughput on a 4+4 core SoC is from 4 Cortex-A15s. The key attribute of IKS is that it relies on existing well-understood mechanisms in the Linux kernel and it is easy to implement, test and characterize in a production environment.

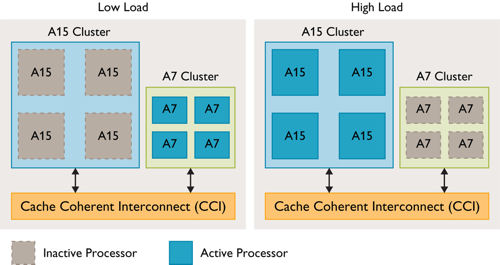

The second is the Global Task Scheduling (GTS) [also known as big.LITTLE MP or Heterogeneous Multi-Processing (HMP)] software developed (and now named) by ARM. This is known in Linaro as big.LITTLE MP. Using GTS all of the big and LITTLE cores are available to the Linux kernel for scheduling tasks. We are very proud that Linaro has contributed to ARM’s development of the GTS software, and that it is now publicly available in Linaro builds. ARM and Linaro recommend GTS for new products, and Linaro members are actively planning product deployments using this solution.

Core Software Configuration for GTS (4+4)

…

The big.LITTLE MP patch set creates a list of Cortex-A15 and Cortex-A7 cores that is used to pick the target core for a particular task. Then, using runnable load average statistics, the Linux scheduler is modified to track the average load of each task, and to migrate tasks to the best core. High intensity tasks are migrated to the Cortex-A15 core(s) and are also marked as high intensity tasks for more efficient future allocations. Low intensity tasks remain resident on the Cortex-A7 core(s).

IKS and GTS are now publicly available in Linaro monthly engineering releases for the ARM TC2 Versatile Express hardware, and in Linaro’s interim Long Term Supported Kernel (LSK) build. Both will also be incorporated into the first full Linaro LSK, which will be based on the next Linux Foundation, Greg Kroah-Hartman designated, Long Term Supported (LTS) kernel.

…

Until GTS functionality is fully upstream, ARM is supporting the big.LITTLE MP patch set for its licensees, leveraging Linaro’s public monthly and Linaro LSK builds, so that it is available to all ARM licensees for product integration and deployment. Linaro also expect to provide a topic branch for the latest work available on the upstream GTS implementation for interested developers.

… ARM and Linaro now recommend product development and deployment to be based on the GTS solution. However, there are some cases where hardware limitations or a requirement for the traditional Linux scheduler (for example in some embedded applications) may lead to IKS still being required.

Future Work

Power management software in Linaro is worked on by the Power Management Working Group. Other activities within the Group will enable additional power savings on ARM multi-core devices. One current project worth highlighting is the work being done by Vincent Guittot on small-task packing. Normally the Linux kernel will spread running tasks over all the available CPU cores. On a handset in standby, or even when being used with low activity, there may be a number of housekeeping and other small tasks that run in the background or relatively infrequently and therefore keep cores active unnecessarily. If “small” tasks can be migrated to one core, then the other cores could be made idle or even turned off completely, potentially resulting in significant power savings. This feature is expected to offer improved power management to systems based on symmetric multi-core SoCs (for example dual or quad-core Cortex-A7 or Cortex-A15 parts), as well as big.LITTLE SoCs.

While the current big.LITTLE efforts are focused on Cortex-A15 and Cortex-A7, the techniques being implemented today for 32-bit systems are already being run on 64-bit models. We therefore expect to see the GTS software running on 64-bit Cortex-A57 and Cortex-A53 based big.LITTLE SoCs as soon as they become available.

Real Life Results

ARM has published further information on big.LITTLE configurations and performance in a blog entry here [Ten Things to Know About big.LITTLE [Brian Jeff on SoC Design blog of ARM, June 18, 2013]].

The first commercial products based on big.LITTLE are certain international versions of the latest Galaxy S4 phone from Linaro member, Samsung. Samsung-LSI provide an ‘Octa-core’ 4+4 big.LITTLE chip for this phone. As has been publicly noted, the current generation of hardware cannot yet take full advantage of the IKS or the GTS designs because the hardware power-saving core switching feature is implemented on a cluster basis rather than on a per-core or a per-pair basis. Even so, the first big.LITTLE implementation produces performance and power consumption on a par with the latest Qualcomm multi-core Snapdragon processor according to reviews from Engadget, PocketNow and others. Often first implementations of new technology never see the light of day – it is a tribute to Samsung’s engineers that the Exynos 5 is already seeing the Cortex-A15 level of performance with the power saving of the Cortex-A7s in a mass market handset in the very first big.LITTLE iteration.

We look forward to seeing what improvements full use of GTS will bring when used on future production devices from Samsung and others.

More information: Power Management with big.LITTLE: A technical overview [by Steven Willis in SoC blog of ARM, June 20, 2013]

Why all this sudden attention on the Linux Scheduler? [LCE13, Linaro Connect Europe]

12:00 PM – 13:00 PM on Monday, Jul 8, 2013 (IST)

Description

The Linux scheduler is getting a lot of attention in the ARM ecosystem these days. Come to this discussion to find out why.

Several people working on the scheduler or interested in changes to the scheduler will be invited to talk about their requirements, what is the state of their work, who will benefit from it, etc.

Minutes of the above discussion

Determinism: problems

———————* Preemption: interrupts, locking

* Latency

* Scheduling overhead

* Realtime processingMost of the requirements are coming from LEG/LNG.

Solutions:

– PREEMPT_RT

– Adaptive NO_HZ (merged in 3.10)Came out of high-performance computing. When there is just one

task, the scheduler is switched off for that CPU. Results in

zero scheduler overhead. When the only task finishes – the CPU

will get into scheduling/idle again.There is still once-per-second tick for scheduling. There

is a patch removing that last remaining bit to make it fully

tickless.We’re not sure yet if all the possible limitations are found –

there still might be some scheduler overhead left.

If interrupt handling is offloaded to other cores, caching

related issues will still affect performance (e.g. serving IO

interrupts for the task on a different core will require the

dedicated core to cache the date once again).– Deadline

Physical process isolation: none addresses

– Needed for KVM.

Temporal isolation: all three (with some limitations)

No scheduling overhead: ADAPTIVE NO_HZ only.

Firm/Hard Real-time PREEMPT_RT only

Complexity:

high for PREEMPT_RT

low for the restRequirements:

all of the abovePower efficiency: history

————————-

* sched-mc (got removed)

* big.LITTLE MP patches implementing GTS (ARM)

* Packing Small Tasks (Linaro/ARM)

Pack all small background tasks on as little number of small cores

as possible to conserve power.Intel approach does not care about which core is selected as the

best one (Turbo Mode is effectively converting the core into a BIG

core, while all the other cores are becoming little ones). Task

migration is expensive – this approach helps avoiding it.* Power aware scheduling (Intel)

Discussions were lasting for a while and then Ingo Molnar requested

an integral solution (not a set of independent bits).He made a good point. What we have an SMP legacy implementation.

Are we starting from scratch because of that?

It is going to be a significal change. We need to re-think as it’s

not SMP case anymore. b.L is not a new architecture – Intel already

does that but differently.The task is to find the most efficient way of performing the work

needed. The best place to make those decisions is the scheduler.Power officiency – proposal (from ARM)

————————————–Separate process and power scheduler (ARM). This is the first step

to get to the fully integral scheduler in the future. Helps fighting

with the complexity at hand. In this case there are certain

limitations – one of the schedulers will be leading while the second

one will be limited.That doesn’t work well for Intel CPUs (no pre-configured small/BIG

cores).Issues:

– Topology

Missing:

– Frequency domains, which CPUs are affected. That would be

useful for the scheduler.– Idle + DVFS

Missing:

– information about the cost of using a certain core at certain

DVFS operation point to perform a certain amount of work.– Thermal

The idea is to keep an eye on the temperature trend to avoid

cases when whole cores are needed to be temporarily shut down to

cool them down.GPU contribution into the thermal budget should also be

considered.Trying to control DVFS from the scheduler. Patches are expected very

soon.Q: How much of the improvements are we looking for (power wise)?

A: Something that will get upstream. 😀

Linux 3.10 [by Linus Torvalds on Linux kernel mailing list, June 30, 2013]

Linux kernel 3.10 arrives with ARM big.LITTLE support [Engadget, July 1, 2013]

Thanks to Linus Torvalds’ figurative stroke of the pen, the Linux kernel 3.10 is now final — paving the way for its inclusion in a bevy of Linux distributions, and even offshoots such as Android and Chrome OS. The fresh kernel brings a good number of changes, such as timerless multitasking, a new caching implementation and support for the ARM big.LITTLE architecture. In simplistic terms, the new multitasking method should help improve performance and latency by firing the system timer only once per second — rather than 1,000 times — when tasks are running. Meanwhile, users with both traditional hard drives and SSDs will find performance benefits from bcache, which brings writeback caching and a filesystem agnostic approach to leveraging the SSD for caching operations. Also of significance, Linux kernel 3.10 enhances ARM supportby including the big.LITTLE architecture, which combines multiple cores of different types — commonly the Cortex-A7 and Cortex-A15 — that focus on either power savings or performance. The full list of improvements is rather lengthy, but if you feel like nerding out with the changelog, just grab a caffeinated beverage and get to it.

Linaro 13.06 Released! [by Amber Graner on Linaro Blog, June 27, 2013]

The Linaro 13.06 release is now available for download!

…

It’s been a very active cycle for the Builds and Baselines team, reporting that the Continuous Integration (CI) loop for the Linaro Stable Kernel (LSK) Android proof of concept which is based on 3.9.6 kernel version was set up and includes the big.LITTLE IKS and MP patches (also called beta patchset). Support for Kernel CI loop with Android filesystem was added to android-build and CI loop was set up to track the ARM Landing Team (LT) integration tree. The HiSilicon member build with complete CI loop was set up and now tracks the LT kernel tree.

…

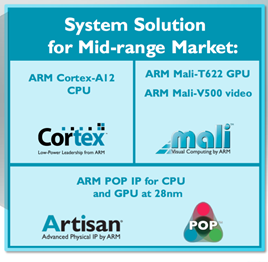

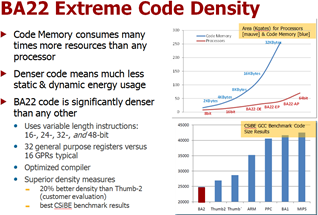

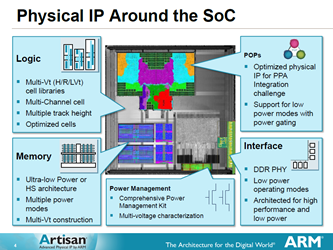

ARM Cortex-A12 CPU cores and Mali-T622 GPU cores with Process Optimization Packs (POPs), plus Mali-V500 video block for mid-range mobile devices of the end of 2014

in order to cover (very competitively) the hole existing in ARM-based SoCs so far:

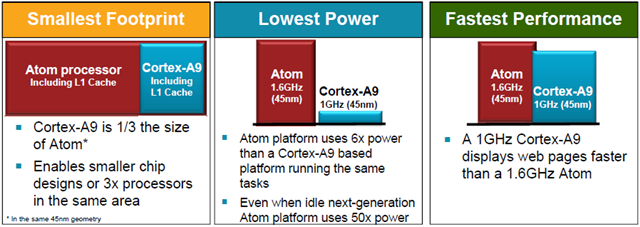

AnandTech’s judgement about the Cortex-A12 announcement:

… The Cortex A9 is too slow to compete with the likes of Intel’s Atom and Qualcomm’s Krait 200/300 based SoCs. The Cortex A15 on the other hand outperforms both of those solutions, but at considerably higher power and die area requirements. … The Cortex A15 island in Samsung’s Exynos 5 Octa occupies 5x the die area as the A7 island, and consumes nearly 6x the power. In exchange for 5x the area and 6x the performance, the Cortex A15 offers under 4x the performance. It’s not exactly an area or power efficient solution, but a great option for anyone looking to push the performance envelope. Today, ARM is addressing that hole with the Cortex A12. …

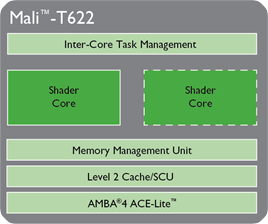

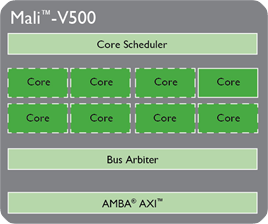

AnandTech’s judgement about Mali-T622 and Mali-V500 announcements:

… The Mali-T622 is a 2-core implementation of the 2nd generation Mali-T600 GPU architecture that we first learned about with the 8-core T628. Each shader core features two ALUs, an LSU and a texture unit. … On the video front, the Mali-V500 video encode/decode block is a multi-core engine used for all video acceleration. The V500 allegedly supports up to 100Mbps High Profile H.264, although details are scarce on more specifics. ARM claims support for up to 120 fps 4K video decode with an 8-core V500 implementation. Mali-V500 also features a protected video path, necessary for gaining content owner support for high-bitrate/high-resolution video decode. The V500 also supports ARM’s Frame Buffer Compression (AFBC), a lossless compression algorithm that can supposedly reduce memory bandwidth traffic by up to 50%. There’s presently no frame buffer compression in Mali GPUs today, but ARM expects to eventually roll AFBC out to Mali GPUs as well.

Announcement information from ARM:

|

|

|

|

|

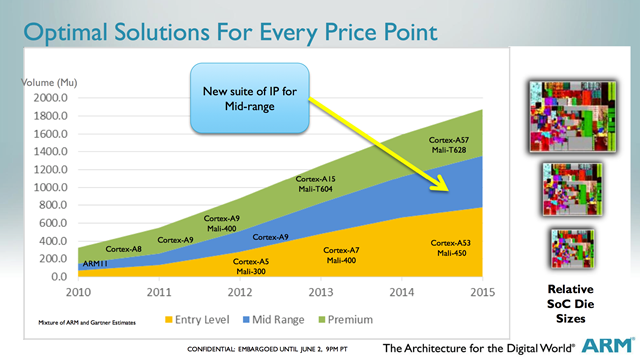

ARM Targets 580 Million Mid-Range Mobile Devices with New Suite of IP [press release, June 3, 2013]

News Highlights:

- Faster time to market and less design risk with suite of IP including:

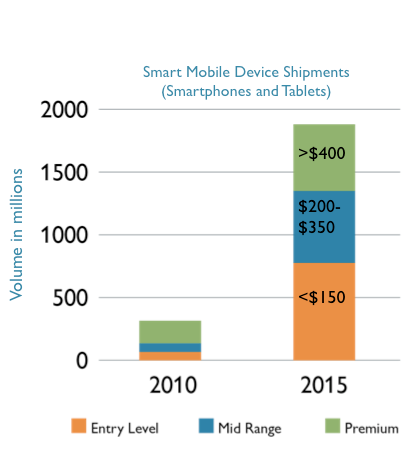

ARM Cortex-A12 processor, Mali-T622 GPU, Mali-V500 video solution and POP IP technology;- 580 million mid-range smartphones and tablets are forecast to be sold in 2015

- Cortex-A12 processor delivers 40 percent more performance than Cortex-A9 and brings premium features such as virtualization to the mid-range mobile device market; efficiency profile also makes it ideal for DTV and home networking;

- Cortex-A12 processor brings optimum performance and maximum efficiency of big.LITTLE processing to mid-range smartphones and tablets;

- Mali-T622 GPU offers an efficient and qualified OpenGL ES 3.0 solution and smallest Full Profile GPU Compute solution, putting even greater compute power into the hands of more mobile users;

- Mali-V500 video IP solution reduces system bandwidth and power, while enabling the protection of premium video content with TrustZone support.

The essence is that the first Cortex-A12 based SoCs are expected by mid-2014

– for mid-range devices (smartphones and tablets) in the $200 … $350 price range by late 2014 to early 2015

– with Cortex-A7/A15 architectural compatibity, thus in big.LITTLE configurations with either core, supporting 40-bit addressing (up to 1 TB) and virtualization

– plus providing the highest efficiency in pairing with Cortex-A7 core

– as the follow-up with +40% performance to the current SoCs for mid-range devices based on Cortex-A9 SoCs

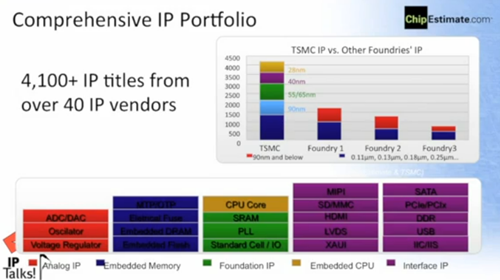

The SoC ramp-up of about one year or so is compared to not less than two years ramp-up for Cortex-A9 based SoCs. This is the result of significant progress with Process Optimization Pack technology of ARM which was first time developed along with the processor and GPU cores themselves. It is available now for TSMC 28HPM process technology for lead partners. Six of them are already starting their SoC design. Moreover it will also be available at GLOBALFOUNDRIES 28-SLP HKMG process technology in Q4 2013. So it is also first time as such complete sourcing from two foundries will be available for SoC vendors so early on. GLOBALFOUNDRIES is even going to achieve up to 70 percent higher performance in comparison to a Cortex-A9 processor core using 40nm process technology. Competition between those 2 foundries will understandably be very strong as the 2015 mid-range smartphone and tablet market is expected to be not less than 580 million units.

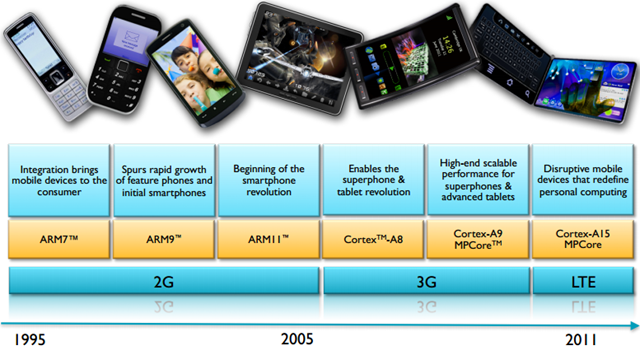

In comparison the Cortex-A9 core was announced in October 2007 and released in 2008

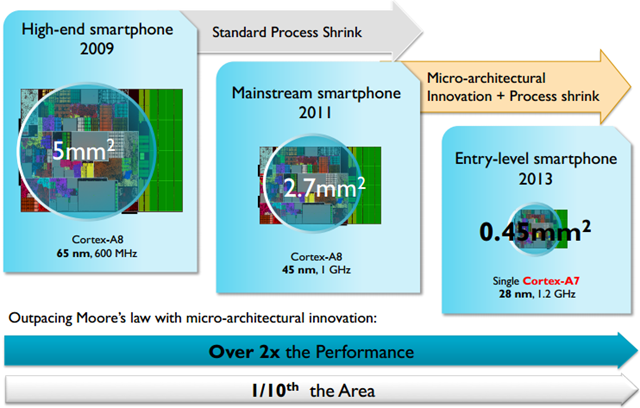

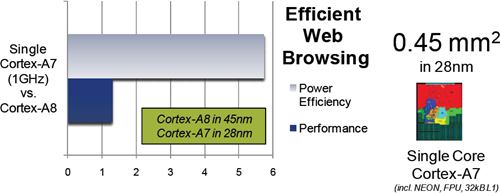

– now contributes to approximately one-third of all smartphone shipments worldwide

– real development opportunities began in H2 2009 with possibility to go even against Intel Atom (source: Computex 2009 – Warren East Presentation [ARM Holdings, June 1, 2009]):

with improving Cortex-A9 performance on 45nm process achieved through:

– 56% improvement from processor and physical IP optimisations

– 44% improvement from other techniques

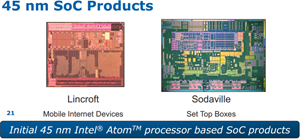

The first SoC products based on 45nm technology came in 2011, namely:

– NXP PNX 847x/8x/9x set-top box SoCs sampling in January 2010. However a month later the business related to these products was sold to Trident Microsystems (see the PNX8490/PNX8491 datasheet of February 2010) and as Trident had experienced continuing operating losses it filed for bankruptcy in January 2012. Its set-top box SoC business had been taken over by Entropic Communications, Inc. in April 2012. Although only the PNX8475 is currently offered by Entropic the original Cortex-A9 related SoC know-how is flourishing quite well there (see also: 1, 2, 3 and 4).

– Samsung Orion application processor, later renamed into Samsung Exynos 4210 then further into Exynos 4 Dual, announced in September 2010 for sampling in Q4 2010 and mass production in H1 2011. It first came out with the Samsung Galaxy S II smartphone announced in February 2011 for May 2011 delivery. Other Samsung smartphone and tablet products then followed.

– Texas Instruments OMAP 4430 and OMAP 4440 (later renamed OMAP 4460) application processors announced in February 2009 for sampling in H2 2009 and expected production by the second half of 2010, but actually debuted a year later in February 2010 with sampling available and expected production in H2 2010. The first product based on OMAP 4430 was the BlackBerry PlayBook tablet announced in September 2010 for early 2011 availability but becoming available in June 2011 only. Smartphone products from Motorola (a lot, also a few tablets) and LG (a few) followed that, as well as a number of tablet products from Archos and most notably the Kindle Fire from Amazon, and the Nook from Barnes & Noble.

ARM is representing and projecting the evolution of the market since then as follows:

More information about that was provided in:

Cortex-A12: Diversification in the Mobile Market – Serving the Mid-Range [ARM Smart Connected Devices blog, June 3, 2013]

Mobile devices have become indispensable in North America, Europe, and much of Asia, and are becoming the primary compute platforms for people in emerging markets. We are entering a new era of computing, the post-PC era. ARM® technology has been at the heart of the mobile revolution for over twenty years and continues to be the bedrock of all innovation and change in this space.

Mobile devices, such as smartphones and tablets, are connecting billions of people. In 2013, we are expecting:

– Over 1 billion smartphones forecasted to ship*

– Smartphones for <$50 and Tablets >$800

– Tablets out-ship notebook PCsWhat becomes clear when looking at mobile devices is that we are seeing segmentation into multiple markets, which is an opportunity for growth for ARM partners:

– Premium devices: Price range > $400

– Mid-range devices: Price range between > $200 and < $350

– Entry-level devices: Price range up to $150Source: Mixture of ARM and Gartner Estimates

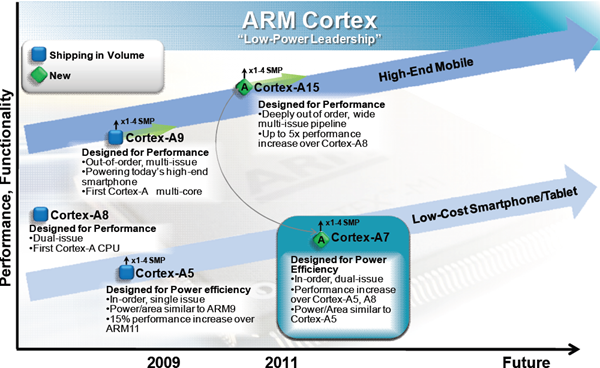

Premium smartphones and tablets receive a great deal of attention, but it is the entry-level and mid-range markets are expected to grow the fastest over the next years. ARM delivered the Cortex®-A7 processorin the fourth quarter of 2011, and it is now shipping in large volumes in low-cost, quad-core devices. It will be followed by the Cortex-A53 processor, which is soon to be released to lead partners. Both are high-efficiency processors, that are efficient by simple in-order eight stage pipelines which are highly efficient and tuned to deliver very good performance for their size. In the mid-range mobile device market, the industry had tremendous success with devices based on the higher-performance Cortex-A9 processor, which uses a partially out-of-order, nine stage pipeline to achieve high performance tuned to the power constraints of smartphones. The Cortex-A9 processor was released in 2008 and now contributes to approximately one-third of all smartphone shipments worldwide.

The market segmentation is driving the diversification in mobile and resulting in many different requirements needed to achieve the highest performance and lowest power within a sustained thermal envelope. These requirements make it mandatory to provide the functionality previously available only in premium devices, but within the power budgets of mid-range devices. Looking at how to serve those markets, it is clear that one size does not fit all anymore.

Today ARM is introducing the Cortex-A12 processor, the highest performance mid-range CPU that is specifically designed for the next-generation mid-range mobile market. The Cortex-A12 processor brings its own mix of high performance and energy efficiency to 2014 SoC designs: more performance than the Cortex-A9 processor with the same mobile-tuned power efficiency. The Cortex-A12 processor is designed to deliver the best mobile experience:

– Highest performance at lowest power consumption and cost

– Highest efficiency within mid-range thermal envelopes, i.e. achieve highest performance at uncompromised area

– Premium feature set in mid-range mobileThe Cortex-A12 processor is the successor to the Cortex-A9 processor and increases single-thread performance by 40 percent, while matching the best-in-class energy efficiency. Measured in 28nm, the Cortex-A12 processor is about 30 percent smaller in area compared to the Cortex-A9 processor in 40nm technology using the same configuration. Additionally, the Cortex-A12 processor brings today’s premium smartphone features into the mid-range, allowing new use cases and great mobile experiences. Some key added features include:

– big.LITTLE™ processing enables the extension of the dynamic range of the Cortex-A12 processor with the addition of the Cortex-A7 processor

– Virtualization and TrustZone® security support enabling new use cases like BYOD (bring your own device)

– 1TB addressable memory, providing close to no boundaries on memory spaceThe Cortex-A12 processor extends the performance capability in mid-range devices without sacrificing energy efficiency when combined with the Cortex-A7 processor as a big.LITTLE CPU subsystem. big.LITTLE processing provides a highly efficient, high-performance processing solution that can scale to many different use cases. The first iterations of big.LITTLE processing featured the Cortex-A15 and Cortex-A7 processors for high-end solutions. Now, the Cortex-A12 processor is bringing big.LITTLE processing to increase the dynamic range of the mid-range by enabling SoC designers to push the Cortex-A12 processor further while using the Cortex-A7 processor to reduce power well below levels of the Cortex-A9 Processor. This results in an ideal combination of compute resource for efficient workload distribution, running lightweight tasks on the Cortex-A7 processor and high-performance tasks on the Cortex-A12 processor. Early results show up to 2x increased efficiency.

Even though it is designed for mid-range smartphone and tablet devices, the Cortex-A12 processor leads with an excellent efficiency profile, making it an ideal fit for other use cases like home networking, residential gateway and auto infotainment systems.

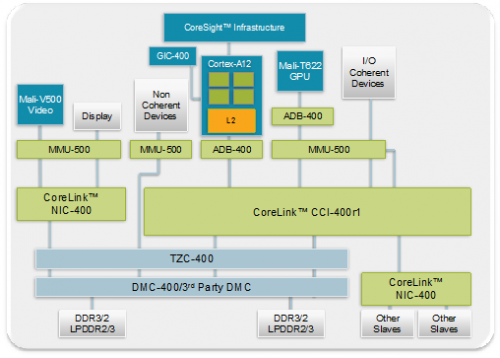

ARM has also designed the Cortex-A12 processor to work efficiently with a complimentary family of high performance, low power ARM CoreLink™ System IP components:

The system diagram shown above illustrates the system IP components that will typically support the Cortex-A12 processor in a mobile SoC. To deliver effortless 1080p30 graphics with 1080p encode/decode the system also features a Mali™-T622 GPU supporting OpenGL/ES 3.0 and a Mali-V500 video accelerator.

The CoreLink CCI-400 cache coherent interconnect provides an IO coherent channel with Mali and opens up a number of exciting possibilities for offload and acceleration of tasks. When combined with a Cortex-A7 processor (not shown) on the ACE port, CCI-400 also allows big.LITTLE operation with full L2 cache coherency between the Cortex-A12 and Cortex-A7 processors. Efficient voltage scaling and power management is enabled with the CoreLink ADB-400 enabling efficient DVFS control of the Cortex-A12 processor.

CoreLink MMU-500 provides a hardware accelerated, common memory view for all SoC components and minimizes software overhead for virtual machines to get on with other system management functions. In this system, the Cortex-A12 processor also enjoys a secure, optimized path to memory to further enhance its market-leading performance with the aid of CoreLink TZC-400 TrustZone address space controller and DMC solution. All interconnect components and the ARM DMC guarantee bandwidth and latency requirements by utilizing in-built dynamic QoS mechanisms.

ARM POP™ IP supports the physical implementation of the Cortex-A12 processor and Mali GPU to enable best power, performance, and area so critical to success in the highly competitive mid-range SoC market. ARM CoreSight™ debug and trace on-chip hardware, coupled with the ARM DS-5™ software development toolchain, enable the debug of random, time-related software bugs, and the non-intrusive analysis of critical areas of software. The ARM Development Studio 5 (DS-5TM) toolchain also makes use of performance counters embedded in the processor, graphics processor and interconnect to enable system-wide optimization.

The ARM Cortex-A12 processor is the highest-performance, mid-range CPU. It is specifically designed for the mid-range mobile market, and is broadly supported by a range of other ARM technology IP including ARM system IP, POP IP and development tools to enable ARM Powered® solutions that contribute to the very best user experience in terms of responsiveness and battery life. At the same time, it allows ARM partners to accelerate time to market for mid-range SoCs, while freeing development time to add their own differentiation. The Cortex-A12 is a highly tuned processor that will bring the performance of high-end mobile devices into mid-range smartphone and tablets, as well as into other great market opportunities we haven’t even considered.

* Source: Bank of America

Related Blogs:

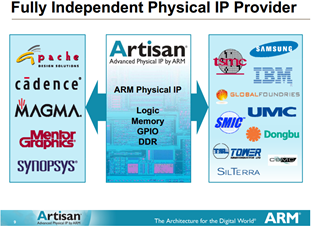

ARM and GLOBALFOUNDRIES to Optimize Next-Generation ARM Mobile Processors for 28nm-SLP Process Technology [press release, June 3, 2013]

New ARM POP technology provides core-hardening acceleration for Cortex-A12 and Cortex-A7 processors

Milpitas, Calif. and Cambridge, UK, June 3, 2013 – In conjunction with the launch of the ARM® Cortex®-A12 processor, ARM and GLOBALFOUNDRIES today announced new power, performance and cost-optimized POP™ technology offerings for the ARM Cortex-A12 and Cortex-A7 processors for GLOBALFOUNDRIES 28nm-SLP High-K Metal Gate (HKMG) process technology. The Cortex-A12 processor was introduced by ARM today as part of a suite of IP targeting the rapidly growing market for mid-range mobile devices.

The companies will combine ARM’s next-generation mobile processor and POP IP with GLOBALFOUNDRIES 28nm-SLP HKMG process solution, enabling a new level of system performance and power efficiency with the optimum economics necessary to serve the mid-range mobile device market. The new initiative builds on the existing robust ARM Artisan® physical IP platform and POP IP for the Cortex-A9 processor already available on GLOBALFOUNDRIES 28nm-SLP, signifying another milestone in the multi-year collaboration between ARM and GLOBALFOUNDRIES.

Central to this increase in functionality for mid-range mobile devices is the new ARM Cortex-A12 processor. The Cortex-A12 processor provides a 40 percent performance uplift and direct upgrade path from the incredibly successful Cortex-A9 processor, while matching the energy efficiency of its predecessor. The Cortex-A12 processor provides best-in-class efficiency as a standalone solution, but additionally supports the innovative big.LITTLE™ processing technology with the Cortex-A7 processor, bringing this energy-efficient technology to the mid-range. GLOBALFOUNDRIES 28nm-SLP process technology and associated ARM POP IP for the Cortex-A12 processor enables up to 70 percent higher performance (measured single-thread performance) and up to 2x better power efficiency in comparison to a Cortex-A9 processor using 40nm process technology. Designers can achieve even higher performance by trading off for lower power efficiency, depending on their application needs. Click here for more information on the Cortex-A12 processor.

The newest POP technology enables customers to accelerate core-hardening of Cortex-A12 and Cortex-A7 processors on GLOBALFOUNDRIES 28nm-SLP HKMG process. POP IP for Cortex processors has successfully enabled ARM-based SoCs with more than 30 different licenses since being introduced over three years ago. POP IP is composed of three elements necessary to achieve an optimized ARM processor implementation: core-specific tuned Artisan physical IP logic libraries and memory instances, comprehensive benchmarking reports, and implementation knowledge that detail the methodology used to achieve the result, to enable the end customer to achieve the same implementation quickly and at low risk.

“With 580 million mid-range smartphones and tablets forecast to be sold in 2015[i], consumers are increasingly looking for the right combination of performance, low power and cost effectiveness,” said Dr. Dipesh Patel, executive vice president and general manager, Physical IP Division at ARM. “With the Cortex-A12 processor and suite of IP announced today, ARM is delivering an optimized system solution leveraging the most innovative technologies available for this market. The POP IP solution on GLOBALFOUNDRIES 28nm-SLP helps designers balance the performance, power and cost tradeoffs to achieve their targets for this growing market.”

GLOBALFOUNDRIES 28nm-SLP technology is ideally suited for the next generation of smart mobile devices, enabling designs with faster processing speeds, smaller feature sizes, lower standby power and longer battery life. The technology is based on GLOBALFOUNDRIES’ “Gate First” approach to High-K Metal Gate (HKMG), which has been in volume production for more than two years. The technology offers a combination of performance, power efficiency and cost that is ideally suited for the mid-range mobile market.

“GLOBALFOUNDRIES is committed to a deep relationship with ARM to enable best-in-class solutions for our mutual customers. Our collaboration on the ARM Cortex-A12 processor implementation is a direct result of this focus and collaboration,” said Mike Noonen, executive vice president of Marketing, Sales, Design and Quality at GLOBALFOUNDRIES.

GLOBALFOUNDRIES’ next-generation 14nm-XM FinFET technology is expected to bring another dimension of enhanced power, performance and area for ARM mobile processors. A Cortex-A9 processor implemented on 14nm-XM technology, using 9-track libraries, is projected to enable a greater than 60 percent increase in frequency at constant power, or a decrease of more than 60 percent in power consumption at constant performance, when compared to implementation on 28nm-SLP technology using 12-track libraries. Similar results are expected for Cortex-A12 processor implementations. Click here for more details on GLOBALFOUNDRIES’ 14nm-XM FinFet technology.

For further discussions about GLOBALFOUNDRIES process technologies or ARM IP offerings please visit the companies’ respective exhibits at the Design Automation Conference (DAC), June 3-5, 2013 in Austin, Texas. ARM is located in booth 931, and GLOBALFOUNDRIES can be found at booth 1314.

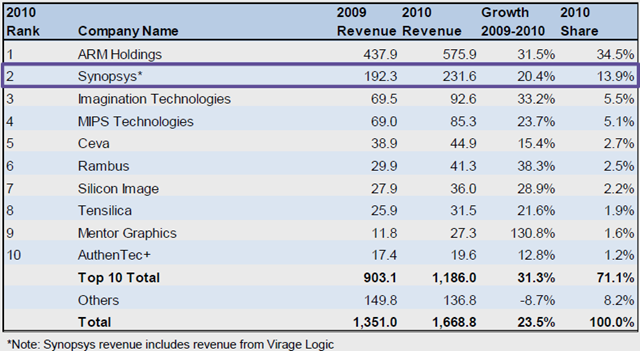

The future of the semiconductor IP ecosystem

December 13 Report:

– Intel’s next-gen SoC manufacturing process will be able to deliver the next Bay Trail Atom only for 2014 products (with higher end Haswell for H2 2013), and it is just a 26nm process in terminology used by the foundry industry not a 22nm one touted by Intel