| <b>Consistency vs. Coherence</b>                                              |                                 |                    |

|-------------------------------------------------------------------------------|---------------------------------|--------------------|

| Terminology                                                                   |                                 |                    |

| <ul> <li>some confusion in liter</li> </ul>                                   | <b>rature</b>                   |                    |

| » but it's rare so be cle                                                     | ar and avoid "mutt"             | ' status           |

| • key is that they are dif                                                    | ferent                          |                    |

| Coherence                                                                     |                                 |                    |

| • defines what value is r                                                     | eturned by a read               | 4                  |

| » e.g. value of the last                                                      | write                           |                    |

| <ul> <li>Consistency</li> </ul>                                               |                                 |                    |

| <ul> <li>defines when things ar</li> </ul>                                    | re coherent                     |                    |

| <ul> <li>bigger issue as system</li> </ul>                                    | ns get bigger                   |                    |

| <ul> <li>sequential consistency</li> </ul>                                    | $y \rightarrow$ value of the la | ast write          |

| » as determined by the                                                        | "decider"                       |                    |

| Both are critical for cor                                                     | rrectness                       |                    |

| <ul> <li>varies as to whether c</li> </ul>                                    | onsistency is exp               | osed to programmer |

| <ul> <li>» sequential consistent</li> <li>• same as usual sequence</li> </ul> | •                               | •                  |

| School of Computing<br>University of Utah                                     | 8                               | <b>CS6810</b>      |

| <b>Performance Issues</b>                                          |                                                           |                 |

|--------------------------------------------------------------------|-----------------------------------------------------------|-----------------|

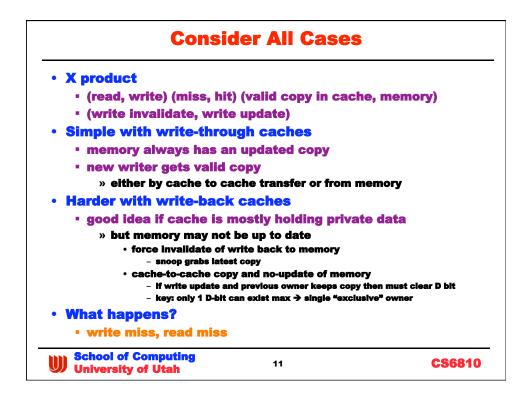

| • Too many to exhaustive                                           | ely list                                                  |                 |

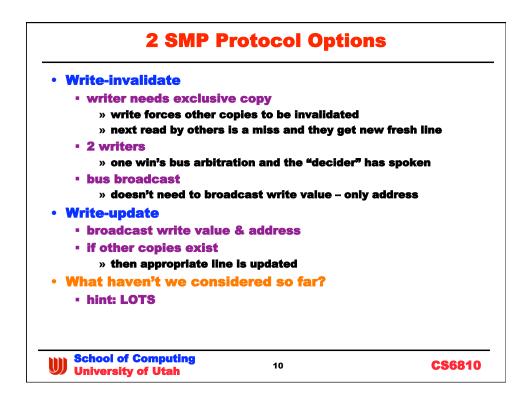

| Key protocol choice iss                                            | sues                                                      |                 |

| <ul> <li>multiple writes to the s</li> </ul>                       | same line write inv                                       | <b>validate</b> |

| » less bus traffic                                                 |                                                           |                 |

| • 1 <sup>st</sup> write → bus inva                                 |                                                           |                 |

| <ul> <li>and data transfer</li> <li>subsequent writes a</li> </ul> |                                                           |                 |

| - as long as there is                                              | •                                                         |                 |

| » typically Wr-Inv is be                                           |                                                           |                 |

|                                                                    | red by one processor at                                   | a time          |

| <ul> <li>write-update</li> <li>» every write generates</li> </ul>  | a hua fraffia                                             |                 |

|                                                                    | s pus tramc<br>issue so it easily satura                  | ates            |

| » still it wins when                                               |                                                           |                 |

|                                                                    | ng hammered by multiple<br>• 1 writer and the rest are co | •               |

| • Programs share variabl                                           | es not cache line                                         | BS              |

| • issues?                                                          |                                                           |                 |

| School of Computing<br>University of Utah                          | 12                                                        | C\$6810         |

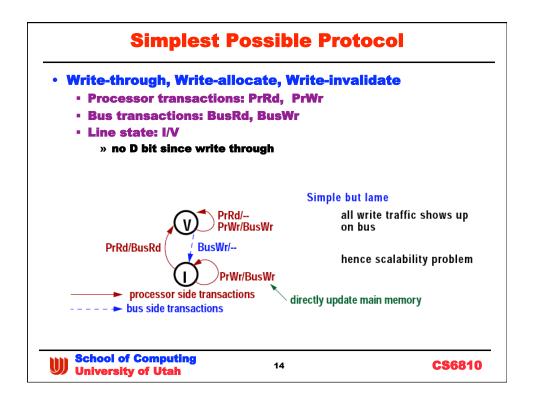

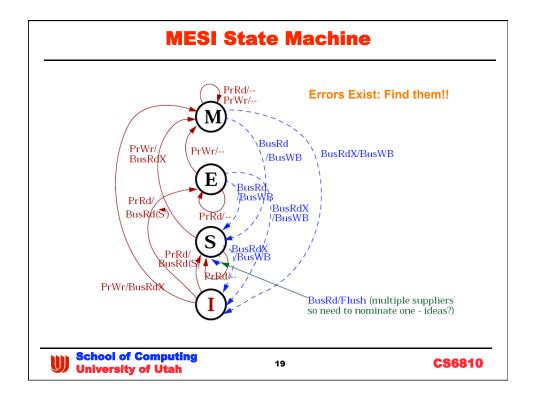

| <b>MESI Protocol</b>                                                       |                     |  |

|----------------------------------------------------------------------------|---------------------|--|

| Add Exclusive state                                                        |                     |  |

| <ul> <li>deals w/ PrRd followed by PrWr p</li> </ul>                       | roblem              |  |

| <ul> <li>meanings change a bit</li> </ul>                                  |                     |  |

| » E = exclusive clean – memory is c                                        | consistent          |  |

| » M = exclusive dirty – memory is in                                       | nconsistent         |  |

| » S = 2 or more sharers, no writers,                                       | , memory consistent |  |

| » i = same as always                                                       |                     |  |

| <ul> <li>New S semantics adds an addition</li> </ul>                       | onal problem        |  |

| <ul> <li>a shared signal must be added to</li> </ul>                       | the bus             |  |

| » single wired-OR wire is sufficient                                       |                     |  |

| note scaling problem – doesn't wa                                          | • •                 |  |

| » BusRd(S) – shared signal asserted<br>busRd(S) – shared signal asserted   |                     |  |

| » BusRd(S') – shared signal not ass » BusRd – means den't care shout to    |                     |  |

| » BusRd – means don't care about s<br>» FLUSH – optional for cache to care | -                   |  |

| School of Computing<br>University of Utah                                  | <b>CS681</b> 0      |  |

| Key Points                                 |                       |                   |

|--------------------------------------------|-----------------------|-------------------|

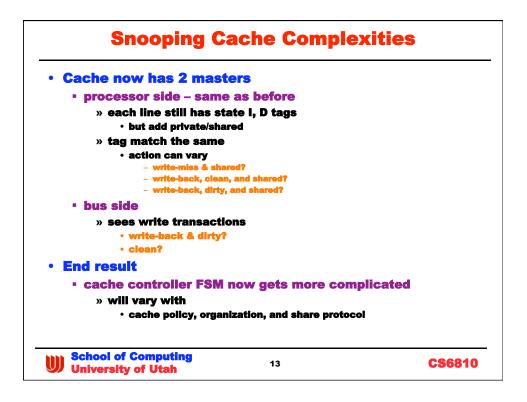

| • Status tags                              |                       |                   |

| need to encode the loc                     | cal line status       |                   |

| » protocol dependent                       |                       |                   |

| • 2 ported cache control                   | ler                   |                   |

| <ul> <li>priority becomes the b</li> </ul> | us                    |                   |

| » since it's the atomic                    | ty point              |                   |

| possibly stalls process                    | s requests            |                   |

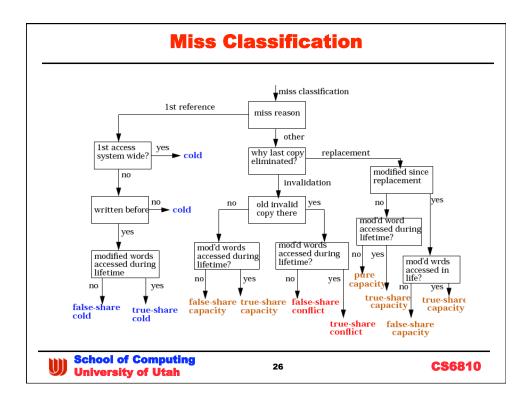

| <ul> <li>New miss source</li> </ul>        |                       |                   |

| • the 4 <sup>th</sup> C: Coherence         |                       |                   |

| » true shared miss: rea                    | ds and writes to sam  | ne target         |

| » false shared miss: re<br>same line       | ads and writes to dif | ferent target but |

| <ul> <li>Increased bus pressure</li> </ul> |                       |                   |

| <ul> <li>due to coherence traff</li> </ul> | ic                    |                   |

| » increased power                          |                       |                   |

| <ul> <li>already a scaling prob</li> </ul> | lem                   |                   |

| School of Computing                        | 24                    | CS6810            |

| University of Utah                         |                       |                   |

|        | <b>Concluding Remarks</b>                                                          |                             |  |

|--------|------------------------------------------------------------------------------------|-----------------------------|--|

| • Ho   | w well does it work                                                                |                             |  |

|        | see Chap. 4.3 data                                                                 |                             |  |

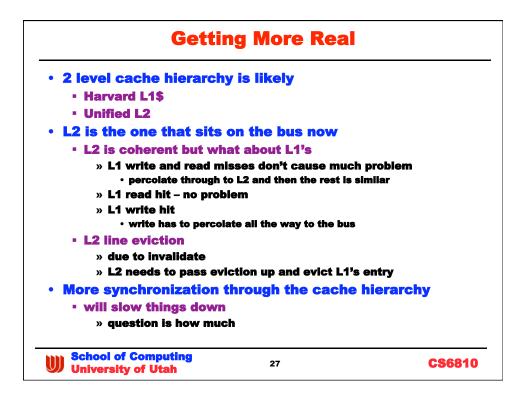

| • Is § | SMP dead because buses are                                                         | dead?                       |  |

|        | small way SMP may make sense                                                       | 1                           |  |

|        | » on multi-core socket                                                             |                             |  |

|        | » or in small clusters where socke                                                 | et is multi-cluster         |  |

|        | short buses aren't so bad                                                          |                             |  |

|        | » easy enough to extend life with                                                  | point to point interconnect |  |

| • Nex  | xt we move onto DSM variant                                                        | of CC-Numa                  |  |

|        | protocol ideas are still valid                                                     |                             |  |

|        | » hence the time spent to underst spent                                            | -                           |  |

|        | <ul> <li>note exam question is highly like<br/>main difference with DSM</li> </ul> | ily                         |  |

|        | » lines have both                                                                  |                             |  |

|        | <ul> <li>Intes have both</li> <li>local state: similar to today's dis</li> </ul>   | cussion                     |  |

|        | • global state: more on that next lo                                               |                             |  |

|        | hool of Computing                                                                  | C86040                      |  |

| 🖤 Un   | iversity of Utah 28                                                                | CS6810                      |  |