# NASA Contractor Report 145334

(NASA-CE-145334)INVESTIGATION OF CHARGEN79-14796COUPLED DEVICE CORRELATION TECHNIQUESProgress Report, Dec. 1974. - Sep. 1977Unclass(Westinghouse Electric Corp.)175 p'HCUnclassA08/MF A01CSCL 08B G3/6040854

# Investigation of Charge Coupled Device Correlation Techniques

# D.R. Lampe, H.C. Lin, T.J. Shutt

Westinghouse Electric Corp. Linthicum Heights , Maryland 21090

Contract NASI-13674 Period Covered : Dec.74 through Sept.77 October 1978

Langley Research Center Hampton, Virginia 23665

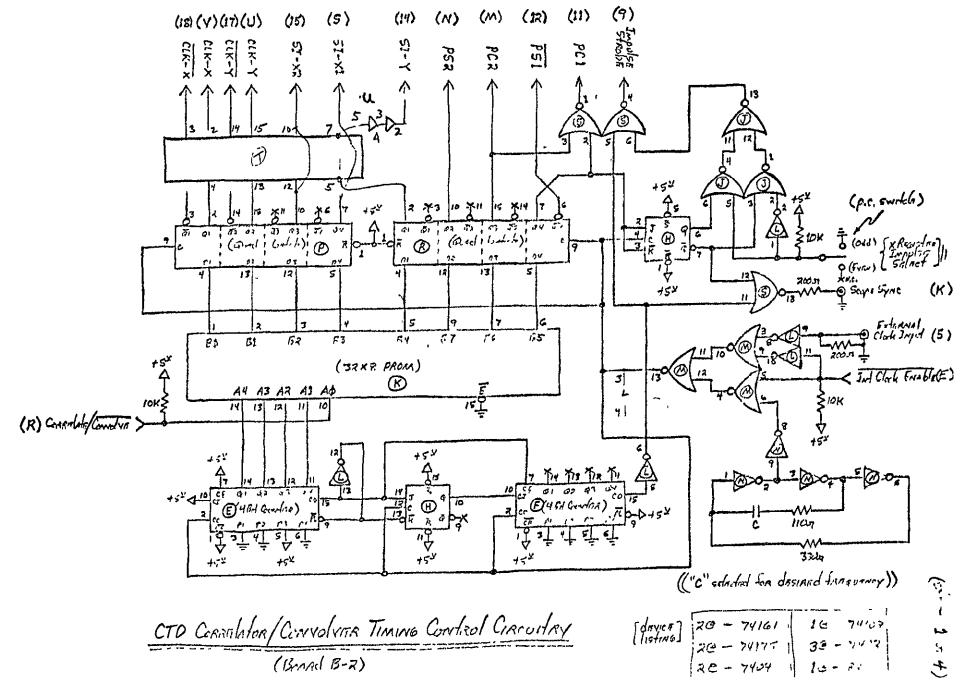

# NOTICE

THIS DOCUMENT HAS BEEN REPRODUCED FROM THE BEST COPY FURNISHED US BY THE SPONSORING AGENCY. ALTHOUGH IT IS RECOGNIZED THAT CERTAIN PORTIONS ARE ILLEGIBLE, IT IS BEING RELEASED IN THE INTEREST OF MAKING AVAILABLE AS MUCH INFORMATION AS POSSIBLE.

N79-14796

NASA CONTRACTOR REPORT 145334

#### INVESTIGATION OF CHARGE

COUPLED DEVICE CORRELATION

TECHNIQUES

D. R. LAMPE, H. C. LIN, T. J. SHUTT

Westinghouse Electric Corporation Linthicum Heights, Maryland 21090

CONTRACT NAS1-13674 Period Covered: Dec 74 through Sep 77 October 1978

# TABLE OF CONTENTS

|     |                        |                                                                                                                  | -        |  |  |

|-----|------------------------|------------------------------------------------------------------------------------------------------------------|----------|--|--|

|     |                        |                                                                                                                  | PAGE     |  |  |

| 1.0 | INTRODUCTION           |                                                                                                                  |          |  |  |

| 2.0 | ELEMENTS OF THE DEVICE |                                                                                                                  |          |  |  |

|     | 2.1                    | Analog Delay Lines With Independent Parallel<br>Nondestructive Readout (NDRO)                                    | 5        |  |  |

|     | 2.2                    | Multiplying Elements                                                                                             | 7        |  |  |

|     |                        | 2.2.1 Logarithmic Diodes, Addition, Anti-<br>Log-Transistor                                                      | 7        |  |  |

| -   |                        | 2.2.2 Pentode Difference of Squares<br>2.2.3 MOSFET Triode                                                       | 13<br>21 |  |  |

| 3.0 | MULT                   | IPLIER BIAS CONCEPTS                                                                                             | 24       |  |  |

|     | 3.1                    | Triode Self-Bias                                                                                                 | 24       |  |  |

|     | 3.2                    | Complementary Buffers                                                                                            | 27       |  |  |

| 4.0 | DIST                   | ORTION ERROR TRIODE MULTIPLIERS                                                                                  | 29       |  |  |

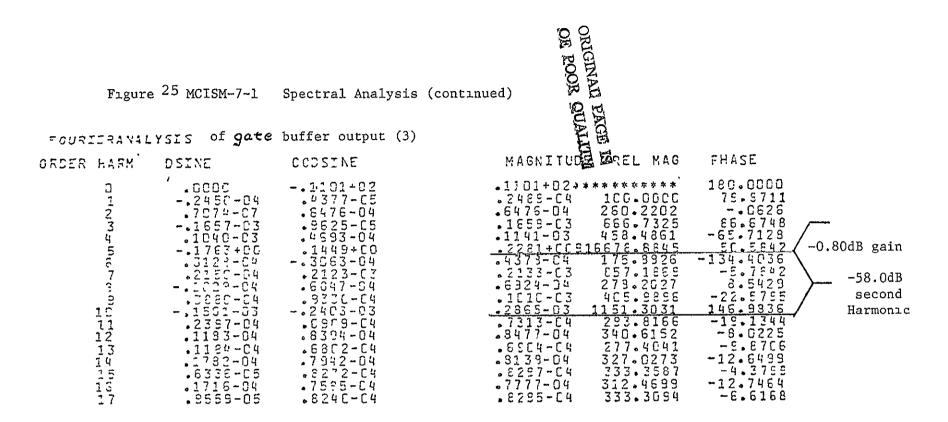

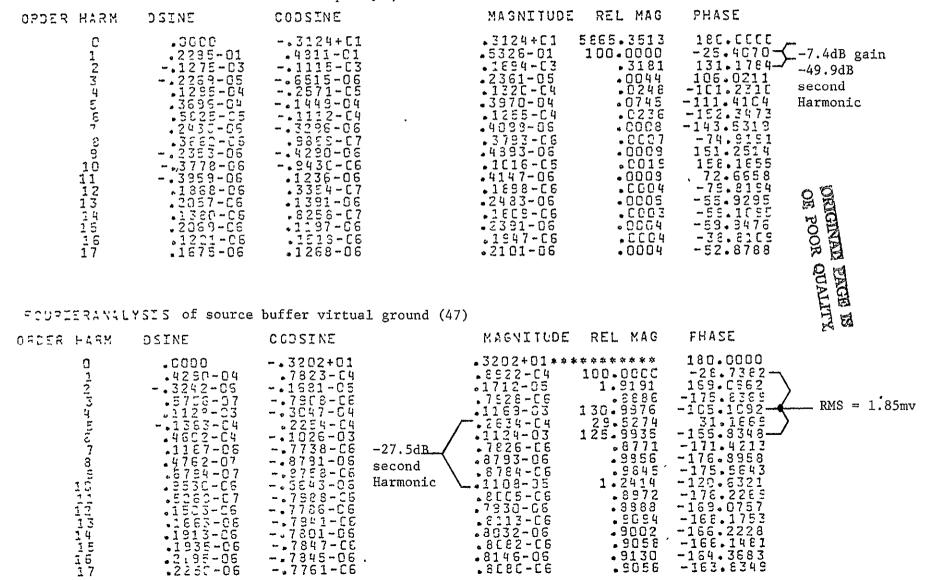

|     | 4.1                    | "Gate Signal" Harmonics from the Drain Buffer                                                                    | 29       |  |  |

|     | 4.2                    | "Drain Signal" Harmonıcs from the Gate Buffer                                                                    | 30       |  |  |

|     | 4.3                    | "Drain Signal" Harmonics from the Multiplying<br>Triode                                                          | 32       |  |  |

| 5.0 | ARRA                   | Y THRESHOLD NONUNIFORMITIES                                                                                      | 34       |  |  |

|     | 5.1                    | Input Feedthrough for Balanced Triodes                                                                           | 34       |  |  |

|     | 5.2                    | Compensation by Feedback in Floating Gate Reset                                                                  | 34       |  |  |

|     | 5.3                    | Compensation with the Sequential Multiply<br>Operator                                                            | 36       |  |  |

|     | 5.4                    | A Balanced-Input Monolithic Sequential Processor                                                                 | 43       |  |  |

|     | 5.5                    | The Multiplier-Sequential Processor Interface<br>(A MOS Differential Current Input to<br>Voltage Output Circuit) | 58       |  |  |

|     | 5.6                    | A Single-Sided Monolithic Sequential Processor                                                                   |          |  |  |

| 6.0 | COMP                   | UTER MODELING                                                                                                    | 62       |  |  |

|     | 6.1                    | "Singular MOS" Quadruply-Balanced Triodes                                                                        | 63       |  |  |

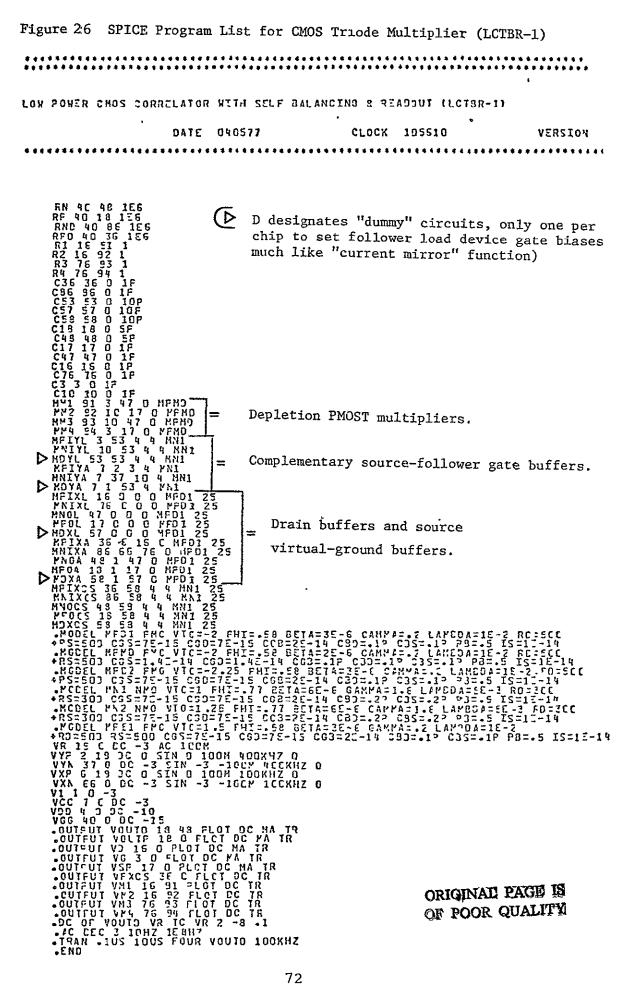

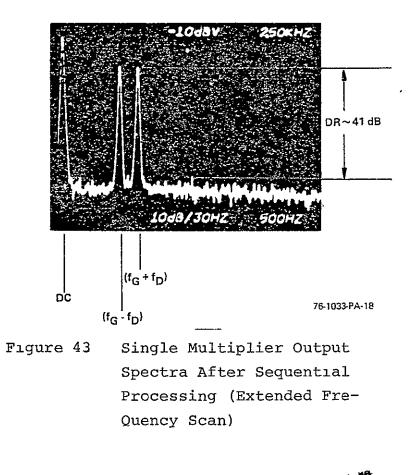

|     | 6.2                    | SPICE Models A CMOS Triode Multiplier                                                                            | 71       |  |  |

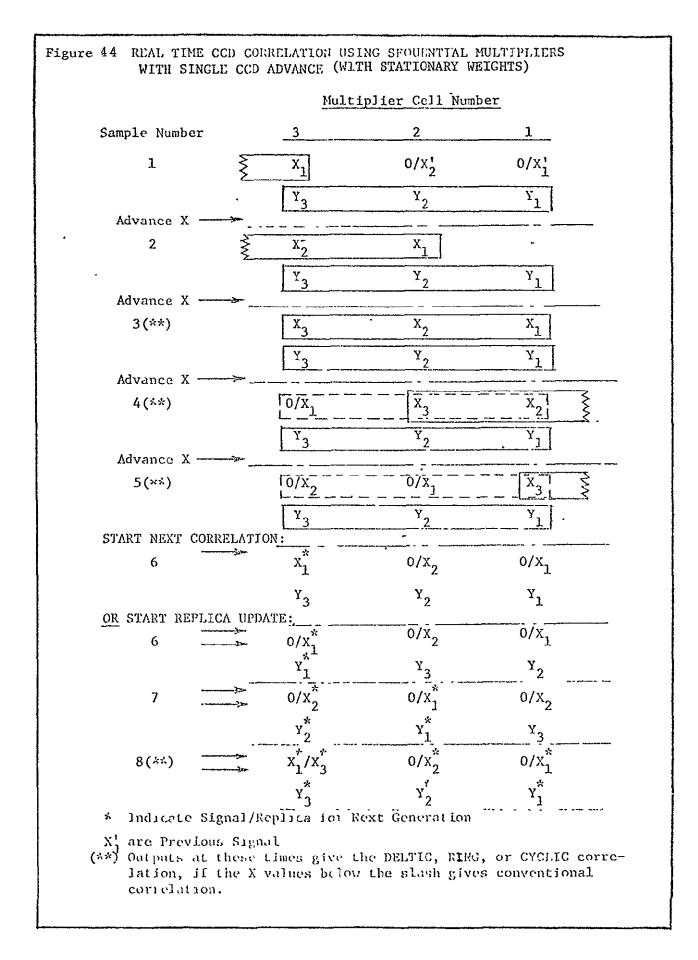

|     | 6.3                    | Performance as a Function of Design and<br>Process Parameters                                                    | 79       |  |  |

#### TABLE OF CONTENTS

# (CONTINUED)

PAGE

.

|      |                      | 6.3.1 Input Dynamic Range<br>6.3.2 Power and Speed versus Sıze                                                                                                     | 81<br>85       |  |  |  |

|------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

|      | 6.4                  | Performance Enhancement Techniques                                                                                                                                 |                |  |  |  |

|      |                      | <ul><li>6.4.1 Doubly and Quadruply Balanced Triodes</li><li>6.4.2 Quadruply-Balanced Triode Configuration</li><li>6.4.3 Sequential Multiply Architecture</li></ul> | 86<br>90<br>92 |  |  |  |

|      | 6.5                  | Performance Comparison: Single Multiplier<br>Versus Multiplier Array                                                                                               | 97             |  |  |  |

| 7.0  | DELIVERED HARDWARE   |                                                                                                                                                                    |                |  |  |  |

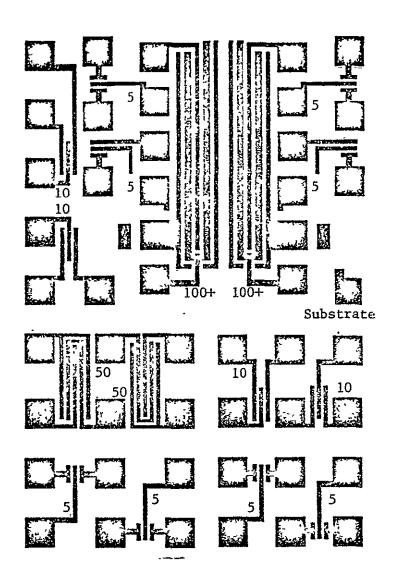

|      | 7.1                  | MOSFET (CCD) Building Block Arrays                                                                                                                                 | 101            |  |  |  |

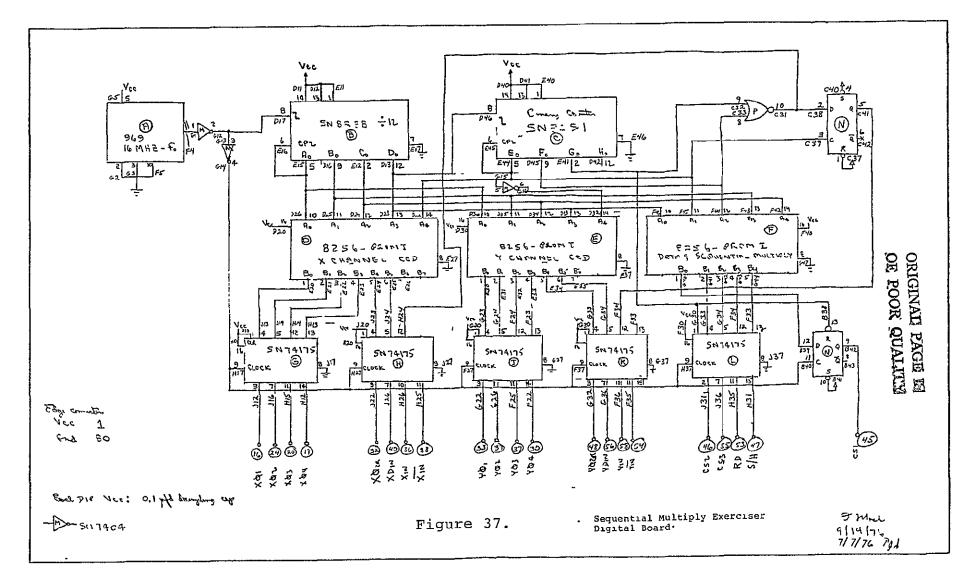

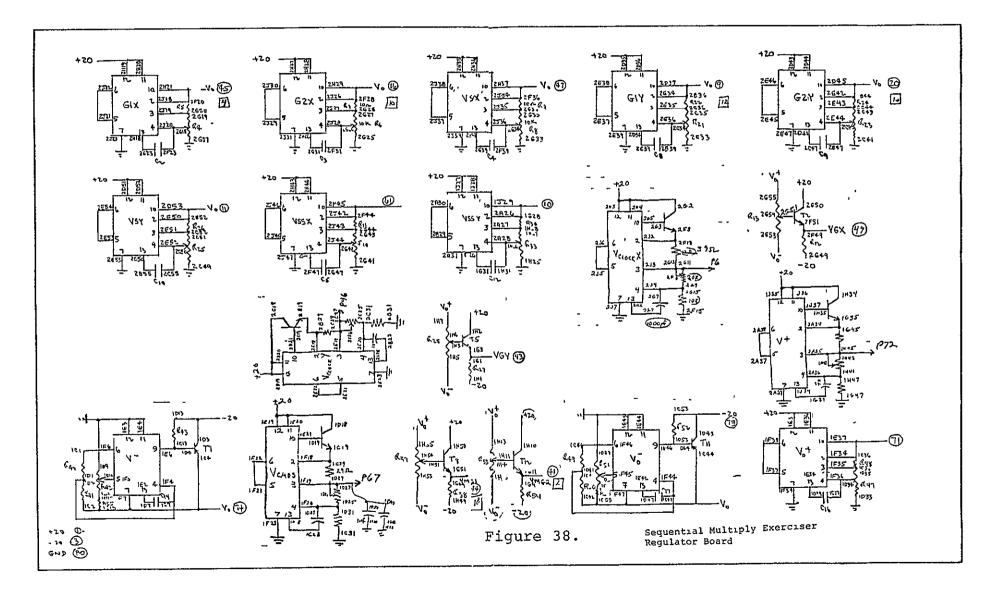

|      | 7.2                  | A Singly-Balanced-Triode Sequential Multiplier<br>(Hybrid, with CCE)                                                                                               | 103            |  |  |  |

|      | 7.3                  | A 16-point Doubly-Balanced-Triode, Sequential-<br>Multiply, Hybrid Correlator                                                                                      | 113            |  |  |  |

|      | 7.4                  | Published Performance Data                                                                                                                                         | 115            |  |  |  |

|      |                      |                                                                                                                                                                    |                |  |  |  |

| 8.0  | FURT                 | HER FACETS OF THE ANALOG CORRELATOR '                                                                                                                              | 121            |  |  |  |

|      | 8.1                  | Fixed Pattern Noise/Errors                                                                                                                                         |                |  |  |  |

|      |                      | 8.1.1 Inpulse Response and Frequency Spectra<br>of Nonuniformities (Or Fixed Patterns)                                                                             | 122            |  |  |  |

|      |                      | 8.1.2 Statistical Evaluation for Devices                                                                                                                           | 127            |  |  |  |

|      |                      | 8.1.3 Further Comparison: Stationary Versus                                                                                                                        | 131            |  |  |  |

|      | 8.2                  | Nonstationary Weights<br>Speed/Multiplıcity Enhancement by Multiplexing                                                                                            | 135            |  |  |  |

| 9.0  | SUMM                 | ARY AND CONCLUSIONS                                                                                                                                                | 13 <b>9</b>    |  |  |  |

| 10.0 | REFERENCES 1         |                                                                                                                                                                    |                |  |  |  |

| 11.0 | ACKNOWLEDGEMENT 14   |                                                                                                                                                                    |                |  |  |  |

| 12.0 | APPENDIX A le        |                                                                                                                                                                    |                |  |  |  |

| 13.0 | DISTRIBUTION LIST 17 |                                                                                                                                                                    |                |  |  |  |

#### 1.0 INTRODUCTION

Analog charge transfer devices (CTD's) offer unique advantages to signal processing systems, which often have large development costs, making it desirable to define those devices which can be developed for general system's use. Such devices are best identified and developed early to give system's designers some interchangeable subsystem blocks, not requiring additional individual development for each new signal processing system. The objective of this work is to describe a discrete analog signal processing device with a reasonably broad system use and to implement its design, fabrication, and testing.

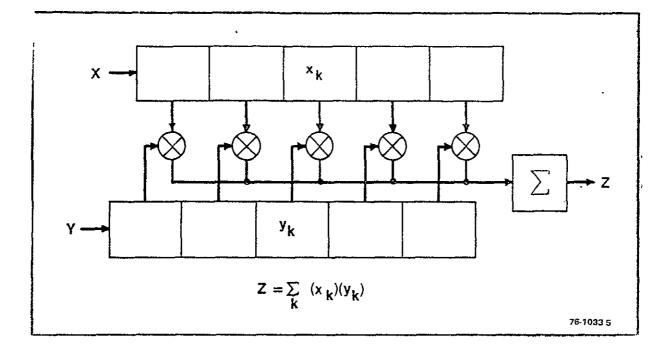

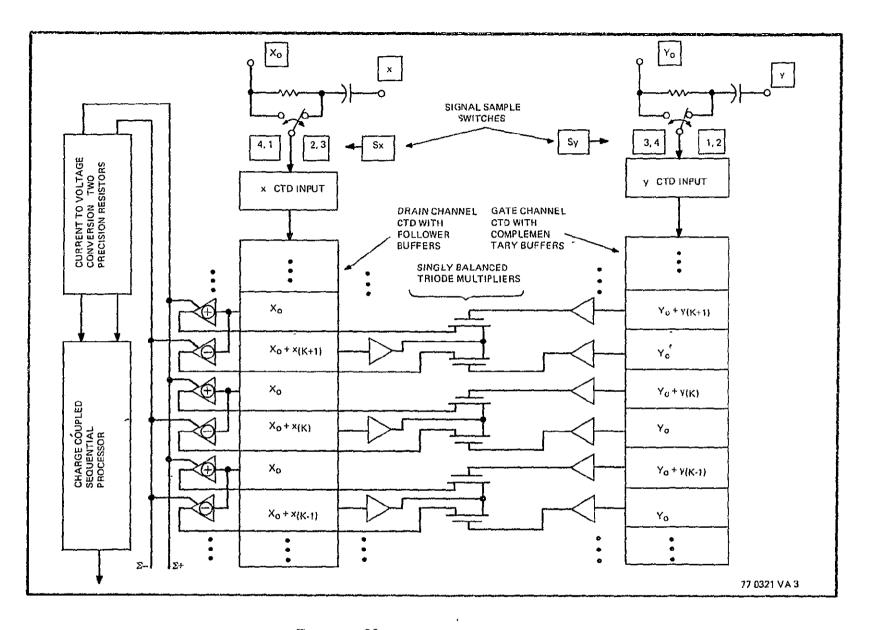

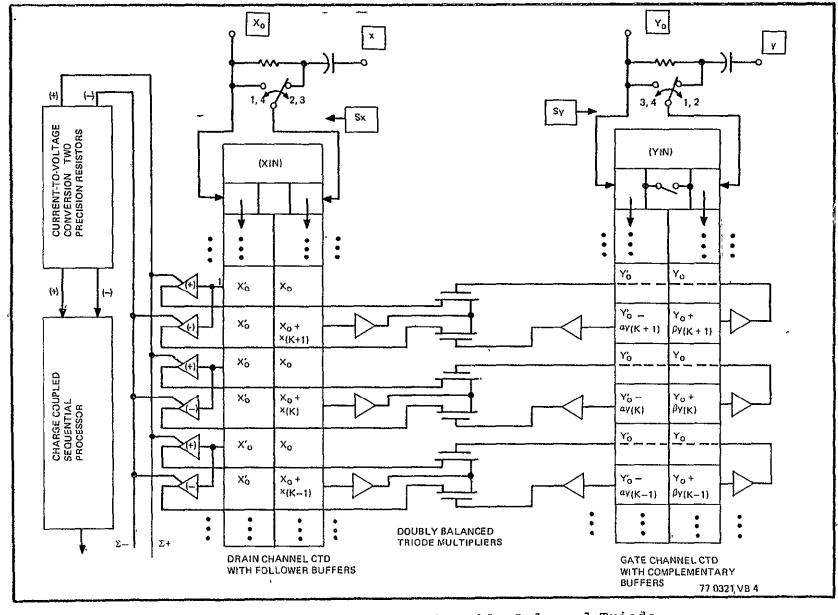

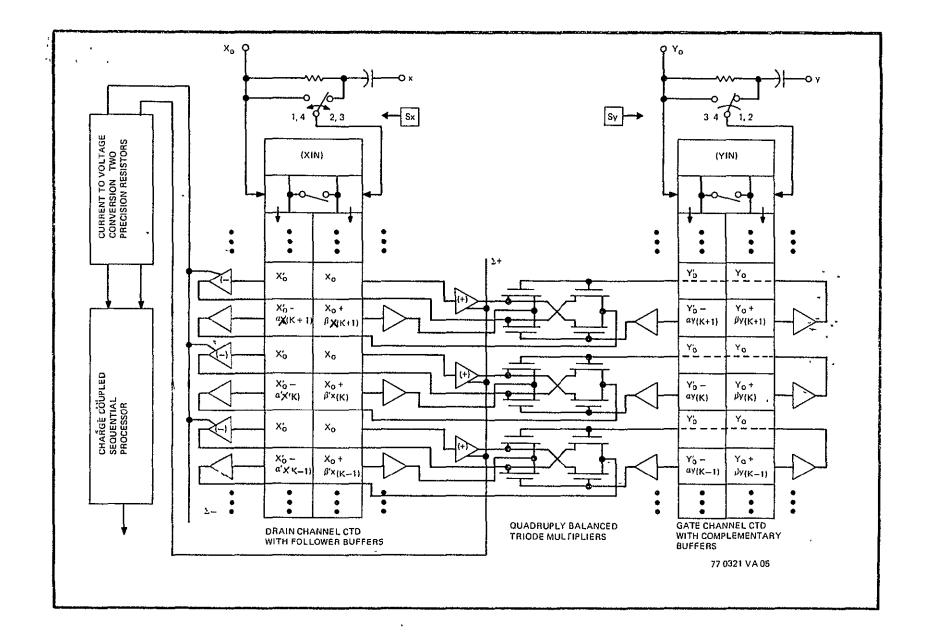

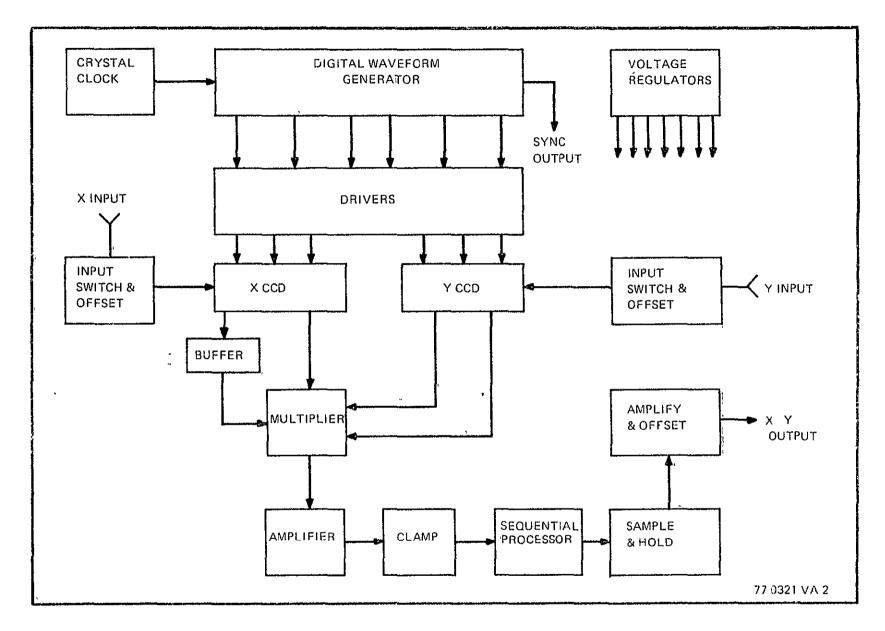

The "Operational Sampled Analog Processor" (OP-SAP) was selected <sup>(1)</sup> as the broadly attractive, general purpose vehicle and is functionally illustrated in Figure 1. Two sets of <u>ANALOG</u> data are presented to parallel analog delay means with the output taken as the sum of the true four-quadrant products. If one set of analog data are shifted by the other set of data, the resulting sequence of computations may be regarded as a discrete convolution function for relative motion in one direction; while relative motion in the other direction gives either a cross-correlation function for different sets of analog data or an autocorrelation function when the same data set is used in both channels. Transversal filters are a further example of a sequence of computations like that shown in Figure 1.

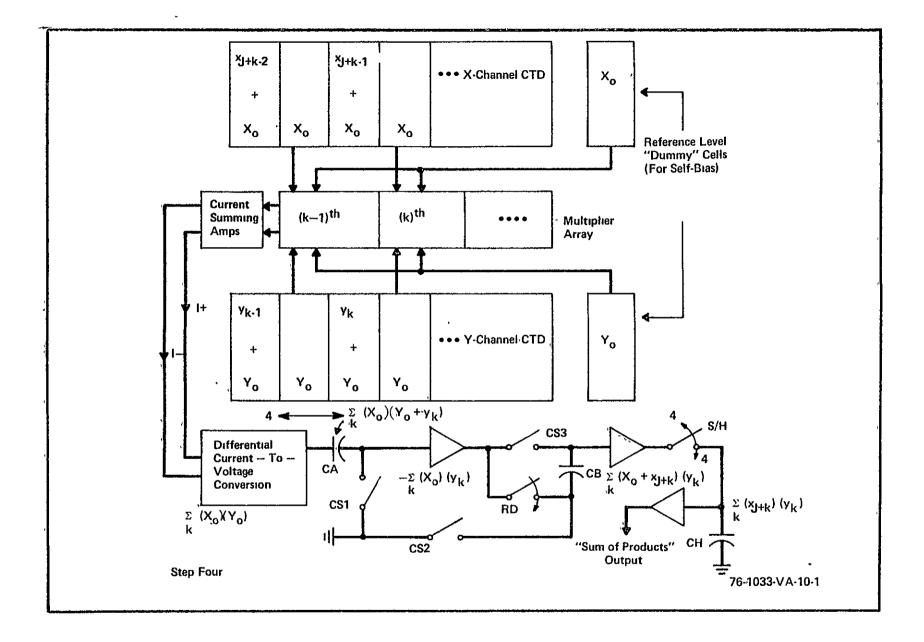

Figure 1 A CTD OP-SAP

Any device capable of the preceding correlation/convolution functions is also capable of a more limited class of applications which may be called analog matrix arithmetic. An example is the analog vector-dot product in which there is one only ONE sum computation with the pairing of analog values to be multiplied together strictly specified before the two data sets are entered into the CTD OP-SAP. Consequently, the motion of one set of analog samples relative to the other is inconsequential for this limited subset of applications. Thus, although of academic interest for the sake of completeness, any analog matrix arithmetic device limited by its inability to move one set of analog samples relative to the other will not be given detailed consideration here because it fails to meet the objective of a broadly useable analog signal processing item. A further restriction on the present investigation of CTD correlation techniques is the format of the input data: both sets of data are purely analog in contrast to binary coded analog for one of the data sets.

Within the boundaries prescribed by the above guidelines, all the essential constituents of a monolithic CTD analog-analog correlator/convolver chip have been investigated and designed on the basis of both experimental and computer model data with most of those elements subsequently incorporated into a hybrid model demonstrating the accuracy and feasibility of the preceding monolithic design effort. After the basic elements of the device are described, two attractive concepts for the bias of the multipliers are presented. Discussed next are some sources of deviations from

true analog-analog multiplication, such as harmonic distortion and direct feedthrough of the input signals due to unbalances from array threshold nonuniformities, as well as corrective measures to reduce the problems. Computer models illustrate the design technique based on the desired fabrication process and performance specifications including some broadly limiting formulas relating performance to fabrication and operation parameters. These formulas are tested against other published performance data after a description of the previously delivered hardware. The summary and conclusions follow additional information on fixed pattern noise and multiplexing of analog-analog correlators.

#### 2.0 ELEMENTS OF THE DEVICE

The basic device elements shown in Figure 1 are of two types: an array of multiplying means disposed between two analog delay means. Since substantial effort has previously been devoted to the needed analog delay means, only a brief comparison of the various attractive possibilities is now presented.

2.1 Analog Delay Lines With Independent Parallel Nondestructive Readout (NDRO)

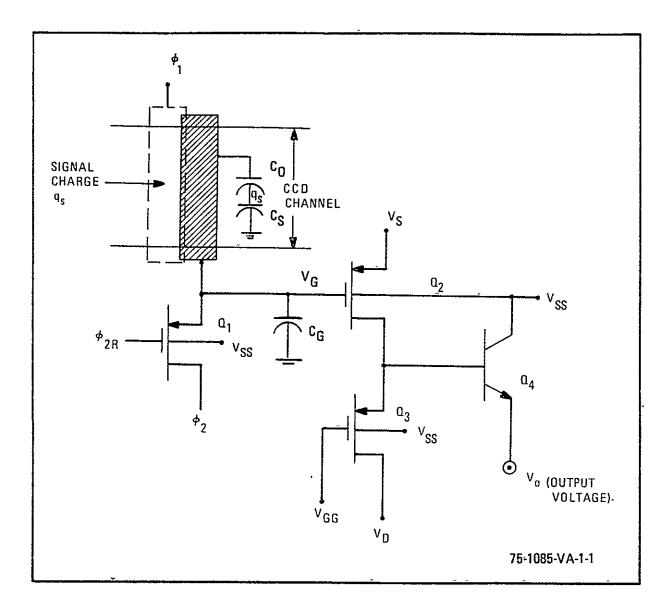

A technique for NDRO in charge transfer devices is to sense the displacement of majority carrier charge which occurs when miniority carriers in a CCD move beneath a floating CCD electrode. Figure 2 illustrates the use of a floating clock electrode technique to convert the signal charge  $q_s$  to a voltage  $v_g$  on the gate of a MOS electrometer amplifier:

$$v_{\rm G} = \frac{C_{\rm o}^{\rm q} s}{C_{\rm s}(C_{\rm o} + C_{\rm g}) + C_{\rm o} C_{\rm g}}$$

where  $C_{\rm G}$  is the external capacitance associated with the reset switch  $Q_1$ , parasitic interelectrode capacitance, and gate capacitance of  $Q_2$ . Thus, considerable loading effects are present at each tap position in addition to a nonlinearity which results from charge sharing between  $C_{\rm S}$  and the other capacitances. The minority carrier charge  $q_{\rm S}$  is not disturbed, however, and the signal results from a redistribution of charge originating in the clock electrode drive circuitry. Such a technique is employed in the split-electrode type of CCD structures.

Figure 2 Floating Clock Electrode Sensor Tap Circuit for NDRO of Analog Signals in a CCD Delay Line

A reset switch is employed in the tap circuitry of Figure 2 in order to avoid long-term drift effects associated with avalanche injection charging of the floating electrode.

#### 2.2 Multiplying Elements

Of the various schemes to achieve electrical analog multiplication, only three merit serious consideration for integration with CTD analog delay lines: MOSFET triodes, difference of squares using MOSFET pentodes, and a combined MOSFET/bipolar log-add-antilog approach. The bipolar transconductance multiplier is analogous to the MOSFET triode, but is much more sensitive to small voltages than MOSFET's, thereby leading to a potential compatibility problem. The multipliers are described in reverse order, leading up to the MOSFET triode which has been used in all published implementations 2',3,4 to date.

#### 2.2.1. Analog Multiplication with Logarithmic Diodes, Addition, Antilog-Transistor

The characteristic of a junction diode is given approximately as  $I_{D} \stackrel{\approx}{=} I_{s} e^{\Lambda V} D$

where

$$I_D$$

is the dc diode current,  $V_D$  is the dc voltage across the diode,  $I_s$  is the saturation current,  $\Lambda$  is a constant equal to  $(38.6 \text{ W})^{-1}$  at  $27^{\circ}$ C. This equation can be rewritten as

$$V_{\rm D} = \left(\frac{1}{\Lambda}\right) \left[ \ln \left( f_{\rm D} / I_{\rm S} \right) \right].$$

(2)

(1)

If two currents  $I_{D1}$  and  $I_{D2}$  are fed through two separate diodes, the two voltages  $V_{D1}$ ,  $V_{D2}$  across the respective diodes can be added

$$\mathbf{v}_{\mathrm{Dl}} + \mathbf{v}_{\mathrm{D2}} = \left(\frac{1}{\Lambda}\right) \left[ \ln \left(\mathbf{I}_{\mathrm{Dl}} \mathbf{I}_{\mathrm{D2}} / \mathbf{I}_{\mathrm{s}}^{2}\right) \right]$$

(3)

Note that the sum of the voltages is proportional to the logarithm of the product  $I_{D1} I_{D2}$ . Thus, if we impress this sum across the base-emitter junction of a transistor the collector current will be proportional to the product  $I_{D1} I_{D2}$ , because the collector current of a transistor is given as

$$I_{C} \cong I_{cs} e^{\Lambda V_{BE}} = I_{cs} e^{\Lambda (V_{D1} + V_{D2})}$$

(4)

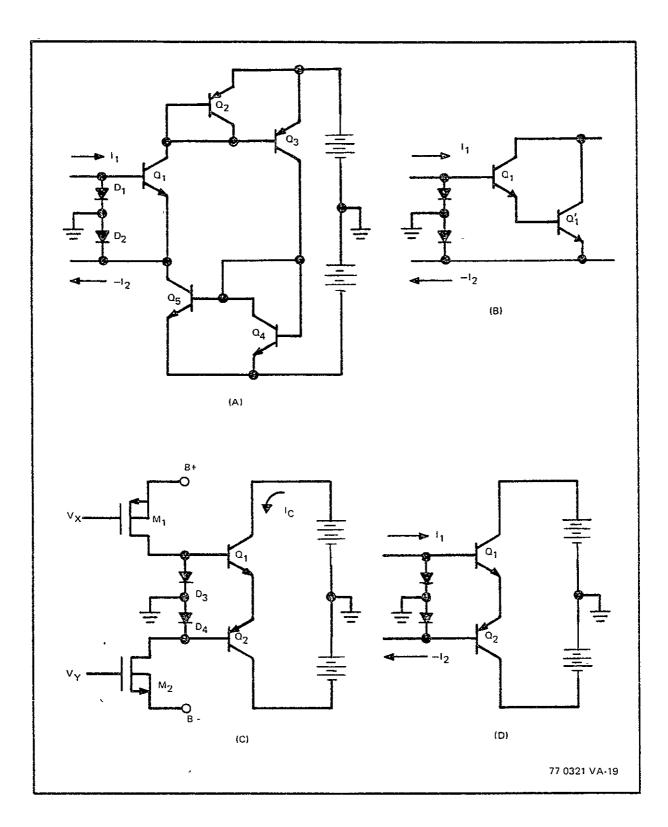

where  $I_{CS}$  is a constant and  $V_{BE}$  is the dc base-emitter voltage which is now equal to  $V_{D1} + V_{D2}$ . A circuit for implementing this logarithmic addition is shown in Figure 8a. The two currents are in opposite polarity. If the common point between the two diodes is grounded, then the emitter of the multiplying transistor  $Q_1$  should not be grounded to avoid short-circuiting the lower diode  $D_2$ . A current mirror consisting of  $Q_2$   $Q_3$   $Q_4$   $Q_5$  may be used to provide a high impedance return path for the emitter of  $Q_1$ .

This circuit has some shortcomings. First, the base-emitter voltage, being equal to the sum of the two diode voltages, would cause an excessively.large collector current to flow if the device sizes of the transistor and the diodes are comparable. From equations (3) and (4), one can derive the collector current

$$I_{C} = \frac{I_{D1} I_{D2} I_{CS}}{I_{s}^{2}}$$

(5)

If the areas and the doping concentrations of the junctions of the diodes and the transistor are comparable, then the  $I_C$  would be orders of magnitude larger than  $I_{D1}$  and  $I_{D2}$ .

$$I_{C} = \frac{I_{D1} I_{D2}}{I_{s}}$$

(6)

Figure 3 Various "Log-Add-Antilog" Multiplying Circuits

Since the saturation current  $I_s$  is usually much smaller than the operating current  $I_D$ , the collector current can be enormous. The foregoing problem can be solved by using two base-emitter junctions across the two diodes, such as the Darlington pair,  $(Q_1, Q_1')$  as shown in Figure 3b. However, the collector currents of the two transistors differ by a factor of  $\beta$ , the current gain; the respective base-emitter voltages are:

$$V_{\rm BE1} = \frac{1}{\Lambda} \ln \frac{I_{\rm C}}{\beta}$$

$$I_{\rm Cs}$$

(7)

$$V_{\rm BE1}' = \frac{1}{\Lambda} \ln \frac{I_{\rm C}}{I_{\rm CS}}$$

(8)

Equating equations (7) and (8) with equation (3)

$$I_{\rm C} = \frac{I_{\rm Cs}}{I_{\rm s}} \sqrt{I_{\rm D1}I_{\rm D2}/\beta}$$

(9)

Thus, the output current is proportional to the square root of the product of the diode currents. For linear multiplication, we should make the diode current proportional to the square of the multiplicand. Furthermore, the signal from the nondestructive readout of a CTD should preferably be applied to the gate of a MOS transistor. Thus, a MOS transistor, operating in the current saturation (pentode) region with a square-law characteristic, can be utilized to furnish both the buffering and the squaring function.

The buffered multiplier circuit is shown in Figure 3c. Note that complementary MOS transistors are used to let the drain current flow into the diode in the proper direction. The dc potentials of the gates are at ground to ensure pentode operation, so long as the

MOS transistors are enhancement-mode devices.

Another scheme for accomplishing the same purpose is to use a pair of complementary bipolar transistors as shown in Figure 3d. The output current is then

$$I_{\rm C} = \frac{\left(I_{\rm CS}\right)}{\left(I_{\rm D1}\right)^2} \left(I_{\rm D1}I_{\rm D2}\right)^2$$

(10)

In either Figure 3b or Figure 3d, it is desirable to make the base current much smaller than the diode currents. Any base current would detract from the diode current and cause deviation from the ideal logarithmic relationship. For this reason, it is desirable to have a high current gain in at least one of the transistors.

In practice, this technique involves both fabrication and performance problems. The manufacturing sequence must simultaneously yield acceptable quality devices of all of the following: CCD's, complementary MOS transistors, and complementary bipolar transistors (with the required high current gain) is hardly a well developed or widely used process. Overlooking such fabrication difficulties, one then encounters the functional problems: In Figure 3c, the voltages  $(V_x, V_y)$  from the CCD include not only the ac signals (x,y) but also biases  $(X_0, Y_0)$  representative of the zero-signal reference level. Thus, the instantaneous output from the circuit of Figure 3c may be written as

$$Z_2 = (X_0 + x) (Y_0 + y)$$

(11)

To obtain the finally desired result, one must similarly generate and combine three more products:

$$xy = Z_4 - Z_3 + Z_2 - Z_1$$

(12)

where

$$z_4 = (x_0) (y_0), z_3 = (x_0 + x) (y_0), z_1 = (x_0) (y_0 + y)$$

To perform the electrical function of equation (12) simultaneously would require replicating the complete circuit of Figure 3c four times with the CMOS FET's of one such replication IDENTICALLY (not nominally) matched for all four replications so as to guarantee that the four separate sets of  $(X_0, Y_0)$  will truly be equal and cancel. That is, each such simulataneous four-quadrant multiplier would need the following sets of perfectly matched devices: 4 PMOST pentodes, 4 NMOST pentodes, 4 high- $\beta$  NPN transistors with matched diodes and independent accessible nodes.

Another aspect of a correlator device based on the multiplying element of Figure 3c is the operation of the two analog delay lines with their respective non-destructive readout. For both the CMOST pentode buffers, Ml and M2, both their sources and drains are connected to low impedance nodes (practically ac virtual grounds) so that interaction from the multiplier through the buffer back into the analog delay line is negligible. But the desired pentode squaring action suggests that  $V_x$  be biased above ground while  $V_y$  be biased below ground, thereby precluding the operation of both delay lines with comparable biases and clock levels. In conclusion, however, the necessarily more

complicated fabrication sequence to obtain fully accessible, high- $\beta$  complementary bipolar transistors as well as CMOST's is a powerful argument against substantial further consideration of the "log-add-antilog" type multiplying element at this time.

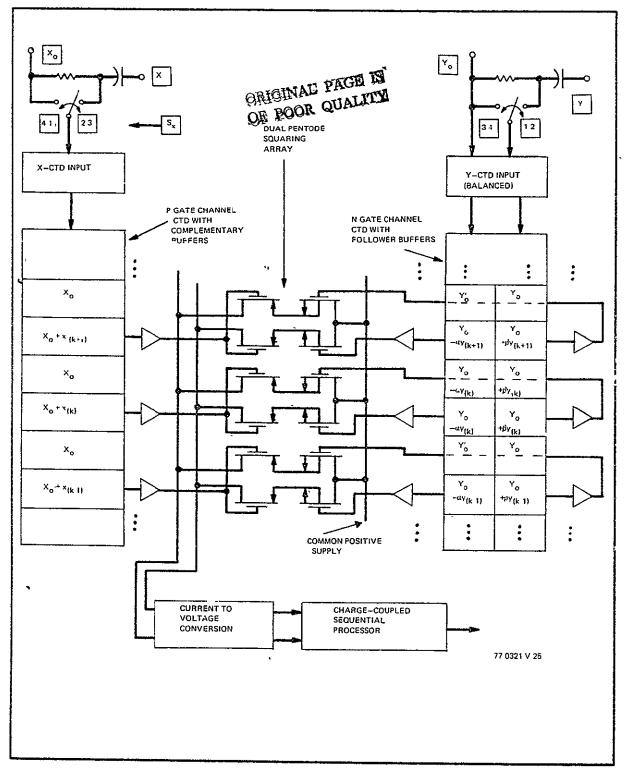

### 2.2.2 Analog Multiplication by Pentode Difference of Squares

This multiplier utilizes the square-law characteristic of an MOS transistor operating in current saturation (pentode) region. The drain current is given as:

$$I_{D} = K(V_{GS} - V_{T})^{2}$$

(13)

If  $V_{GS}$  is made equal to  $(V_0 + A + B)$  for one transistor:

$$I_{D2} = K2 (V_0 + A + B - V_{T2})^2$$

(14)

If related signals are similarly applied to MOSFET pentode gates, we find

$$I_{D1} = K1 (V_{O} + B - V_{T1})^{2}, I_{D3} = K3 (V_{O} + A - V_{T3})^{2}$$

$$I_{D4} = K4 (V_{O} - V_{T4})^{2}$$

(15)

If four perfectly matched devices are used, (or, as we shall see later, if the four voltages are sequenced onto the same MOSFET pentode) so that

$$K1 = K2 = K3 = K4 = and V_{T1} = V_{T2} = V_{T3} = V_{T4}$$

, (16)

the four contributions may be combined exactly as in equation (2-12) to give

$$2K \cdot A \cdot B = I_{D4} - I_{D3} + I_{D2} - I_{D1}$$

(17)

The simplicity of this technique is overwhelmingly attractive from almost every aspect MOS fabrication of a single carrier type is well developed and not complicated. It would be difficult to reduce the transistor count to less than a single MOSFET pentode. MOSFET pentodes with lightly doped bodies can perform squaring efficiently. Ac virtual grounds at both source and drain of the pentode eliminate feedback from the multiplier to the CCD with no additional buffering. And finally, pentode squaring can be achieved over a fairly large range of biases. The principal limitation is implied in equation (14) which shows that the two independent quantities to be multiplied must be ADDED (or subtracted) in order to enable the multiply operation. This means that a sum of products such as

$$z = \sum_{K=1}^{N} A_{K} \cdot B_{K}$$

(18)

may easily be obtained by this technique PROVIDED the sets  $(A_K)$  and  $(B_K)$  are fixed relative to each other since each  $(A_K, B_K)$  are mixed together by addition or subtraction prior to application to the MOSFET pentode gate. Consequently, a single pentode squarer does not allow the relative motion of one data set relative to the other as needed to generate such FUNCTIONS as correlation or convolution.

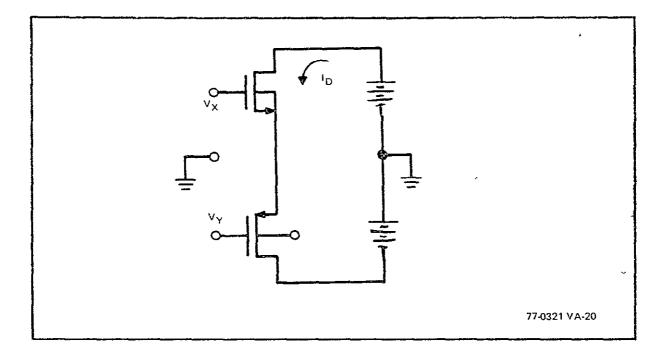

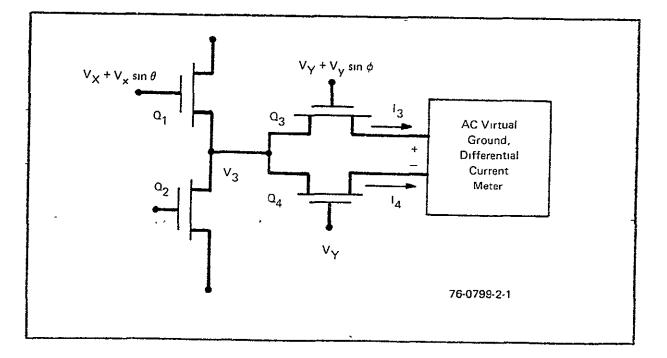

This functional deficiency may be overcome by the use of a second complementary MOSFET pentode in series as shown in Figure 4, and connected to the two independent data delay lines as indicated. The drain current is proportional to the square of the sum of the two gate voltages, provided that the two transistors are in current saturation as follows.

Figure 4 The CMOS Pentode "Difference of Squares" Multiplier

When two signals are applied to the gates of two series CMOS transistors, the current must be the same. If the transistors are in current saturation, the current varies as the square of the gate to source voltage. Thus, for two complementary, but not symmetrical transistors, with a ratio m for their values of K, we can represent and equate the drain currents as

$$K (V_{I} - V_{S})^{2} = K m (V_{S} - V_{II})^{2}$$

(19)

The solution for the common source voltage is

$$V_{\rm S} = \frac{V_{\rm I} + m V_{\rm II}}{1 + m}$$

(20)

and the current is

$$I_{\rm D} = \frac{K m (V_{\rm I} - V_{\rm II})^2}{1 + m}$$

(21)

Note that the drain current remains proportional to the square of input voltage difference, so long as body effect can be ignored.

This last limitation, however, is quite serious. For conventional CMOS, where the doping of the PMOST bodies is about  $1 \times 10^{15}$  while that of the NMOST bodies is near  $4 \times 10^{16}$ , the NMOST body effect completely destroys the desired squaring action. Fortunately, the NMOST body effect can be completely eliminated by connecting each NMOST source to its respective body. The multiplying element of Figure 4 does indeed need a buffered interface from the two independent CCD analog delay lines. Since complementary source-follower action is occurring, this multiplying element can introduce interaction between the two independent data sets unless buffers are used to isolate the gates from the delay line taps. Furthermore, such buffers must be able to provide the two independent ac signals with adequate bias separation to allow for the sum of the two threshold voltages plus the residual PMOST body effect plus the maximum signal excursion.

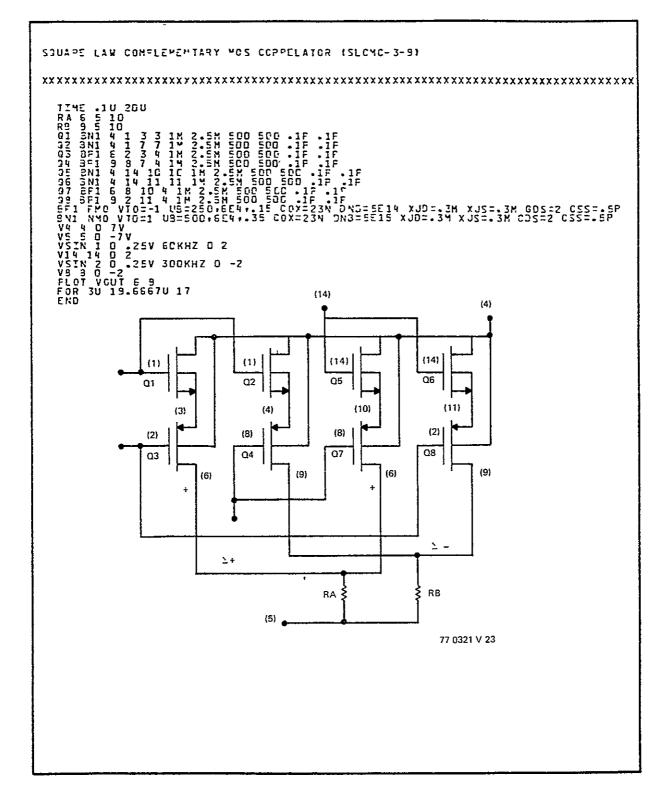

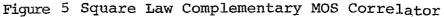

Such buffers are described in more detail in connection with their design for the triode multiplier, but we take the liberty of including some of the results here that are relevant to this CMOS, two-pentode, difference of squares multiplier. With both CCD delay line outputs at basically the same dc bias, an NMOS source follower shifts one signal in the negative direction. This NMOS buffer uses a 7 - to 10 - volt bias and needs only 18  $\mu$ amps to give better than 1-MHz bandwidth for a power consumption of 180 µ watts. A depletionmode PMOS source-follower using a 5-volt supply and drawing  $20\mu$  amps for a power of 100µ watts also gives a 1-MHz bandwidth for the other analog signal buffer. The resultant dc separation between the two signals is increased form zero to 4.5 volts. The circuit of Figure 4 was computer simulated with these results in mind. The circuit model with its operational listing are given in Figure 5, while the resultant dc operating points and the output Fourier analysis are shown in Figure 6. Equations (14) through (17) determined the circuit model with the sequencing of different signals through the series pentode pair (as in equation (16) replaced by the simultaneous or parallel arrangement shown. The spectral analysis of Figure 11 indicates a complete error rejection in excess of 50 dB. Increasing device sizes somewhat to assure a safer bias margin gives extrapolated values like 10µ amps from a 10-volt supply.

Thus, a 1-MHz CTD/CMOS difference of squares multiplying element element with about 50 dB error rejection would need (180 + 100 +  $100)\mu$ watts = 0.38 mwatts, and requires only 6 MOSFETs including buffers.

| SOUARE LAW COMFLEMENTARY HOS CORRELATOR (SLCMC-3-9)<br>TEMF = 300.00                                          |                                                                                                                                                                                                                          |                                                                                                                                                                                         |                                                                                      |                                |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. OF ITER. =<br>NODE VOLTAGES<br>( 0) .0000<br>( 4) 7.0000<br>( 8) -2.0000<br>(14) 2.0000                   | 0 (1)<br>7 (5)                                                                                                                                                                                                           | 2.0000<br>-7.0000<br>-7.0000                                                                                                                                                            | (2)<br>(5)<br>(10)                                                                   | -2.0000<br>-7.0000<br>1.0332   | ( 3)<br>( 7)<br>(11)                                                                                                                                                                                                                                                                                                                                                   | 1.0332<br>1.0332<br>1.0332                                                                                                                                                                                                                                                                                                                                                                  |

| IRAMSISTOR OF. 6<br>NAME TP V<br>91 N<br>02 N<br>03 F<br>04 F<br>05 N<br>05 N<br>05 N<br>05 N<br>05 N<br>28 F | FT<br>GS<br>-9668<br>-3.0332<br>-3.0332<br>-9668<br>-9668<br>-3.0332<br>-3.0332<br>-3.0332                                                                                                                               | -                                                                                                                                                                                       | 5.9668<br>9663<br>8.0332<br>5.9668<br>5.9668<br>5.9668<br>5.9668<br>8.0332<br>8.0332 | 00.<br>-5.91<br>-5.96<br>-5.90 | COO<br>200<br>268<br>269<br>000<br>000                                                                                                                                                                                                                                                                                                                                 | (DS(NA)<br>.C011<br>.0011<br>0011<br>.0011<br>.0011<br>.0011<br>0011<br>0011                                                                                                                                                                                                                                                                                                                |

| RESISTOR CURREN<br>NAME CURRENT<br>RA .00<br>RP .00                                                           |                                                                                                                                                                                                                          | POWER (MW)<br>.0000(<br>.0000(                                                                                                                                                          | 0005                                                                                 |                                |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                             |

| FOURIERANALYSIS                                                                                               | IN 17 HA                                                                                                                                                                                                                 | RMONICS FR                                                                                                                                                                              | :0M .300                                                                             | 3-05 IILL                      | +1967-04                                                                                                                                                                                                                                                                                                                                                               | SECONDS                                                                                                                                                                                                                                                                                                                                                                                     |

| ORDER HARM DSI                                                                                                | NE C                                                                                                                                                                                                                     | ODSINE                                                                                                                                                                                  |                                                                                      | MAGNITUDE                      | REL MAG                                                                                                                                                                                                                                                                                                                                                                | PHASE                                                                                                                                                                                                                                                                                                                                                                                       |

| 1<br>2<br>3<br>4<br>5<br>5<br>7<br>7<br>8<br>9<br>-<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>7            | 0000<br>1848-09<br>1097-09<br>1791-06<br>1914-09<br>2042-10<br>2042-10<br>2042-10<br>2078-09<br>2078-09<br>2774-10<br>2774-10<br>2774-10<br>2167-10<br>1491-10<br>1491-10<br>1491-10<br>1309-10<br>1790-10<br>00 SECONDS | 6530-11<br>5058-09<br>5519-10<br>8765-07<br>29538-09<br>15395-07<br>29538-09<br>129542-109<br>2843-09<br>2843-09<br>21245-09<br>11257-09<br>11257-09<br>11257-09<br>13774-09<br>1354-09 |                                                                                      | .3393-09                       | $\begin{array}{c} 1 \cdot 2127 \\ 100 \cdot 00000 \\ 200 \cdot 2723 \\ 34 \cdot 8978 \\ 334 \cdot 8978 \\ 554 \cdot 578 \\ 37 \cdot 3024 \\ 557 \cdot 7398 \\ 28 \cdot 0959 \\ 51 \cdot 2988 \\ 28 \cdot 0959 \\ 51 \cdot 2986 \\ 21 \cdot 7912 \\ 27 \cdot 2768 \\ 24 \cdot 0645 \\ 25 \cdot 25891 \\ 25 \cdot 3609 \\ 25 \cdot 3609 \\ 25 \cdot 3609 \\ \end{array}$ | $\begin{array}{c} \bullet 0000\\ \bullet 20 \bullet 0694\\ \bullet 7 \bullet 1921\\ \bullet 2 \bullet 499\\ 349 \bullet 271\\ 29 \bullet 3272\\ 59 \bullet 32972\\ 59 \bullet 32972\\ 59 \bullet 32972\\ 59 \bullet 32972\\ 59 \bullet 32947\\ -18 \bullet 57264\\ -27 \bullet 313 \bullet 46735\\ -49 \bullet 64951\\ -99 \bullet 5292\\ -49 \bullet 5292\\ -7 \bullet 5292\\ \end{array}$ |

|                                                                                                               |                                                                                                                                                                                                                          |                                                                                                                                                                                         |                                                                                      |                                |                                                                                                                                                                                                                                                                                                                                                                        | 77-0321 V-24                                                                                                                                                                                                                                                                                                                                                                                |

.

# Figure 6 Results of CMOS Square Law Correlator

Furthermore, the pentode squaring action does not require extremely critical biases or balancing which we will find to be a serious problem with triode multipliers. On-chip, monolithic signal-summation from the drain of pentodes (like current sources) is significantly easier than summing currents in an on-chip voltage -controlled ac-virtual-ground node. The implementation of the needed sequencing and an attractive block diagram to perform the above multiplication will be presented in a later section.

Although the preceding description appears extremely attractive, two potential problem areas have been submerged therein. First, in Figure 5, one notes the doping levels used for the CMOS fabrication: Starting material of  $5\times10^{14}$  cm<sup>-3</sup> with the complementary isolation tubs implanted and driven to give a value of  $5\times10^{15}$  cm<sup>-3</sup>. Such very light doping seems to be the only way to achieve the needed pentode squaring by the NMOST devices because typical levels of  $4\times10^{16}$  cm<sup>-3</sup> give very poor pentode squaring. Secondly is the difficulty of obtaining such devices for laboratory evaluation of the pentode squaring action, since such a CMOS process is a deviation from well developed techniques and would require some adjustment of the fabrication steps.

Consequently, we feel that the CMOS difference of squares approach certainly warrants more investigation than computer modelling; but the likely need for some fabrication process development suggests it is a slightly higher risk approach relative to the triode technique, which does not need fabrication development and thereby provides more rapid chip development albeit at the expense of chip power consumption.

#### 2.2.3 Analog Multiplication by MOSFET Triode

The multiplication function can be performed with MOS transistors operating in the triode region. The drain current  $I_D$  of an MOS transistor can be approximated as

$$I_{\rm D} = \alpha (V_{\rm GS} - V_{\rm T}) V_{\rm DS} + \beta V_{\rm DS}^{2}$$

(22)

where  $V_{\rm GS}$  is the gate to source voltage,  $V_{\rm T}$  is the threshold voltage,  $V_{\rm DS}$  is the drain to source voltage and  $(\alpha,\beta)$  are physical parameters proportional to the width to length ratio and mobility of the channel When the drain to source voltage is small

$$I_{D} \approx \alpha (V_{GS} - V_{T}) V_{DS}$$

<sup>(23)</sup>

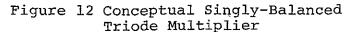

If  $V_{GS}$  and  $V_{DS}$  represent two signals, then the drain current has a term ( $\alpha V_{GS} \cdot V_{DS}$ ) which is proportional to the product of the two signals. If the two signals represented by  $V_{GS}$  and  $V_{DS}$  are substituted in equation (22) or equation (23) there are terms other than the desired multiplied outputs such as  $\alpha V_{DS} \cdot V_T$  or  $\beta/2 (V_{DS})^2$ . These extraneous components of the drain current can be reduced in a balanced multiplier as shown in Figure 12. But the signals may contian dc biases which must eventually be eliminated. One signal is given as  $V_x \sin \theta$  with a dc offset  $V_x$ . The other signal is  $V_y \sin \phi$  with a dc offset  $V_y$ . The signal  $V_x + V_x \sin \theta$  is applied to the common drain of QM and QR via the buffer (QA, QL). The signal  $V_y + V_x \sin \phi$  is applied to the gate of QM, but only the offset voltage  $V_y$  is applied to the gate of QR.

The currents of QM and QR can be obtained by substituting in Eq. (22)  $V_X + V_x \sin \theta$  as  $V_{DS}$  and  $V_Y + V_y \sin \phi$  as  $V_{GS}$  for QM and  $V_y$  as  $V_{GS}$  for QR.

$$I3 = IM = \alpha_{M} \left[ (V_{Y} + V_{Y} \sin \phi - V_{TM}) (V_{X} + V_{X} \sin \theta) \right]$$

$$\beta_{M} \left[ (V_{X} + V_{X} \sin \theta)^{2} \right]$$

$$I4 = IR = \alpha_{D} \left[ (V_{U} - V_{DD}) (V_{D} + V_{D} \sin \theta) \right] + (24)$$

$$\beta_{R} \left[ \left( V_{X} + V_{X} \sin \theta \right)^{2} \right]$$

$$(25)$$

The differential output current  $I_{DO}$  is obtained by subtracting equation (25) from equation (24), assuming identical physical parameters  $(\alpha_M = \alpha_R, \beta_M = \beta_R)$  and a threshold difference  $\Delta V_m = V_{TR} - V_{TM}$ :

$$I_{DO} = IM - IR = \alpha V_X V_Y \sin \theta \sin \phi + \alpha V_X V_Y \sin \phi + (V_X + V_X \sin \theta) (\Delta V_T)$$

(26)

From this last equation, several important conclusions can be drawn. First, we see that any mismatch between the nominally balanced pair of MOSFET triodes such as threshold  $(\Delta V_T)$ , or equivalently their dc bias, contributes to the differential output a term which is directly proportional to the signal applied between drain and source of the triode. Next we see that any dc component of the drain/source voltage,  $V_{\chi}$ , contributes an output term which is directly proportional to the voltage difference between the gates of the two triodes, (QM, QR). These two observations lead us even further into the question:

How can a MOSFET triode pair be operated in practice to minimize the undesired output contributions fed through directly from the input signals in proportion to the extent of unbalance between the two MOSFET's?

This problem area we shall refer to as the rejection of input feedthrough due to a lack of precise or detailed differential balance arising mostly from MOSFET array threshold (and other) nonuniformities, which will be discussed in more detail in section five.

#### 3.0 MULTIPLIER BIAS CONCEPTS

The existing partially-integrated singly-balancedtriode-multiplier correlator chips <sup>2,4,5</sup> have demonstrated the need for elaborate routines for operator-controlled, off-chip optimal biasing because of two distinctly different reasons: for best triode multiplication, the source to gate bias should be much larger than the source to drain bias which sould be as close to zero as practical. Consequently, user appeal is much enhanced by use of circuits and architecture which automatically provides on chip the following: (1) Zero soruce-drain bias and balanced source-gate biases for triode multipliers, (2) adequate offset for triode source-gate bias or the complementary gates for the CMOS pentodes difference of squares multiplier.

#### 3.1 Triode Self-Bias

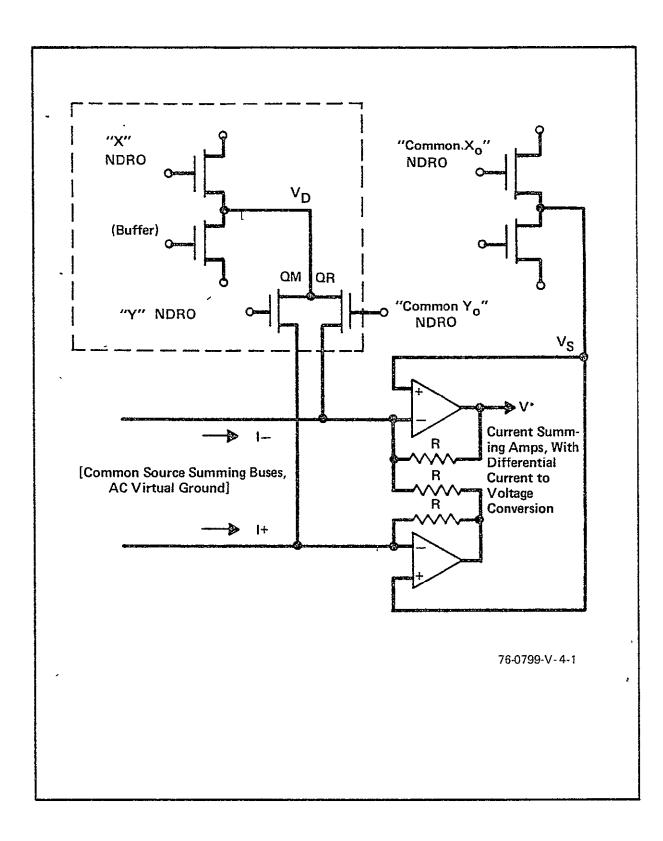

An illustrative example of one way to automatically set the bias on a MOSFET triode multiplier is given in Figure 13. In addition to the CTD stages propagating the actual data, nominally identical reference stages containing only the ZERO signal reference levels (e.g.,  $X_0$ ,  $Y_0$ ) provide two reference levels: (1)  $Y_0$  sets the dc level applied to the gate of the reference triode, QR, to the approximate dc value on the gate of QM; (2)  $X_0$  sets the dc potential  $(V_s)$  of the "virtual ground" current-summing-node to approximate equality with the dc potential applied to the triode drains,  $V_D$ . It is important to note this self-bias concept optimally biases the triode multiplier array; that is, over the array, the average unbalance between individual sources and drains or between gate pairs goes to an acceptably small value. But the concept of Figure 8 by itself,

Figure 8 MOS Analog Triode Multiplier Array Self-Bias Concept does not achieve the detailed differential balance of each multiplier within the array needed to give a high rejection of input feedthrough.

When no provision is made for any self-bias scheme, either like that illustrated in Figure 8 or some alternative, each such partially integrated device<sup>2,4,5</sup> required IN-SITU biasing and fine adjustment. A frequently used technique for such fine adjustment is the spectral analysis approach implied in equation (26); that 1s, two different sine waves are applied to the device and the output spectrum is monitored while the biases are adjusted. The dc value of the virtual ground summing node is set to minimize the feedthrough of the sine wave applied to the gates of the multiplier, thereby yielding the minimum average source/drain bias across the array. For singlybalanced triode multipliers, as illustrated in Figure 7 and 8, where dc is applied to the gate of the reference triode, QR, the dc gatebias for QR is likewise operator adjusted to minimize the feedthrough of the sine wave applied to the triode drains - thus giving the minimum average offset between multiplier gate pairs (inclusive of thresholds), but not necessarily balancing any pair perfectly. This routine for operator optimum biasing must be repeated whenever the conditions for the CTD analog delay line are changed so as to affect the signals from the NDRO buffers, if input feedthrough rejection is to be maintained at its maximum value. Most practical system applications for such analog/analog convolvers would not be able to tolerate such a bias adjustment routine On the other hand, use of such a routine greatly facilitated partially integrated devices 2,4,5 demonstrating the basic principle of CTD/MOSFET-triode correlator action.

#### 3.2 Complementary Buffers

In addition to the preceding feature desired by large systems users, another user attraction is ability to operate both analog delay lines with comparable voltage levels.

To permit such operation, the gate and drain buffer dc output levels can be used to properly bias the MOSFET triode multiplier which needs: small impedance (large conductance) for the drain buffer, minimal bias of drain to source, large bias from gate to (source, drain). We now must add the consideration of low power operation which most strongly affects the drain buffer, since that circuit must be able to supply the triode drain current. Assuming the simplicity of enhancement mode FET's with a CTD NDRO bias of  $V_{\rm C}$ , one quickly finds that the two options become:

Source Follower:

$$g_m = \frac{2I_o}{(V_G/2) - V_T}$$

, Power =  $I_o V_G$

Inverter:  $g_m = \frac{2I'_o}{V_G - V_T}$ , Power  $\geq 2I_o' V_G$  (for unity gain)

Requiring equal  $g_m$  gives us

$$I_{o}' = \frac{V_{G} - V_{T}}{(V_{G}/2) - V_{T}} \cdot I_{o}$$

Thus to give the same output drive, with the same gain, an inverter consumes more than twice as much power as a source follower, thereby dictating the use of a source follower to drive the triode drains.

Buffer configurations to bias the multiplier triode follow directly from the last observation. Source follower stages generally shift the output dc level toward the potential of their body. Extrapolating these generalities to CMOS circuits, we easily

see a signal applied to an NMOS source follower is shifted toward its body voltage and away from the voltage of the common PMOS body. Tabulated below are the preferred buffer configurations to give the needed triode bias:

| Buffer | Singular MOS    | CMOS                             |

|--------|-----------------|----------------------------------|

| Drain  | Source Follower | Source Follower                  |

| Gaté   | Inverter        | Complementary Source<br>Follower |

#### 4.0 DISTORTION ERROR TERMS FOR TRIODE MULTIPLIERS

Since the computation for the product by any REAL, CTDcompatible multiplier is necessarily imperfect, one must describe the various possible sources of errors. A very sensitive technique to study error source is spectral analysis. The application of two distinct sinusoidal signals to an ideal multiplier or correlator gives a well defined output, especially in the spectral or frequency domain. The amplitude of any other frequency components in the output (such as harmonics or higher intermodulation products) is a measure of an associated error source in the multipliers. In this section, we consider three such "harmonic" sources of error.

4.1 "Gate Signal" Harmonics form the Drain Buffer

In Figures 7 and 8, the common (drain) conductance node is driven by a source-follower MOSFET stage with both transistors in the pentode mode (characterized by a squaring relationship between gate-source voltage and drain current). In a singly balanced multipler, the modulated conductance forces the source-follower drain driver to supply a current related to the signals applied to the gate of the modulated conductance. If the transconductance of the source-follower drain driver  $(g_{mB})$  is inadequate compared to the modulated conductance q an erroneous voltage harmonically related to the multiplier gate signal is added to the common (drain) conductance node. This result may be expressed in formulas as follows: Let

$$R_{OB} = 1/g_{mG} = \frac{1}{\mu C_{OX}} \left(\frac{L}{W}\right)_{B} - \frac{1}{(V_{GS} - V_{T})_{B}}$$

(27)

be the output impedance of the drain buffer. Then a voltage  $I_{xy}$  R<sub>OB</sub> would appear at the drain:

$$I_{xy}^{R}OB = \alpha_{m} V_{x}^{V}V_{y}^{R}OB', \text{ where } \alpha_{m} = \mu C_{OX} \left(\frac{W}{L}\right)_{M}.$$

(28)

When multiplied by the gate signal  $V_y$ , an undesired product current is produced:

$$I = \alpha_{\rm m} V_{\rm y} (\alpha_{\rm m} V_{\rm x} V_{\rm y} R_{\rm OB}), \qquad (29)$$

This current should be much less than the desired product current  $\alpha_m V_x V_y$ . Since the distortion described by equation (29) is clearly associated with the signal applied to the gate, even through the drain driver is the cause of the problem, let us define a gate signal distortion rejection ratio,  $\Gamma_{\alpha}$ :

$$\Gamma_{g} = \frac{\alpha_{m} V_{x} V_{y}}{\alpha_{m} V_{y} (\alpha_{m} V_{x} V_{y} R_{OB})} = \frac{1}{\alpha_{m} V_{y} R_{OB}}$$

(30)

or

$$\Gamma_{g} = \frac{(W/L)_{B} \cdot (V_{GS} - V_{T})_{B}}{(W/L)_{m} \cdot V_{Y}}$$

For the purposes of giving examples, let us assume a desired rejection of 40 dB (i.e., 1%). Thus, for example, if one assumes the geometric ratio of MOSFET's in equation (21) to be 50 with a typical source follower bias  $(V_{GS} - V_{T})_{B} \approx 2$  volts, one obtains

$$y_{max} \approx 1$$

volt for  $r_g = 100$ .

4.2. "Drain Signal" Harmonics from the Gate Buffer

The previous section shows one absolute requirement for the buffer used to drive the drain of the triode. The parameters of this particular buffer relative to the multiplier triode, the buffer's bias and the ac signal on the triode gate, mutually determine the gate signal distortion rejection ratio,  $\Gamma_{g}$ , as in equation (30). But, in some cases buffers to drive multiplier gates may serve only to provide reverse isolation to prevent signals within the multiplier from adversely affecting analog delay within the associated CTD. Even though some nondestructive readout schemes circumvent such a problem, the following related difficulty can occur.

Any impedance in series with the gate of the multiplier can develop a voltage by virtue of the feedthrough capacitance from the drain of the multiplier transistor. If the multiplier gate signal is directly derived from the floating gate of a CCD with sensing capacitance,  $C_{FG}$ , the impedance of the driver is the impedance of the capacitance  $C_{FG}$ . The voltage feedthrough is equal to  $V_x C_{gdm} / C_{FG}$ , where  $C_{gdm}$  is the multiplier triode gate to drain overlap capacitance. If the desired signal is  $V_y$ , the rejection ratio limited by gate interaction is simply

$$\frac{V_y C_{FG}}{V_x C_{gdm}} = RR(G)$$

(31)

One way to reduce the adverse effect of the feedthrough from the drain to the gate of the multiplier transistor is to place a buffer between the floating gate of the CCD and the gate of the multiplier. Since the gate buffer output impedance is approximately  $1/(g_m)_{\rm GB}$ , the feedthrough signal from the drain now becomes

$$\frac{1}{\frac{1}{j C_{gcm}} + \frac{1}{(g_m)_{GB}}} \times \frac{1}{(g_m)_{GB}}$$

(32)

Thus the gate buffer changes equation (31) to

$$RR(G) = \frac{V_{y}}{V_{x}} \cdot \left[1 + \frac{(g_{m})_{GB}}{j\omega C_{gdm}}\right]$$

(33)

Typically, for  $C_{gdm} \leq 0.02$  pF and one megahertz, the overlap coupling becomes 126 nanomhos, which may be easily buffered by minimal FET stages of ten to a hundred micromhos.

Consideration of the buffer frequency response gives a further condition related to that of equation (33). If GC is the gate buffer corner frequency, we have

$$f_{GC} \stackrel{\simeq}{=} \frac{\binom{(g_m)}{GB}}{2\pi (C_{GBM} + C_{GP})}$$

(34)

where  $C_{GBM}$  is the multiplier gate to body capacitance and  $C_{GP}$  is the parasitic capacitance on the multiplier gate node. Combining equations (33) and (34) gives

$$RR(G) = \frac{V_y}{V_x} \cdot \left[1 + \frac{C_{GBM} + C_{GP}}{j C_{gdm}} \cdot \frac{f_{GC}}{f}\right] \quad (35)$$

Equation (35) suggests that self-aligned polygate technology could help reduce  $C_{gdm}$  and the transconductance of the gate buffer,  $(g_m)_{GB}$ , must be designed to give the needed rejection at the maximum operating frequency. Failure to observe this precaution will contribute an error term behaving like the square of the drain signal and thus becomes almost indistinguishable from the triode nonlinearity of an overly large drain signal, which is described immediately below.

### 4.3 "Drain Signal" Harmonics from the Multiplying Triode

To evaluate drain signal distortion rejection ratio,  $\Gamma_{d}$ , we require that the MOSFET multiplier always be well into the triode region. Furthermore, we assume  $\Gamma_d$  is directly related to that triode characteristic; or for the worst case:

$$2(V_{GS} - V_{T})_{m} \stackrel{\geq}{=} r_{d} (V_{DS})_{m}$$

(36)

This assumption is very simplistic since the triode drain-gate coupling of equation (33), which causes the same functional distortion, is not incorporated. At this point we must start including quantitatively such array problems as threshold voltage nonuniformity, the average value of which we designate by  $\Delta V_{\rm T}$ . In predicting the worst case for equation (36) we must assume the self-bias technique can result in dc errors comparable to  $\Delta V_{\rm T}$ . Thus, equation (36) may be written

$$\sum_{\substack{2 \ (Y_{o} - V_{T_{m}} - \Delta V_{T} - y_{max}) \ge \Gamma_{d} (\Delta V_{T} + x_{max}) \\ \text{or} } (\Gamma_{d}/2) x_{max} + y_{max} \le (Y_{o} - V_{T_{m}}) - (1 + \Gamma_{d}/2) (\Delta V_{T}).$$

(37)

Consequently, equations (30) and (37) prescribe upper limits on signal levels in terms of array nonuniformities, geometry, biases, and distortion rejection ratios.

At the end of section two, we saw how signals applied to a balanced triode multiplier were fed directly through to the output due to imperfect matching caused by typical array threshold nonuniformities.

5.1 Input Feedthrough Rejection,  $\psi$ , for Balanced Triodes

We must now apply equation (26) to an array of matched triodes using the self-bias technique to give an average source-drain dc value of  $\Delta V_{\eta}$  with the applied ac signals written as (x,y) yielding:

$$I_{D0} \cong \alpha_{m} [xy + y (\Delta V_{T}) + x (\Delta V_{T})]$$

Taking the ratio of the desired signal to the undesired input feedthrough from equation (38) gives the rejection,  $\psi$ , which limits the minimum usable (x,y):

$$(x_{\min}, y_{\min}) \approx \psi \cdot (\Delta V_T).$$

Thus, for a typical  $\Delta V_T \approx 0.1$  volt and a desired input rejection of 40 dB, one finds  $(x_{min}, y_{min}) \approx 10$  volts. This result alerts us to a significant technical problem: each matched triode pair must undergo a detailed balance which self-bias cannot provide if there is to be any hope of achieving acceptable values of input rejection.

5.2 Compensation by Feedback in Floating Gate Reset

In this section, consider nondestructive readout only by means of floating gates. If one could selectively address and adjust the dc bias on each floating gate sensor, then one may postulate the following operation. After loading both CCD shift registers with zero-signal, reference-level-only charge samples, a "unit one" sample is

propagated through one of the delay lines. The output of the correlator to sucha "unit one" is a random pattern which measures the nonuniformities from stage to stage of the other delay line for the combination of both the floating gate sensor and its associated buffer. If now a feedback loop were closed from the correlator output through a selective switch addressing only the stage associated with the "unit one", the feedback amplifier could sense any deviation of the correlator output from a prescribed fixed level and, thence, adjust the bias on that selected floating gate  $t_0$  obtain a null before moving on to the next stage. Theoretically, this could be iterated for both channels so as to completely compensate for threshold nonuniformities everywhere in the array.

In practice, however, several problems appear likely. The published data 2,3 and other estimates indicate that compensation of threshold nonuniformities must fall in the range of 40 to 60 dB to enable even a remote chance of obtaining any usable input dynamic range. Since typical MOS nonuniformities are about 100 millivolts, switched feedback control to better than 1 millivolt is thus called for. But operation of the selective/address feedback switches introduce feedthroughs (even when shielded) due to parasitic and channel coupling capacitance comparable to or larger than a millivolt. Furthermore, such a feedback scheme requires an exclusive "house-keeping" interval; and the compensation stays valid only for short periods of time as thermal leakage fixed patterns destroy the feedback settings very rapidly at MIL Spec temperatures. In contrast, the sequential multiply process

continuously compensates for threshold nonuniformities independent of ambient temperature to better than 50 dB accuracy, as we see in subsequent sections.

5.3 Compensation with the Sequential Multiply Operator

The use of CTD's to provide analog delay with nondestructive readout necessarily requires sensing by means of FET gates with all their attendant array threshold nonuniformities. This alone is a strong argument for a sequential approach whereby a calculation is performed in parts, serially, using the same device elements as well as "zerosignal reference levels for each contributory computation, independent of the functional form of the multiplying element. Traditionally, highly accurate multipliers in analog computing technology used time division multiplexing between the signals and selected references. Equations (11) and (12) suggest the sequential scheme for any ideal multiplier. We now describe the operation in detail and derive some of the extra benefits the technique offers for the triode multiplier.

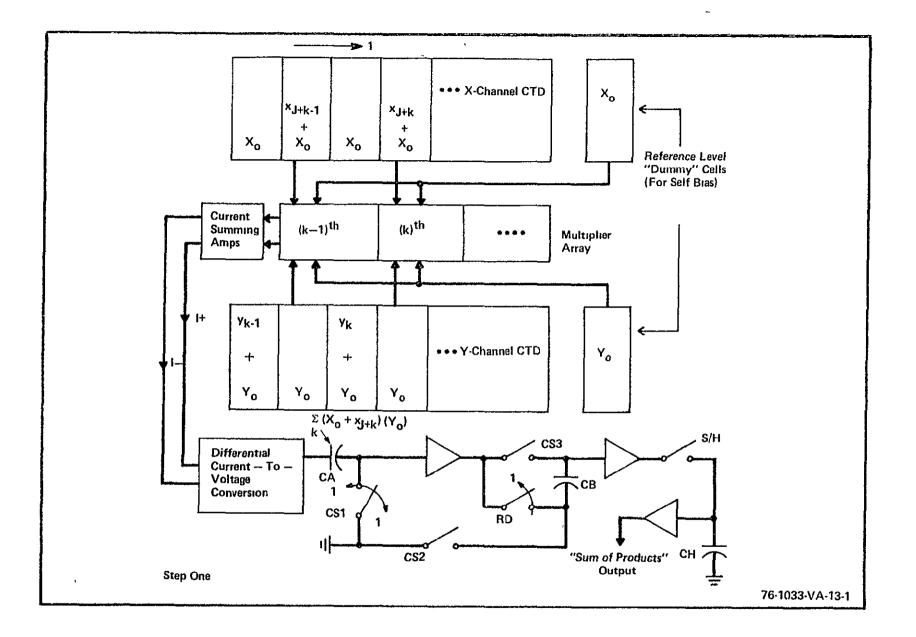

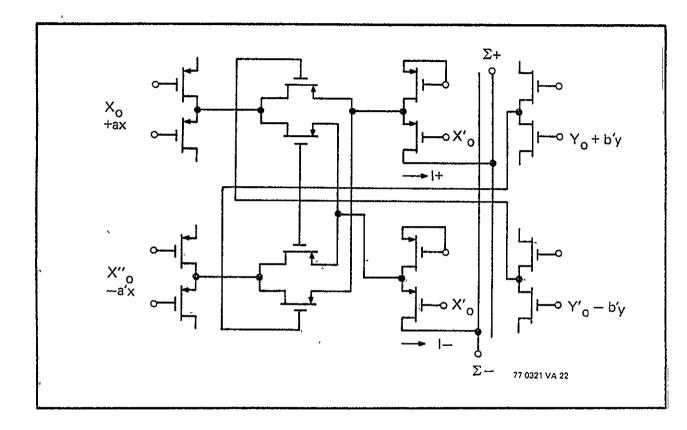

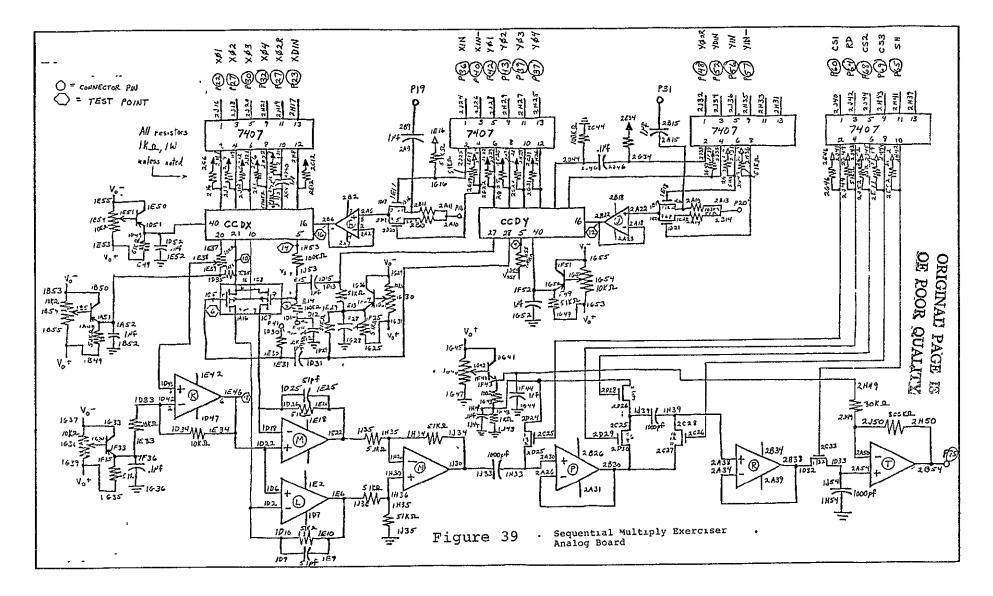

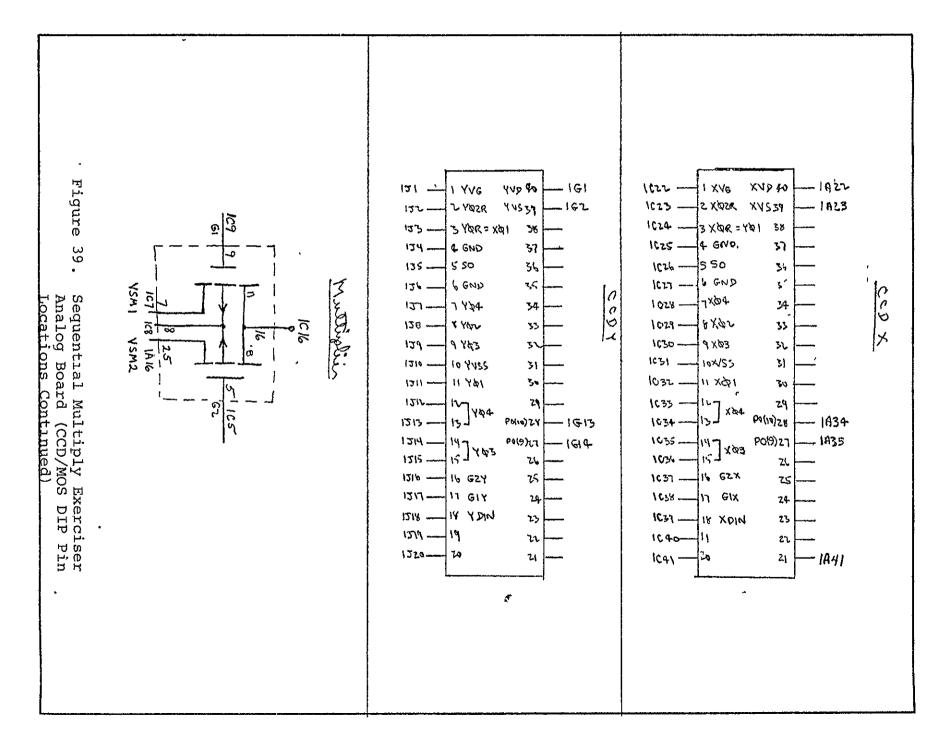

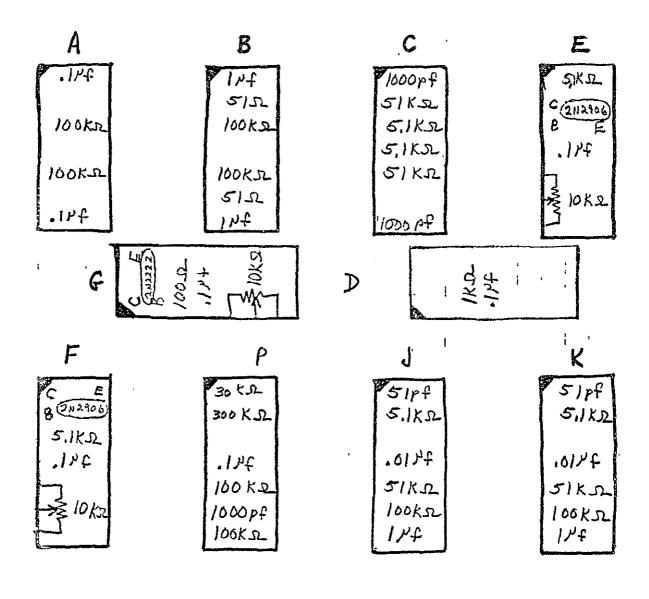

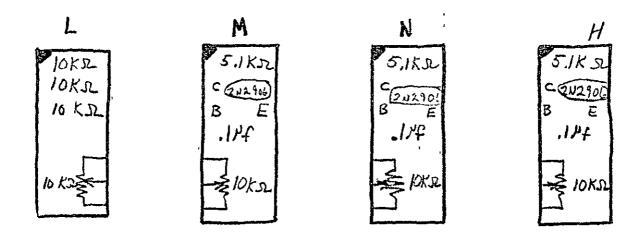

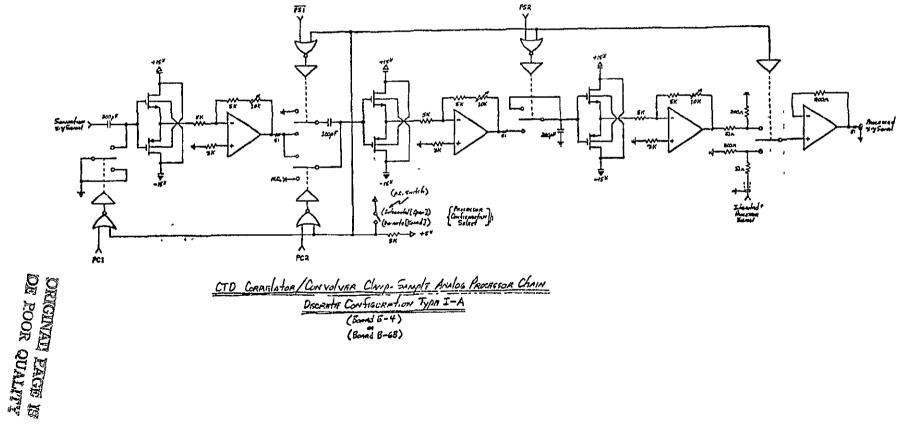

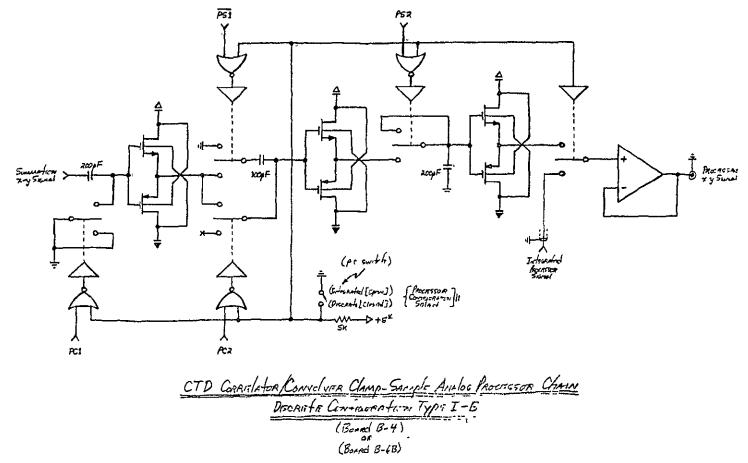

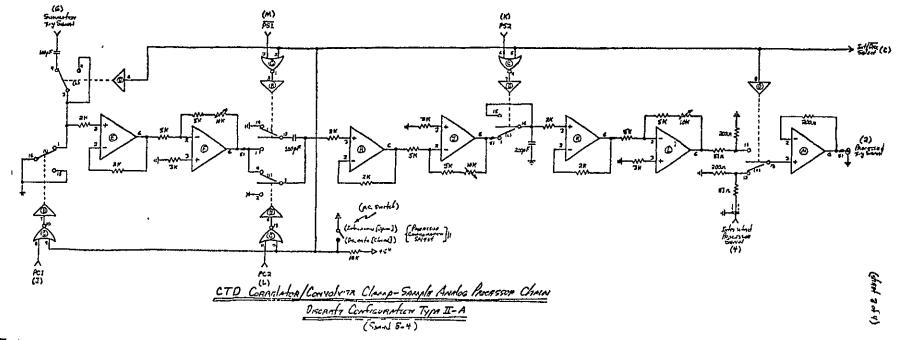

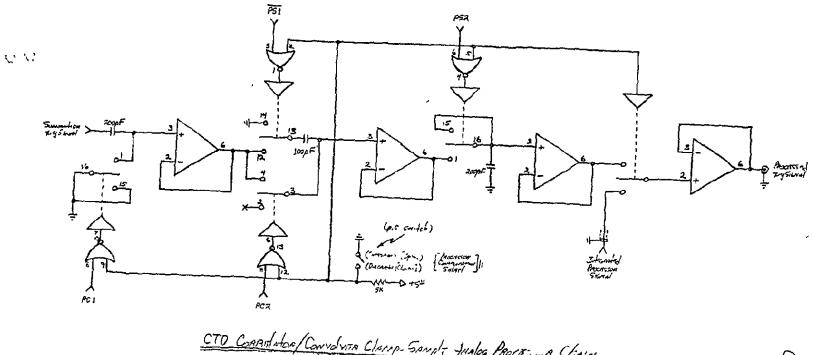

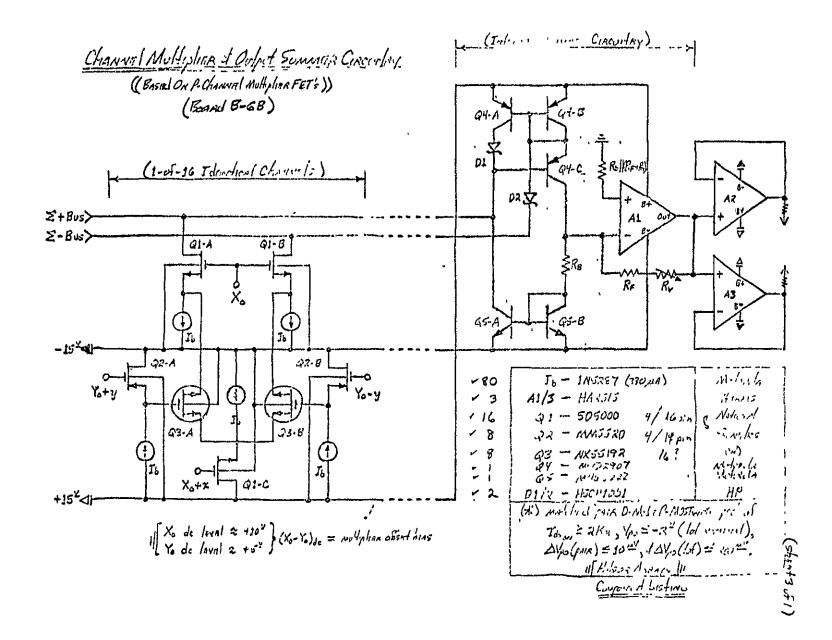

In the sequential multiplying scheme, all the undesired product terms associated with the dc "fat-zero" or threshold voltage deviations are cancelled sequentially in the same multiplying transistor. The discrete/hybrid circuitry for accomplishing this time cancellation is shown in Figures 9 through 12. In both the X and Y CTD channels, samples of signals' ac-zero reference level only  $(X_0, Y_0)$  and referenceplus-signal"  $|(X_0 + x), (Y_0 + y)|$  occupy alternate stages. The product current (I-) due to the common $(Y_0)$  multiplied by X-channel signals is balanced against the product current (I+) due to Y-channel signal multiplied by X-channel signals. All the incremental (I-)'s are fed to a summing amplifier and the (I+)'s to another summing amplifier, to give

# Figure 9 Step One of Sequential Multiply Operation

## FIGURE 10 Step Two of Sequential Multiply Operation

FIGURE 11 Step Three of Sequential Multiply Operation

FIGURE 12 Step Four of Sequential Multiply Operation

the differential output currents,  $\Delta I(t) = \Sigma | (I+)(t) - (I-)(t) |$ .

The signal samples  $x_{(J + K-1)}$ ,  $x_{(J + K)}$ , ... are separated by common ...  $X_0$  and  $Y_0$  respectively. To multiply the quantities  $x_{J + K}$ , and  $y_k$ , four steps are required: The X-channel signals are advanced with respect to the Y-channel signal, as illustrated in figure 9. In the first step, the signal in X-channel CTD is transferred forward by one stage with respect to the Y-channel.

The signal sample  $x_{(J+k)}$  is multiplied by the common  $Y_0$ . The product current is:

$$I + (1) = \sum_{k=1}^{N} \left[ \alpha_{k}^{+} (Y_{0} - V_{T+}^{k}) (x_{J+k} + V_{TX}^{k} - V_{TX}^{k}) + \beta_{k}^{+} (x_{J+k} + V_{TX}^{k} - V_{TX}^{\prime})^{2} \right]$$

(40)

where k indicates the k<sup>th</sup> multiplier,

,

$v_{\rm T+}^{\rm \ k}$  is the equivalent threshold voltage of the  ${\rm k}^{\rm th}$  multiplying MOS transistor.

$v_{\rm TX}^{\ k}$  is the equivalent threshold voltage of the  $k^{\rm th}$  source follower buffer.

$\rm V^{}_{TX}$  is the equivalent threshold voltage of the common/dummy source opening of switch CSl, as in figure 9 .

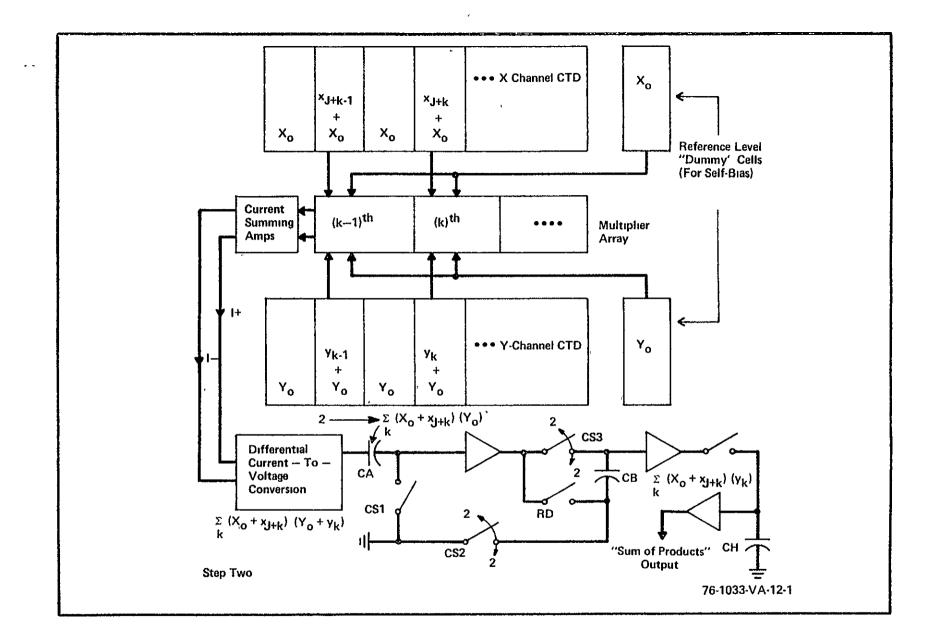

In the second step, the Y-channel is advanced with respect to the X-channel and the signal  $Y_0 + Y_k$  is multiplied by the unchanged  $x_{(J+k)}$  to give the summation current:

I + (2)

$$\sum_{k=1}^{N} \{\alpha_{,}^{+} (Y_{0}^{+} y_{k}^{-} V_{T+}^{k})$$

(41)

$$(x_{J+k}^{-} + V_{TX}^{k} - V_{TX}^{-}) + \beta_{k}^{+} (x_{J+k}^{-} + V_{TX}^{k} - V_{TX}^{-})^{2} \}$$

The switches are now set as in figure 10 such that the previous value associated with equation (2-63) subtracted from the new value equation (41) difference value:

$$[I + (2)] - [I + (1)] = \sum_{k=1}^{N} [\alpha_{k}^{+}(y_{k}) (x_{J+k} + V_{TX}^{k} - V_{TX}')]$$

(42)

clamped directionally onto capacitor CB by the operation of the switches CS2 and CS3. Note that equation (42) depends on only a single multiplying transistor at each multiplier location and is basically identical to equation (26) for the balanced multiplier.

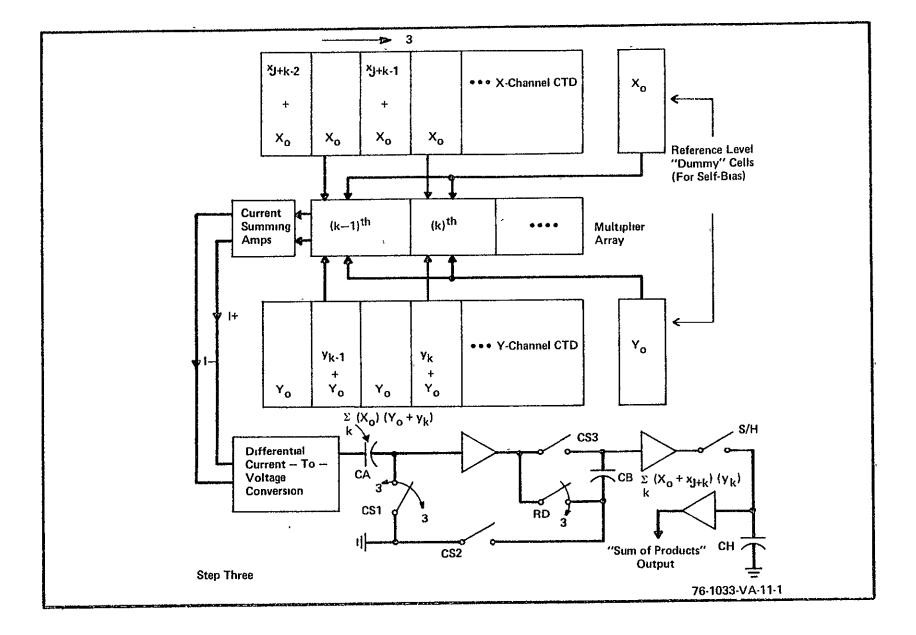

In the third step shown in figure 11 the X-channel signals are advanced with respect to the Y-channel signal. The y-channel signal  $Y_0 + y_k$  is multiplied by the common  $X_0$ . The summation current,

$$I + (3) = \sum_{k=1}^{N} \left[ \alpha_{k}^{+} (Y_{0} + y_{k} - V_{T+}^{k}) (V_{TX}^{-k} - V_{TX}) + \beta_{k}^{+} (V_{TX}^{-k} - V_{TX}')^{2} \right]$$

(43)

gives a third output which is clamped onto CA by means of CSl as in the first step. Prior to the fourth step, read switch RD is closed as in Figure 11, so that value stored on CB adds to the output of the preceding amplifier.

In the final step as illustrated in Figure 12, the Y-channel signal may be either advanced, if a completely new vector dot-product is desired, or receded with respect to the X-channel, if additional dot-products with the same replica vector are desired, as for correlation or convolution functions. The common  $X_0$  and common  $Y_0$  are multiplied. The summation current is

$$I + (4) = \sum_{k=1}^{N} \left[ a_{k}^{+} (Y_{0} - V_{T+}^{k}) (V_{TX}^{k} - V_{TX}^{-}) + \beta_{k}^{+} (V_{TX}^{k} = V_{TX}^{-1})^{2} \right]$$

(44)

As in the second step, the value stored on capacitor CA from step 3 subtracts from the fourth partial output, to give a second difference which is added to the first difference (as stored on capacitor CB) for a final four-quadrant sum of products output.

$$V_{out} (J) = R \Delta I = [\Delta I(4) - \Delta I(3) + \Delta I(2) - \Delta I(1)]$$

$$= R \sum_{k=1}^{N} a_{k}^{+} x_{J+k} y_{k}$$

(45)

NOTE THAT ONLY THE DESIRED SIGNAL PRODUCT APPEARS AT THE OUTPUT, WITH MULTIPLIER "PURE DRAIN-SOURCE NONLINEARITIES" ALSO CANCELLED. THUS, IN THIS MANNER, THE SEQUENTIAL PROCESSOR ENHANCES THE DRAIN HARMONIC DISTORTION REJECTION,  $\Gamma_d$ , FOR THE SINGLY-BALANCED TRIODE.

#### 5.4 A Balanced-Input Monolithic Sequential Processor

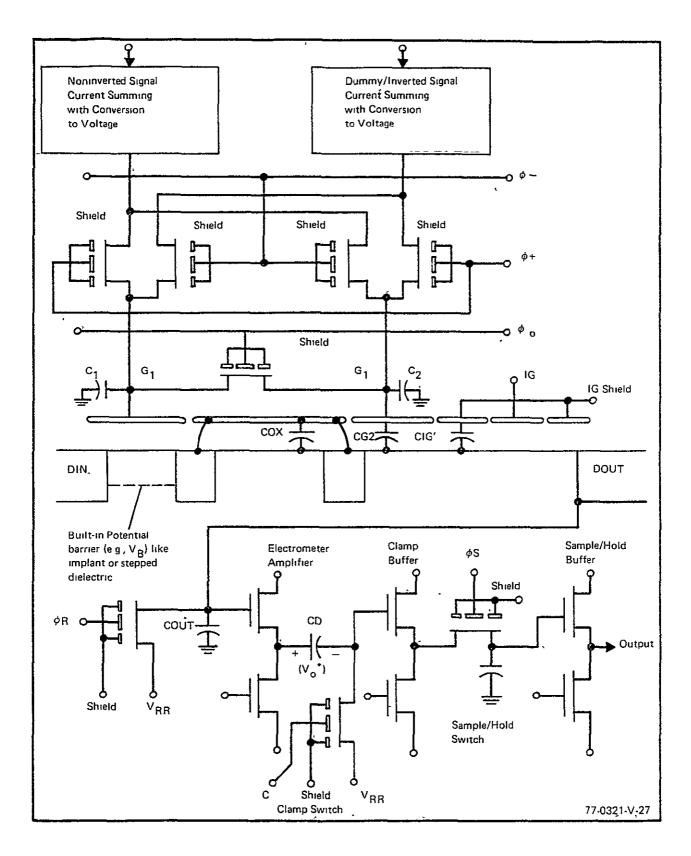

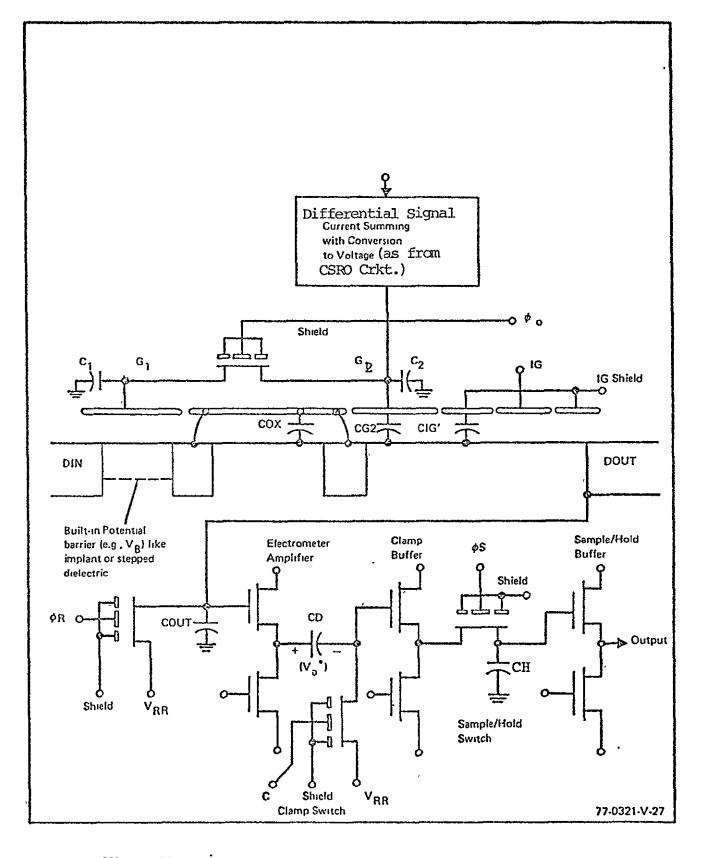

A monolithic implementation of the sequential processor described above is illustrated in Figure 13. The inherent differential action of the "fill/spill" input technique is used to subtract the applied balanced signals. A built-in bias-charge potential barrier,  $V_{\rm B}$ , is used to guarantee that balanced signals of either sign can be processed.

Thus, when charge is metered and read while switch  $\beta_0$  is activated, the quantity of charge is given by  $Q^* = (CIN) \cdot (V_B)$  where the effective input capacitance is given by CIN = COX + CG2 + CIG'. The resultant potential increment on the output collecting diode, DOUT, and hence, the output capacitance for that node, COUT, is given by  $V_{out} = \frac{Q^*}{C_{out}} = \left(\frac{CIN}{COUT}\right) \cdot \left(V_B\right)$ , with an associated device gain of  $G = \frac{CIN}{COUT}$ If multiple charge packets (such as N) are metered and collected on the

Figure 13 A Monolithic Charge-Coupled Sequential Processor

output capacitor (to give the effect of algebraic addition) before that node is reset to make the next measurement, the overall voltage excursion is limited by the bias applied to the output circuit:  $V_{RR}^{=}$ reset reference voltage so that:  $N \cdot (V) < V_{RR}$ , or  $V_{RR}^{>N \cdot G \cdot V_{B}}$ . This formula establishes a limiting relationship between the device gain, built-in barrier, algebraic addition multiplicity, and the reference reset bias voltage.

If the current-summing-to-voltage converters have an effective offset or threshold difference designated by  $\Delta$ , while the resultant output voltages are indicated by (K+), the sequence of charge packets metered on CIN and collected on COUT after the reset operation becomes:

a) Reset the output capacitor, then activate  $\emptyset_0$ , disable  $\emptyset$  + and  $\emptyset$ -, repeat the metering operation four times to give  $Q_0 = 4Q^*$ . The output of the electrometer at that instant  $(V_0^*)$  is stored on the "difference" capacitor, CD, by momentarily activating the clamp switch via the  $\emptyset$ C pulse, in the direction indicated in figure 18, which effectively subtracts  $V_0^*$  from all subsequent signals output by the electrometer.

b) Reset the output capacitor, then activate  $\emptyset$ +, disable  $\emptyset$ -and  $\emptyset_{O}$ , to meter  $Q_1 = Q^* + CIN (\Delta + (A+) - (A-), onto COUT.$

c) Activate Ø-, disable Ø+ and Ø<sub>0</sub>, to add  $Q_2 = Q^* + CIN$  ( (B-) - $\Delta$ -(B+) ), with  $Q_1$  on COUT.

d) Activate Ø+, disable Ø - and Ø<sub>0</sub>, to add Q<sub>3</sub> = Q\* + CIN ( $\Delta$  + (C+)-(C-), with (Q<sub>1</sub> + Q<sub>2</sub>) on COUT.

e) Activate  $\emptyset$ -, disable  $\emptyset$ + and  $\emptyset$ ; to add  $Q_4 = Q^* CIN (D-) - \Delta - (D+)$ , with  $(Q_1 + Q_2 + Q_3)$  on COUT.

With all four charge packets added algebraically on the output capacitor:

$$\sum_{i=1}^{4} Q_{K} = 4Q^{*} + CIN \cdot [\delta A - \delta B + \delta C - \delta D], \text{ where } \delta K = (K^{+}) - (K^{-}).$$

$$(46)$$

But the voltage  $V_0^*$ , derived from the electrometer output at a time when  $Q_0 = 4Q^*$  had been added on its gate, previously stored on CD cancels the contribution from  $4Q_0^*$ , leaving only the increment

$$V_{\text{SIG}} = \frac{\text{CIN}}{\text{COUT}} [\delta A - \delta B + \delta C - \delta D],$$

applied to the gate of the clamp buffer. At this instant, the Sample/ Hold switch is momentarily activated to update the final output stage. In this manner, a fully reconstructed step-wise output waveform, including dc restoration, is generated. The clamp or dc restoration part of the circuit is optional and may be omitted if ac coupling is permitted.

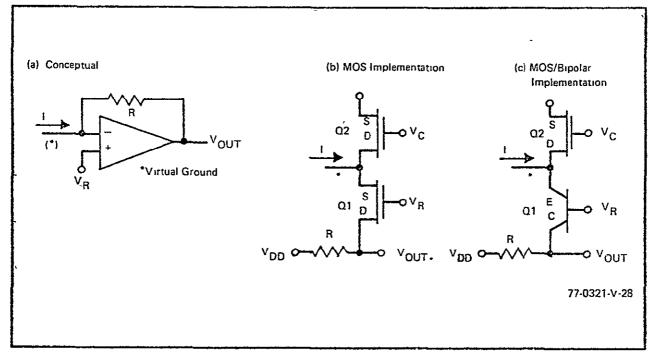

### 5.4 A MONOLITHIC READOUT WITH SELF-BIAS AND DIFFERENTIAL CURRENT-TO-VOLTAGE CONVERSION

The actual multiplying elements need a readout scheme which provides DC-balanced virtual ground input nodes, the DC bias of which is controlled by a voltage applied to further node. One conceptual and two simplistic forms of a single-sided or unbalanced version of such a scheme are illustrated in Figure 14. Since most analog multiplying devices consist of counterbalancing elements, yielding currents which

### Figure 14. Current-to-Voltage Converters

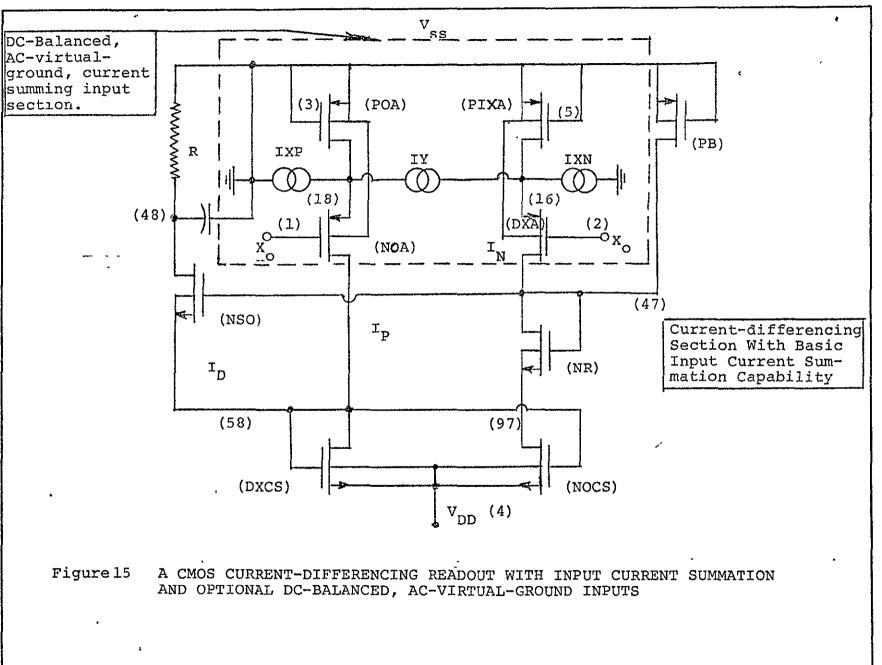

must be subtracted, an attractive technique gives the differential current directly from high impedance current sources that can be added in parallel (without interaction) to feed a high resistance for conversion of small differential signal currents into large signal voltages. Use of such a desirable large resistor in the circuits of Figures 14-band 14-c is severely limited, however, because the full bias current needed to increase the  $g_m$  of the virtual-ground stage must flow through that resistor. Consequently, paired circuits, each like that of Figure 14-b mated with the differential monolithic sequential processor, give smaller differential signal voltages due to the smaller allowed resistor; thereby, yielding a reduced output signal-to noise ratio (S/N) or requiring a larger area output sequential processor to maintain the same S/N achieved with a higher resistance.

A possible CMOS circuit to difference the two currents (cancelling the DC bias components) so as to enable higher resistances to be used is illustrated in Figure 15. The circuit consists partly of a DC balanced pair of virtual-ground stages similar to those of Figure19-b. The remainder is the basic current differencing part of the circuit and closely resembles a modified current-mirror circuit. That is, the currents through transistors (DXCS) and (NOCS), which are nominally matched, try to establish themselves at very near equality

$$I_{D} + I_{P} = I_{N+} \Delta I \tag{47}$$

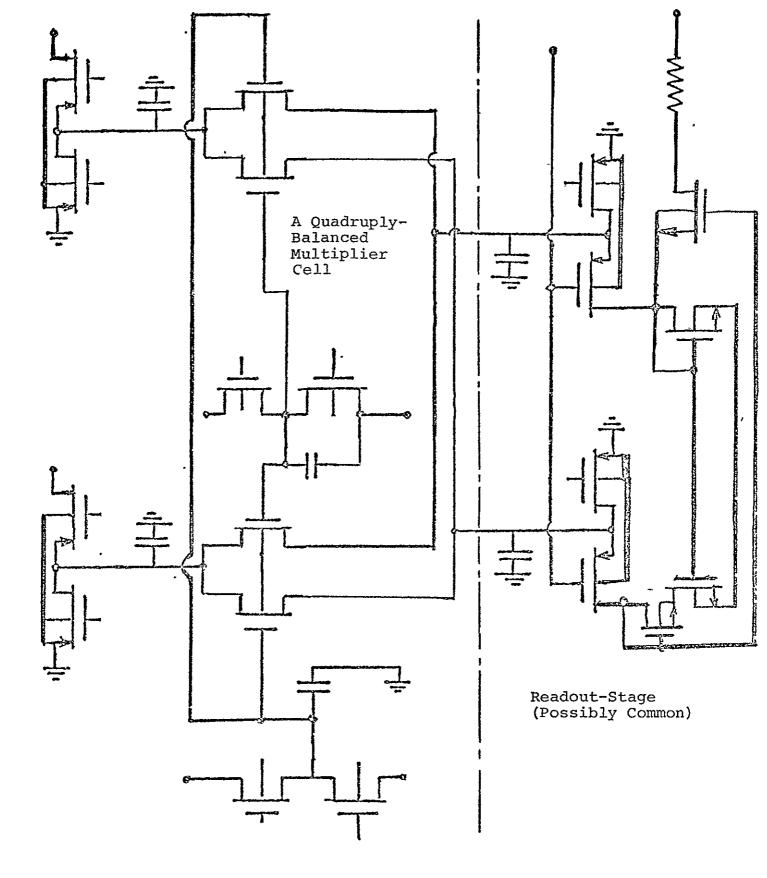

where  $(I_p, I_N)$  are the signal (IXP, IXN, IY), plus bias currents for the two counterbalancing legs of the multiplier as fed into their respective AC virtual ground nodes, AI is a fixed incremental offset current to enable readout of bipolar current differentials, and  $I_D$ is the differential readout current. When a complete quadruply balanced triode multiplier cell replaces the test sources, (IXP, IXN, IY), the circuit of Figure 16 results.

In Figure 16 the transistors to the left of the dot-dash line are those belonging to whatever multiplier cell is selected and needs to be duplicated for each such multiplier needed within the correlator chip. The remaining elements form part of the readout mechanism and may be scaled according to the number of multipliers involved, for incorporation as a single common readout stage. Some advantages, however, may be obtained if the part of the readout stage which provides the DC-balanced AC-virtual-ground node-pair, and which is enclosed by a dashed box in Figure 15 is distributed along with each individual multiplier rather than lumped into a common readout stage: The resultant closer proximity of each DC-controlled AC-virtual ground node to its associated counterpart, which includes one of the input signals, may give statistically better matching across each multiplier

Figure 16 : A CMOS CORRELATOR CELL WITH SELF-BIAS AND DIFFERENTIAL CURRENT-TO-VOLTAGE READOUT

as well as some averaging across the array and a more uniform distribution of heat generation around the chip.

We may now briefly describe the circuit operation, assuming the bias currents for the AC-virtual ground stages are given by (IB±):

$$I_P = (IB+) + (IXP) - (IY)$$

$I_N = (IB-) + (IXN) + (IY)$  (48)

Combining the last few equations gives:

$$I_{D} = (\Delta I) + 2(IY) + \{(IXN) - (IXP)\} + \{(IB-) - (IB+)\}$$

(49)

For MOS triode-type multipliers, (IXP, IXN) are the drain-source currents when a common signal is applied jointly to both drains, so that any AC component of such a common drain signal cancels to the extent that the matched pair of MOSFET triodes are truly identical. The last equation further tells us that the fixed bias current, AI, must be comparable to the worst case of unbalance for the virtual-ground stage biases, PLUS the unbalance between the nominally matched multiplier MOSFETS, plus the peak signal excursion. Consequently, one may ascribe a common-mode rejection ratio(CMRR) to this circuit:

$$CMRR = \frac{IX]_{IN}}{IX]_{OUT}}$$

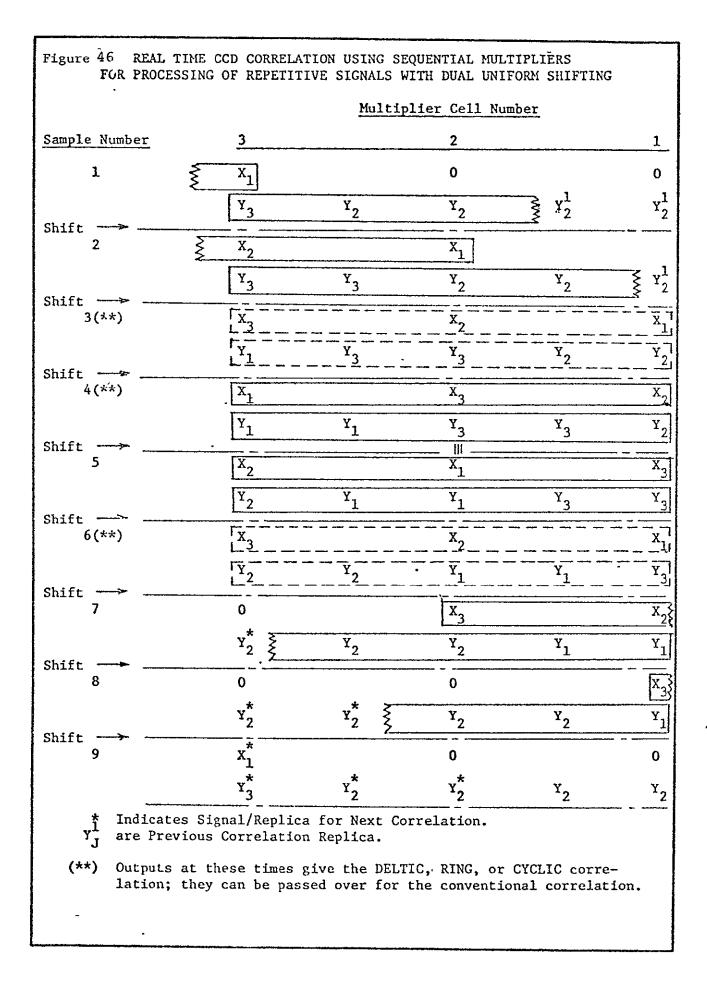

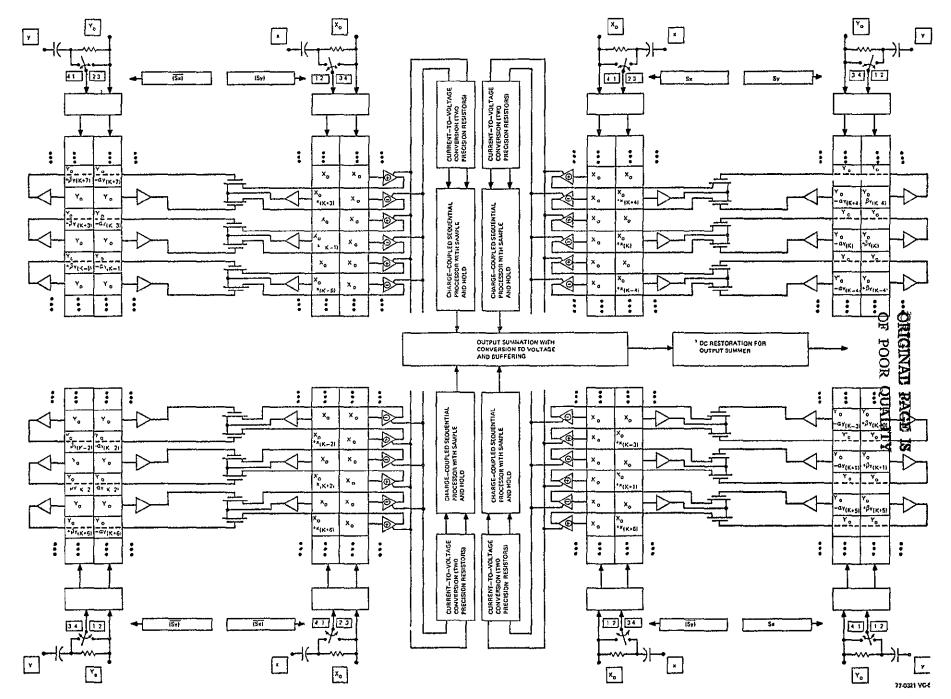

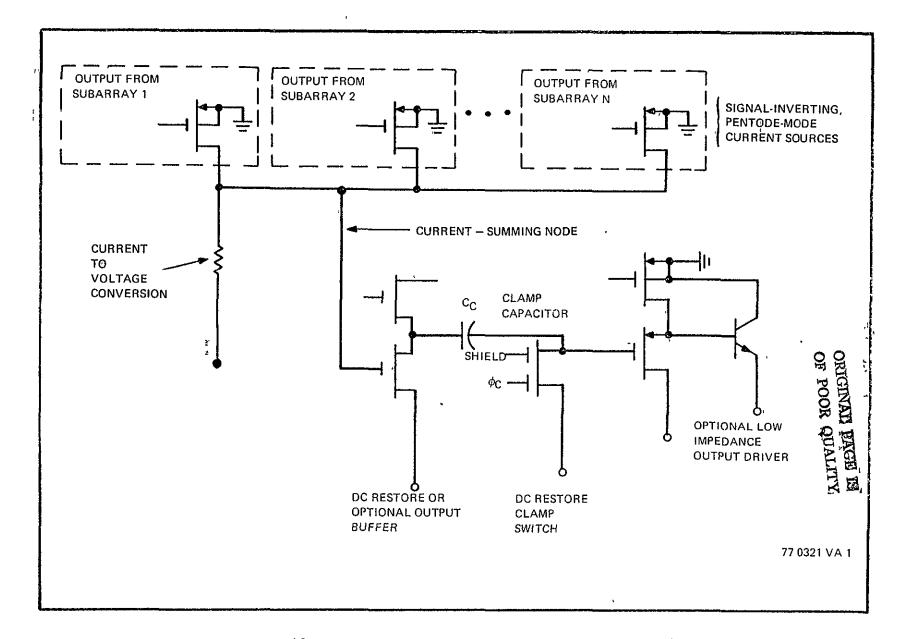

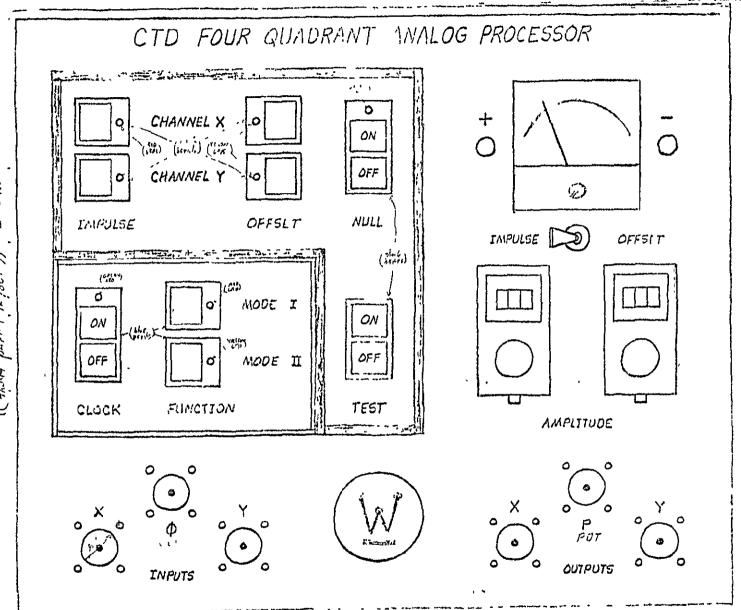

(50)