### On Development, Feasibility, and Limits of Highly Efficient CPU and GPU Programs in Several Fields

Fast Parallel SIMDized GPU-accelerated Reed-Solomon Encoding, Heterogeneous Linpack Benchmark, and Event Reconstruction for the ALICE Experiment

Dissertation

for attaining the PhD degree

of Natural Sciences

submitted to the Faculty for Computer Science and Mathematics

of the Johann Wolfgang Goethe University

in Frankfurt am Main

by

David Rohr

from Mannheim

Frankfurt 2013

(D 30)

accepted by the Faculty for Computer Science and Mathematics of the Johann Wolfgang Goethe University as a dissertation.

Dean:

Prof. Dr. Thorsten Theobald

Expert assessor:

Prof. Dr. Volker Lindenstruth Prof. Dr. Udo Kebschull

Date of the disputation:

23.6.2014

### Abstract

#### On Development, Feasibility, and Limits of Highly Efficient CPU and GPU Programs in Several Fields

Fast Parallel SIMDized GPU-accelerated Reed-Solomon Encoding, Heterogeneous Linpack Benchmark, and Event Reconstruction for the ALICE Experiment

With processor clock speeds having stagnated, parallel computing architectures like GPUs have achieved a breakthrough in recent years. Despite of their shortcomings concerning efficient execution of serial tasks, their sheer parallel processing power makes them predestined for parallel applications while the simple construction of their cores makes them unbeatably power efficient. Unfortunately, old programs cannot profit through simple recompilation, and adaptation usually requires rethinking and modifying algorithms. Modern clusters are often designed heterogeneously and offer different processors for different applications. In order not to waste the available compute power, highly efficient programs are mandatory. This thesis is about the development of fast algorithms and their implementations on modern CPUs and GPUs, about the maximum achievable efficiency with respect to peak performance and to power consumption respectively, and about feasibility and limits of programs for CPUs, GPUs, and heterogeneous systems. Three totally different applications from distinct fields, which were developed in the course of this thesis, are presented.

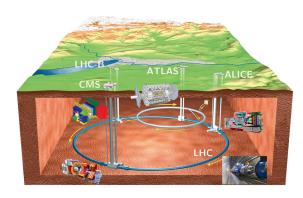

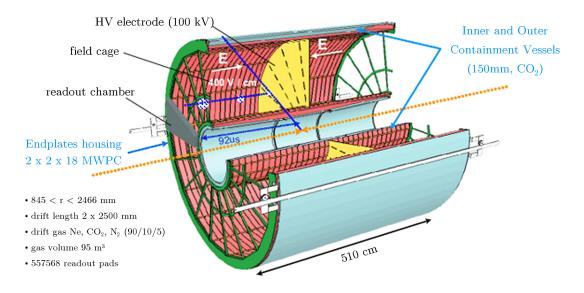

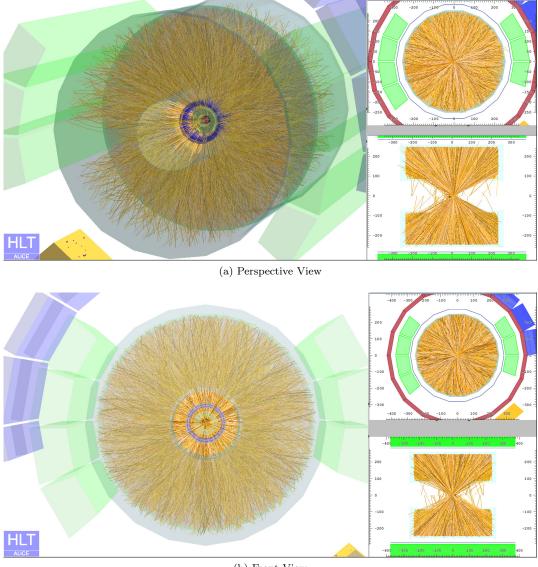

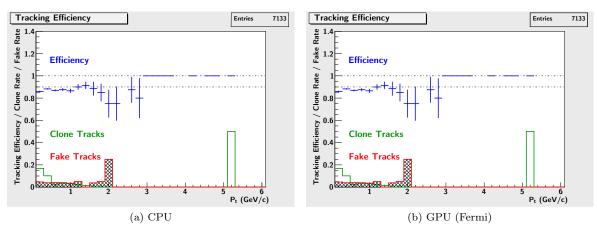

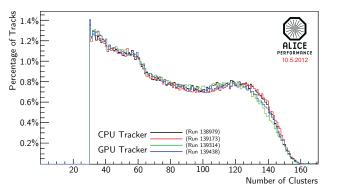

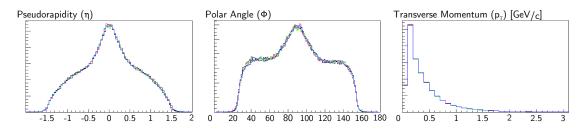

The ALICE experiment at the LHC studies heavy-ion collisions at high rates of several hundred Hz, while every collision produces thousands of particles, whose trajectories must be reconstructed. For this purpose, ALICE HLT TPC track reconstruction and track merging have been adapted for GPUs outperforming the fastest available CPUs by about a factor three. Since the beginning of 2012, the tracker has been running in nonstop operation on 64 nodes of the ALICE HLT providing full real-time track reconstruction.

The Linpack benchmark employs matrix multiplication (DGEMM) to solve a dense system of linear equations and is the standard tool for ranking compute clusters. Heterogeneous multi-GPU-enabled versions of DGEMM and Linpack have been developed supporting CAL, CUDA, and OpenCL as backend. An elaborate lookahead algorithm hides the serial CPU-bound tasks of Linpack behind DGEMM execution on the GPU reaching the highest efficiency on GPU-accelerated clusters. Employing this implementation, the LOEWE-CSC cluster ranked place 22 in the November 2010 Top500 list of the fastest supercomputers, and the Sanam cluster achieved the second place in the November 2012 Green500 list of the most power efficient supercomputers.

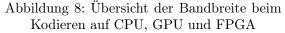

Failure erasure coding enables failure tolerant data storage and is an absolute necessity for present-day computer infrastructure. The mathematical theory behind the codes involves matrixcomputations in finite fields, which are not natively supported by modern processors and hence computationally very expensive. This thesis presents a novel scheme for fast encoding matrix generation and demonstrates fast implementations for the encoding itself, which use exclusively either integer or logical vector instructions. Depending on certain parameters, they always hit different hard limits of the hardware: either the maximum attainable memory bandwidth, or the peak instruction throughput, or the PCI Express bandwidth limit when GPUs or FPGAs are employed.

The thesis demonstrates that in most cases GPU implementations can be as efficient as their CPU counterparts with respect to the available peak performance. With respect to costs and power consumption, they are much more efficient. For this purpose, complex tasks must be split in serial as well as parallel parts such that multithreaded pipelines and asynchronous DMA transfers can hide CPU bound tasks ensuring continuous GPU kernel execution. Few cases are identified where this is not possible due to PCI Express limitations or not reasonable because practical GPU languages are missing.

# **Table of Contents**

| Ta | able of Contents                                                                                           | 1          |

|----|------------------------------------------------------------------------------------------------------------|------------|

| Ι  | Introduction                                                                                               | 9          |

| 1  | Motivation & Outline                                                                                       | 10         |

| 2  | CPUs                                                                                                       | 12         |

|    | 2.1 Intel                                                                                                  | <br>12     |

|    | 2.1.1 Nehalem                                                                                              | <br>12     |

|    | 2.1.2 Westmere & Sandy Bridge                                                                              | <br>13     |

|    | 2.2 AMD                                                                                                    | <br>13     |

|    | 2.2.1 Magny-Cours                                                                                          | <br>13     |

|    | 2.2.2 Interlagos $\ldots$ | <br>14     |

|    | 2.3 Summary                                                                                                | <br>14     |

| 3  | GPUs                                                                                                       | 15         |

|    | 3.1 General GPU Architecture                                                                               | <br>15     |

| 4  | Benchmark Proceeding & Statistics                                                                          | 18         |

|    | 4.1 Conventions & Statistics                                                                               | <br>18     |

|    | 4.2 Benchmark Conditions for NVIDIA                                                                        | <br>18     |

|    | 4.3 Benchmark Conditions for AMD                                                                           | <br>19     |

| II | Event Reconstruction for the ALICE Experiment                                                              | 20         |

| 5  | Introduction                                                                                               | <b>2</b> 1 |

|    | 5.1 The ALICE Detector of the LHC Experiment                                                               | <br>21     |

|    | 5.2 The High Level Trigger                                                                                 | <br>22     |

|    | 5.3 The ALICE HLT TPC Tracker                                                                              | <br>22     |

|    | 5.3.1 Geometry                                                                                             | <br>23     |

|    | 5.3.2 Creating Track Seeds                                                                                 | <br>23     |

|   |     | 5.3.3   | Fitting Tracks with the Kalman Filter                                                                                          |

|---|-----|---------|--------------------------------------------------------------------------------------------------------------------------------|

|   |     | 5.3.4   | Initialization & Output                                                                                                        |

| 6 | TPO | C Slice | Tracking on GPU 25                                                                                                             |

|   | 6.1 | The A   | ALICE HLT TPC GPU Tracker                                                                                                      |

|   | 6.2 | Portir  | ng the Tracker to the Fermi Architecture $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 26$                          |

|   |     | 6.2.1   | Fermi Support & Compiler Bugs                                                                                                  |

|   |     | 6.2.2   | First Comparison                                                                                                               |

|   |     | 6.2.3   | Tuning Parameters    28                                                                                                        |

|   |     | 6.2.4   | Integration in the HLT Framework                                                                                               |

|   | 6.3 | Onlin   | e Tracking during the November 2010 Heavy Ion Run                                                                              |

|   |     | 6.3.1   | Evaluation & Quality Assurance for the Tracking Results                                                                        |

|   |     |         | 6.3.1.1 Verification of Simulated Data                                                                                         |

|   |     |         | 6.3.1.2 Verification of Physics Runs                                                                                           |

|   | 6.4 | Furth   | er Optimizations & the Heavy Ion Runs in 2011 and 2012 $\ldots \ldots 35$                                                      |

|   |     | 6.4.1   | Improving the Cluster Assignment                                                                                               |

|   |     |         | 6.4.1.1 Incorporating the $\chi^2$ Value $\ldots \ldots \ldots \ldots \ldots \ldots 35$                                        |

|   |     |         | 6.4.1.2 Track Order                                                                                                            |

|   |     |         | 6.4.1.3 Binary Comparison                                                                                                      |

|   |     | 6.4.2   | Using the GTX580                                                                                                               |

|   |     |         | 6.4.2.1 Variable Block Size                                                                                                    |

|   |     | 6.4.3   | Multi-Threading the CPU Parts                                                                                                  |

|   |     | 6.4.4   | Improved Scheduling                                                                                                            |

|   |     |         | 6.4.4.1 Improved Scheduling Performance                                                                                        |

|   |     | 6.4.5   | Combined GPU/CPU Tracking 41                                                                                                   |

|   |     | 6.4.6   | Final Performance Analysis    42                                                                                               |

|   |     | 6.4.7   | The 2011 Heavy Ion & 2012 Proton-Lead Runs                                                                                     |

|   |     | 6.4.8   | GPU Tracking on non-CUDA Hardware                                                                                              |

| 7 | TPO | C Trac  | k Merging on GPU 44                                                                                                            |

|   | 7.1 | Revie   | w of the Situation $\ldots \ldots 44$             |

|   | 7.2 | GPU-    | based Track Fit                                                                                                                |

| 8 | Glo | bal Tra | acking across Slice Borders 46                                                                                                 |

|   | 8.1 | Limit   | s of the Slice Tracking Approach                                                                                               |

|   | 8.2 | Imple   | mentation $\ldots \ldots 46$ |

|   | 8.3 | Resul   | ts                                                                                                                             |

|   |     |         |                                                                                                                                |

9 Comparison to Offline & Conclusions

| III   | Hetero    | geneous High Performance Linpack Benchmark      | 54 |

|-------|-----------|-------------------------------------------------|----|

| 10 In | troducti  | on to Linpack, DGEMM, and LOEWE-CSC             | 55 |

| 10    | .1 Heter  | ogeneous Compute Clusters                       | 55 |

| 10    | 0.2 The I | OEWE-CSC Compute-Cluster                        | 55 |

| 10    | .3 Linpa  | ck                                              | 56 |

|       | 10.3.1    | High Performance Linpack                        | 57 |

|       | 10.3.2    | Double Precision General Matrix Multiplication  | 58 |

| 11 A  | n Optim   | ized HPL Variant for the LOEWE-CSC              | 59 |

| 11    | .1 Targe  | t Architectures                                 | 59 |

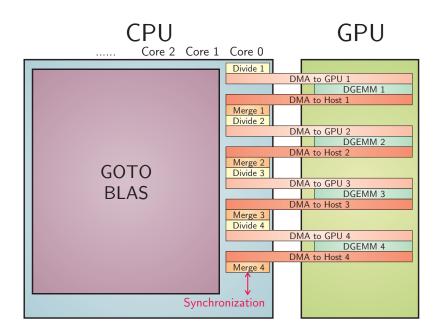

| 11    | .2 CALI   | ОДЕММ                                           | 59 |

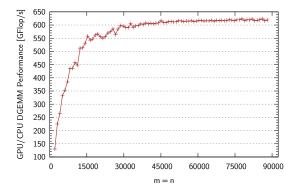

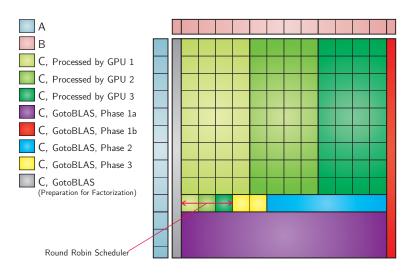

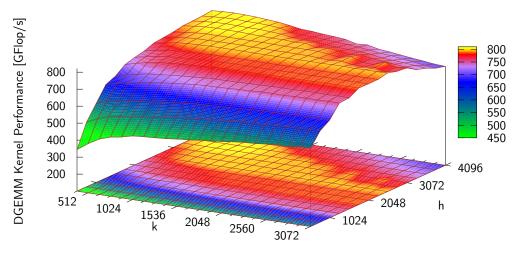

|       | 11.2.1    | GPU-based DGEMM                                 | 59 |

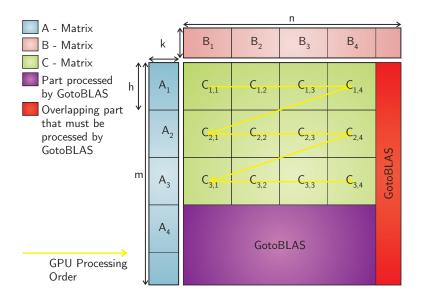

|       | 11.2.2    | Implementation Details                          | 61 |

|       | 11.2.3    | Combined GPU/CPU DGEMM                          | 61 |

|       |           | 11.2.3.1 CPU Affinity                           | 62 |

|       | 11.2.4    | DGEMM Optimizations                             | 63 |

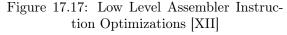

|       |           | 11.2.4.1 Kernel Optimization                    | 63 |

|       |           | 11.2.4.2 Data Buffer Format                     | 69 |

|       |           | 11.2.4.3 Exemplary $8 \times 8$ Kernel          | 70 |

|       |           | 11.2.4.4 Scheduling & GPU/CPU Performance Ratio | 72 |

|       |           | 11.2.4.5 Second & Third Phase                   | 74 |

|       |           | 11.2.4.6 Transfer Optimizations                 | 75 |

|       | 11.2.5    | Vectorization & Patched AMD Driver              | 78 |

|       |           | 11.2.5.1 Miscellaneous Optimizations            | 79 |

|       | 11.2.6    | Summary & Results                               | 81 |

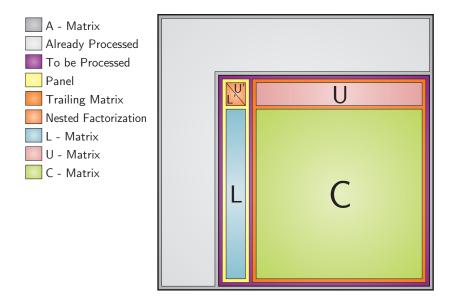

| 11    | .3 GPU-   | based HPL                                       | 81 |

|       | 11.3.1    | Integrating CALDGEMM                            | 81 |

|       | 11.3.2    | Optimizing HPL                                  | 82 |

|       |           | 11.3.2.1 Alignment                              | 82 |

|       | 11.3.3    | Multi-Node HPL                                  | 83 |

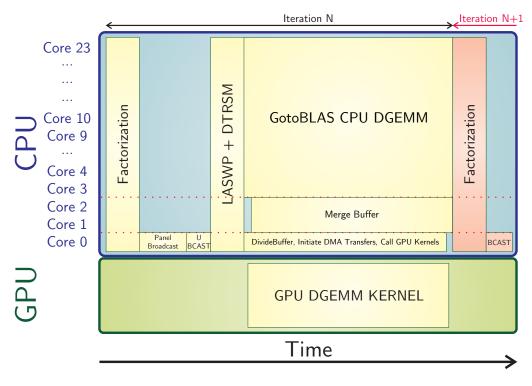

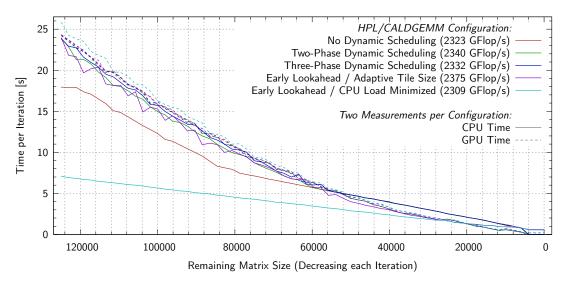

|       | 11.3.4    | Lookahead                                       | 84 |

|       |           | 11.3.4.1 Lookahead 1                            | 85 |

|       |           | 11.3.4.2 Lookahead 2                            | 88 |

|       |           | 11.3.4.3 Performance Analysis                   | 91 |

|       | 11.3.5    | Miscellaneous                                   | 94 |

|       |           | 11.3.5.1 Rescheduling Workload                  | 94 |

|       |           | 11.3.5.2 MPI Threading Support                  | 94 |

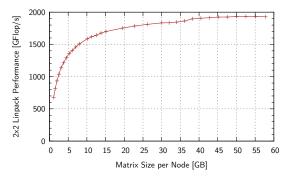

| 11    | .4 DGEI   | MM & Linpack Performance                        | 95 |

| 11.5   | Tortu  | re Tests                                               |

|--------|--------|--------------------------------------------------------|

| 12 Opt | imizat | ions for other architectures 97                        |

| 12.1   | CPU-   | only HPL                                               |

| 12.2   | Real-7 | Fime Operating Systems    97                           |

|        | 12.2.1 | The Chaos Operating System                             |

|        | 12.2.2 | SUSE Linux Enterprise Server with Real-Time Extensions |

| 12.3   | CPU    | Scaling                                                |

| 12.4   | Heter  | ogeneous Nodes                                         |

|        | 12.4.1 | Heterogeneous Solver for Triangular Matrices           |

|        | 12.4.2 | Heterogeneous HPL Performance                          |

| 12.5   | Zero-0 | Copy DMA Transfer on Intel CPUs                        |

|        | 12.5.1 | Kernel DMA Performance                                 |

|        | 12.5.2 | Alternative DMA Transfer Approach                      |

|        | 12.5.3 | DMA Performance Comparison                             |

| 12.6   | Dual-  | GPU & Multi-GPU                                        |

|        | 12.6.1 | Dual-GPU DGEMM Implementation                          |

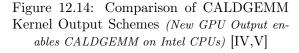

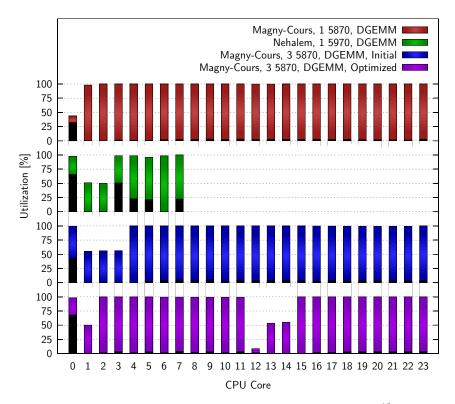

|        |        | 12.6.1.1 CPU & GPU Utilization                         |

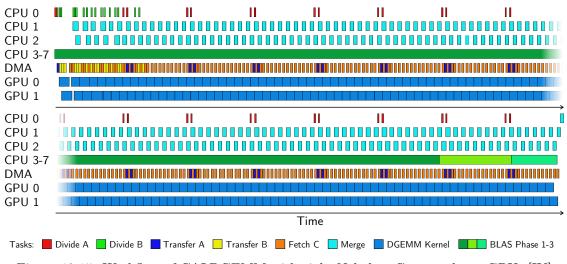

|        |        | 12.6.1.2 Performance                                   |

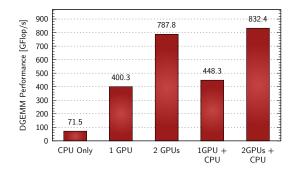

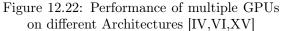

|        | 12.6.2 | Scaling to Multi-GPU DGEMM                             |

|        |        | 12.6.2.1 Memory & PCI Express Throughput               |

|        |        | 12.6.2.2 CPU Utilization                               |

|        |        | 12.6.2.3 Other Multi-GPU Improvements                  |

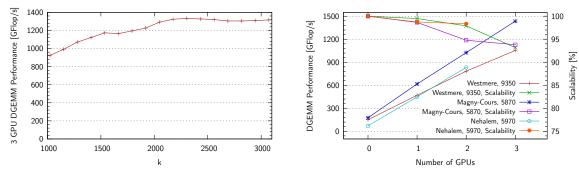

|        | 12.6.3 | Multi-GPU DGEMM Results                                |

|        | 12.6.4 | Multi-GPU HPL                                          |

|        |        | 12.6.4.1 GPU-based Factorization                       |

|        |        | 12.6.4.2 GotoBLAS Tuning                               |

|        |        | 12.6.4.3 Enabling Lookahead                            |

| 12.7   | Energ  | y Efficiency                                           |

|        |        | Multi-GPU Considerations                               |

|        | 12.7.2 | First Results                                          |

|        | 12.7.3 | Improvements by more efficient Hardware                |

| 12.8   | AMD    | 6000 Series GPU                                        |

|        | 12.8.1 | Temperature & Power                                    |

|        | 12.8.2 | DMA Performance                                        |

|        | 12.8.3 | Workaround for the DMA Issue                           |

|        |        | 12.8.3.1 Improving GPU to Host Transfer                |

|        |        | 12.8.3.2 Improving Host to GPU Transfer                |

|        | 12.8.4 | 6000 Series Multi-GPU DGEMM & HPL Performance          |

| 12.9 CALDGEMM for Interlagos/Sandy Bridge and without GotoBLAS $\ldots \ldots \ldots 125$                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.10 Performance Limits & Exceeding Peak Performance                                                                                                           |

| 12.11 Systems with a slow CPU                                                                                                                                   |

| 12.12 Overview of CALDGEMM DMA Paths                                                                                                                            |

| 12.13 Single Precision General Matrix Multiplication                                                                                                            |

|                                                                                                                                                                 |

| 13 CALDGEMM Support for Arbitrary GPU Frameworks13213 CALDGEMM Support for Arbitrary GPU Frameworks132                                                          |

| 13.1 Motivation                                                                                                                                                 |

| 13.2 A DMA Framework with better Scalability                                                                                                                    |

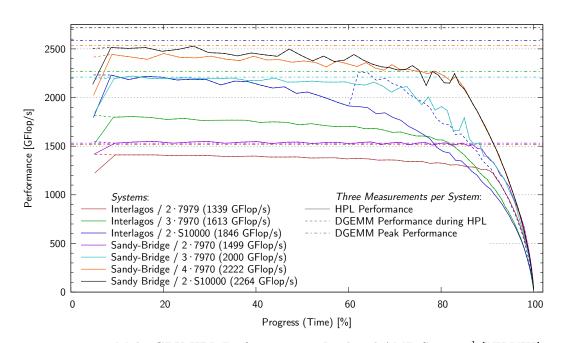

| 14 The Sanam Cluster & the Lattice-QCD Cluster at GSI 137                                                                                                       |

| 14.1 AMD 7000 Series (Tahiti)                                                                                                                                   |

| 14.2 Putting the Pieces together                                                                                                                                |

| 14.2.1 Preliminary Improvements                                                                                                                                 |

| 14.2.2 Early Lookahead                                                                                                                                          |

| 14.2.3 Choosing a Platform                                                                                                                                      |

| 14.2.4 Multi-Node, Fine-Tuning, and Results                                                                                                                     |

| 14.2.4.1 Grouped DMA Thread Mode                                                                                                                                |

| 14.2.4.2 Lookahead 2b                                                                                                                                           |

| 14.2.4.3 Power Efficiency                                                                                                                                       |

| 14.2.5 The November 2012 Top500 & Green500 Lists $\ldots \ldots \ldots \ldots \ldots 146$                                                                       |

| 15 Summary & Perspective for the Future 148                                                                                                                     |

| 15.1 Summary                                                                                                                                                    |

| 15.2 Perspective for the Future                                                                                                                                 |

|                                                                                                                                                                 |

| IV Optimized High Performance Redundant Data Storage 150                                                                                                        |

| 16 Theory 151                                                                                                                                                   |

| 16.1 Coding Theory                                                                                                                                              |

| 16.2 Reed-Solomon Code $\dots \dots \dots$                      |

| 16.3 Integer Calculations & Codes on finite Rings $\ldots \ldots 154$                     |

| 16.3.1 Deriving Codes from Algebraic Number Fields                                                                                                              |

| 16.3.1.1 Integrality $\ldots \ldots 154$                                    |

| 16.3.1.2 An MDS-Code on Residue Class Rings $\dots \dots \dots$ |

| 16.3.1.3 Codes on $\mathbb{Z}/p^b\mathbb{Z}$ (Integral Codes)                                                                                                   |

| 16.3.1.4 The general Case $\ldots \ldots 157$                                      |

| 16.3.2 Deriving Codes from Finite Field MDS-Codes                                                                                                               |

| 16.3.3 Summary                                                                                                                                                  |

| 16.4   | Cauchy-Reed-Solomon Code                                                                                                                  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

|        | 16.4.1 <i>XOR</i> -only Codes                                                                                                             |

|        | 16.4.2 Add-only Codes $\dots \dots \dots$ |

| 16.5   | Variants                                                                                                                                  |

|        | 16.5.1 Encoding by Matrix-Matrix Multiplication                                                                                           |

|        | 16.5.2 Strassen Matrix-Matrix Multiplication                                                                                              |

|        | 16.5.3 Parallel Codes                                                                                                                     |

| 16.6   | Code Overview                                                                                                                             |

| 16.7   | Computational Complexity                                                                                                                  |

| 16.8   | Lower Bound for $l$                                                                                                                       |

| 16.9   | Partial Update-Codes (Differential Codes)                                                                                                 |

| 17 Imp | blementation 166                                                                                                                          |

| 17.1   | Metrics                                                                                                                                   |

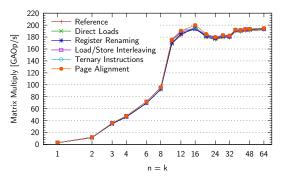

| 17.2   | Matrix Multiplication based Codes                                                                                                         |

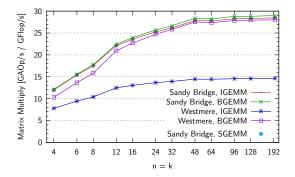

|        | 17.2.1 IGEMM                                                                                                                              |

|        | 17.2.2 BGEMM                                                                                                                              |

| 17.3   | Automorphic Assembly Codes                                                                                                                |

|        | 17.3.1 <i>XOR</i> -only Encoding                                                                                                          |

|        | 17.3.2 Blocking & Cache Usage                                                                                                             |

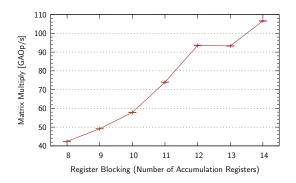

|        | 17.3.2.1 Register Blocking                                                                                                                |

|        | 17.3.2.2 L1 Blocking                                                                                                                      |

|        | 17.3.2.3 L1 Instruction Cache Blocking                                                                                                    |

|        | 17.3.2.4 L2 Blocking                                                                                                                      |

|        | 17.3.2.5 L1 Blocking, Second View                                                                                                         |

|        | 17.3.3 Code Optimizations                                                                                                                 |

|        | 17.3.3.1 Prefetching                                                                                                                      |

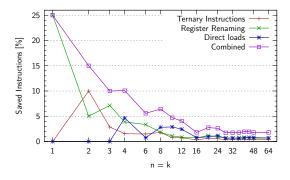

|        | 17.3.3.2 Ternary Instructions                                                                                                             |

|        | 17.3.3.3 Register Selection $\ldots \ldots 173$              |

|        | 17.3.4 Reducing Computational Complexity                                                                                                  |

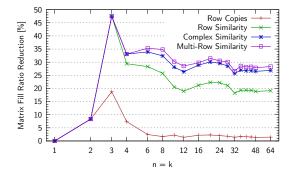

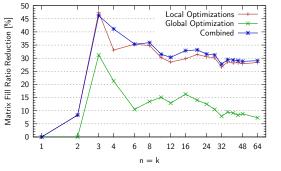

|        | 17.3.4.1 Local Matrix Optimizations                                                                                                       |

|        | 17.3.4.2 Global Matrix Optimizations                                                                                                      |

|        | 17.3.4.3 Eliminating Instructions                                                                                                         |

|        | 17.3.5 Improved Matrix Size (Smaller $l$ Dimension)                                                                                       |

|        | 17.3.6 Large Matrices                                                                                                                     |

|        | 17.3.6.1 Assembling Large Codes                                                                                                           |

|        | 17.3.6.2 L2 Instruction Blocking                                                                                                          |

|        | 17.3.7 Exploiting the Strassen Algorithm                                                                                                  |

|        | 17.3.8 Small Matrices                                                                                                                     |

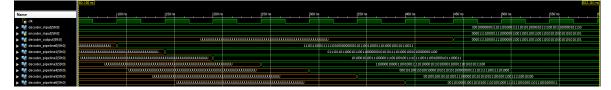

|                                                                                                                 | 17.3.9 Complex Code Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 181                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                 | 17.3.10 Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 183                                                                                                                                                                                 |

|                                                                                                                 | 17.3.11 Variants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 184                                                                                                                                                                                 |

|                                                                                                                 | 17.3.11.1 Add-only Encoding $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 184                                                                                                                                                                                 |

|                                                                                                                 | 17.3.11.2 A 256-bit $XOR$ -only Code with AVX $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 184                                                                                                                                                                                 |

|                                                                                                                 | 17.3.12 Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 185                                                                                                                                                                                 |

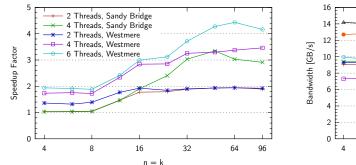

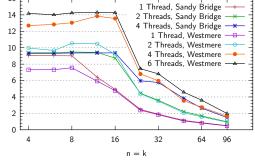

| 17.4                                                                                                            | Multi-Threading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 186                                                                                                                                                                                 |

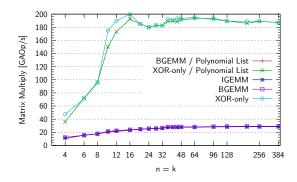

| 17.5                                                                                                            | Update-Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 187                                                                                                                                                                                 |

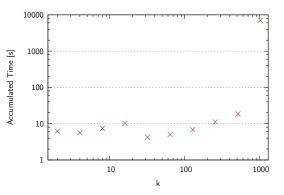

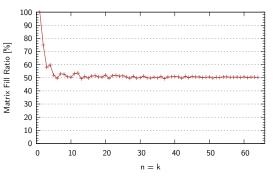

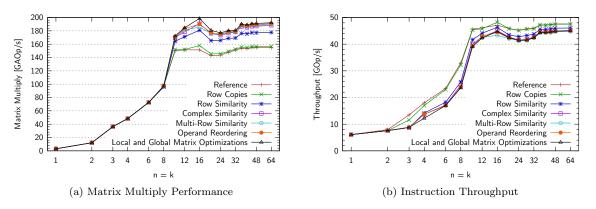

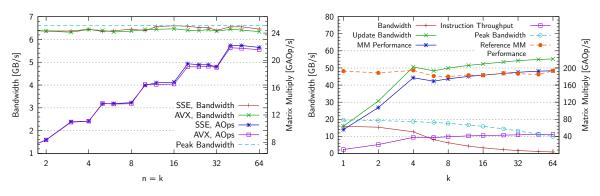

| 17.6                                                                                                            | Dependency on $k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 187                                                                                                                                                                                 |

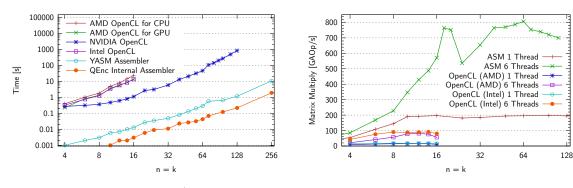

| 18 Enc                                                                                                          | oding with GPU & FPGA Accelerators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 188                                                                                                                                                                                 |

| 18.1                                                                                                            | Matrix Multiplication based Codes for GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 188                                                                                                                                                                                 |

| 18.2                                                                                                            | XOR-only Encoding with OpenCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 188                                                                                                                                                                                 |

| 18.3                                                                                                            | An FPGA Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 189                                                                                                                                                                                 |

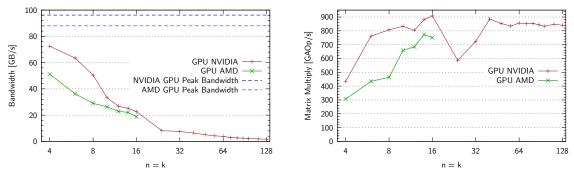

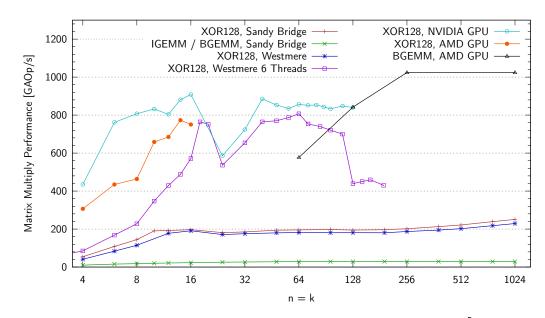

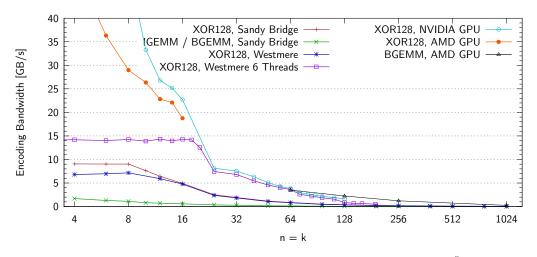

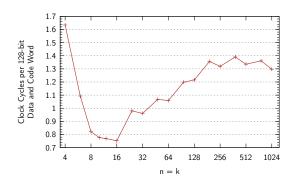

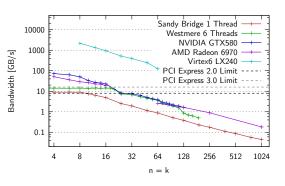

| 18.4                                                                                                            | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 190                                                                                                                                                                                 |

| 19 Res                                                                                                          | ults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 191                                                                                                                                                                                 |

| 19.1                                                                                                            | Achieved Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 191                                                                                                                                                                                 |

| 19.2                                                                                                            | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 194                                                                                                                                                                                 |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |

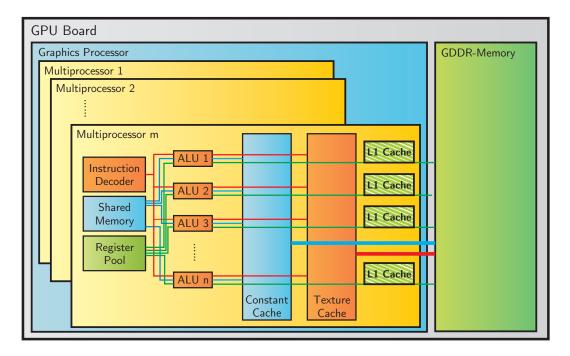

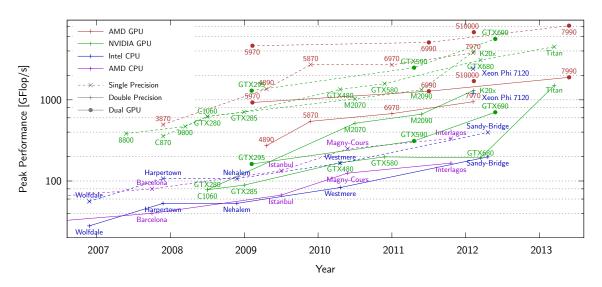

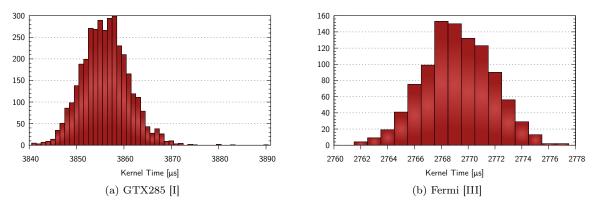

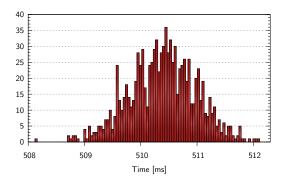

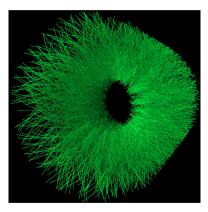

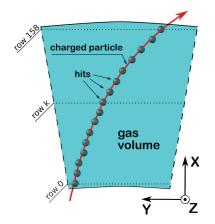

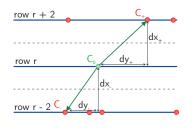

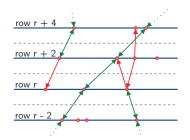

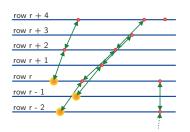

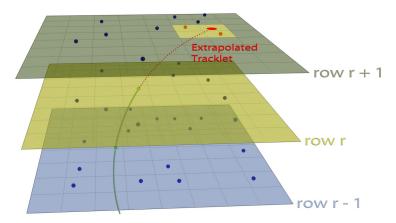

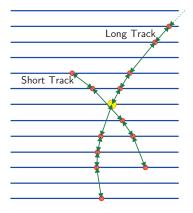

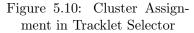

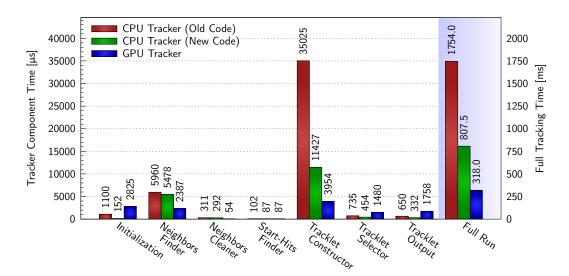

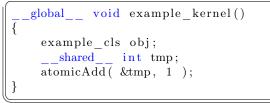

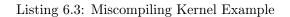

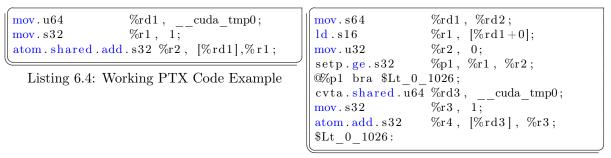

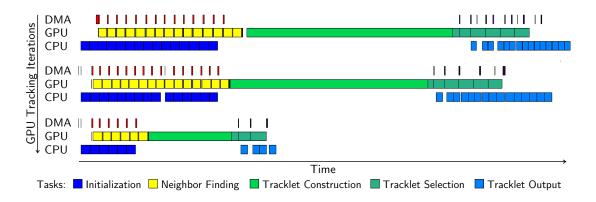

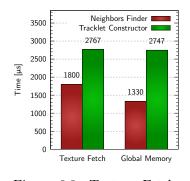

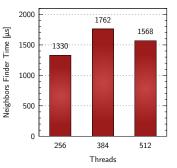

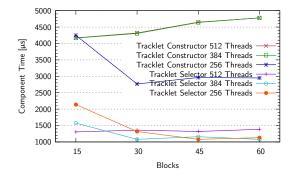

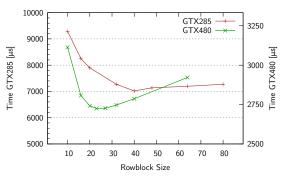

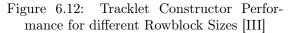

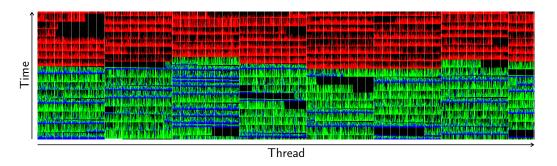

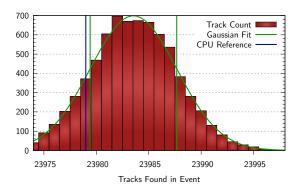

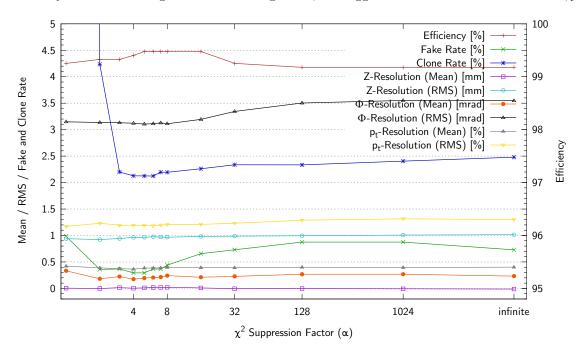

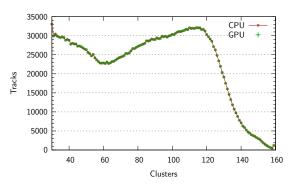

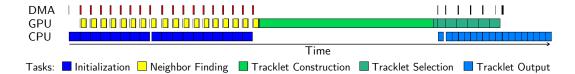

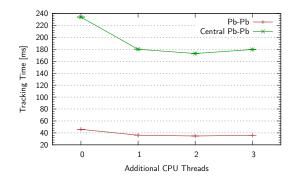

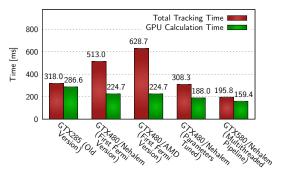

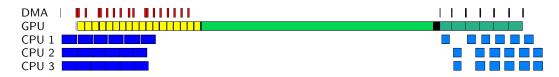

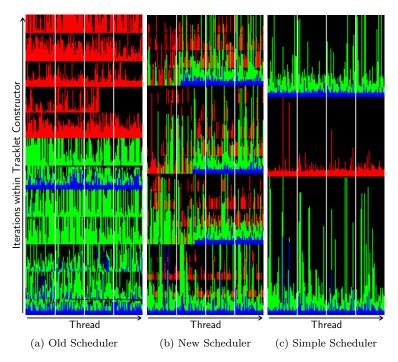

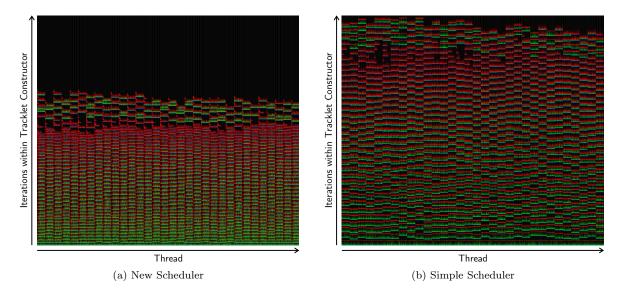

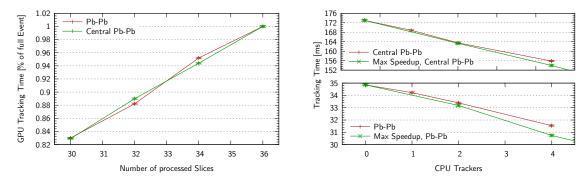

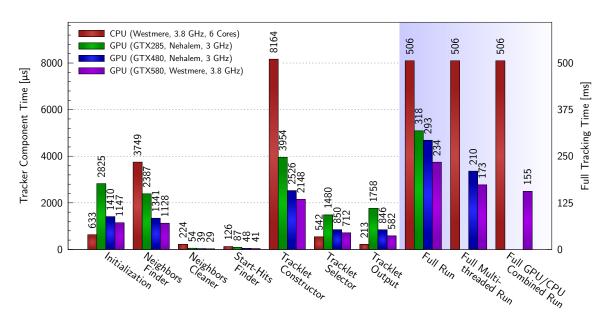

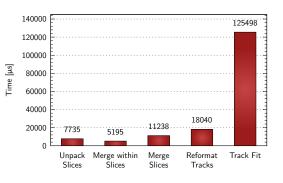

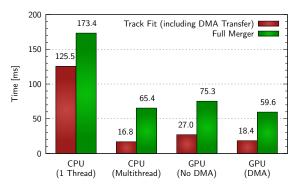

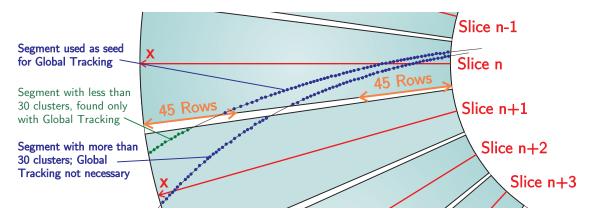

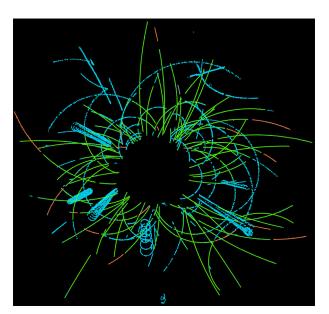

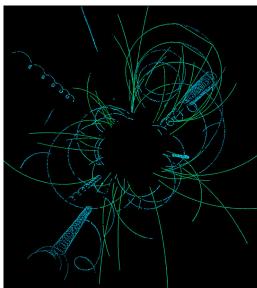

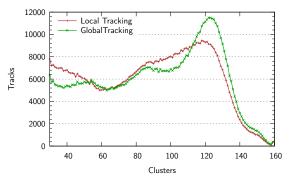

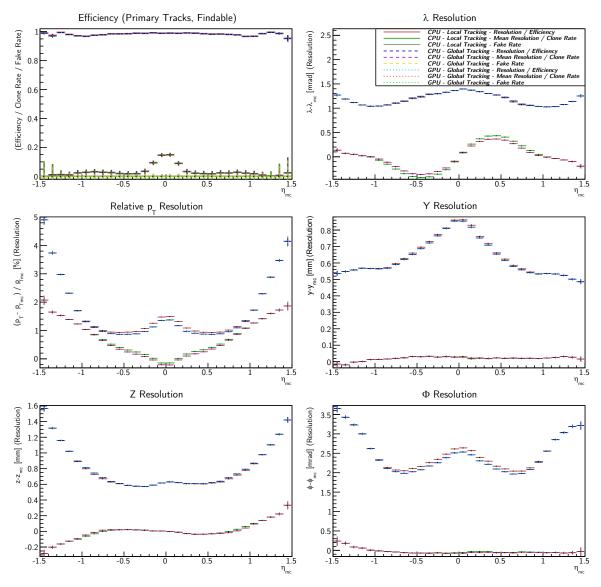

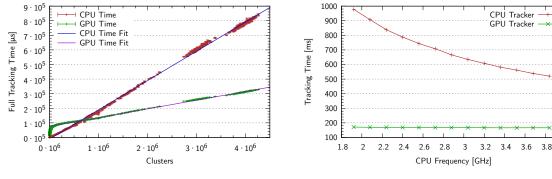

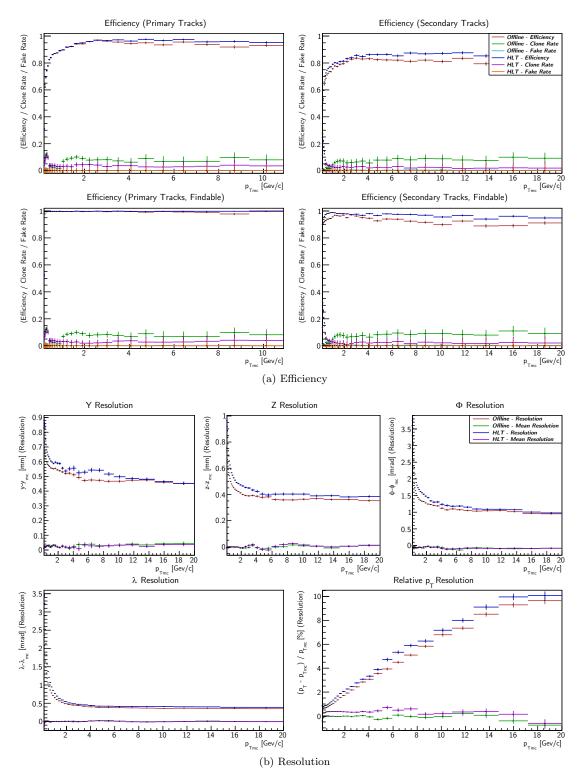

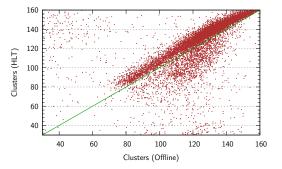

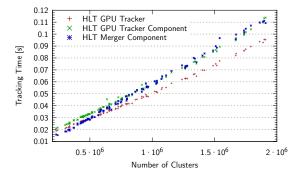

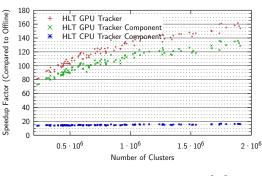

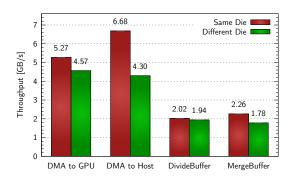

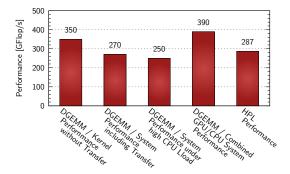

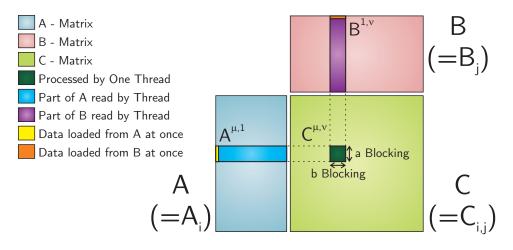

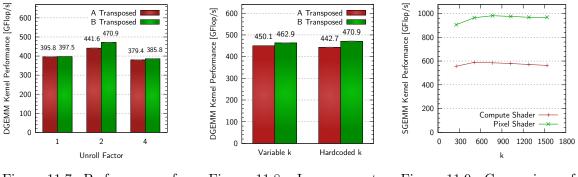

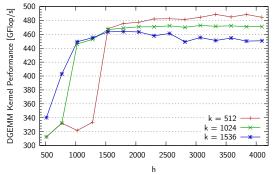

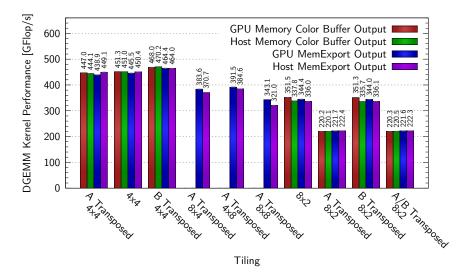

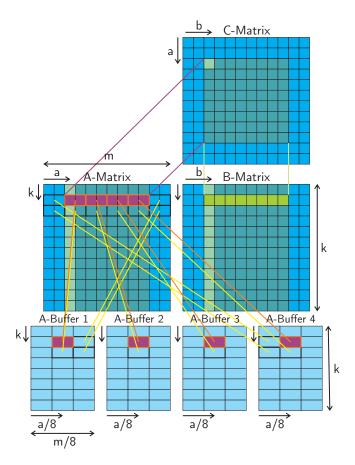

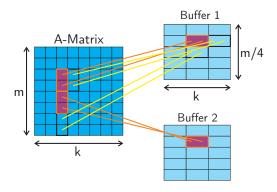

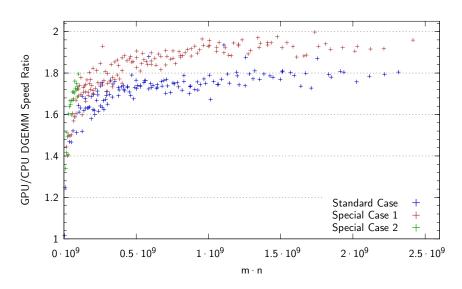

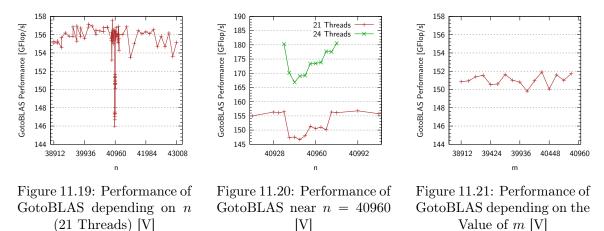

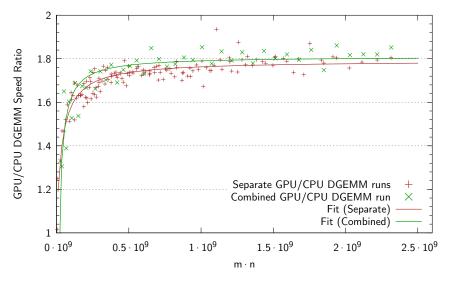

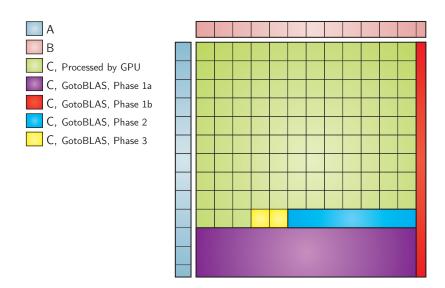

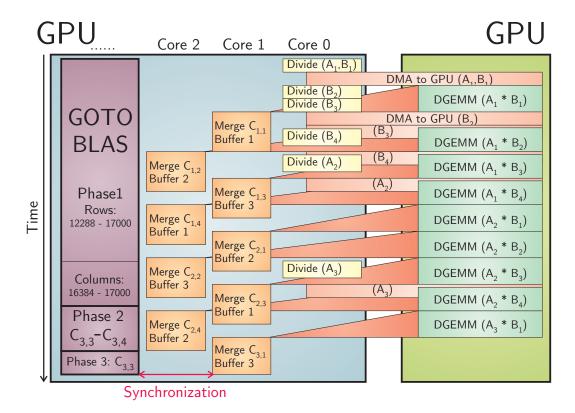

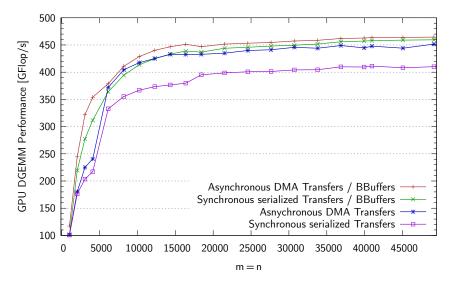

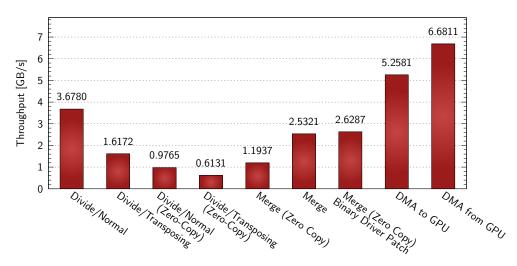

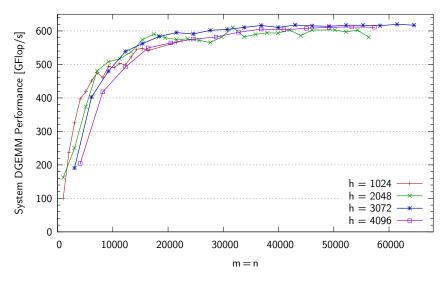

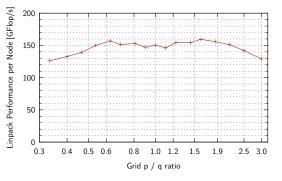

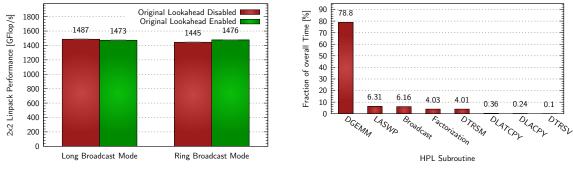

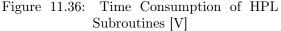

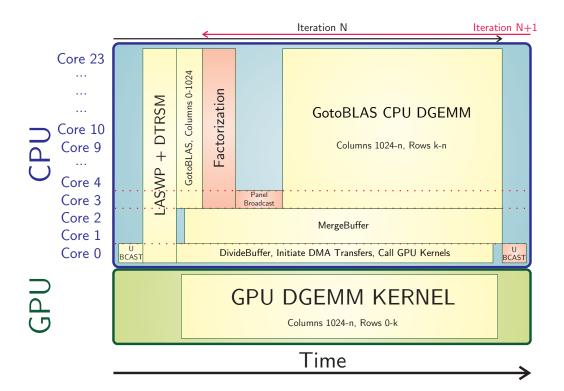

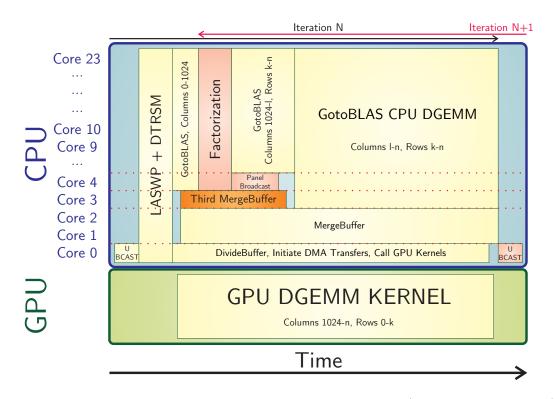

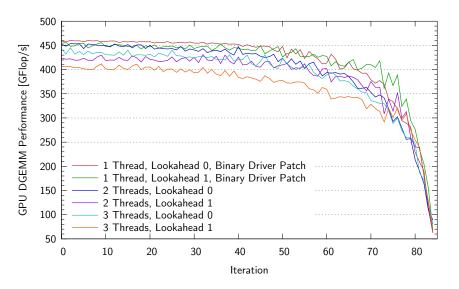

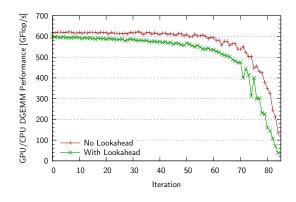

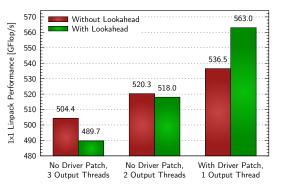

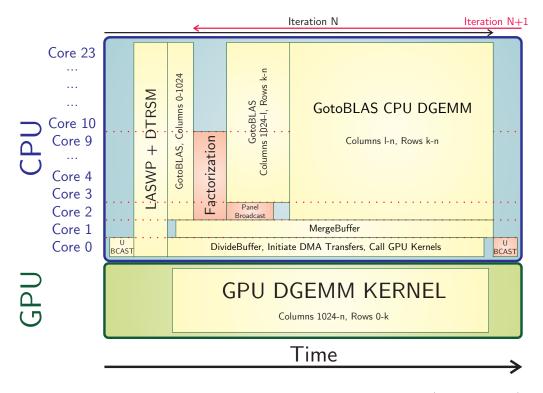

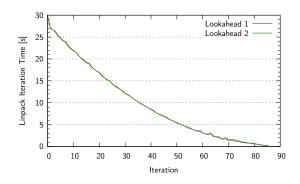

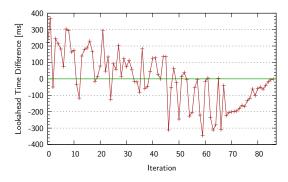

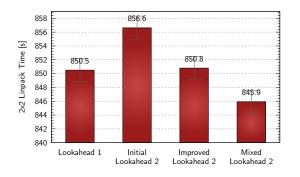

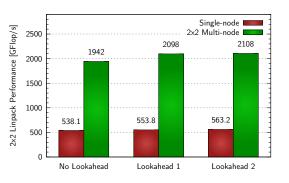

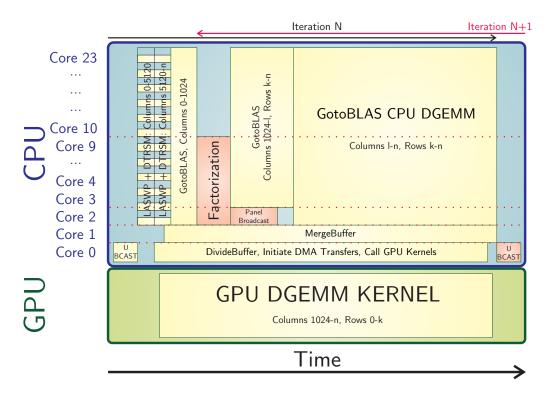

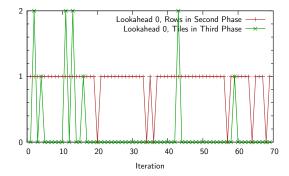

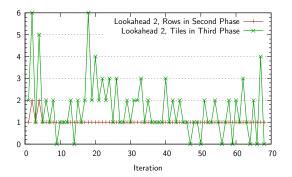

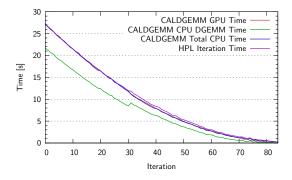

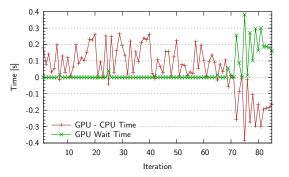

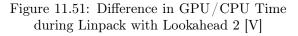

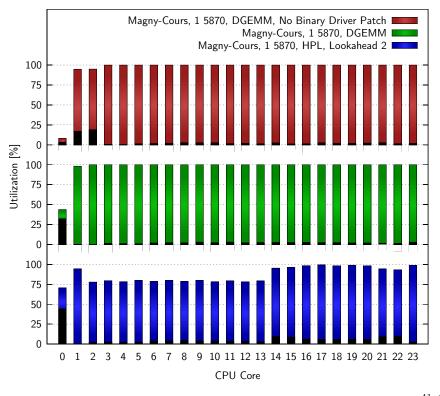

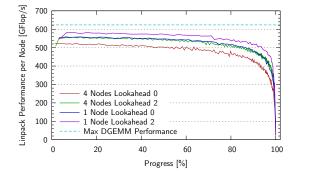

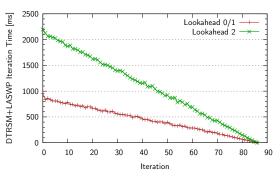

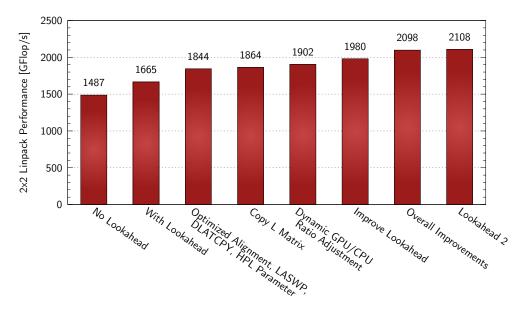

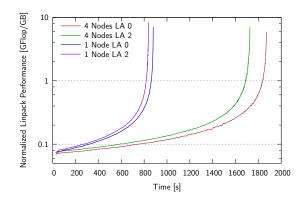

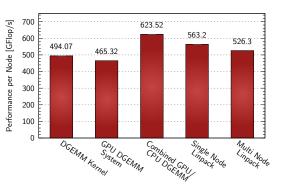

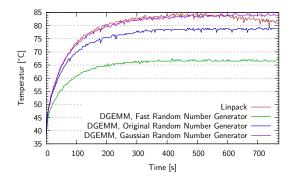

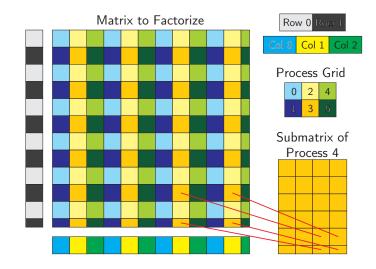

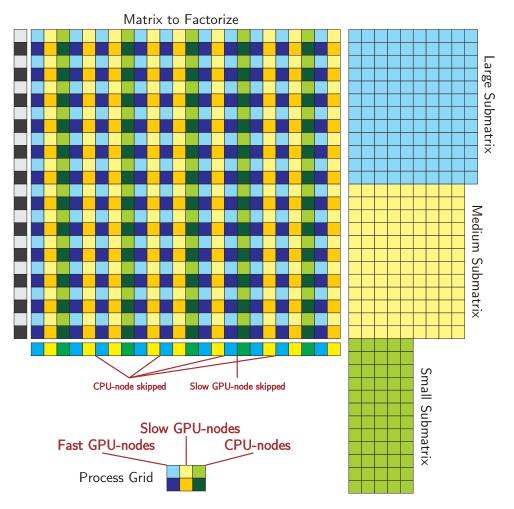

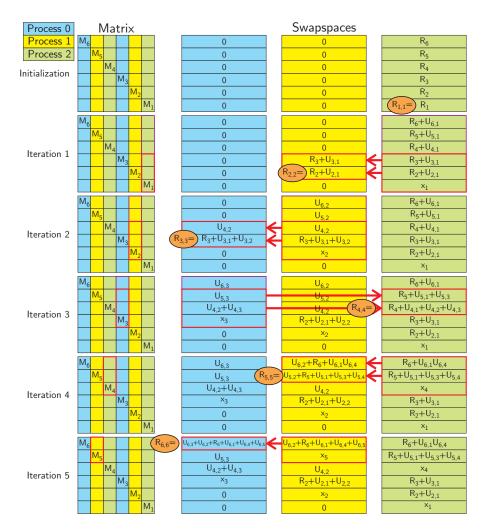

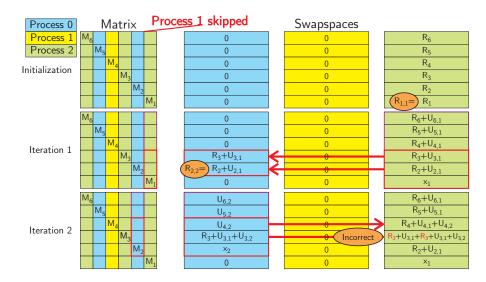

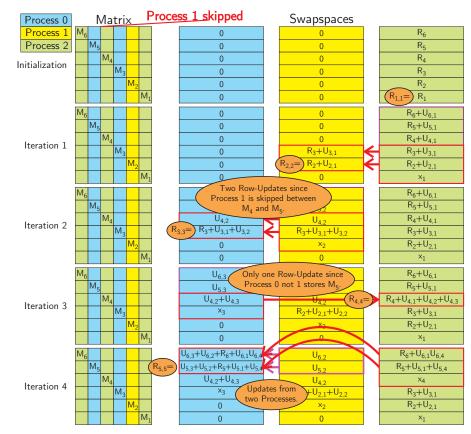

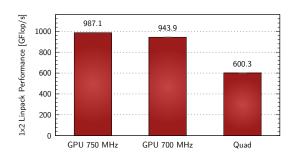

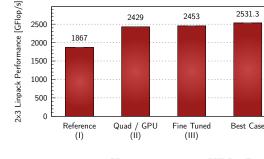

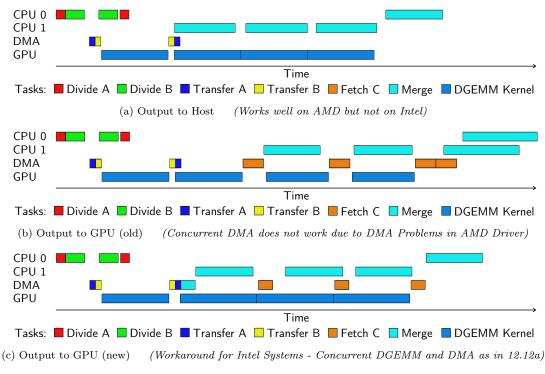

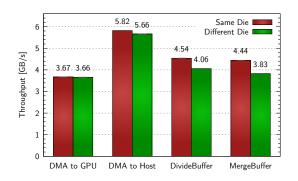

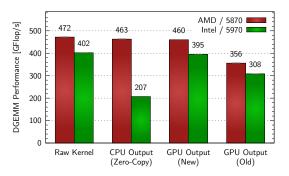

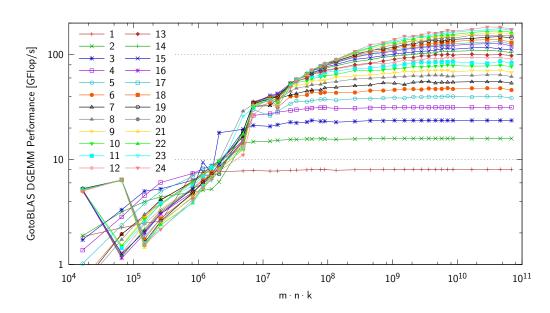

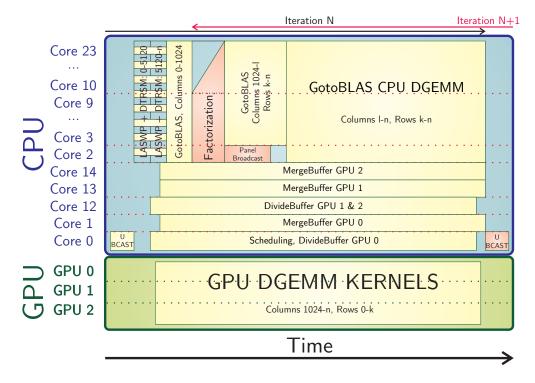

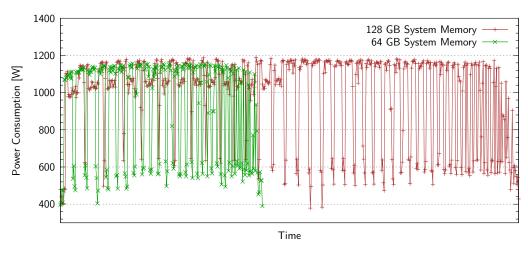

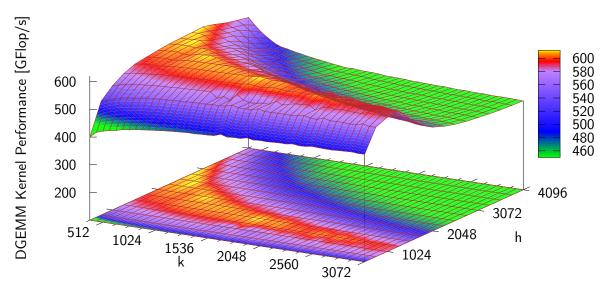

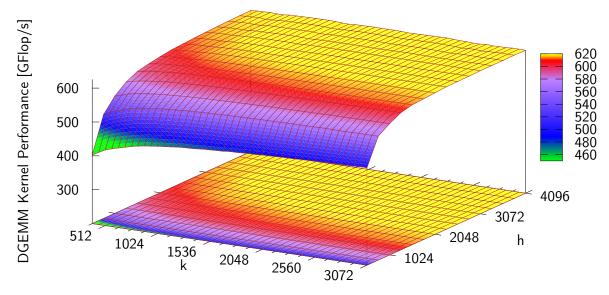

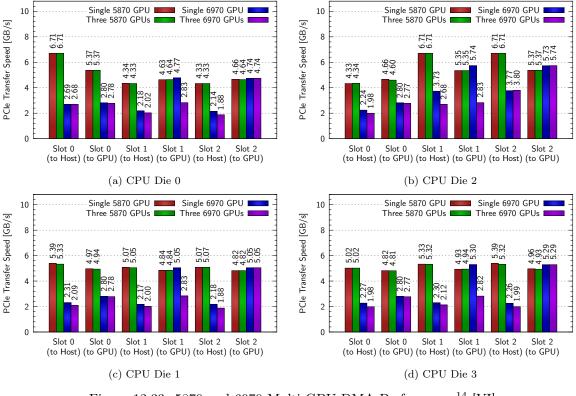

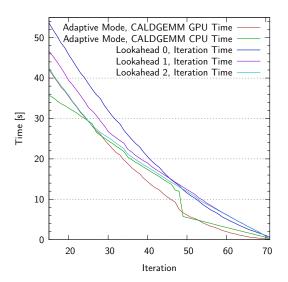

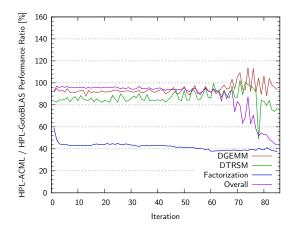

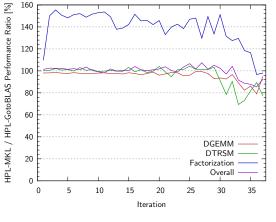

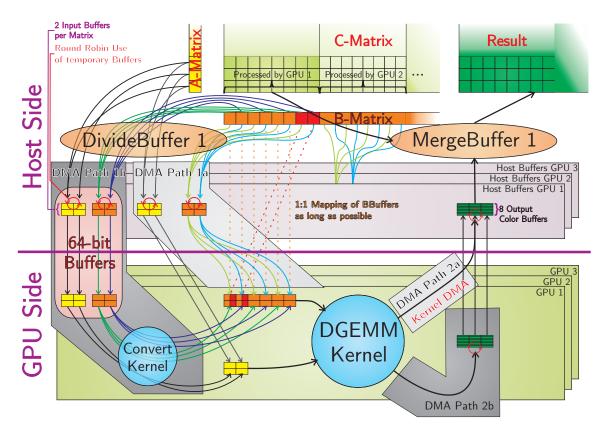

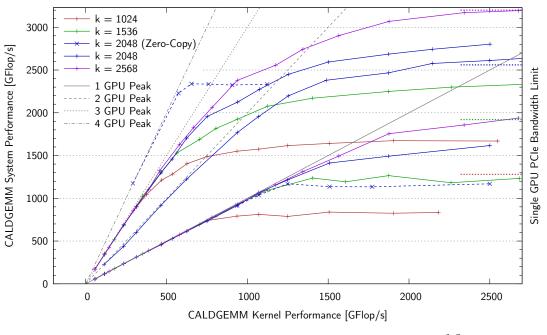

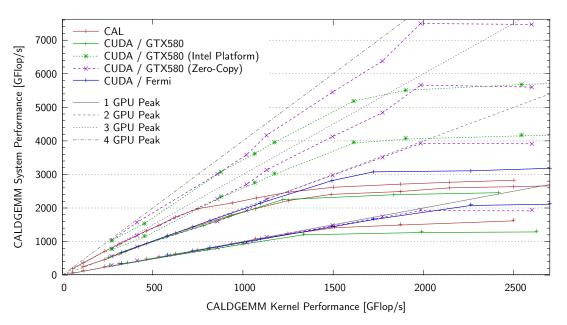

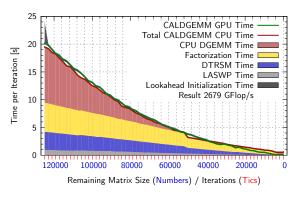

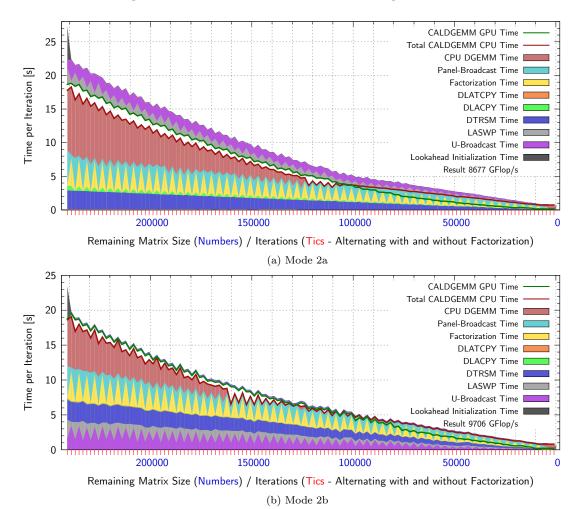

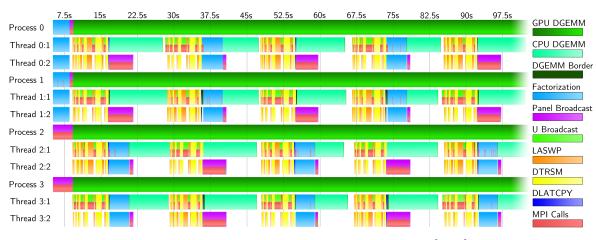

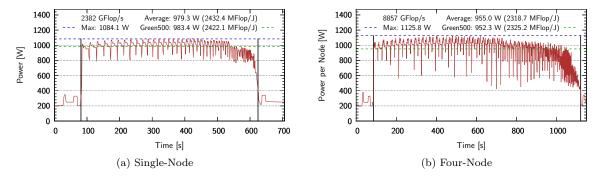

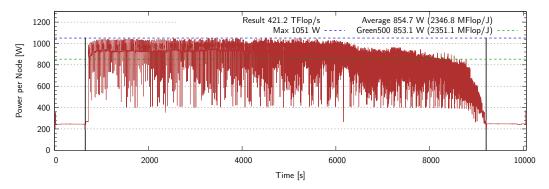

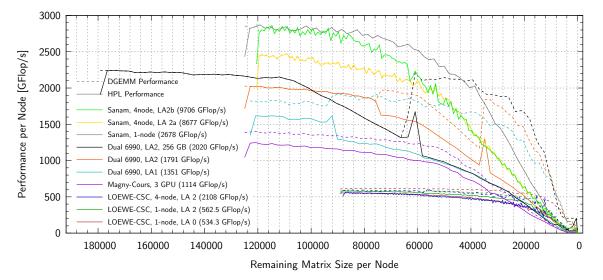

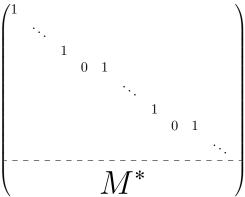

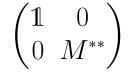

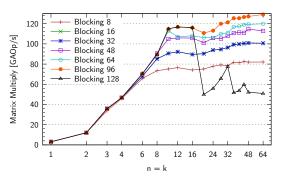

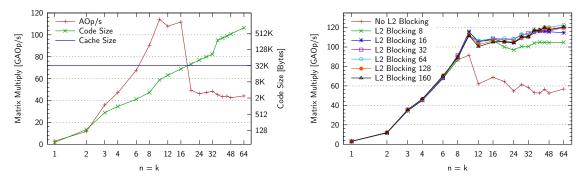

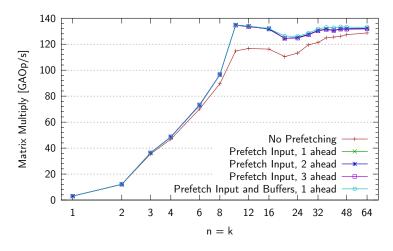

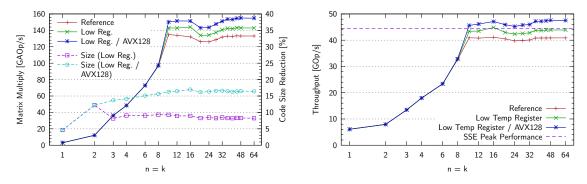

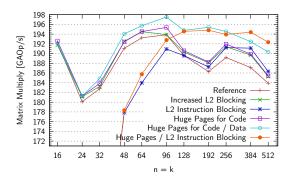

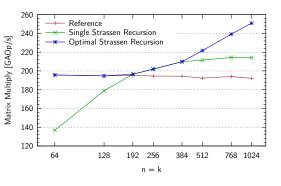

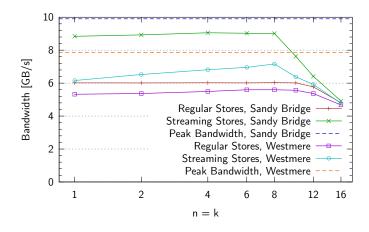

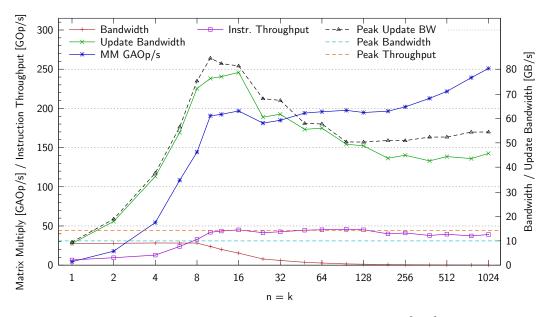

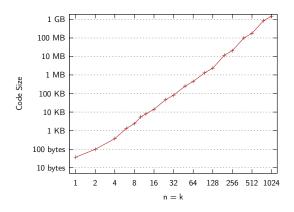

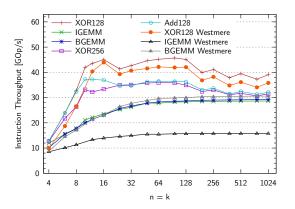

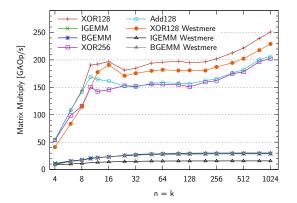

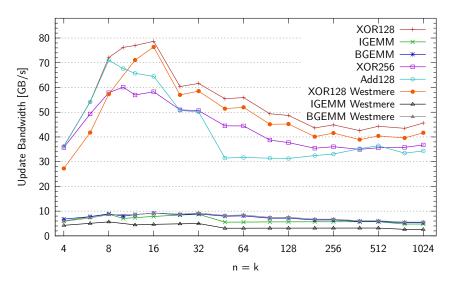

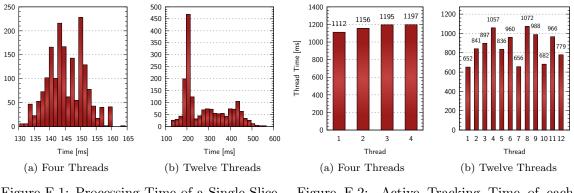

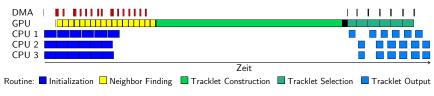

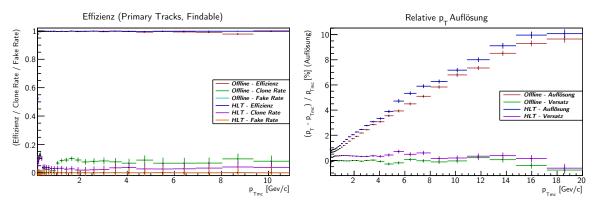

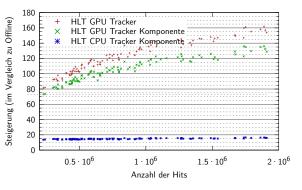

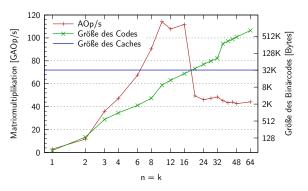

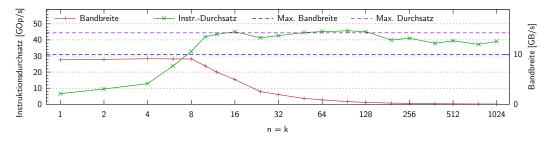

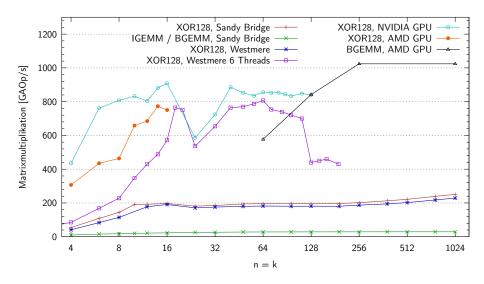

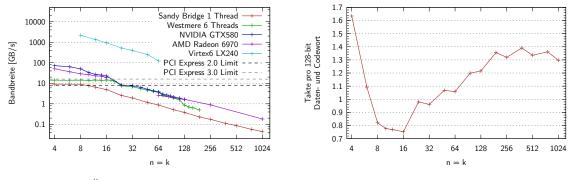

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |