#### République Algérienne Démocratique et Populaire Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Ecole Nationale Polytechnique

Département d'électronique Laboratoire des dispositifs de Communication et de conversion Photovoltaïque

# Doctoral thesis in science

**Option: Electronic Engineering**

# Study and wide band characterization of nanometric materials on SOI

#### Yasmina ATROUCHE-BELAROUSSI

Presented and publicly supported on 15/05/2018

#### Composition of the Jury:

| President :     | Mr. Cherif Larbes,           | Professor         | ENP    |

|-----------------|------------------------------|-------------------|--------|

| Advisor:        | Mr. Mohamed Trabelsi,        | Professor         | ENP    |

| Advisor:        | Mr. Mohand Tahar Belaroussi, | Research Director | DGRSDT |

| Examiners :     | Mr. Arab Azrar,              | Professor         | UMBB   |

|                 | Mr. Mourad Adnane,           | Senior Lecturer A | ENP    |

|                 | Mr. Mouloud Challal,         | Senior Lecturer A | UMBB   |

|                 | Mr. Noureddine Gabouze,      | Research Director | CRTSE  |

| Invited member: | Mr. Jean-Pierre Raskin       | Professor         | UCL    |

#### **ENP 2018**

#### République Algérienne Démocratique et Populaire

#### Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Ecole Nationale Polytechnique

Département d'électronique Laboratoire des dispositifs de Communication et de conversion Photovoltaïque

# Doctoral thesis in science

**Option: Electronic Engineering**

# Study and wide band characterization of nanometric materials on SOI

#### Yasmina ATROUCHE-BELAROUSSI

Presented and publicly supported on 15/05/2018

#### Composition of the Jury:

| President :     | Mr. Cheri Larbes,            | Professor         | ENP    |

|-----------------|------------------------------|-------------------|--------|

| Advisor:        | Mr. Mohamed Trabelsi,        | Professor         | ENP    |

| Advisor:        | Mr. Mohand Tahar Belaroussi, | Research Director | DGRSDT |

| Examiners :     | Mr. Arab Azrar,              | Professor         | UMBB   |

|                 | Mr. Mourad Adnane,           | Senior Lecturer A | ENP    |

|                 | Mr. Mouloud Challal,         | Senior Lecturer A | UMBB   |

|                 | Mr. Noureddine Gabouze,      | Research Director | CRTSE  |

| Invited member: | Mr. Jean-Pierre Raskin       | Professor         | UCL    |

ملخص

أدخلت هذه الأطروحة متغيرات جديدة من ركائز السليكون المسامية(PSi). بفضل قياسات الأداء التردد الراديو (RF). الركائز PSi) المقترحة تمت مقارنتها للعديد من ركائز تستند على السليكون الصلب، من بينها، السليكون القياسي(dtS)، السليكون الغني بالفخاخ (TR) والسليكون عالي المقاومية (HR). وقد تم إدماج خطوط (CPW) على كل الركائز المذكورة ودر اسة خصائصها إلى غاية (TR) والسليكون عالي المقاومية (HR). وقد تم إدماج خطوط (CPW) على كل الركائز المذكورة ودر اسة خصائصها إلى غاية (TR) والسليكون عالي المقاومية (HR). وقد تم إدماج خطوط (CPW) على كل الركائز المذكورة ودر اسة خصائصها إلى غاية (TR) والسليكون عالي المقاومية (HR). وقد تم إدماج خطوط (CPW) على كل الركائز المذكورة ودر اسة خصائصها إلى غاية منذه الترددات الميليمترية (70جيجا هرتس). وأظهرت الركائز الجديدة (PSi) انخفاضا في السماحية النسبية الفعالة للركيزة إلى قيم منخفضة تصل إلى 7.5 وزيادة كبيرة في المقاومية الفعالة إلى قيم أكبر من 7 كيلو أوم سم. ومن أجل إظهار فائدة الركيزة (PSi) منخفضة تصل إلى 3.7 وزيادة كبيرة في المقاومية الفعالة إلى قيم أكبر من 7 كيلو أوم سم. ومن أجل إظهار فائدة الركيزة (PSi) منخفضة تصل إلى 3.7 وزيادة كبيرة في المقاومية الفعالة إلى قيم أكبر من 7 كيلو أوم سم. ومن أجل إظهار فائدة الركيزة (PSi) منخفضة التصميم دوائر التردد الراديو(RF) العاملة في نطاق المليمتر، تم دمج مرشاح ممر الموجة (MBPF) المركز عند 27جيجا هرتس على الركائز المدروس. بالمقارنة مع (MBPF) التقليدية التي تنفذ على ركائز القياسية على أساس السليكون الصلبة، وقد أظهرت على ركائز القياسية على أساس السليكون الصلبة، وقد أظهرت معايير فياس 8 من (MBPF) على أساس السليكون الصلبة، وقد أظهرت وركائز وذلك زيادة في عامل الجودة، بالإضافة إلى ذلك، تم الحفاط على هذا الأداء حتى مع تغير في درجة الحرارة، وقد أشكن جيد المرشر وذلك وركاز (وكان المرارة، وقد أثبتت بشكل جيد وكذلك زيادة في عامل الجودة، بالإضافة إلى ذلك، تم الحفاظ على هذا الأداء حتى مع تغير في درجة الحرارة، وقد أثبتت بشكل جيد وكذلك زيادة في عامل الجودة، بالإضافة إلى ذلك، تم الحفاظ على هذا الأداء حتى مع تغير في درجة الحرارة، وقد أثبتت بشكل جيد فعالية ركاز (زكار)) المقترحة.

ا**لكلمات الدالة:** مرشاح ممر الموجة (FBP)، ارتفاع في درجة الحرارة، موجة ملليمتر، الحد الأدنى فقدان الإدراج، السليكون المسامية (PSi).

#### Résumé : Etude et caractérisation large bande de matériaux nanométriques sur SOI

Dans cette thèse, de nouvelles variantes de substrats en silicium poreux (PSi) ont été introduites. Grâce aux mesures des performances RF, les substrats PSi proposés ont été comparés à différents substrats à base de silicium massif, à savoir, le silicium standard (Std), le silicium riche en piège (trap-rich) (TR) et le silicium à haute résistivité (HR). Des lignes CPW ont été intégrées sur tous les substrats mentionnés et une caractérisation jusqu'aux fréquences millimétriques (70 GHz) a été effectuée. Les nouveaux substrats PSi ont montré une réduction de la permittivité relative effective du substrat à des valeurs aussi basse que 3,7 et une augmentation considérable de la résistivité effective à des valeurs supérieures à 7 k $\Omega$ cm. Afin de démontrer l'utilité du substrat PSi pour la conception des circuits RF fonctionnant en bande millimétrique, un filtre passe-bande (MBPF) centré à 27 GHz a été intégré sur les substrats étudiés. Par rapport au MBPF classique mis en œuvre sur des substrats standards à base de silicium massif, les paramètres S mesurés du MBPF à base de PSi ont montré des performances de filtrage élevées, comme la réduction des pertes d'insertion, une amélioration de la sélectivité du filtre ainsi qu'une augmentation du facteur de qualité, de plus, ces performances ont été maintenue même avec le changement de la température, l'efficacité des substrats PSi proposés a été bien mise en évidence.

**Mots-clés :** Filtre passe-bande (BPF), Haute température, Onde millimétrique, Perte d'insertion minimale, Silicium poreux (PSi).

#### Abstract

In this thesis, new variants of porous silicon (PSi) substrates have been introduced. Through RF performance measurements, the proposed PSi substrates have been compared with different silicon-based substrates, namely, standard silicon (Std), trap-rich (TR) and high resistivity (HR). All of the mentioned substrates have been fabricated where identical samples of CPW lines have been integrated on and characterization to the millimeter wave frequencies (70 GHz) was performed. The new PSi substrates have shown successful reduction in the substrate's effective relative permittivity to values as low as 3.5 and great increase in the effective resistivity to values higher than 7 k $\Omega$ .cm. As a concept proof, a millimeter-wave bandpass filter (MBPF) centered at 27 GHz has been integrated on standard silicon-based substrates, the measured S-parameters of the PSi-based MBPF have shown high filtering performance, such as, a reduction in insertion loss and an enhancement of the filter selectivity. Having obtained the same filter performance by varying the temperature, the efficiency of the proposed PSi substrates has been well highlighted.

**Keywords:** Bandpass filter (BPF), High temperature, Millimeter-wave, Minimum insertion loss, Porous silicon (PSi)

"The art of being sometimes very daring and sometimes very careful is the art of succeeding "

Napoléon Bonaparte

#### Acknowledgments

بسم الله الرحمان الرحيم

In the Name of God, the Most Gracious, the Most Merciful

All praise is due to ALLAH, the almighty, for giving me the strength and power to start and finish this work.

First of all, I would like to thank my PhD supervisors: Prof. Mohamed Trabelsi, and Dr. Mohand Tahar Belaroussi for the follow-up of my thesis, their patience, and the trust they have granted on me throughout these years.

I wish to thank all the jury members, who have kindly accepted to be part of my thesis Jury and for the honor they granted me by agreeing to examine my work and particularly Prof. Cherif Larbes for having agreed to chair this Jury.

I would like to express my heartfelt gratitude to Prof. Jean-Pierre Raskin for having hosted me in the ICTEAM laboratory at the Université Catholique de Louvain, Belgium for eighteen months, during which I had the immense privilege and the honor to interact with him and the other members of his group. I would also like to thanks him for his sympathy, support and valuable advices. I do not forget to express my gratitude and thankfulness to Pascal Simon, the technical manager of the WELCOME platform. I am grateful to ICTEAM administrative and technical staffs for their help, and all the WINFAB clean-room team Christian, Andre, Miloud and Ester. My special thanks also go to all friends whom I met during this PhD journey, Gilles, Khaled, Martin, Mostafa, Jonathan, Laurent and Mohamed. Last and the best important, special thanks go to all my friends, who adopted me and being my second family during my stay in Belgium for your support, friendship, care and love: Lila, Kinda, Assia, Lamia, Donia, Karima, Nora, Ibtissem, Siham, and Dina.

I would like to thank Dr. N. Gabouze for opening the doors of the CMSI (Thin Films, Surfaces and Interfaces) laboratory of CRTSE and the interest carried for my work.

A lively thanks for my colleague Dr. Ahmed Abdelhalim Saadi for all his scientific discussions, his advice, his precious reading, correction of the memory, and especially for his moral support. My thanks for my dear friends Karima and Amel.

I thank my husband who always encouraged me to go ahead. A warm thanks for my mother and mother in law for their prayers.

# CONTENTS

| LIST OF FIGURES                                                              |      |

|------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                               |      |

| LIST OF ACRONYMS                                                             |      |

| LIST OF SYMBOLS                                                              |      |

| GENERAL INTRODUCTION                                                         | 17   |

| CHAPTER 1. SUBSTRATES TECHNOLOGIES FOR RF APPLICATIONS                       |      |

| 1.1 Introduction                                                             | 22   |

| 1.2 Description of substrates for RF applications                            | . 22 |

| 1.2.1 Standard silicon substrate (Std)                                       | . 22 |

| 1.2.2 High resistivity silicon on insulator substrate (HR-SOI)               | . 23 |

| 1.2.3 Trap-rich high resistivity substrate TR-Si                             | . 23 |

| 1.2.4 Porous silicon substrate PSi                                           | . 24 |

| 1.3 The physics of porous silicon                                            | . 25 |

| 1.3.1 Introduction                                                           | . 25 |

| 1.3.2 History of porous silicon                                              | . 26 |

| 1.3.3 Nanostructuring and morphology                                         | . 26 |

| 1.3.4 Gravimetric measurement                                                | . 27 |

| 1.3.5 Thickness layers                                                       | . 29 |

| 1.3.6 Thermal oxidation of porous silicon                                    | . 29 |

| 1.3.7 Applications of porous silicon                                         | 30   |

| 1.4 Conclusion                                                               | 31   |

| CHAPTER 2. ELABORATION AND PHYSICAL CHARACTERIZATION OF PSI FOR APPLICATIONS | RF   |

| 2.1 Introduction                                                             | 33   |

| 2.2 Elaboration of porous silicon                                            | 33   |

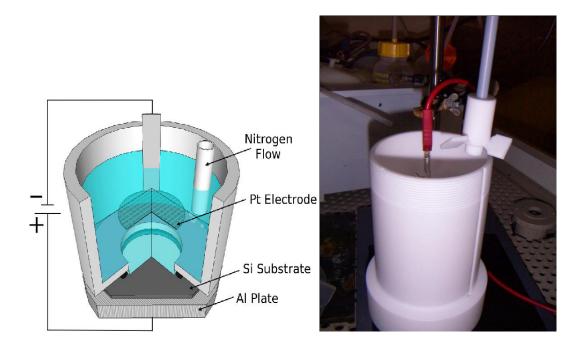

| 2.2.1 Experimental setup for the electrochemical etching                     | 33   |

| 2.2.2. Porous silicon anodization parameters                                 | 35   |

| 2.3 Morphological characterization of porous silicon                         | 35   |

| 2.3.1 Scanning electron microscopy (SEM) analysis                            | . 36 |

|                                                                              |      |

| 2.3.2 Porosity                                                              |               |

|-----------------------------------------------------------------------------|---------------|

| 2.3.3 Atomic force microscopy (AFM) analysis                                |               |

| 2.4 Optical characterization of porous silicon                              |               |

| 2.5 Mechanical characterization of porous silicon                           |               |

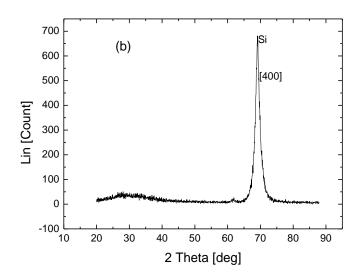

| 2.5.1 X-ray diffraction (XRD) analysis                                      |               |

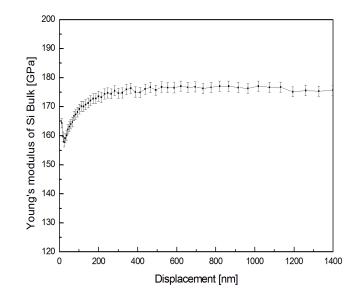

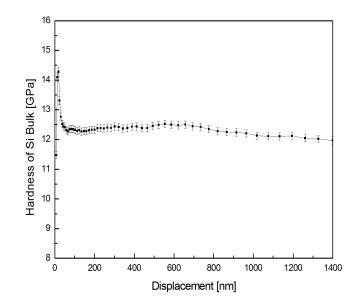

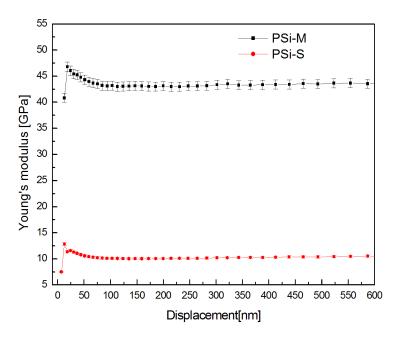

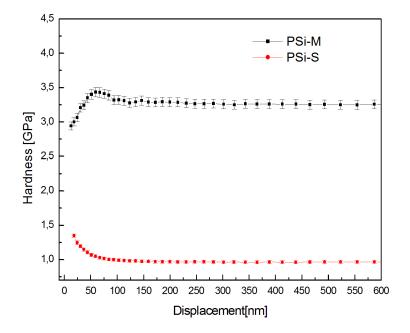

| 2.5.2 Measurement of Young's modulus and hardness                           |               |

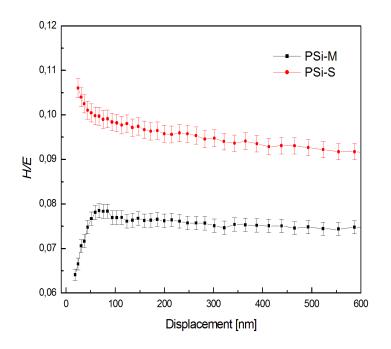

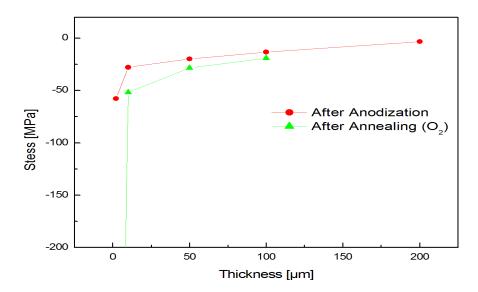

| 2.5.3 Stress determination                                                  | 53            |

| 2.6 Conclusion                                                              | 55            |

| CHAPTER 3. SUBSTRATES WIDE BAND CHARACTERIZATION FOR APPLICATIONS           | OR RF         |

| 3.1 Introduction                                                            |               |

| 3.2 Transmission lines, microstrip and coplanar structures                  |               |

| 3.3 Characterization of CPW transmission lines                              | 61            |

| 3.3.1 Transmission line model of CPW                                        |               |

| 3.3.2 Scattering parameters                                                 |               |

| 3.3.3 Effective resistivity of CPW transmission lines                       |               |

| 3.3.4 Measurement setup of CPW characterization                             |               |

| 3.4 Harmonic distortion                                                     |               |

| 3.4.1 Non-linear system                                                     |               |

| 3.4.2 Setup for harmonic distortion characterization                        |               |

| 3.5 Integration of CPW lines on Si-based substrates                         |               |

| 3.5.1 Si-based substrates preparation                                       |               |

| 3.5.2 Integration of CPW lines                                              |               |

| 3.6 RF characterization of PSi substrates annealed at different temperative | ature 76      |

| 3.7 RF characterization of Si-based substrates                              | 80            |

| 3.7.1 Small-signal RF measurements of CPW                                   | 80            |

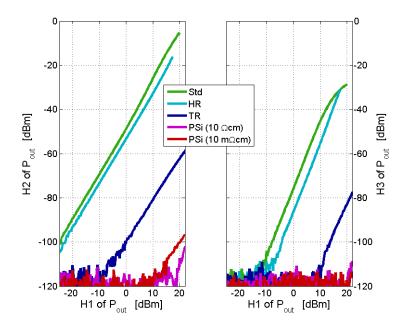

| 3.7.2 Large-signal harmonic distortion of CPW lines                         | 83            |

| 3.8 Effect of temperature on RF performances                                |               |

| 3.9 Conclusion                                                              | 87            |

| CHAPTER.4. ELABORATION OF A DEMONSTRATOR ON SI BASE                         | ED SUBSTRATES |

| 4.1 Introduction                                                            |               |

| 4.2 Bandpass filter design in millimeter band                               |               |

| 4.3 Electromagnetic simulation used in filter design                        |               |

| 4.4 Millimetric filter on Si-based substrates                               |               |

| 4.5 Characterization of the fabricated filter                               |               |

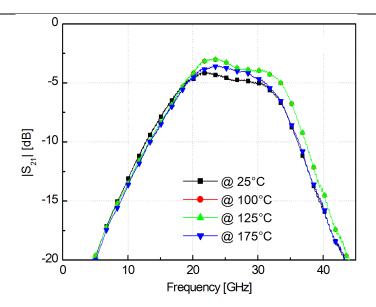

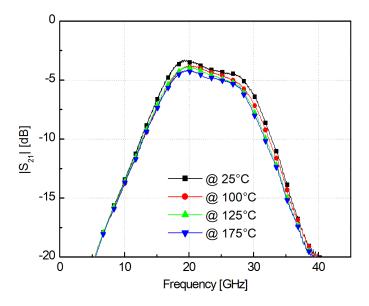

| 4.6 Effect of temperature on the RF performance of the bandpass filte       | er 98         |

| 4.7 Results and discussion                                                  |               |

| 4.8 Conclusion                                                              |               |

| GENERAL CONCLUSION                                                          |               |

| BIBLIOGRAPHY | 107 |

|--------------|-----|

| ANNEX        |     |

| Annex A      | 123 |

# **List of Figures**

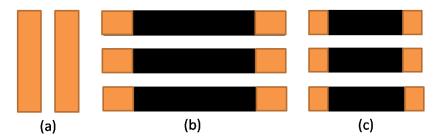

| Figure 1.2 Trap-rich wafer                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.3 Porous Silicon wafer                                                                                                                                    |

| Figure 1.4 Morphological features of porous silicon                                                                                                                |

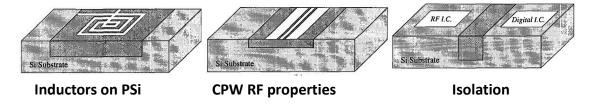

| Figure 1.5 Porous silicon technology for RF Integrated Circuit Applications [65-66]30                                                                              |

| Figure 2.1 Electrochemical cell used for the anodization                                                                                                           |

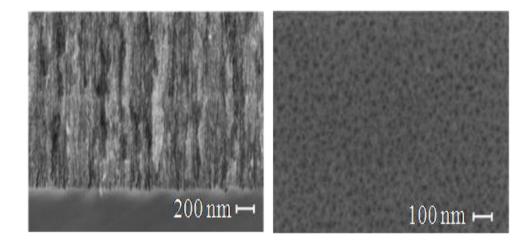

| Figure 2.2 Cross-sectional SEM image (left) and top view (right) of mesopores obtained after anodization of highly doped P-type Si ( $\rho$ = 5-20 m $\Omega$ .cm) |

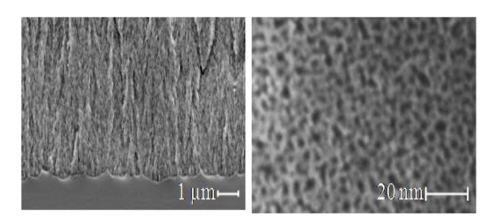

| Figure 2.3 Cross-sectional SEM image (left) and top view(right) of mesopores obtained after anodization of standard P-type Si ( $\rho = 1-10\Omega.cm$ )           |

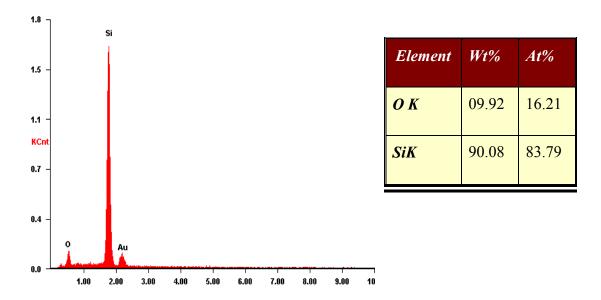

| Figure 2.4 Energy dispersive spectroscopy spectrum of porous silicon layer after oxidation.37                                                                      |

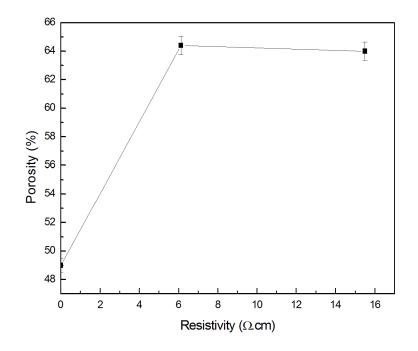

| Figure 2.5 Porosity vs resistivity for 50µm of porous silicon                                                                                                      |

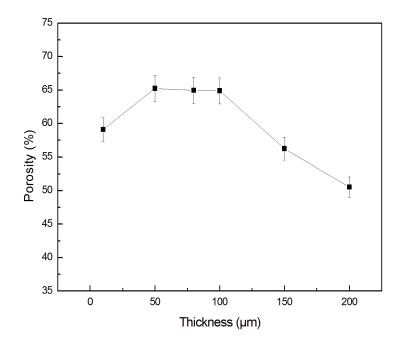

| Figure 2.6 Variation of porosity with thickness for 50 μm of porous silicon                                                                                        |

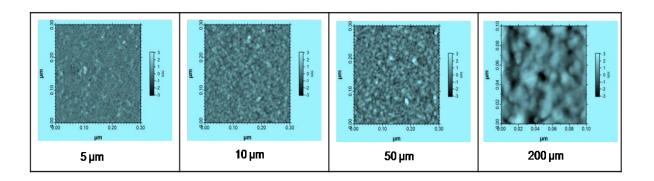

| Figure 2.7 AFM image of different thickness of PSi-S substrate $(1-10\Omega.cm)$                                                                                   |

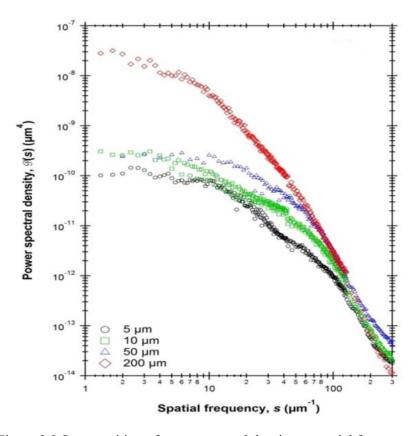

| Figure 2.8 Superposition of pozer spectrql density vs spqtiql freauency of $(5\mu m, 10 \mu m, 50 \mu m)$ thickness of PSi-S substrate                             |

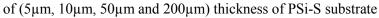

| Figure 2.9 Superposition of RMS roughness vs length scqle of (5μm, 10 μm, 50 μm and 200 μm) thickness of PSi-S substrate                                           |

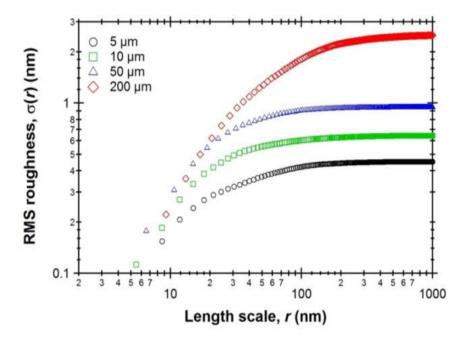

| Figure 2.10 RMS roughness and correlation length vs thickness of PSi-S substrate                                                                                   |

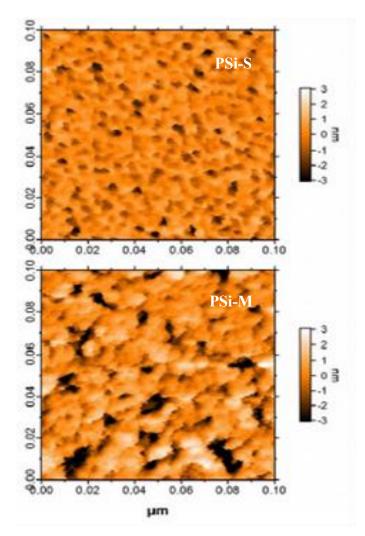

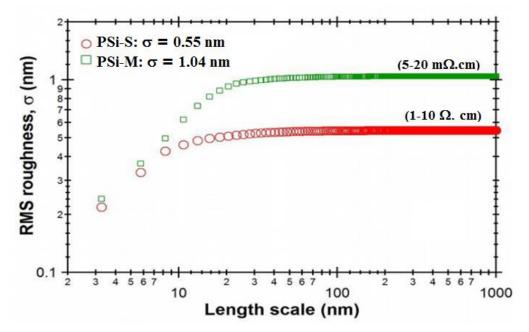

| Figure 2.11 AFM image of PSi-S and PSi-Mwith the same thickness 50µm of PSi                                                                                        |

| Figure 2.12 RMS roughness for two resistivity used PSi-S (1-10 $\Omega$ .cm) and PSi-M (5-20 m $\Omega$ .cm) with the same thickness 50 $\mu$ m of PSi             |

| Figure 2.13 FTIR Spectrum of porous silicon layer before oxidation                                                                                                 |

| Figure 2.14 FTIR Spectrum of porous silicon layer after oxidation                                                                                                  |

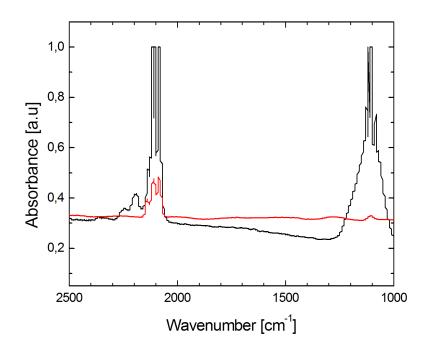

| Figure 2.15 Superposition of FTIR spectra of the 50 µm porous Si film after oxidation 46                                                                           |

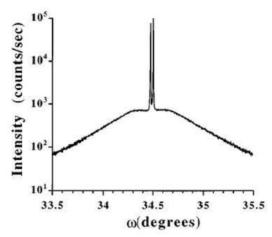

| Figure 2.16 High resolution X-ray diffraction profile obtained on a mesoporous silicon sample with a 65% porosity <b>[83]</b>                                      |

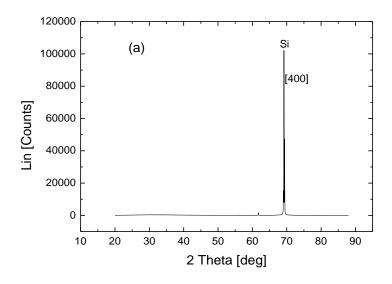

| Figure 2.17 X-ray diffraction spectrum of porous Si (100) p-type before oxidation                                                                                  |

| Figure 2.18 X-ray diffraction spectrum of porous Si (100) p-type after oxidation                                                                                   |

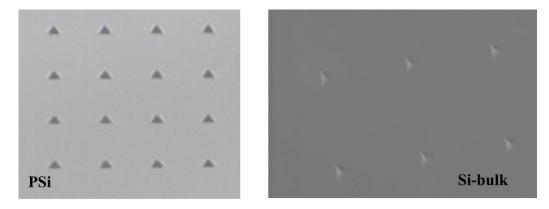

| Figure 2.19 Pyramidal fingerprints obtained by the hardness test on PSi and Si-bulk                                                                                |

| Figure 2.20 Variation of Young's modulus vs displacement in bulk silicon                                                                                           |

| Figure 2.21 Hardness vs displacement in bulk silicon 49                                                                                                            |

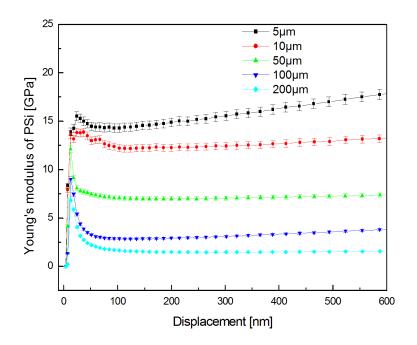

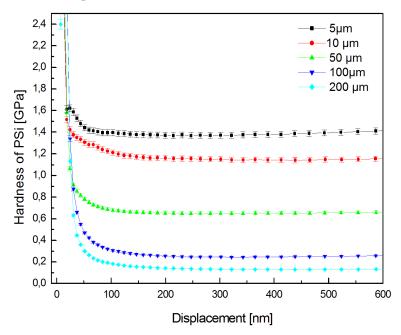

| Figure 2.22 Variation of the Young's modulus vs displacement inporous silicon for different thickness of PSi                                                 |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.23 Hardness vs displacement inporous silicon for different thickness of PSi                                                                         | 50   |

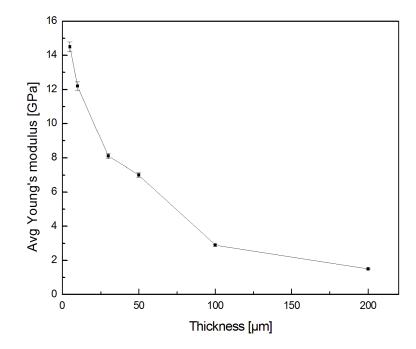

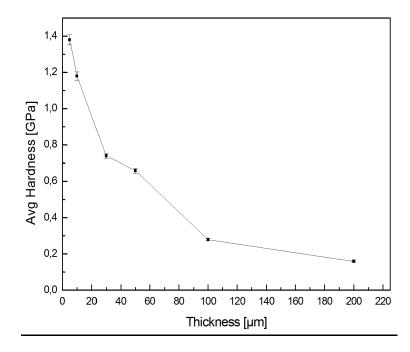

| Figure 2.24 Variation of average Young's modulus vs thickness of PSi                                                                                         | 51   |

| Figure 2.25 Variation of average hardness vs thickness of PSi                                                                                                | 51   |

| Figure 2.26 Effect of resistivity on Young's modulus                                                                                                         | . 52 |

| Figure 2.27 Effect of resistivity on Hardness                                                                                                                | . 52 |

| Figure 2.28 <i>H/E</i> vs. displacement for PSi-S and PSi-M samples                                                                                          | . 53 |

| Figure 2.29 Stress varition vs thickness                                                                                                                     | 54   |

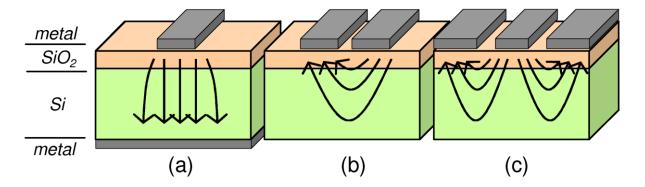

| Figure 3.1 Schematic representation of (a) MIS microstrip line, (b) coplanar stripline and (coplanar waveguide and their electric field distribution [29]    |      |

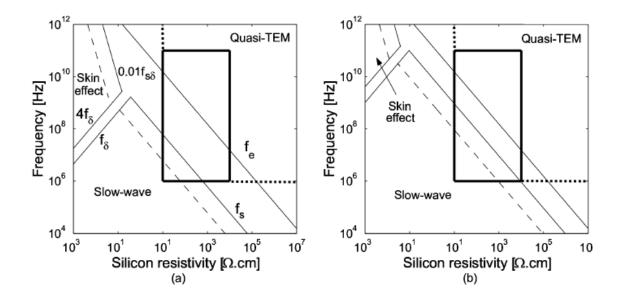

| Figure 3.2 Resistivity vs. frequency domain chart for Si substrates of (a) MIS MS line and CPW [95]                                                          |      |

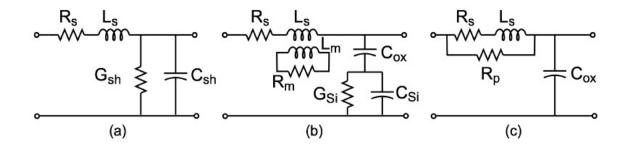

| Figure 3.3 Equivalent circuit for (a) Quasi-TEM mode, (b) Skin effect mode and (c) Slow-<br>wave propagation mode in MIS line <b>[95]</b>                    |      |

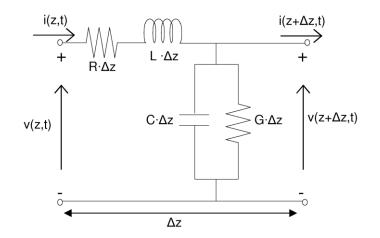

| Figure 3.4 Equivalent circuit of a lumped-element model of a transmission line [29]                                                                          | 63   |

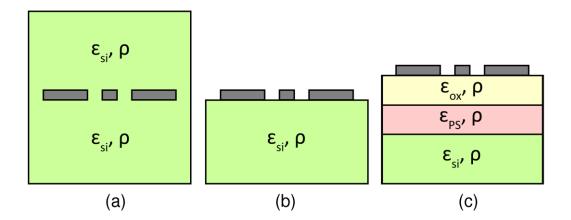

| Figure 3.5 CPW line (a) in a homogeneous material, (b) on top of a homogeneous material and (c) on top of a non-homogeneous material resistivity <b>[29]</b> |      |

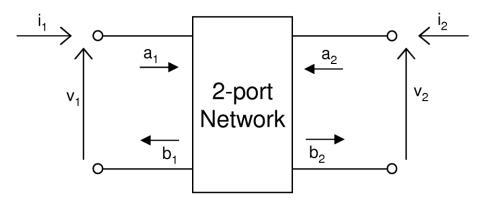

| Figure 3.6 Schematic view of a 2-port network [29]                                                                                                           | 66   |

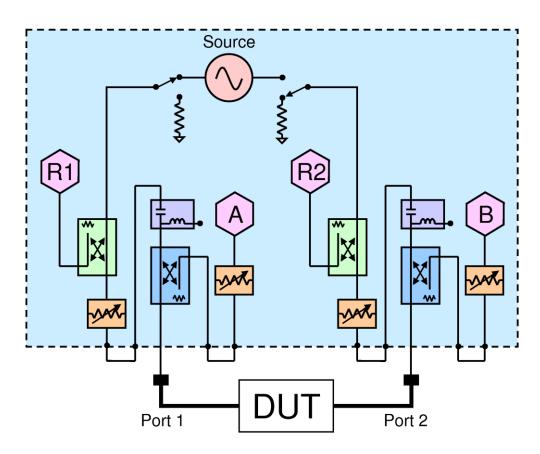

| Figure 3.7 Schematic circuit of a 2-port vector network analyzer(AGILENT's PNA-X)[109                                                                        | _    |

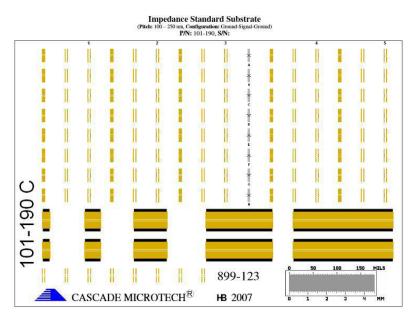

| Figure 3.8 Standards fabricated on Impedance Standard Substrate (ISS) used for calibration                                                                   |      |

| Figure 3.9 Layout of calibration standard for SOLT calibration: (a). short or open, (b) line, and (c). thru                                                  |      |

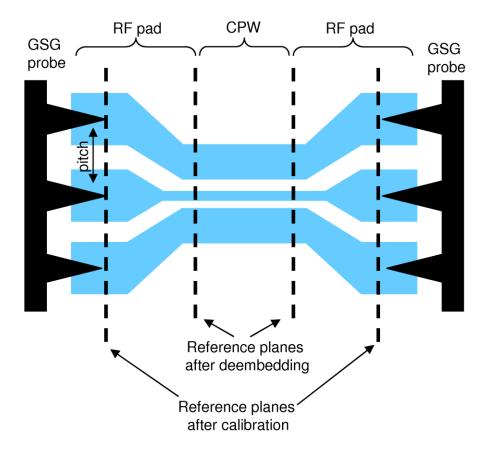

| Figure 3.10 Reference plane before and after de-embedding [29]                                                                                               | 70   |

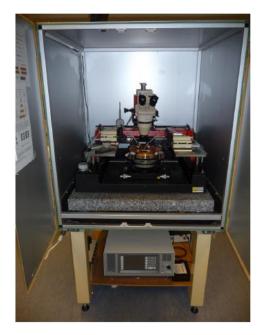

| Figure 3.11 Introduction to On-Wafer Measurement at Microwave Frequencies                                                                                    | 72   |

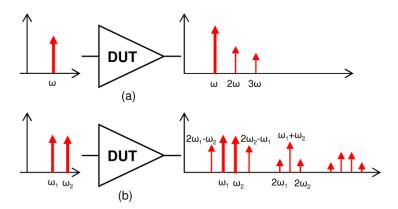

| Figure 3.12 Frequency response of a non-linear system from (a) one-tone input and (b) two tone input [29]                                                    |      |

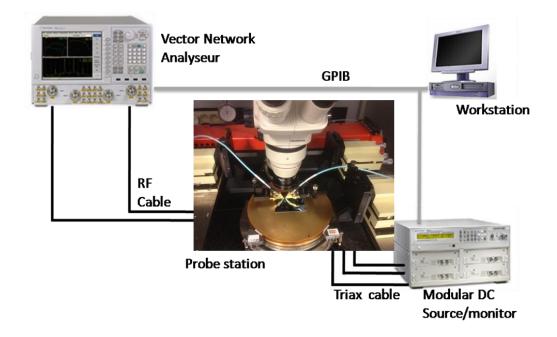

| Figure 3.13 Picture of the non-linear measurement setup                                                                                                      | 74   |

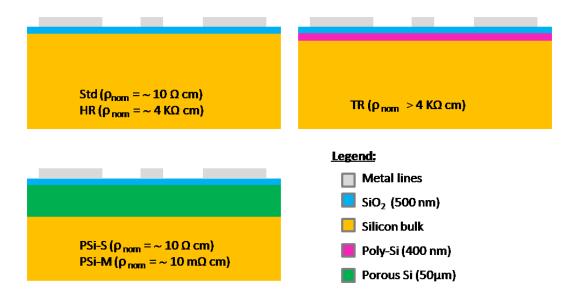

| Figure 3.14 Illustration of the five Si-based substrates under consideration                                                                                 | 75   |

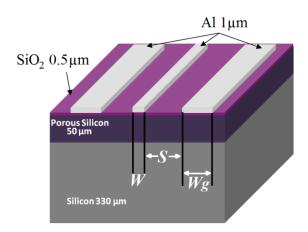

| Figure 3.15 Schematic of CPW transmission line fabricated on porous Si substrates                                                                            | 76   |

| Figure 3.16 Picture of structures fabricated on porous silicon substrate                                                                                     | 76   |

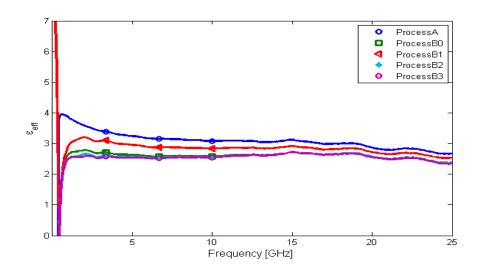

| Figure 3.17 Effective dielectric permittivity ( $\epsilon_{eff}$ ) versus frequency of CPW line on 5 differ porous Si substrates                             |      |

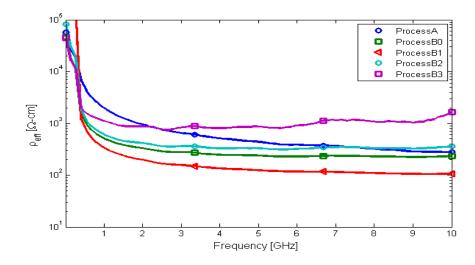

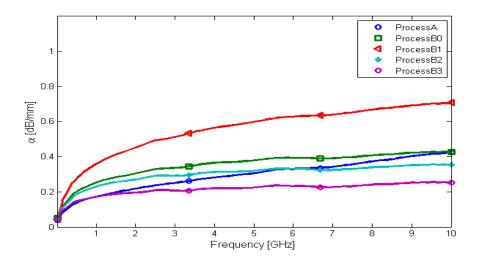

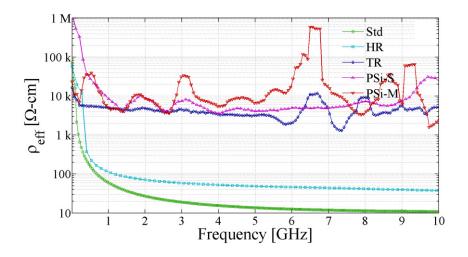

| Figure 3.18 Effective resistivity ( $\rho_{eff}$ ) versus frequency of 5 different porous Si substrates.                                                     | 78   |

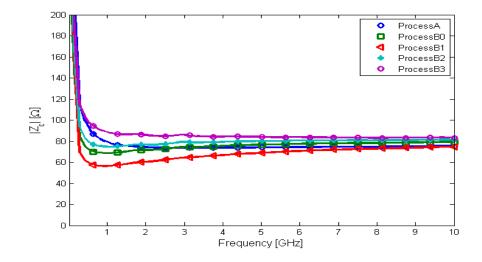

| Figure 3.19 Characteristics impedance of CPW lines on 5 different porous Si substrates                                                                       | 79   |

| Figure 3.20 Attenuation of CPW lines on5 different porous Si substrates                                                                                      | 79   |

| Figure 3.21 Picture of the wafer with the structures fabricated on PSi substrate with B3 annealing process                                                   | 80   |

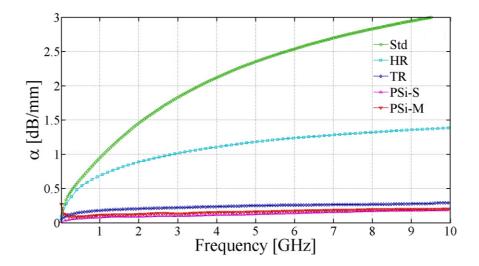

| Figure 3.23 Attenuation of CPW lines lying on five different Si-based substrates                                                                             | 82 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

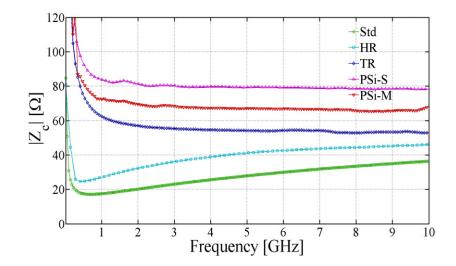

| Figure 3.24 Characteristic impedance of CPW lines lying on five different Si-based Si substrates                                                             | 82 |

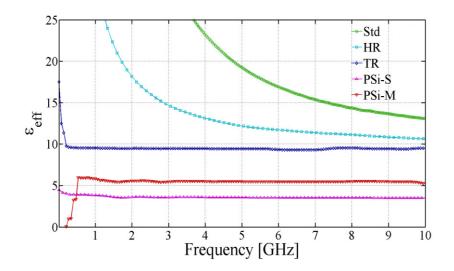

| Figure 3.25 Effective relative permittivity for CPW lines lying on five different Si-base substrates                                                         |    |

| Figure 3.26 Comparison of the measured HD levels induced in 8 mm-long CPW lines implemented on the various Si-based substrates under consideration           | 84 |

| Figure 3. 27 On-wafer probing with Temptronics High Temperature control station                                                                              | 85 |

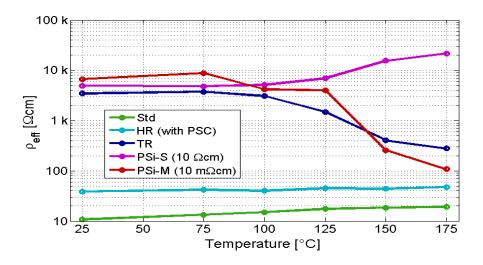

| Figure 3.28 Effective resistivity extracted at different temperature points ranging from 2 to 175°C for the five Si-based substrates                         |    |

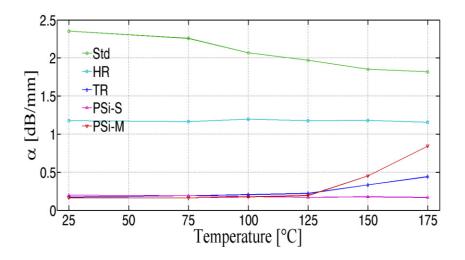

| Figure 3.29 Losses extracted at different temperature points ranging from 25°C to 175°C                                                                      | С  |

| for the five Si-based substrates                                                                                                                             | 87 |

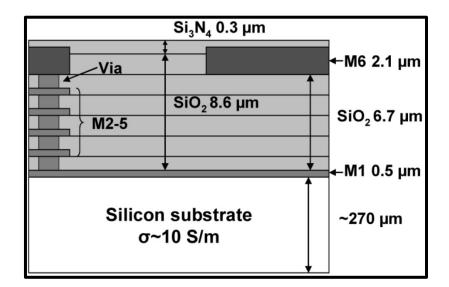

| Figure 4.1 Layers constituting 0.18 µm CMOS technology                                                                                                       | 92 |

| Figure 4.2 Simulation method No. 1 used in the design of millimetric filter                                                                                  | 92 |

| Figure 4.3 Simulation method No. 2 used in the design of millimetric filter                                                                                  | 93 |

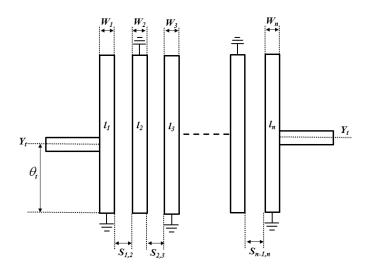

| Figure 4.4 General configuration of the interdigital band filter [135]                                                                                       | 95 |

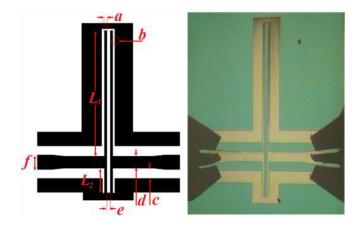

| Figure 4.5 Layout (left) and photography being measured on the probe station using 67 GSG picoprobes (right) of mm-wave bandpass filter in CPW configuration |    |

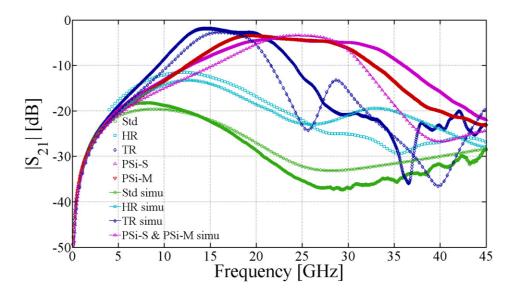

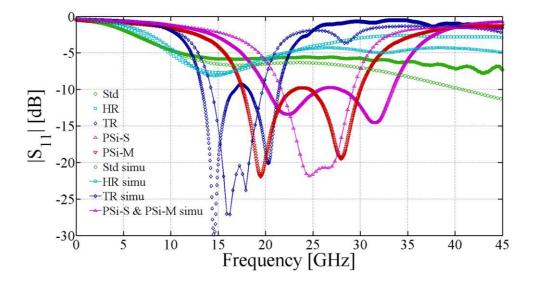

| Figure 4.6 Insertion loss of mm-wave filter implemented on various Si-based substrate                                                                        | 97 |

| Figure 4.7 Return loss of mm-wave filter implemented on various Si-based substrates                                                                          | 98 |

| Figure 4.8 Mm-wave filter insertion loss at various temperatures on PSi-Ssubstrate                                                                           | 99 |

### **List of Tables**

| Table 1 - Substrates characteristics                                                                                     | 19   |

|--------------------------------------------------------------------------------------------------------------------------|------|

| Table 2.1 - Comparison between two nominal resistivity                                                                   | 39   |

| Table 2.2 - Roughness ( $\sigma$ ) and correlation length ( $\xi$ ) corresponding values of different thickness of PSi-S | . 42 |

| Table 3.1 - Detailed description of process conditions                                                                   | 77   |

| Table 3.2 - Characteristics for Si-based substrates                                                                      | 83   |

| Table 3.3 -Comparison of PSi-based transmission line performance to the state-of-the-art         [124]                   |      |

| Table 4.1 -Variation of the insertion losses with temperature                                                            | 99   |

| Table 4.2 - Comparison of PSi-S-based mm-wave filter with filters implemented in CMOS         process                    |      |

# Acronyms

| AFM     | Atomic Force Microscopy                                 |

|---------|---------------------------------------------------------|

| BOX     | Buried Oxide                                            |

| BPF     | Band Pass Filter                                        |

| CMOS    | Complementary Metal-Oxide Semiconductor                 |

| CPS     | Coplanar Striplines                                     |

| CPW     | Coplanar Waveguide                                      |

| DUT     | Device Under Test                                       |

| EDS     | Energy Dispersive Spectroscopy                          |

| FTIR    | Fourier Transform Infrared Spectroscopy                 |

| PVD     | Physical Vapor Deposition                               |

| HD      | Harmonic Distortion                                     |

| HF      | hydrofluoric acid                                       |

| HR-Si   | High Resistivity Silicon                                |

| HR-SOI  | High Resistivity SOI                                    |

| ІоТ     | Internet of Thing                                       |

| КОН     | Potassium Hydroxide                                     |

| MNFM    | Metallic-nanowire-filled-membrane                       |

| mm-wave | millimeter-wave                                         |

| MOS     | Metal-Oxide-Semiconductor                               |

| MS      | Micro Strip                                             |

| PECVD   | Plasma-Enhanced Chemical Vapor Deposition               |

| pMOS    | Metal-Oxide-Semiconductor with p-type silicon substrate |

|         |                                                         |

| PSC              | Parasitic Surface Conduction                                                   |

|------------------|--------------------------------------------------------------------------------|

| PSi              | Porous Silicon                                                                 |

| PSi-M            | Porous Silicon from a nominal resistivity p-type Si wafer (5-20 m $\Omega$ cm) |

| PSi-S            | Porous Silicon from a standard resistivity p-type Si wafer (1-10 $\Omega$ cm)  |

| RF               | Radio Frequency                                                                |

| RMS              | Root Mean Square                                                               |

| S-CPW            | Slow-Wave Coplanar Waveguide                                                   |

| SEM              | Scanning Electron Microscope                                                   |

| SiO <sub>2</sub> | silicon oxide                                                                  |

| SN               | Sensing Nodes                                                                  |

| SoC              | System-on-Chip                                                                 |

| SOI              | Silicon-On-Insulator                                                           |

| SOLT             | Short-Open-Load-Thru                                                           |

| Std              | Standard                                                                       |

| SW-µstrip        | Slow wave µicrostrip                                                           |

| TL               | Transmission Lines                                                             |

| TMH              | TetramethylammoniumHydroxide                                                   |

| TRL              | Thru-Reflection-Load                                                           |

| TR               | Trap-Rich                                                                      |

| TR-Si            | Trap-Rich Silicon                                                              |

| VNA              | Vector Network Analyzer                                                        |

| WPAN             | Wireless Personal Area Network                                                 |

| XRD              | X-Ray Diffraction                                                              |

|                  |                                                                                |

# List of symbols

| At%               | Atomic percentage                    |

|-------------------|--------------------------------------|

| α                 | Attenuation coefficient              |

| Z <sub>C</sub>    | Characteristic impedance             |

| کے                | Correlation length                   |

| $ ho_{eff}$       | Effective resistivity                |

| Н                 | Hardness                             |

| ρ                 | Nominal resistivity                  |

| 3                 | Permittivity                         |

| Υsi               | Poisson's ratio                      |

| Р                 | Porosity                             |

| Р                 | Power spectral density               |

| Q                 | Quality factor                       |

| E <sub>reff</sub> | Relative effective permittivity      |

| σ (r)             | RMS roughness                        |

| σ                 | Stress                               |

| t <sub>PSi</sub>  | Thickness of porous silicon film     |

| t <sub>Si</sub>   | Thickness of silicon                 |

| $\mathcal{E}_0$   | Vacuum permittivity                  |

| Ε                 | Young's modulus                      |

| $E_{Si}$          | Young's Modulus of silicon substrate |

| Wt %              | Weight percentage                    |

| W       | Signal line Width               |

|---------|---------------------------------|

| S       | Signal-to-ground line distance  |

| $W_{g}$ | Ground-line-width               |

| $f_e$   | Dielectric relaxation frequency |

# **General Introduction**

#### **GENERAL INTRODUCTION**

At the dawn of 2020 the deployment of Internet of Thing (*IoT*) will become a reality. The concretization of IoTis unsurprisingly based on the concept of sensing network in which the sensing nodes (SN) will attract major interest towards the success of this challenge. A massive production of these SNs will emerge, and industrials will need to tradeoff between efficiency and cost to keep the competiveness of their products. In fact, to accomplish this tradeoff, a suitable choice of the components should be performed, the use of emergent active devices is highly recommended [1], and the quality factor of passive components should be accounted for [2]. One of the most important aspects impacting the performance of these components is the good choice of the substrate on which the SN is integrated. Indeed, bulk silicon is the most widely used substrate for the integrated circuits in the semiconductor industry. However, due to its high electrical conductivity and high-frequency losses, bulk silicon substrate suffers from significant losses at high frequencies which drastically reduce the RF performance of passive and active devices [2]. This degradation becomes more severe at millimeter-wave (mm-wave) frequencies.

In addition, the growing trend in mm-wave design is to go toward realizing fully integrated Front-end. Therefore, the integration of both passive and active analog circuits on the same chip with the digital part becomes inescapable. High isolation between different circuits lying on the same substrate should be considered, thus, the cross-talk must be reduced. Thus, substrates with high resistivity and low permittivity should be utilized.

By observing the current trends of microelectronics industry we can note the convergence toward the integration of RF circuit on SOI (Silicon on Insulator) especially with the introduction of trap-rich substrates. Indeed, ICTEAM laboratory at UCL in Belgium has proved an expertise in this area since they have proposed trap-rich substrate, which has been already adopted by industrials, for instance, SOITEC. Nonetheless, it is pertinent to report the care of the scientific community about the suitability of trap-rich for the integration of mm-wave circuits.

For the above reasons, and to continue on the same scope, we tried over the current work to replace the trap-rich substrate by the porous silicon substrate. We believe that the porous silicon is adve rtised as the good candidate thanks to its low cost and short process and it constitutes suitable alternative to trap-rich.

Various Si-based substrates, compatible with Silicon-on-Insulator (SOI) CMOS process, have been proposed to overcome the problem of performance degradation such as High Resistivity SOI (HR-SOI), Trap-Rich Silicon (TR-Si)[**3**–7] as well as nanocrystalline porous silicon which is a very promising alternative to bulk silicon substrates for the fabrication of low cost RF circuits [**8**]. Porous Si exhibits low permittivity, whose value depends on the porosity between those of air ( $\varepsilon_r = 1$ ) and that of silicon ( $\varepsilon_r = 11.7$ ) [**9**]. It can be fabricated from aSi wafer by electrochemical dissolution of bulk crystalline silicon. The main advantages of PSi are, its very low cost, and its CMOS process compatibility enabling the integration of both passive and active devices on the same substrate, and thus the development of a System-on-Chip (SoC). Furthermore, most investigated porous silicon substrates for RF applications are mesoporous made from n-type [**9**] and p+-type doped silicon owning a nominal resistivity lower than 20 mΩcm [**8**–14]. In fact, many PSi-based materials were found suitable for a wide range of integrated circuits with high performance, as it has been demonstrated in previous studies [**15** – **18**].

Actually, the integration of mm-wave circuits in porous silicon has been already investigated through various works, as we can see over the references cited in this thesis. However, the research on this topic remains and the researchers continue to enhance the quality of the proposed porous silicon. In this context, we aimed to propose improved porous silicon substrate compared with those presented in the literature.

The foreseen objective is to optimize all parameters, in order to present high quality porous silicon substrate especially when mm-wave applications are accounted for. By considering these applications, the proposed porous silicon should own pores size less than 5 nm[19], anodized layers with high uniformity and sufficiently spongy structure, all of these, to reach high insulating properties and low permittivity thus high quality factor (see Table 1).

| Substrate | Bulk<br>thickness<br>(µm) | Nominal<br>resistivity<br>(Ωcm) | Porous<br>thickness<br>(µm) | Porosity<br>and pore<br>diameter | Oxide<br>thickness<br>(nm) | α<br>(dB/mm) | Q@26/60GHz | Fabrication<br>cost<br>estimation |

|-----------|---------------------------|---------------------------------|-----------------------------|----------------------------------|----------------------------|--------------|------------|-----------------------------------|

| Std       | $381\pm20$                | 1 - 10                          |                             |                                  | 500                        | 3.8          | 2.1/4.9    | High                              |

| HR        | $725\pm25$                | >4k                             |                             |                                  | 500                        | 1.6          | 4.5/10.5   | High                              |

| TR        | 725 ± 25                  | >10k                            |                             |                                  | 500                        | 0.35         | 20.6/47.5  | High                              |

| PSi-S     | 381±20                    | 1 - 10                          | 50                          | 65%<br>< 5 nm                    | 500                        | 0.18         | 25.2/58.3  | Low                               |

| PSi-M     | 381±20                    | 5 - 20 m                        | 50                          | 50%<br>~ 12 nm                   | 500                        | 0.34         | 16.0/36.9  | Low                               |

Table 1. Substrates characteristics

Finally, the reached characteristics besides the low cost make the proposed porous silicon original compared with those already published in previous work. Moreover, to emphasize the high quality of the realized substrate, as concept proof, mm-wave filters have been integrated on, while they are usually based on 0.18-µm and 0.13-µm CMOS technologies. As we have observed over the presented results, a successful reduction in insertion loss has been achieved. Also, to the best of author knowledge, this is the first mm-wave bandpass filter integrated in PSi substrate.

Consequently, to summarize the originality of our work four main aspects should be considered. First, the low cost development compared with generally used process for the integration of mm-wave circuits. Second, the low complexity process. Third, the new variant of porous silicon having high insulating properties and high quality factor as depicted in Table 1. Forth, the performed high temperature analysis showed the reliability of the proposed PSi.

The scope of this work isto investigate RF performances of the Si-based substrates (Std, HR, TR and PSi) and their suitability to co-integrate on-chip passive elements and active devices for RF and system-on-chip applications.

This thesis is organized as follows:

- Chapter 1, brings together the substrates technologies for RF applications, and introduces porous silicon as substrate with some of his applications area. In this thesis five types of Si-based substrates are compared.

- 2. Chapter 2is dedicated to elaboration and physical characterization of porous silicon PSi for RF application

- 3. In chapter 3, we present the integration of CPW lines on PSi substrate using a low complexity fabrication process (see Annex A), with their wide band characterization, and we have observed their behavior at high temperature up to 175°C after their submission to temperature variation and compared with their respective counterpart TR, HR and Std substrates.

- 4. In chapter 4, we propose a demonstrator on Si based substrates, a bandpass filter is designed around the frequency of 27 GHz and fabricated on top of Std, HR, TR and PSi substrates. A good agreement between simulations and measurements results is obtained. We have compared the performance of the PSi-based mm-wave filter to relevant works tied to mm-wave filters fabricated in various CMOS technologies.in this context, we have submitted the filter to temperature variation up to 175°C, the filter response remains almost unchanged even at high temperature.

- 5. A general conclusion of this thesis is presented in chapter 5 that highlight the efficiency of PSi substrate. Therefore, the proposed porous silicon substrate offers low cost alternative to 0.18-mm CMOS technology and trap rich technology, especially when mm-wave circuit design is accounted for.

# **Chapter 1**

# SUBSTRATES TECHNOLOGIES FOR RF APPLICATIONS

#### 1.1 Introduction

In the fields of microelectronics, photonics, optoelectronics, radiofrequency (RF) applications or high power devices, the selection of the appropriate semiconductor substrate technology is a critical issue. Indeed, suitable selection can provide a capital advantage to achieve high performance. RF and microwave systems, require specific back-end-of-line to fulfill their needs, substrates such as standard silicon or high resistivity (HR) silicon have been widely used. However, the increasing expansion of RF applications, such as 5G telecommunication, high data rate WPAN (Wireless Personal area Network), and *IoT* (Internet of things), leads to new requirements for the integration of digital and analog devices on the same chip like, low loss, low cost and manufacturing easiness; these constraints become more important especially when frequencies higher than 20 GHz are targeted.

Thus, before going toward the treated topic by this thesis, it is appropriate to review the commonly used substrates in the industry of microelectronics.

#### **1.2** Description of substrates for RF applications

#### **1.2.1 Standard silicon substrate (Std)**

From a physical and mechanical point of view, a classical solid substrate is made up of silicon, the maturity of silicon technologies and the progress of MOS transistors in the microwave domain, explains the success of silicon compared to III-V technologies [20-23].

Since the 80s, CMOS technology has become the dominant technology for integrated circuits. The manufacture of RF components involves the use of substrates favoring weak

energy losses. These losses are of two types. Capacitive losses by coupling with substrate and eddy current losses induced in the substrate.

#### **1.2.2 High Resistivity Silicon-on-Insulator substrate (HR-SOI)**

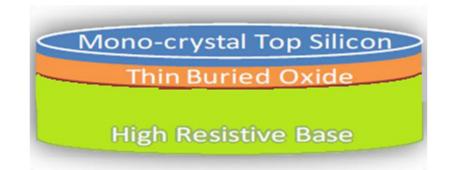

RF SOI is composed of a top layer a thin film of monocrystalline silicon, an isolation layer as an oxide and a high resistive substrate as the handle substrate. Although, High-resistivity substrates (HR-Si, HR-SOI) (Fig 1.1) are compatible with the processes and manufacturing CMOS circuits [24-25], they still suffer from crosstalk and parasitic surface charges (PSC). In the RF SOI products, the oxide of the insulator BOX still contains positive charges, those charges create a parasitic surface conduction at the interface between the BOX and the high-resistivity handle substrate [7,26]. A new substrate that do not suffer as much from the parasitic effects and crosstalk is the ideal for RF applications, one could think of about a glass or quartz substrates. However, their high thermal resistance can lead to self-heating phenomena [27], we are going to discover this new substrate in the next section.

Figure 1.1 High Resistivity wafer

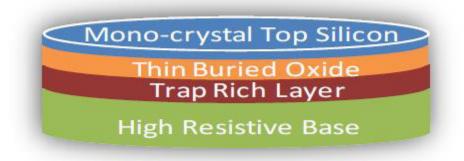

#### 1.2.3 Trap-rich high resistivity substrate TR-Si

The proposed substrate resistivity can reach several k $\Omega$ .cm. This high-resistivity characteristic, translates to very low RF insertion loss along coplanar waveguide (CPW) transmission lines and purely capacitive crosstalk similar to quartz substrate [28]. This means get around the parasitic effect and crosstalk.

J-P. Raskin and coworkers **[29-31]** have invented a technic consisting of adding a rich trap-rich poly silicon layer underneath the buried oxide as shown in Figure 1.2, it is the best

method for reducing the surface parasitic effect (PSC) which degrades the high resistivity properties of HR-Si substrates, thus increasing their losses [32].

Figure 1.2 Trap-rich wafer

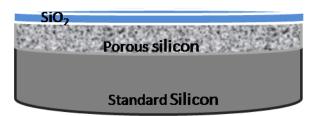

#### 1.2.4 Porous silicon substrate PSi

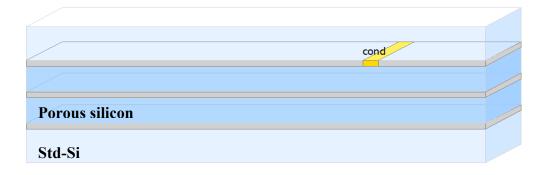

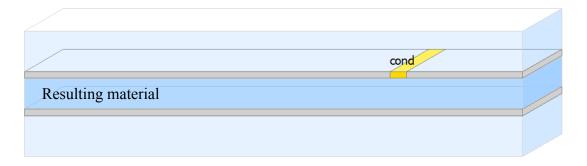

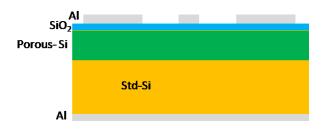

A new promising substrate that could be the solution to the integration problem may be the porous silicon (PSi). As discussed in [33], this material can be locally formed on the Si plate by electrochemical dissolution of solid crystalline Si [34]. Figure 1.3 represent the porous silicon substrate PSi with an SiO<sub>2</sub> layer.

Figure 1.3 Porous Silicon wafer

The properties of PSi are highly dependent and can be driven by the electrochemical conditions used during anodization. For RF circuits, the desirable characteristics are low dielectric constant and low loss, which will be explained later in this thesis.

The high permittivity of the bulk Si increases the crosstalk between the lines, decreases the antenna efficiency and the maximum operating frequency in the inductors. This could lead to the conclusion that PSi should have as high a porosity as possible to approach air permittivity ( $\varepsilon_r$ = 1), but the situation is not so simple since the increase of porosity, increases fragility substrate.

Different morphologies lead to different degrees of interconnection in the substrate. More oriented structures leave an electric path for the eddy currents, leading to the higher polarization loss. However, the random distribution of pores in moderately propagated structures has shown promising results due to the reduction of eddy currents in the substrate [**35**]. Another factor that has an impact on the parameters of interest is the annealing step. During annealing, the thin layer of oxide on the walls of the pores grows in a controlled manner. The PSi may be fully oxidized, the oxide has fixed charges, which can polarize the surface and create a highly conductive layer all along the boundary of the pores that are the walls of bulk silicon.

In view of all the above, it is essential to carefully select the morphology of the porous silicon layer PSi so as to optimize the RF parameters if the PSi is to be used as an RF substrate.

#### **1.3** The Physics of porous silicon

#### **1.3.1 Introduction**

Porous silicon is a well-known material produced by anodization of silicon in hydrofluoric acid (HF)-based electrolyte. A number of factors determine the pore morphology. Though each of types of pores (micro, meso, and macrospores) has been extensively investigated and can be produced under a variety of conditions [35-37]. Other technological solutions have also been proposed using silicon nano-pillar arrays to create a vertically oriented field effect transistor for the decoupling of device density from channel length [38-40].

The ability to insert a thick porous silicon layer on a low resistivity Si wafer, on which the RF devices can be integrated, enabled the elaboration of insulating/semiconductor mixed substrates [8-41]. In fact, this material exhibits low permittivity, whose value depends on the porosity between those of air ( $\varepsilon_r = 1$ ) and silicon ( $\varepsilon_r = 11.7$ ) [9]. Moreover, most porous silicon substrates studied in the literature for RF applications are mesoporous and made from p-type silicon of resistivity below 10m $\Omega$ .cm. The materials are generally of moderate thicknesses (10 to 200µm) with porosities of 70 to 80% [42-44]. Furthermore, porous silicon on n-type substrates in the field of radio frequencies has also been demonstrated in terms of electrical insulation while maintaining low mechanical stresses in the substrate and good thermal conduction [10]. Additionally, the ease and low cost of obtaining porous Si and its particular electrical, optical and thermal properties make this material a field of development for microsystems. In this context, it appears possible to combine the use of several of these properties in a single integrated micro device. As of the use of its dielectric properties, porous silicon implementation has been most often made in the form of thick insulating boxes mainly in the field of radio frequencies **[45-46]**.

#### **1.3.2 History of porous silicon PSi**

Porous silicon (PSi) is a structural form of silicon chemical element. It has a large surface to volume ratio due to a large number of micro-, meso- and macropores. In most PSisamples, these pores are mainly oriented in the crystallographic direction [47], and are carried out in the platelet by electrochemical dissolution, mainly using aqueous or ethanoic solutions of hydrofluoric acid (HF).

The first realization of a layer of porous silicon was made by A. Uhlir in 1956 [48] during his work on electropolishing. This discovery initially aroused interest in the production of SOI (Silicon On Insulator) substrate by increasing the dielectric property of the porous by its oxidation [49-50]. The following was L.T.Canham's by discovering the high luminescence of porous silicon at ambient temperature[51], that this material was devoted with high interest and became the main research object [52-55], during coming years. Nonetheless, PSi continues its investigation and new ideas are explored, from biosensors to RF applications.

#### 1.3.3 Nanostructuring and morphology

The porous silicon has a nanostructured form of monocrystalline silicon, its degree of anodization is defined by the rate of layer formation and porosity, with the pore morphology which depends on the type of wafer and the resistivity, the applied current density as well as process duration, and the composition of the electrolyte (HF concentration, with or without additives). Its morphology is usually classified into three categories according to the diameter of the silicon nanocrystallites that make it up. Their size can range from a few nanometers to a few micrometers, so we will speak of silicon [**56**]:

- micro-porous: crystallites between 1 and 5 nm

- meso-porous: crystallites between 5 and 50 nm

• macro-porous: crystallites greater than 50 nm

For all the morphologies, the crystallites are separated by pores, which are nearly the same size as the crystallites obtained. All three kinds of pore structures have found their own applications

#### **1.3.4 Gravimetric measurement**

In addition to its structural morphology, porous silicon is characterized by its porosity. For the portion of monocrystalline silicon concerned by the porosification, this represents the proportion of material removed relative to the initial fraction, i.e. the ratio of the volume of created vacuum over the volume of initial silicon. Moreover, in its most general sense, a "pore" is an engraving pit whose depth exceeds its width [57].

Porosity is most commonly determined by gravimetric measurement and it is calculated by the following formula [58]:

$$P(\%) = \frac{m_1 - m_2}{m_1 - m_3} \tag{2.1}$$

Where  $m_1$  (g) is the sample weight before anodization,  $m_2$  (g)sample weight just after anodization and  $m_3$ (g) is the sample weight after dissolution of the complete PSi layer. Complete removal of the porous silicon is easily accomplished by chemical dissolution in concentrated potassium (KOH) solution (34%) at room temperature with the use of ultrasound for a few minutes. From these measured masses, it is possible to determine the thickness L of the porous layer according to the following formula:

$$L = \frac{m_1 - m_3}{S \cdot \rho} \tag{2.2}$$

Where  $\rho$  (g.cm<sup>-3</sup>) is the density of bulk silicon and S(cm<sup>-2</sup>) is the area of the wafer exposed to HF during anodization [57].

It should be noted that, when a material is annealed, some pore openings might close, resulting in closed porosity. For gravimetric measurements, if a probe molecule size is smaller than the pore size, then the pore can accommodate the probe molecule and thus the porosity can be measured. Porosity is a macroscopic parameter that does not completely describe the porous material. In order to gain a complete understanding of all the

characteristics of a porous material, it is necessary to consider the morphology of the material as well. It is difficult to systematically characterize the morphology of a PSi layer.

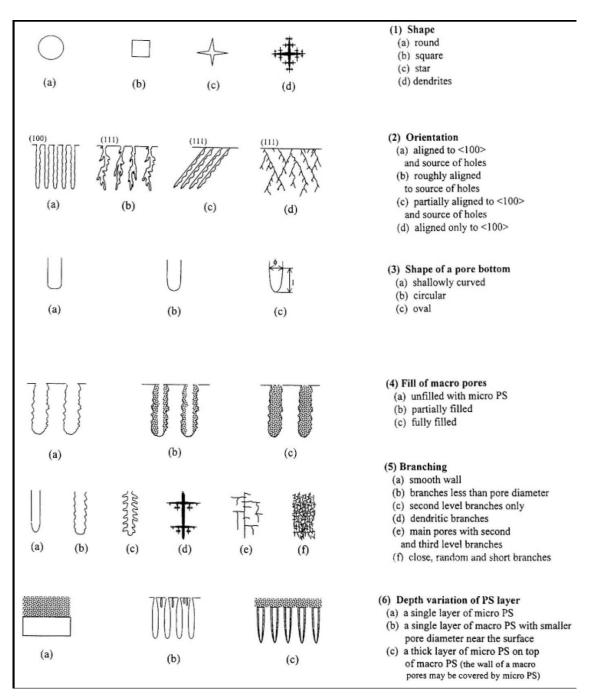

Qualitatively, besides porosity, there is a distinction between the following six parameters: pore shape, pore orientation, shape of the bottom of a pore, fill of macropores, branching and depth variation as shown in Fig. 2.1 [59].

Figure 1.4 Morphological features of Porous silicon [59]

#### 1.3.5 Thickness layers

The anodization time is particularly the most important parameter of which the thickness of PSi layer depend. Higher duration lead to thicker PSi layer [35].

Scanning electron microscopy (SEM) measurement is the common technique to measure the layer thickness of PSi material, from this later the etching rates is calculated as shown in equation (2.3).

$$v_{PSi} = \frac{d}{t} \tag{2.3}$$

Where  $v_{PSi}(\mu m/min)$  is the etching rate of PSi layer,  $d(\mu m)$  is the layer thickness and t(min) is the etching time.

#### **1.3.6 Thermal oxidation of porous silicon**

Micro- and meso-PSi can be partly oxidized, by chemical or electrochemical methods, however, these last are not compatible with the microelectronics fabrication methods due to potential contamination issues, but they may offer a good choice for other applications. Many oxidation methods exist, for instance, anodic oxidation in non-fluoride electrolyte, chemical oxidation using HNO<sub>3</sub>,O<sub>3</sub>, H<sub>2</sub>O<sub>2</sub>, aging in ambient conditions, thermal oxidation in wet and dry O<sub>2</sub>, rapid thermal annealing and nitridization at different temperatures [**60**].

Thermal oxidation is needed to fully oxidize the PSi layer and used in the microelectronic industry to produce high-quality oxides on flat silicon. The difference between these silicon structures is the extent of the oxidation.

A preliminary annealing at low temperatures (up to 300°C) improves the parameters of oxidized PSi. It has been shown that it is not desirable to anneal as-prepared PSi at temperatures that exceed 400°C because it could lead to a drastic restructuring of the PSi layer. Even at low temperatures, surface migration of silicon atoms leads tothe coalescence of pores due to the large surface area [61]. The desorption of dihydride (Si - H<sub>2</sub>) occurs at 300°C and Si - H bonds seem to be stable at this temperature upto around 400°C at which point hydrogen starts to desorb [62]. Therefore, pre-oxidation of PSi at low temperatures in the range of 300°C creates anoxide layer along the pore walls, which prevents the restructuring of the sample. Thermal oxidation of PSi layer allows increasing insulation of the substrate, to ensure high resistivity and low permittivity of this later in RF application. Furthermore, the pores size degrade the properties of the substrate when they are relatively small (a few nm) due to the tunneling effect between the adjacent crystallites. A pre-oxidation in either  $O_2$  or  $N_2$ environment is necessary, it's stabilizes the structure and creates a native oxide in a controlled fashion [16].

#### **1.3.7** Applications of porous silicon

According to the literature **[63]**, the applications of porous silicon are grouped into twelve domains: electronics, optoelectronics, optics, diagnostics, energy conversion, catalysis, filtration, adsorbents, medicine, food, cosmetics and consumer care.

In our work, we are particularly interested in the microelectronic field, in terms of the use of the dielectric properties of porous silicon, its implementation was most often done in the form of thick insulating boxes mainly in the field of radio frequencies [54],[56], [64]. Researchers have demonstrated positive results in reducing losses, improving quality factors for passive inductance devices and abilities on porous silicon [65].

While the SOI silicon substrate offers the possibility of combining high and low resistivity of the materials in a single circuit, one of the main advantages of a porous silicon approach is the possibility of locally defining high resistivity regions in a substrate essentially low resistivity [66].

Recent work on localized porous silicon has been carried out by the team of A. G. Nassiopoulou [8], [12], [33], [67], and that of G. Gauthier [13], [18], [44], [68].

Figure 1.5 Porous silicon technology for RF Integrated Circuit Applications [65-66]

#### 1.4 Conclusion

A brief description thus characteristics, advantages and disadvantages of substrates (Standard bulk silicon (Std), High Resistivity (HR), Trap-rich high resistivity (TR) and Porous silicon (PSi)) used in the industry of microelectronics was presented in this first part. The focus is on porous silicon substrate, thanks to its lower permittivity, high resistivity, its morphology and its nano-structuring, which leads it suitability to co-integrate on-chip passive elements and active devices for RF and system-on-chip applications.

The ease of implementation of the electrochemical production process that we will study in Chapter 2, makes porous silicon, a relatively easy material to integrate into the technology related to microelectronics, and at the same time presents a low cost process.

# Chapter 2

# ELABORATION AND PHYSICAL CHARACTERIZATION OF PSI FOR RF APPLICATIONS

#### 2.1 Introduction

The objective of the work is first to explore the influence of the nanostructure, nanomechanical properties, stress, and roughness of the porous silicon layer through different characterizations methods, then, the relationships between the analyzed structure of the Porous silicon layer versus its electronic properties, as it has been demonstrated in our work[16]. The ease and low cost of obtaining porous silicon and the multitude of its applicable properties make this material a field of radio frequency devices development.

#### 2.2 Elaboration of porous silicon

#### 2.2.1 Experimental setup for the electrochemical etching

Electrochemical etching in a hydrofluoric acid (HF) solution is a well known technique for making different silicon structures for a wide range of applications. The advantage of this method is its simplicity and ability to anodize silicon-on-insulator structures, the simplest way to realize an electrochemical cell is to immerse two connected electrodes within an electrolyte. One electrode supplies electrons to the solution (the cathode), where the reduction takes place. The other one removes electrons from the solution (the anode), where the oxidation is occurring. The current supply is provided by the current source which is driven by a potentiostat. The whole system is ultimately controlled by a computer. There is more than one way to organize an electrochemistry experimental setup for PSi, and various methods have been described in the literature, such as, the immersion cell[69], the O-Ring cell [35], the double cell [70], cell with electrolyte circulation [60], etc.

The design of the anodizing tool depends largely on the nature of the application, the type of layers and the flexibility of the required process, the proposed flow and the degree of automation. The electrolytes used for the anodic etching process are based on a mixture of hydrofluoric acid (HF) and ethanol. Silicon wafers (100) of p-type with different resistivity (5-20 m $\Omega$ -cm), (1-10  $\Omega$ -cm) and (10-25  $\Omega$ -cm) were used as substrates for anodizing the porous silicon, an Ohm contact was made through the deposition of a 200 nm layer of aluminum behind the wafers. Adhesive tape was used to mask the entire substrate with the exception of the area where the anodizing and plating were performed as shown in Figure 2.1. The sample was mounted in an electrochemical cell connected to a potentiostat -galvanostat PAR 362. In the case of our application, the surface of the silicon wafer required pre-cleaning before the anodization, to remove the native oxide film, which cover the surface wafer. The oxide layer will be removed when the wafer is immersed in two successive cleaning baths of the solution (H<sub>2</sub>SO<sub>4</sub> + H<sub>2</sub>O<sub>2</sub>) and then in the HF. Distinct morphologies of meso and micropores were obtained as a function of doping of the Si wafer as well as by the change of the electrochemical parameters.

Figure 2.1 Electrochemical cell used for the anodization

The choice of cell materials depends on the targeted electrolyte. Since HF based electrolytes are widely used in the electrochemistry of silicon, materials resistant to HF must be used PVC(polyvinyl chloride), PP (Polypropylene), PTFE (polytetrafluoroethylene) and

PVdF (Polyvinylidene fluoride) are all used, with PVC being superior because it is inexpensive, inert in HF and it has good mechanical performance [35].

#### 2.2.2 **Porous silicon anodization parameters**

For the manufacture of a microporous layer structure on Si substrate with resistivity of (1-10  $\Omega$ .cm), a HF : ethanol based electrolyte and a current density of 10 mA.cm<sup>-2</sup>were applied during the etching process to obtain a porous thickness of 2 µm to 200 µm related to an etching time ranging from 250 s to 24000 s, respectively. All specimens were made in the dark on an electrochemical etching platform inside a fume hood at room temperature (18 ± 1°C). Finally, the samples were rinsed in deionized water and dried with a stream of nitrogen.

The relevant parameters which influence the formation process are summarized as fellow:

- Substrate doping

- Wafer type and resistivity;

- Current density;

- HF concentration in electrolyte;

- The used Solvent; lowering the surface tension with, for example, the use of ethanol, allows hydrophobic porous silicon to be more wet enabling higher homogeneity;

- Etching time;

- Temperature and ambient humidity;

- Drying conditions

Once a porous layer is formed, no more electrochemical etching occurs in that layer. This creates the possibility to change porosity as a function of depth.

# 2.3 Morphological characterization of porous silicon

The condition to produce high performance RF devices is always related to the surface state (structure) of substrate. Then, it is important to study its structural and mechanical properties before and during the different steps of the post-anodization process of silicon. Consequently, an important number of articles are devoted to the mechanical properties of Si bulk substrate [71-73]. In the other hand, many works concerning the morphology and structural properties of Porous silicon have been performed [19], [74-75].

The stress and roughness in porous Si could affect the integration of porous Si devices in microelectronic integrated circuits based on silicon.We investigate the nanomechanical properties and the structure analysis of the porous silicon layer with different thicknesses formed on p-type Si substrate with two resistivities. The formed PSi layers are characterized by Scanning electron microscopy (SEM), Atomic force microscopy (AFM), and Nanoindentation.

#### 2.3.1 Scanning Electron Microscopy (SEM) analysis

For any application of the porous Si a morphological characterization is of prime, a field emission scanning electron microscope (FE-SEM, GEMINI Ultra 55 Zeis) under 3 keV electron acceleration voltage is used in order to measure: the thickness of the porous silicon, the size of the pores and the crystallites. The sample PSi-M with 50  $\mu$ m thickness of a mesoporous layer is obtained after anodization of p-type Si ( $\rho$ =5-20 mΩ.cm)in (50%) HF: ethanol (1:1), at current density of 75mA/cm<sup>2</sup> during 40 min. Figure 3.2 shows the cross-sectional and top view SEM images of the mesoporous layer with pores varying from 10 to 12 nm. On the other hand, standard p-type ( $\rho$  = 1-10 Ωcm) sample (PSi-S) is exposed to an electrolyte based on (2:1) mixture of (50%) HF and ethanol, and the anodization is conductedat a current density of 10 mA/cm<sup>2</sup> during 100 min for 50 µm thickness of porous layer.A spongy structure with pores can be varied depending on the time period of the electrochemical process. In the present work, the thickness of the porous silicon layer is about 50 µm for the two types of wafers doping.

Figure 2.2 Cross-sectional SEM image (left) and top view (right) of mesopores obtained after anodization of highly doped P-type Si ( $\rho$ = 5-20 m $\Omega$ .cm)

Figure 2.3 Cross-sectional SEM image (left) and top view (right) of mesopores obtained after anodization of standard P-type Si( $\rho = 1-10\Omega$ .cm)

The microporous silicon layer after oxidation is characterized by Energy Dispersive Spectroscopy (EDS), this later is a chemical microanalysis technic which is used in conjunction with scanning electron microscopy (SEM)

The recorded energy dispersive spectroscopy analysis spectrum reveals the presence of oxygen after oxidation through the whole layer thickness and into the filled pores indicating that the sample contains silicon and oxygen. The average compositions of the anodization and oxidation have been estimated quantitatively with values of 84% for Si and 16% for O within the anodized layer as shown in Figure2.4.

Figure 2.4 Energy dispersive spectroscopy (EDS) spectrum of porous silicon layer after oxidation

### 2.3.2 Porosity

A mesoporous layer structure of the PSi-M substrate is obtained with an estimated porosity of 50 % for PSi 50µm thickness, and about 44 % for the 10µm PSi thickness. The variation in porosity with thickness is related to the chemical dissolution of the porous material during its formation. According to results of R. Herino et *al*[76], who studied porosity as function of the thickness, their work summarizes that the porosity and pore sizes increase with an increase in forming current density or a decrease in hydrofluoric acid concentration. One can conclude that for PSi-M substrate the porosity increase with the increase of the resistivity, as it shown in (Fig. 2.5).

On the other hand, the same observation is made for PSi-S substrate, where the porosity increases with thickness until reaching saturation, which seems to be the highest porosity of 65% for 50µm thickness as it is shown in Fig. 2.6. Thereafter, the PSi develops cracks and small pores start growing. All results corresponding to the two nominal resistivities are summarized in Table 2.1.

Figure 2.5 Porosity vs resistivity for 50µm of porous silicon

Figure 2.6 Variation of porosity with thickness for PSi-S

| Nominal resistivity | Porous thickness | Pore size | Porosity |

|---------------------|------------------|-----------|----------|

| (Ω.cm)              | (μm)             | (nm)      | (%)      |

| 0.005- 0.02         | 50               | 10 - 12.5 | ≈50      |

| 1-10                | 50               | 1 - 5     | ≥ 65     |

Table. 2.1 Comparison between two nominal resistivity

## 2.3.3 Atomic Force Microscopy(AFM)analysis

The porous silicon layer obtained after anodization and oxidation must have similar characteristics to that of monolithic silicon to withstand of a standard process in microelectronics (deposits, etching and high temperature annealing) until devices integration. In this context, the morphology, the roughness and the spectral analysis of the porous silicon layer were characterized by Atomic force microscopy (AFM Agilent 5500).

From atomic force microscopy image (Fig. 2.7), a change in the porous silicon structure is observed, for a PSi-S substrate (1-10  $\Omega$ .cm), the size of pores and crystallites increase with PSi thickness.

Figure 2.8 presents the superposition of power spectral density versus spatial frequency for different thicknesses of PSi,  $5\mu m$ ,  $10\mu m$ ,  $50\mu m$  and  $200\mu m$ . At the lower spatial frequency, a flat curve with a constant value is observed for all PSi thicknesses except for 200  $\mu m$  thickness a significant variation of the power spectral density is shown.

Figure 2.9 shows at small-scale, a roughness which is quite identical regardless the thickness of the PSi layer. However, at large-scale the roughness increases with the thickness of the PSi layer. The RMS (*Root Mean Square*) roughness becomes constant above 100 nm scan, this indicates, that is necessary to scan at least 100 nm to avoid losing information on the surface roughness.

RMS roughness and correlation length as a function of the thickness are extracted as it is shown in (Fig. 2.10). RMS is the root mean square average of the profile height deviations from the mean line, recorded within the evaluation length; the correlation length  $\xi$  is the typical distance between two different irregularities (or bumps) on the surface, which increases with increasing thickness of porous silicon. According to the Table 2.2, rough surface when values close to 1 indicate a smooth surface [75, 77]

From this results, we can conclude that the porous layer due to the electrochemical etching of silicon surface leads to an increase of the surface roughness, despite this, the roughness reach 0.9 nm for  $50\mu$ m, so the surface of PSi still smooth, it is 2.5 nm for  $200\mu$ m thickness of PSi. In the other hand the correlation length, remain fixed until  $50\mu$ m thickness of PSi. Therefore, one of the main benefits of the porous silicon substrate compared to the silicon is having a rougher surface with large specific surface.

Figure 2.7 AFM image of different thickness of PSi-S substrate (1-10Ω.cm)

Figure 2.8 Superposition of power spectral density vs spatial frequency

Figure 2.9 Superposition of RMS roughness vs length scale of (5µm, 10µm, 50µm and 200µm) thickness of PSi-S substrate

Figure 2.10 RMS roughness and correlation length vs thickness of PSi-S substrate

| PSi thickness (μm) | σ (nm) | ξ (nm) |

|--------------------|--------|--------|

| 5                  | 0.45   | 7.5    |

| 10                 | 0.65   | 7.5    |

| 50                 | 0.9    | 7.5    |

| 200                | 2.5    | 24     |

Table. 2.2 Roughness ( $\sigma$ ) and correlation length ( $\xi$ ) corresponding values of different thickness of PSi-S

Regarding to the previous results, the PSi-S 50  $\mu$ m seems have surface roughness less than 1 nm, for that we investigated two different resistivity for the same thickness of porous silicon. In the figures 2.11 the effect of substrate resistivity is highlighted by the surface morphology of PSi, where the substrate PSi-M present large pores size. Through the roughness of PSi-M, which is two times greater than that of PSi-S (Fig. 2.12) the PSi-S substrate, give better results comparing with the PSi-M. The SEM results are confirmed by the AFM analysis, the SEM and AFM are complementary analysis.

Figure 2.11 AFM image of PSi-S and PSi-M with the same thickness 50µm of porous silicon

# 2.4 Optical characterization of porous silicon

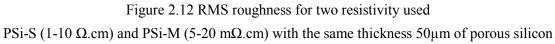

The Fourier Transform Infrared Spectroscopy (FTIR) measurements allow us to follow the evolution of the absorbance spectrum of oxygen versus time due to the oxidation of the samples. S. Gardelis, AG Nassiopoulou et *al* **[78]** used Transmission Electron Microscopy (TEM) and Fourier Transform Infrared Spectroscopy (FTIR) to characterize silicon nano-pores (1.5 - 7nm) after laser irradiation for photonic applications.

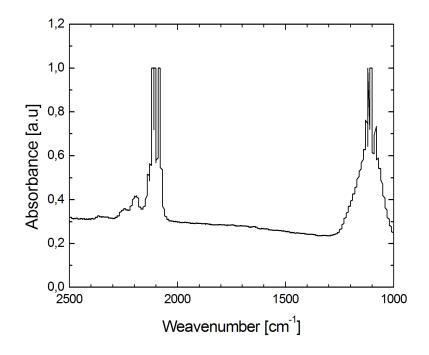

Thermo-Nicolet Nexus 670 Fourier transform infrared spectrometer was used to characterize the bonding properties of porous silicon layer. The infrared spectra were measured in absorbance mode and were referenced against a single silicon crystal sample. Figure 2.13 shows the IR spectra of PSi layer, it show a small peak at about 1100 cm<sup>-1</sup>, corresponding to the stretching vibration of Si-O bond(oxygen present in interstitial sites in the silicon crystal lattice). A periodicity is observed, which is due to interference phenomena in thin layers. Porous silicon is commonly highlighted by the stretching vibrations of Si-H, Si-H<sub>2</sub> and Si-H<sub>3</sub>, respectively, at 2087, 2110, and 2140 cm<sup>-1</sup>[**78-80**]. Furthermore, other modes have been observed such as scissor bending at 915cm<sup>-1</sup> of the Si-H<sub>2</sub> bond and at 626 cm<sup>-1</sup> from bending mode of the Si-H bond. The torsional and the rotation modes have also been observed at 665 cm<sup>-1</sup> and at 512 cm<sup>-1</sup>, respectively [**80**].

Figure 2.13 FTIR Spectrum of porous silicon layer before oxidation

Figure 2.14 FTIR Spectrum of porous silicon layer after oxidation