INSTRUMENTATION

# **VLSI SYSTEMS AND ARCHITECTURE** 2021-22 Lecture 7 **Hardware Flow Chart-Part-2** By Dr. Sanjay Vidhyadharan

ELECTRICAL

ELECTRONICS

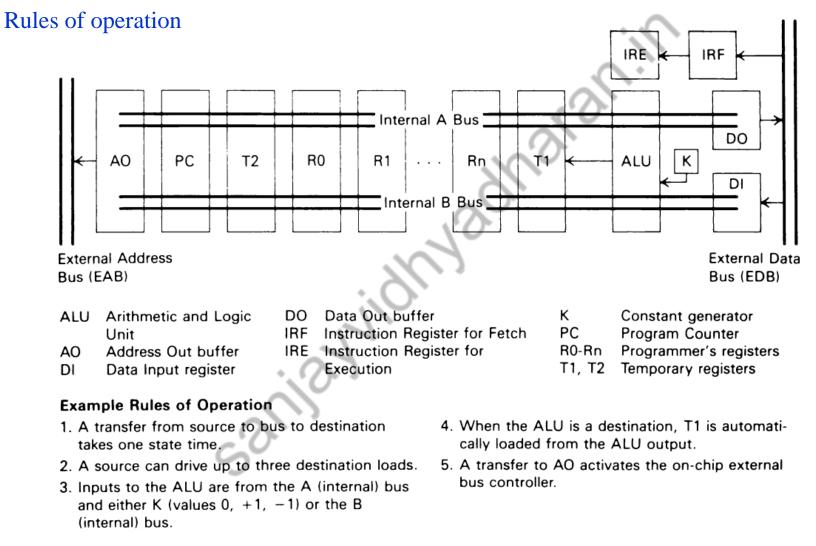

# **MIN execution unit block diagram**

#### 4/2/2022

#### **ELECTRONICS**

#### **Level 2 flowcharts**

Housekeeping tasks merged with the operation tasks to form level 2 flowcharts.

#### **Level 2 flowcharts**

4/2/2022

COMMUNICATION

#### **Level 2 flowcharts**

4/2/2022

#### **Feedback on Execution Unit Design**

Less than full use of the A and B buses in the resulting sequence would signal the need to improve the execution unit.

4/2/2022

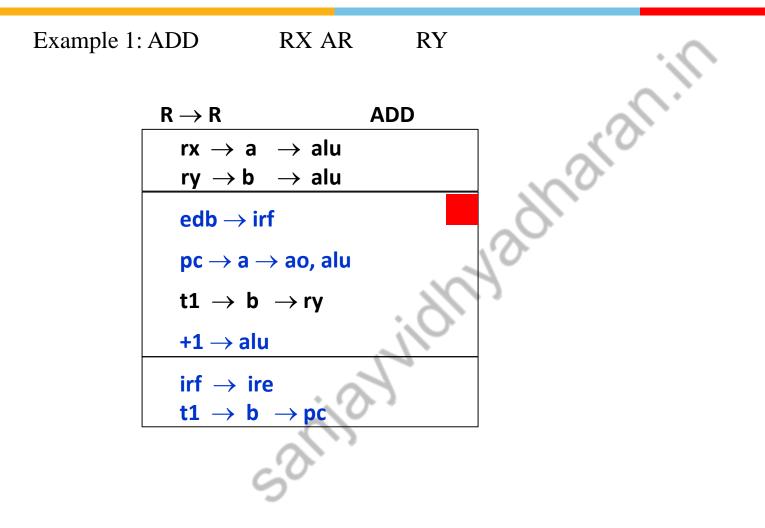

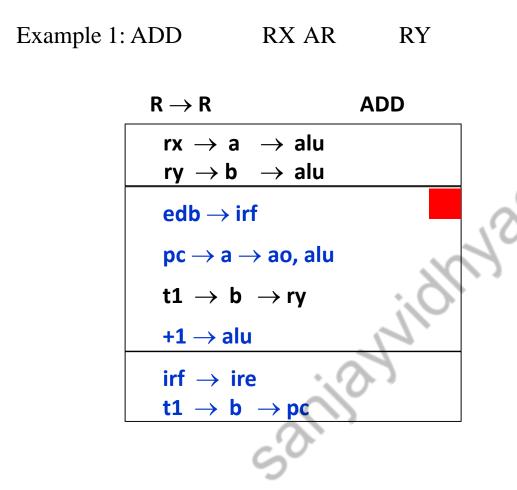

### **Feedback on Execution Unit Design**

ADD sequence for an execution unit in which Output transferred to only one location

Additional One Cycle is required.

# **Feedback on Controller Design**

4/2/2022

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

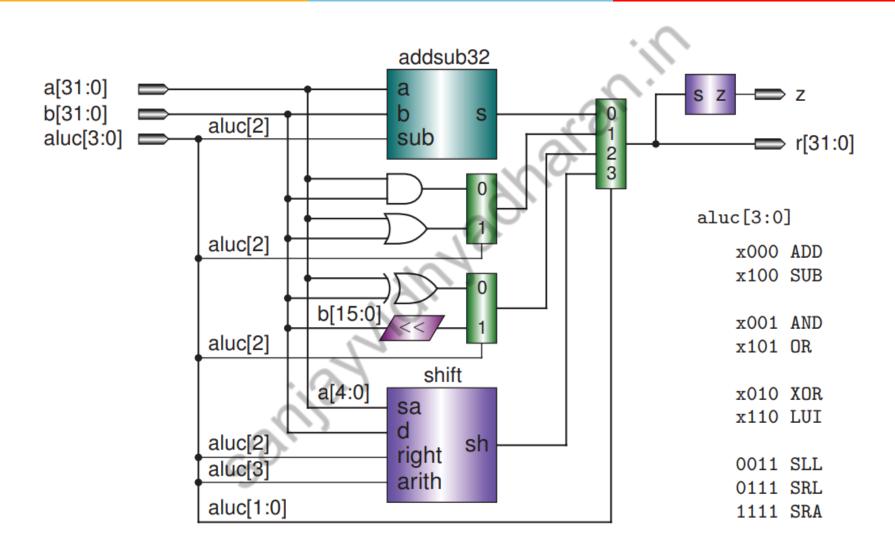

# **ALU Design**

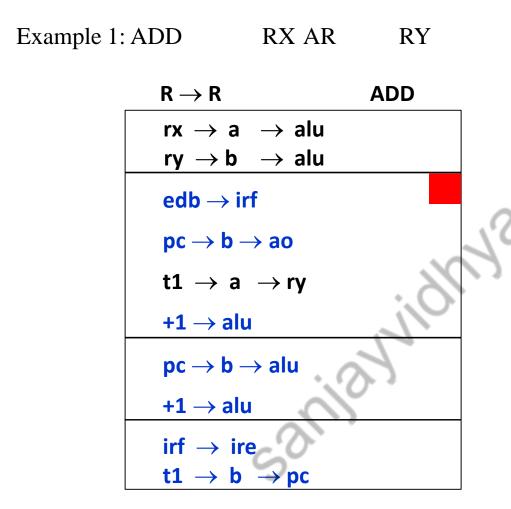

### **Feedback on Controller Design**

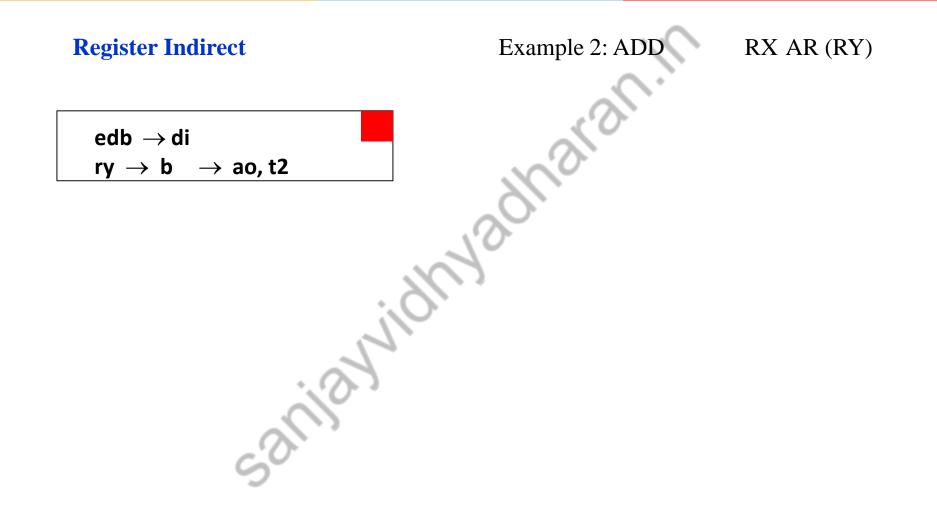

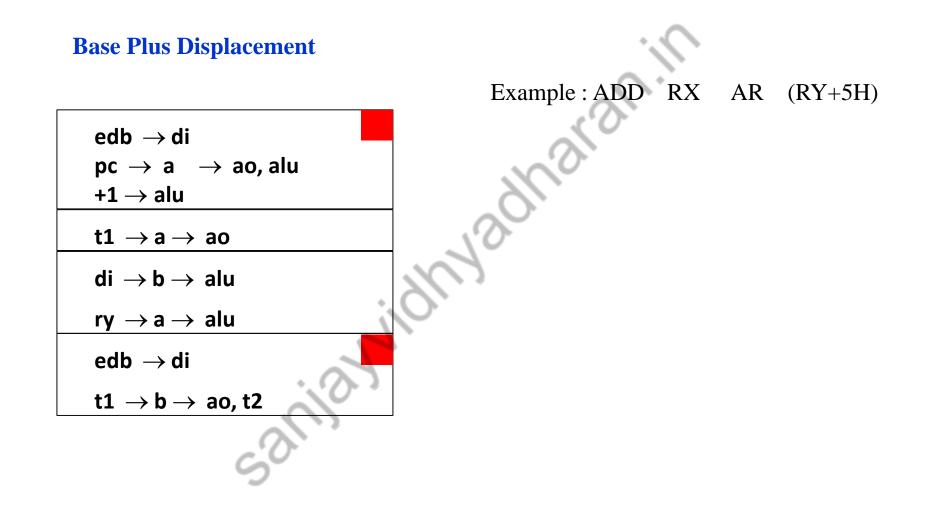

The combination of an address mode sequence and an execution sequence forms a control word sequence. If an instruction (such as a register-to-register ADD) does not need an address mode sequence, then the execution sequence and the control word sequence are the same.

4/2/2022

COMMUNICATION

### **Address Mode Sequences**

COMMUNICATION

4/2/2022

**ELECTRICAL**

**ELECTRONICS**

#### **Address Mode Sequences**

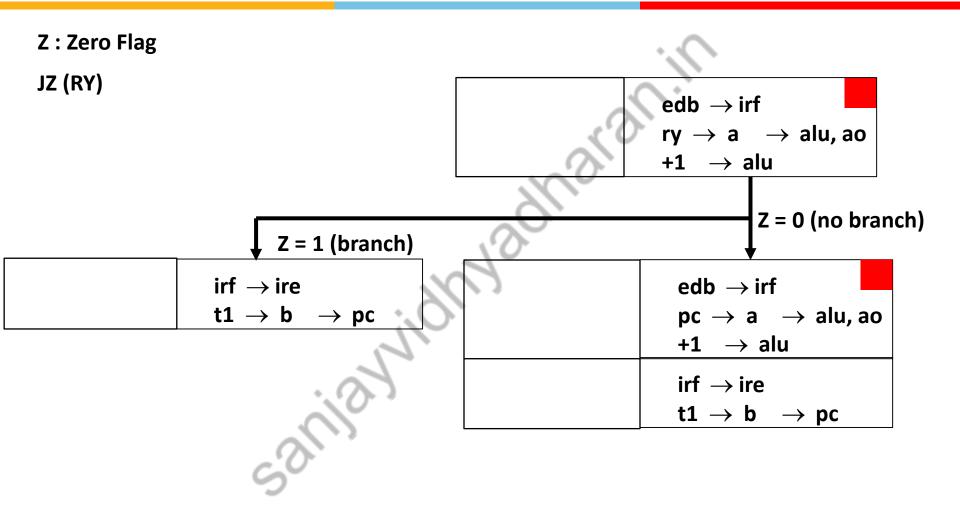

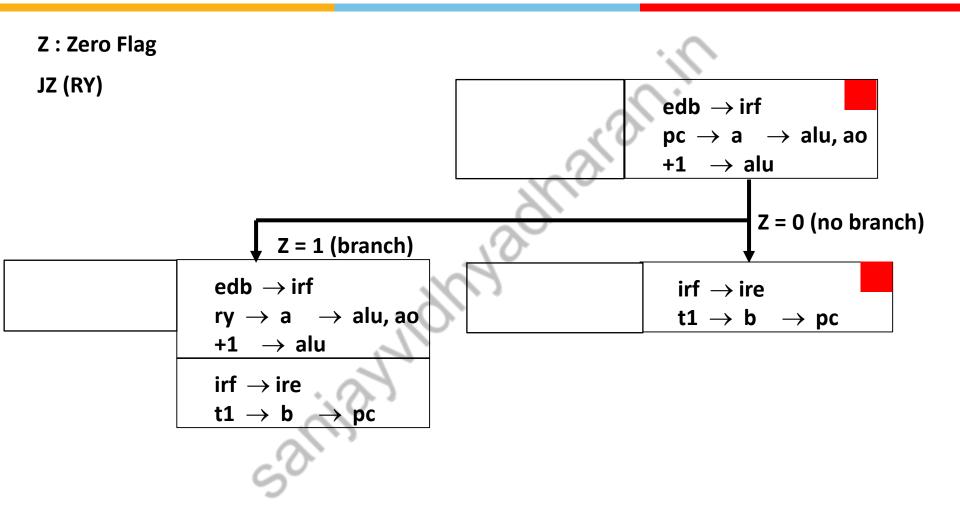

### **Branch Instruction**

4/2/2022

**ELECTRICAL**

**INSTRUMENTATION**

13

ELECTRONICS

### **Branch Instruction**

4/2/2022

ELECTRONICS

COMMUNICATION

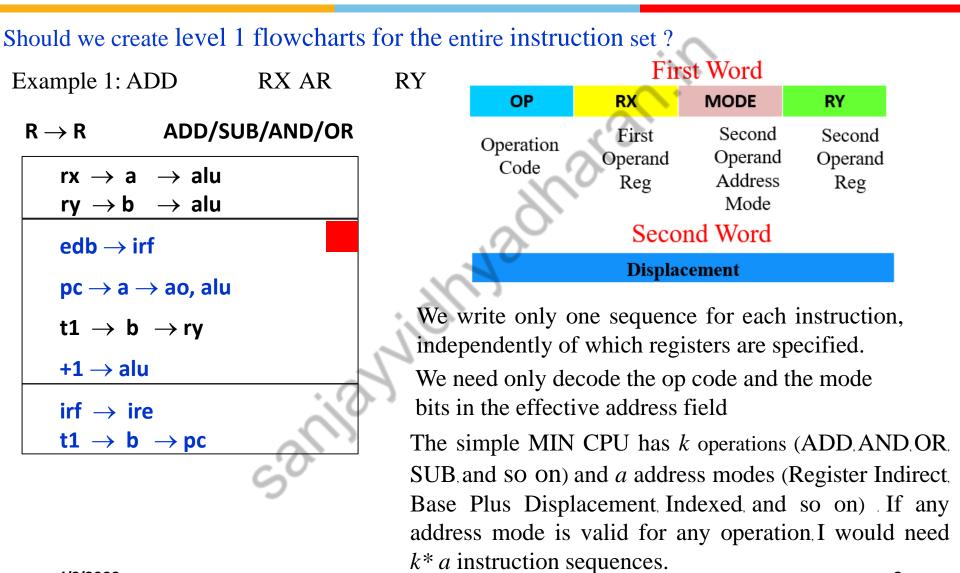

# **Rules for Doing Level 1 Flowcharts**

**1.** At the beginning of instruction execution, IRE is assumed to contain the current instruction. It must be loaded by the previous instruction. Each instruction's control word sequence will, therefore, have to fetch the next instruction and load it into IRE.

2. Instruction execution begins with the address mode sequence (if the instruction has one) and implicitly branches to the appropriate execution sequence for completion.

3. The execution sequences for register-to-register instructions cannot be shared with execution sequences for memory reference instructions.

4. The execution sequences for standard dual operand instructions (ADD, AND, SUB, and so on) are identical except for the(implied) ALU function. They can use a common execution sequence if the op code directly specifies the ALU operation (the same way register fields select the registers ).

COMMUNICATION

4/2/2022

ELECTRICAL

ELECTRONICS

#### **Execution Sequences for Register-to-Register**

| LOAD                  |                                   |               | STORE                 | N                                     |

|-----------------------|-----------------------------------|---------------|-----------------------|---------------------------------------|

| ry→a→alu, rx<br>0→alu | edb→irf<br>pc→a→alu, ao<br>+1→alu |               | rx→a→alu, ry<br>0→alu | edb→irf<br>pc→a→alu, ao<br>+1→alu     |

|                       | irf→ire<br>t1→a→pc                | 12            | 20.0                  | irf→ire<br>t1→a→pc                    |

| ADD                   |                                   | $\mathcal{O}$ | SUB                   |                                       |

| rx→a→alu<br>ry→b→alu  | edb→irf<br>pc→a→alu, ao<br>+1→alu |               | rx→a→alu<br>ry→b→alu  | edb →irf<br>pc →a →alu, ao<br>+1 →alu |

| t1→a→ry               | irf→ire<br>t1→a→pc                |               | t1→a→ry               | irf→ire<br>t1→a→pc                    |

COMMUNICATION

4/2/2022

**ELECTRICAL**

**ELECTRONICS**

#### **Execution Sequences with a Memory Operand Reference**

| ADD                  |                                   | AND |                      |                                   |

|----------------------|-----------------------------------|-----|----------------------|-----------------------------------|

| di→b→alu<br>rx→a→alu | edb→irf<br>pc→a→alu, ao<br>+1→alu |     | di→b→alu<br>rx→a→alu | edb→irf<br>pc→a→alu, ao<br>+1→alu |

| t1→a→do<br>t2→b→ao   | irf-→ire<br>t1→b→pc               | 19  | t1→a→do<br>t2→b→ao   | irf→ire<br>t1→b→pc                |

SUB

| di→b→alu<br>rx→a→alu | edb→irf<br>pc→a→alu, ao<br>+1→alu |

|----------------------|-----------------------------------|

| t1→a→do              | irf→ire                           |

| t2→b→ao              | t1→b→pc                           |

#### **Execution Sequences with a Memory Operand Reference**

4/2/2022

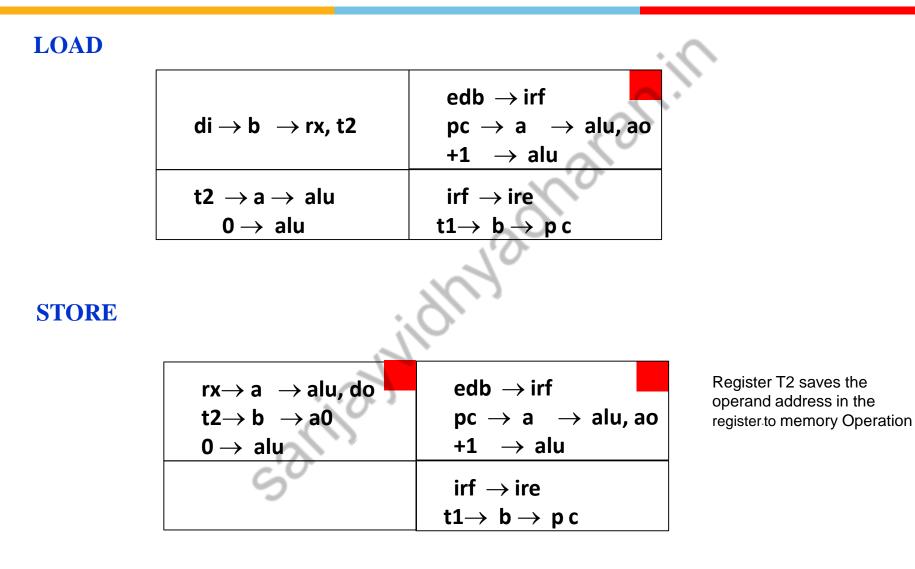

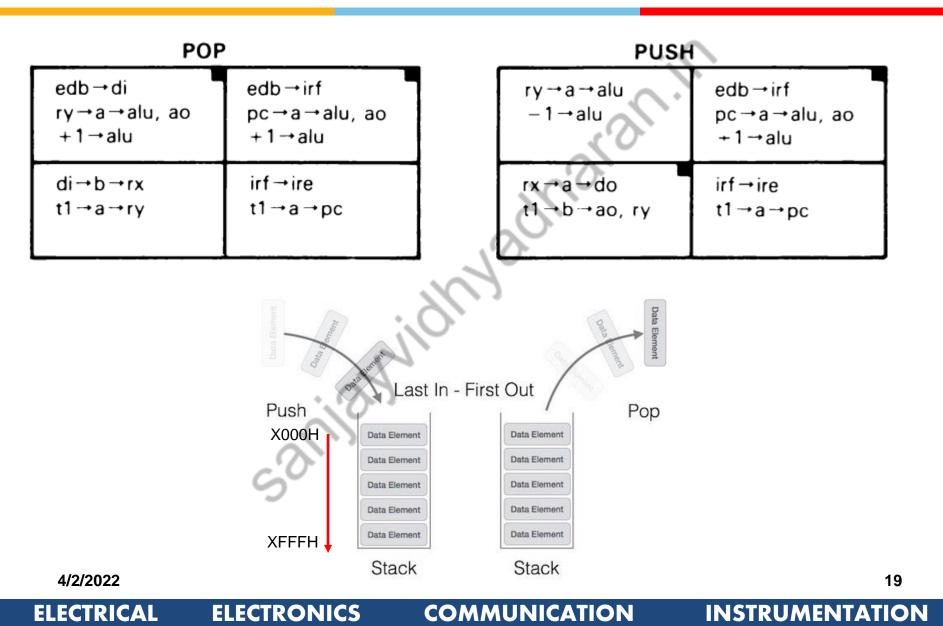

#### **Execution Sequences for Special Instructions**

4/2/2022

**ELECTRICAL**

**ELECTRONICS**

COMMUNICATION

INSTRUMENTATION