كلية المستقبل الجامعة قسم الانطمة الطبية الذكية 2022-2023

# **Processing Unit Design**

## Lecture 4

## MSc. Riyam K. Marjan 2022-2023

كلية المستقبل الجامعة قسم الانطمة الطبية الذكية 2022-2023

### I. CPU Basics

- 1. The central processing unit(CPU). The brain of any computer system is the CPU. It controls the functioning of the other units and process the data. The CPU is sometimes called the processor, or in the personal computer field called "microprocessor".

- 2. The processor acts as the controller of all actions or services provided by the system. Processor actions are synchronized to its clock input.

- 3. The execution cycle is repeated as long as there are more instructions to execute

- 4. Usually, we use mega Hertz (MHz) and giga Hertz (GHz) as in 1.8 GHz Pentium. The processor can be thought of as executing the following cycle forever:

- Fetch an instruction from the memory,

- Decode the instruction (i.e., determine the instruction type),

- Execute the instruction (i.e., perform the action specified by the instruction).

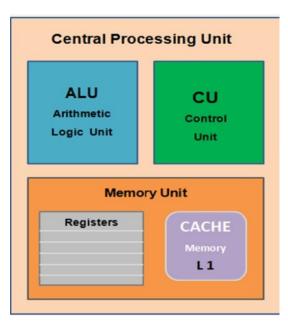

#### The components of CPU:

A typical CPU has three major components:

- 1. Memory Unit (Registers)

- 2. Arithmetic logic unit (ALU)

- 3. Control Unit (CU)

## II. Register Set \types\design issues

- The CPU register holds the key role which is small data holding place or memory, and is an integral part of the processor.

- It is a very fast memory of computer mainly used to execute the programs and operation.

Register basically used to quickly store, accept, transfer, and operate on data based on the instructions used by the CPU.

كلية المستقبل الجامعة قسم الانطمة الطبية الذكية 2022-2023

#### How Register works into the CPU?

When we give the input, these are stored and in register processes and the output is from the register only. So basically a register will perform the following operations.

- **Fetch**: To fetch the instructions of the user also the instructions that are present in the main memory in a sorted way

- **Decode**: The second operation is to decode the instructions that need to perform. Thus CPU will be knowing what are the instructions

- **Execute**: Once the instructions are decoded then execute operation is performed by the CPU. Once done the result is presented on the user screen

#### What are the types of registers into the CPU?

Here are the following types of registers

| NO | NAME                        | SYMBOL | FUNCTIONING                                                                                                                                                                                                       |

|----|-----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Accumulator                 | AC     | used to store information taken from memory.                                                                                                                                                                      |

| 2  | Memory address<br>registers | MAR    | Used to store Address location of memory to be accessed later. It is called by both MAR and MDR together                                                                                                          |

| 3  | Memory data<br>registers    | MDR    | All the information written and read from a certain memory<br>address is stored here                                                                                                                              |

| 4  | General-purpose<br>register | GPR    | Consist of a series of registers generally starting from R0 and<br>running till Rn - 1. These registers tend to store any form of<br>temporary data that is sent to a register during any<br>undertaking process. |

| 5  | Program counter             | PC     | These registers are utilized in keeping the record of a program that is being executed or under execution.                                                                                                        |

| 6  | Instructions<br>registers   | IR     | Instruction registers hold the information about to be executed.                                                                                                                                                  |

| 7  | Condition code<br>registers |        | These have different flags that depict the status of operations.<br>These registers set the flags accordingly if the result of<br>operation caused zero or negative                                               |

| 8  | Temporary<br>registers      | TR     | Holds temporary data                                                                                                                                                                                              |

كلية المستقبل الجامعة قسم الانطمة الطبية الذكية 2022-2023

| 9  | Input registers           | INPR | Carries input character                                                                                      |

|----|---------------------------|------|--------------------------------------------------------------------------------------------------------------|

| 10 | Output registers          | OUTR | Carries output character                                                                                     |

| 11 | Index registers           | BX   | Store values and numbers included in the address information<br>and transform them into effective addresses. |

| 12 | Memory buffer<br>register | MBR  | The basic functionality of these is to save called data from memory.                                         |

| 13 | Stack control registers   | SCR  | Stack is a set of location memory where data is stored and retrieved in a certain order.                     |

| 14 | Flag register             | FR   | Flag registers are used to indicate a particular condition.                                                  |

| 15 | Segment register          | SR   | Hold address for memory                                                                                      |

| 16 | Data register             | DX   | Hold memory operand                                                                                          |

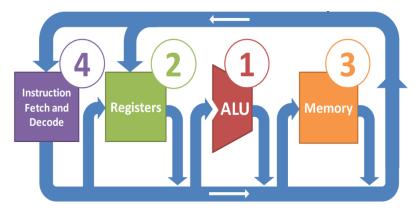

### III. Data path

• Datapath is the path that the input data follows in a processor to appear as an output. A data path is a set of functional units that carry out data processing operations. Datapaths, with a control unit, make up the CPU (central processing unit) of a computer system.

• The datapath elements are the functional blocks within a microprocessor that actually interact to perform computational operations. These tasks include reading/writing to memory, arithmetic, logic operations, and numerical shift operations

كلية المستقبل الجامعة قسم الانطمة الطبية الذكية 2022-2023

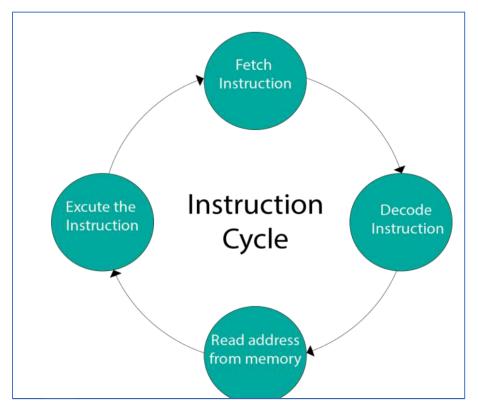

## IV. CPU Instruction Cycle

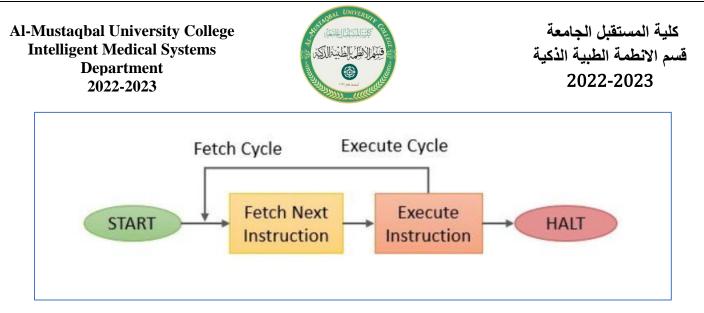

- The instruction cycle (also known as the fetch-decode-execute cycle, or simply the fetch-execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process instructions.

- The processing involved in the execution of a single instruction is termed as Instruction Cycle. This processing is done in two steps i.e. fetch and execute. To execute an instruction the processor first reads an instruction from the memory which is called **fetching** and then the fetched instruction is **executed**.

#### **Example:**

The figure below shows you the processing of the basic instruction cycle. In the beginning, to start the execution of a program, the processor runs the fetch cycle and fetches the first instruction from the memory. The execution cycle interprets the operation and performs the operations specified in the instruction accordingly.

This cycle repeats until all the instructions are executed from the program and after the execution of the last instruction the instruction cycle get halt. So, this was the scenario where there were no interrupts.