PC Hardware

# Contents

| 1 | Com  | nputer hardware                              | 1  |

|---|------|----------------------------------------------|----|

|   | 1.1  | Von Neumann architecture                     | 1  |

|   | 1.2  | Sales                                        | 1  |

|   | 1.3  | Different systems                            | 2  |

|   |      | 1.3.1 Personal computer                      | 2  |

|   |      | 1.3.2 Mainframe computer                     | 3  |

|   |      | 1.3.3 Departmental computing                 | 4  |

|   |      | 1.3.4 Supercomputer                          | 4  |

|   | 1.4  | See also                                     | 4  |

|   | 1.5  | References                                   | 4  |

|   | 1.6  | External links                               | 4  |

| 2 | Carr |                                              | _  |

| 2 |      | tral processing unit                         | 5  |

|   | 2.1  | History                                      | 5  |

|   |      | 2.1.1 Transistor and integrated circuit CPUs | 6  |

|   | 2.2  | 2.1.2 Microprocessors                        | 7  |

|   | 2.2  | Operation                                    | 8  |

|   |      | 2.2.1 Fetch                                  | 8  |

|   |      | 2.2.2 Decode                                 | 8  |

|   |      | 2.2.3 Execute                                | 9  |

|   | 2.3  | Design and implementation                    | 9  |

|   |      | 2.3.1 Control unit                           | 9  |

|   |      | 2.3.2 Arithmetic logic unit                  | 9  |

|   |      | 2.3.3 Integer range                          | 10 |

|   |      | 2.3.4 Clock rate                             | 10 |

|   |      | 2.3.5 Parallelism                            | 11 |

|   | 2.4  | Performance                                  | 13 |

|   | 2.5  | See also                                     | 14 |

|   | 2.6  | Notes                                        | 14 |

|   | 2.7  | References                                   | 15 |

|   | 2.8  | External links                               | 15 |

|   |      |                                              |    |

|   | 3.1 | Computers                                                | 16       |

|---|-----|----------------------------------------------------------|----------|

|   | 3.2 | Move toward processor integration in PCs                 | 17       |

|   | 3.3 | See also                                                 | 17       |

|   | 3.4 | Notes                                                    | 17       |

| 4 | Gra | phics processing unit                                    | 18       |

|   | 4.1 | History                                                  | 18       |

|   |     | 4.1.1 1980s                                              | 18       |

|   |     | 4.1.2 1990s                                              | 19       |

|   |     | 4.1.3 2000 to 2006                                       | 20       |

|   |     | 4.1.4 2006 to present                                    | 20       |

|   |     | 4.1.5 GPU companies                                      | 20       |

|   | 4.2 | Computational functions                                  | 21       |

|   |     | 4.2.1 GPU accelerated video decoding                     | 21       |

|   | 4.3 | GPU forms                                                | 21       |

|   |     | 4.3.1 Dedicated graphics cards                           | 21       |

|   |     | 4.3.2 Integrated graphics solutions                      | 22       |

|   |     | 4.3.3 Hybrid solutions                                   | 22       |

|   |     | 4.3.4 Stream Processing and General Purpose GPUs (GPGPU) | 23       |

|   |     | 4.3.5 External GPU (eGPU)                                | 23       |

|   | 4.4 | Sales                                                    | 23       |

|   | 4.5 | See also                                                 | 24       |

|   |     | 4.5.1 Hardware                                           | 24       |

|   |     | 4.5.2 APIs                                               | 24       |

|   |     | 4.5.3 Applications                                       | 24       |

|   | 4.6 | References                                               | 24       |

|   | 4.7 | External links                                           | 25       |

| 5 | Ran | dom-access memory                                        | 26       |

| 5 | 5.1 | History                                                  | 26<br>26 |

|   | 5.2 | Types of RAM                                             | 20       |

|   | 5.3 | Memory hierarchy                                         | 28       |

|   | 5.4 | Other uses of RAM                                        | 28       |

|   | 5.1 | 5.4.1 Virtual memory                                     | 28       |

|   |     | 5.4.2 RAM disk                                           | 28       |

|   |     | 5.4.3 Shadow RAM                                         | 28       |

|   | 5.5 | Recent developments                                      | 28       |

|   | 5.6 | Memory wall                                              | 20<br>29 |

|   | 5.7 | See also                                                 | 29       |

|   | 5.8 | Notes and references                                     | 29       |

|   | 5.9 | External links                                           | 2)<br>30 |

|   | 5.7 |                                                          | 20       |

| 6 | Read | d-only memory 3                       | 81       |

|---|------|---------------------------------------|----------|

|   | 6.1  | History                               | 51       |

|   |      | 6.1.1 Use for storing programs        | 32       |

|   |      | 6.1.2 Use for storing data            | 33       |

|   | 6.2  | Types                                 | 33       |

|   |      | 6.2.1 Semiconductor based             | 33       |

|   |      | 6.2.2 Other technologies              | 34       |

|   | 6.3  | Speed                                 | 34       |

|   |      | 6.3.1 Reading                         | 34       |

|   |      | 6.3.2 Writing                         | 34       |

|   | 6.4  | Endurance and data retention          | 35       |

|   | 6.5  | Content images                        | 35       |

|   | 6.6  | See also                              | 5        |

|   | 6.7  | Terminology                           | 35       |

|   | 6.8  | References                            | 35       |

| - | DIO  |                                       |          |

| 7 | BIOS | · · · · · · · · · · · · · · · · · · · | 86<br>26 |

|   | 7.1  |                                       | 86<br>86 |

|   | 7.2  |                                       | 86<br>77 |

|   | 7.3  | 1                                     | 87<br>7  |

|   |      |                                       | 37       |

|   |      | 1                                     | 37       |

|   | 7.4  |                                       | 38       |

|   | 7.4  |                                       | 39<br>No |

|   |      | 1                                     | 39<br>10 |

|   |      |                                       | 10<br>10 |

|   |      | ,                                     | 10<br>10 |

|   | 7.5  |                                       | 10       |

|   |      | 7.5.1 Processor microcode updates     |          |

|   |      | 7.5.2 Identification                  |          |

|   |      | 7.5.3 Overclocking                    |          |

|   |      | 7.5.4 Modern use                      |          |

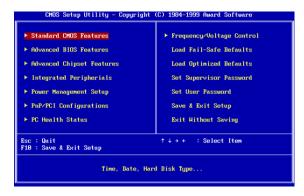

|   | 7.6  | Configuration                         |          |

|   |      | 7.6.1 Setup utility                   |          |

|   |      |                                       | 12       |

|   | 7.7  |                                       | 12       |

|   | 7.8  | 1                                     | 13       |

|   | 7.9  |                                       | 13       |

|   |      |                                       | 15       |

|   |      |                                       | 15       |

|   |      |                                       | 15       |

|   | 7.13 | References                            | 15       |

|    | 7.14                 | Further reading                  | 46              |

|----|----------------------|----------------------------------|-----------------|

|    | 7.15                 | External links                   | 46              |

| 8  | Boot                 | strapping                        | 47              |

|    | 8.1                  | Etymology                        | 47              |

|    | 8.2                  | Applications                     | 47              |

|    |                      | 8.2.1 Computing                  | 47              |

|    |                      | 8.2.2 Research                   | 49              |

|    |                      | 8.2.3 Statistics                 | 49              |

|    |                      | 8.2.4 Business                   | 49              |

|    |                      | 8.2.5 Biology                    | 49              |

|    |                      | 8.2.6 Law                        | 49              |

|    |                      | 8.2.7 Linguistics                | 49              |

|    |                      | 8.2.8 Physics                    | 49              |

|    |                      | 8.2.9 Electronics                | 49              |

|    |                      | 8.2.10 Electric power grid       | 50              |

|    |                      | 8.2.11 Cellular networks         | 50              |

|    |                      | 8.2.12 Media                     | 50              |

|    | 8.3                  | See also                         | 50              |

|    | 8.4                  | References                       | 50              |

|    | 8.5                  | External links                   | 51              |

| •  | т.                   |                                  | 50              |

| 9  | <b>F</b> IFIN<br>9.1 |                                  | <b>52</b><br>52 |

|    |                      | -                                |                 |

|    | 9.2                  |                                  | 52              |

|    | 9.3                  | -                                | 53              |

|    | 9.4                  |                                  | 53              |

|    | 9.5                  | 1                                | 53              |

|    | 9.6                  |                                  | 54              |

|    | 9.7                  | C                                | 54              |

|    | 0.0                  |                                  | 54              |

|    | 9.8                  | 5                                | 54              |

|    | 9.9                  |                                  | 55              |

|    |                      |                                  | 55              |

|    | 9.11                 | External links                   | 55              |

| 10 | Unifi                | ed Extensible Firmware Interface | 56              |

|    | 10.1                 | History                          | 56              |

|    | 10.2                 | Advantages                       | 56              |

|    | 10.3                 | Compatibility                    | 57              |

|    |                      | 10.3.1 Processor compatibility   | 57              |

|    |                      | 10.3.2 Disk device compatibility | 57              |

|    | 10.4  | Features    |                     |             |         | <br> | <br> |    | <br> |     | <br>••• |       | 58        |

|----|-------|-------------|---------------------|-------------|---------|------|------|----|------|-----|---------|-------|-----------|

|    |       | 10.4.1 S    | ervices             |             |         | <br> | <br> |    | <br> |     | <br>    |       | 58        |

|    |       | 10.4.2 A    | pplications .       |             |         | <br> | <br> |    | <br> |     | <br>    |       | 58        |

|    |       | 10.4.3 P    | rotocols            |             |         | <br> | <br> |    | <br> |     | <br>    |       | 58        |

|    |       | 10.4.4 D    | evice drivers       |             |         | <br> | <br> |    | <br> |     | <br>    |       | 58        |

|    |       | 10.4.5 G    | raphics feature     | s           |         | <br> | <br> |    | <br> |     | <br>    |       | 59        |

|    |       | 10.4.6 E    | FI System part      | ition       |         | <br> | <br> |    | <br> |     | <br>    |       | 59        |

|    |       | 10.4.7 B    | ooting              |             |         | <br> | <br> |    | <br> |     | <br>    |       | 59        |

|    |       | 10.4.8 C    | ompatibility Su     | apport Mo   | dule .  | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    |       | 10.4.9 U    | EFI shell           |             |         | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    |       | 10.4.10 E   | xtensions           |             |         | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    | 10.5  | Implemen    | tation and ado      | ption       |         | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    |       | 10.5.1 Ir   | ntel EFI            |             |         | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    |       | 10.5.2 P    | latforms using      | EFI/UEFI    |         | <br> | <br> |    | <br> |     | <br>    |       | 60        |

|    |       | 10.5.3 O    | perating system     | ns          |         | <br> | <br> |    | <br> |     | <br>    |       | 61        |

|    |       | 10.5.4 U    | se of UEFI wit      | h virtualiz | ation   | <br> | <br> |    | <br> |     | <br>    |       | 62        |

|    | 10.6  | Applicatio  | ons developmer      | 1t          |         | <br> | <br> |    | <br> |     | <br>    |       | 62        |

|    | 10.7  | Criticism   |                     |             |         | <br> | <br> |    | <br> |     | <br>    |       | 62        |

|    |       | 10.7.1 S    | ecure boot          |             |         | <br> | <br> |    | <br> |     | <br>    |       | 62        |

|    |       | 10.7.2 F    | irmware issues      |             |         | <br> | <br> |    | <br> |     | <br>    |       | 63        |

|    | 10.8  | See also    |                     |             |         | <br> | <br> |    | <br> |     | <br>    |       | 63        |

|    | 10.9  | Notes .     |                     |             |         | <br> | <br> |    | <br> |     | <br>    |       | 63        |

|    | 10.10 | )Reference  | es                  |             |         | <br> | <br> |    | <br> |     | <br>• • |       | 64        |

|    | 10.1  | Further re  | eading              |             |         | <br> | <br> |    | <br> |     | <br>    |       | 66        |

|    | 10.12 | 2External 1 | inks                |             |         | <br> | <br> |    | <br> |     | <br>    |       | 66        |

| 11 | D     | ( <b>^•</b> | -)                  |             |         |      |      |    |      |     |         |       | (7        |

| 11 |       | (computin   |                     | 1.4         |         |      |      |    |      |     |         |       | <b>67</b> |

|    | 11.1  | -           | nd and nomenc       |             |         |      |      |    |      |     |         |       | 67        |

|    |       |             | iternal bus         |             |         |      |      |    |      |     |         |       | 68<br>68  |

|    | 11.0  |             | xternal bus         |             |         |      |      |    |      |     |         |       | 68        |

|    |       | -           | tation details      |             |         |      |      |    |      |     |         |       |           |

|    | 11.5  | •           | · · · · · · · · · · |             |         |      |      |    |      |     |         |       | 68        |

|    |       |             | irst generation     |             |         |      |      |    |      |     |         |       | 69        |

|    |       |             | linis and micro     |             |         |      |      |    |      |     |         |       | 69        |

|    |       |             | econd generation    |             |         |      |      |    |      |     |         |       | 70        |

|    | 11.4  |             | hird generation     |             |         |      |      |    |      |     |         |       | 70        |

|    | 11.4  |             | of internal cor     |             |         |      |      |    |      |     |         |       | 70        |

|    |       |             | arallel             |             |         |      |      |    |      |     |         |       | 70        |

|    | 11 5  |             | erial               |             |         |      |      |    |      |     |         |       | 71        |

|    | 11.5  |             | of external con     |             |         |      |      |    |      |     |         |       | 71        |

|    |       |             | arallel             |             |         |      |      |    |      |     |         |       | 71        |

|    |       | 11.5.2 S    | erial               |             | • • • • | <br> | <br> | •• | <br> | ••• | <br>••• | <br>• | 71        |

| 11.6 Examples of internal/external computer buses       | 71 |

|---------------------------------------------------------|----|

| 11.7 See also                                           | 71 |

| 11.8 References                                         | 72 |

| 11.9 External links                                     | 72 |

| 11.10Text and image sources, contributors, and licenses | 73 |

| 11.10.1 Text                                            | 73 |

| 11.10.2 Images                                          | 78 |

| 11.10.3 Content license                                 | 81 |

# **Chapter 1**

# **Computer hardware**

For other uses, see Hardware. Computer hardware (usually simply called hardware

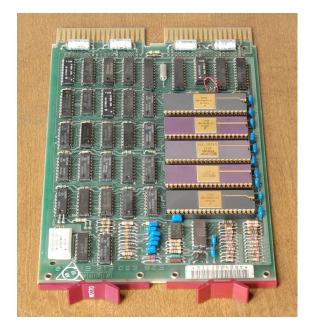

PDP-11 CPU board

when a computing context is implicit) is the collection of physical elements that constitutes a computer system. Computer hardware is the physical parts or components of a computer, such as the monitor, mouse, keyboard, computer data storage, hard disk drive (HDD), system unit (graphic cards, sound cards, memory, motherboard and chips), and so on, all of which are physical objects that can be touched (that is, they are tangible).<sup>[1]</sup> In contrast, software is instructions that can be stored and run by hardware.

Software is any set of machine-readable instructions that directs a computer's processor to perform specific operations. A combination of hardware and software forms a usable computing system.<sup>[2]</sup>

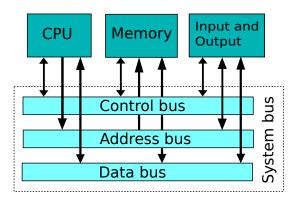

# **1.1** Von Neumann architecture

Main article: Von Neumann architecture The template for all modern computers is the Von Neu-

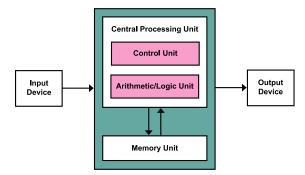

Von Neumann architecture scheme.

mann architecture, detailed in a 1945 paper by Hungarian mathematician John von Neumann. This describes a design architecture for an electronic digital computer with subdivisions of a processing unit consisting of an arithmetic logic unit and processor registers, a control unit containing an instruction register and program counter, a memory to store both data and instructions, external mass storage, and input and output mechanisms.<sup>[3]</sup> The meaning of the term has evolved to mean a stored-program computer in which an instruction fetch and a data operation cannot occur at the same time because they share a common bus. This is referred to as the Von Neumann bottleneck and often limits the performance of the system.<sup>[4]</sup>

# 1.2 Sales

For the third consecutive year, U.S. business-to-business channel sales (sales through distributors and commercial resellers) increased, ending 2013 up nearly 6 percent at \$1 doller. The impressive growth was the fastest sales increase since the end of the recession. Sales growth accelerated in the second half of the year peaking in fourth quarter with a 6.9 percent increase over the fourth quarter of 2012.<sup>[5]</sup>

# **1.3** Different systems

There are a number of different types of computer system in use today.

#### **1.3.1** Personal computer

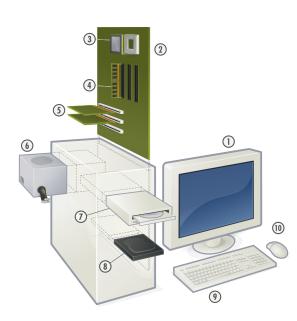

Hardware of a modern personal computer

1. Monitor 2. Motherboard 3. CPU 4. RAM 5. Expansion cards 6. Power supply 7. Optical disc drive 8. Hard disk drive

9. Keyboard 10. Mouse

Inside a custom-built computer: power supply at the bottom has its own cooling fan.

The personal computer, also known as the PC, is one of the most common types of computer due to its versatility and relatively low price. Laptops are generally very similar, although may use lower-power or reduced size components.

#### Case

#### Main article: Computer case

The computer case is a plastic or metal enclosure that houses most of the components. Those found on desktop computers are usually small enough to fit under a desk, however in recent years more compact designs have become more common place, such as the all-in-one style designs from Apple, namely the iMac. Laptops are computers that usually come in a clamshell form factor, again however in more recent years deviations from this form factor have started to emerge such as laptops that have a detachable screen that become tablet computers in their own right.

#### **Power supply**

Main article: Power supply unit (computer)

A power supply unit (PSU) converts alternating current (AC) electric power to low-voltage DC power for the internal components of the computer. Laptops are capable of running from a built-in battery, normally for a period of hours.<sup>[6]</sup>

#### Motherboard

#### Main article: Motherboard

The motherboard is the main component of computer. It is a large rectangular board with integrated circuitry that connects the other parts of the computer including the CPU, the RAM, the disk drives(CD, DVD, hard disk, or any others) as well as any peripherals connected via the ports or the expansion slots.

Components directly attached to or part of the motherboard include:

- The **CPU** (Central Processing Unit) performs most of the calculations which enable a computer to function, and is sometimes referred to as the "brain" of the computer. It is usually cooled by a heat sink and fan. Most newer CPUs include an on-die Graphics Processing Unit (GPU).

- The **Chipset**, which includes the north bridge, mediates communication between the CPU and the other components of the system, including main memory.

- The **Random-Access Memory** (RAM) stores the code and data that are being actively accessed by the CPU.

- The **Read-Only Memory** (ROM) stores the BIOS that runs when the computer is powered on or otherwise begins execution, a process known as Bootstrapping, or "booting" or "booting up". The **BIOS** (Basic Input Output System) includes boot firmware and power management firmware. Newer motherboards use Unified Extensible Firmware Interface (UEFI) instead of BIOS.

- **Buses** connect the CPU to various internal components and to expansion cards for graphics and sound.

- The CMOS battery is also attached to the motherboard. This battery is the same as a watch battery or a battery for a remote to a car's central locking system. Most batteries are CR2032, which powers the memory for date and time in the BIOS chip.

#### **Expansion cards**

Main article: Expansion card

An expansion card in computing is a printed circuit board that can be inserted into an expansion slot of a computer motherboard or backplane to add functionality to a computer system via the expansion bus.

#### Storage devices

#### Main article: Computer data storage

Computer data storage, often called storage or memory, refers to computer components and recording media that retain digital data. Data storage is a core function and fundamental component of computers.

#### Fixed media

Data is stored by a computer using a variety of media. Hard disk drives are found in virtually all older computers, due to their high capacity and low cost, but solid-state drives are faster and more power efficient, although currently more expensive than hard drives, so are often found in more expensive computers. Some systems may use a disk array controller for greater performance or reliability.

#### **Removable media**

To transfer data between computers, a USB flash drive or Optical disc may be used. Their usefulness depends on being readable by other systems; the majority of machines have an optical disk drive, and virtually all have a USB port.

#### Input and output peripherals

#### Main article: Peripheral

Input and output devices are typically housed externally to the main computer chassis. The following are either standard or very common to many computer systems.

#### Input

Input devices allow the user to enter information into the system, or control its operation. Most personal computers have a mouse and keyboard, but laptop systems typically use a touchpad instead of a mouse. Other input devices include webcams, microphones, joysticks, and image scanners.

#### **Output device**

Output devices display information in a human readable form. Such devices could include printers, speakers, monitors or a Braille embosser.

## **1.3.2** Mainframe computer

An IBM System z9 mainframe

A mainframe computer is a much larger computer that typically fills a room and may cost many hundreds or thousands of times as much as a personal computer. They are designed to perform large numbers of calculations for governments and large enterprises.

#### **1.3.3** Departmental computing

In the 1960s and 1970s more and more departments started to use cheaper and dedicated systems for specific purposes like process control and laboratory automation.

Main article: Minicomputer

## 1.3.4 Supercomputer

A supercomputer is superficially similar to a mainframe, but is instead intended for extremely demanding computational tasks. As of November 2013, the fastest supercomputer in the world is the Tianhe-2, in Guangzhou, China.<sup>[7]</sup>

The term supercomputer does not refer to a specific technology. Rather it indicates the fastest computers available at any given time. In mid 2011, the fastest supercomputers boasted speeds exceeding one petaflop, or 1000 trillion floating point operations per second. Super computers are fast but extremely costly so they are generally used by large organizations to execute computationally demanding tasks involving large data sets. Super computers typically run military and scientific applications. Although they cost millions of dollars, they are also being used for commercial applications where huge amounts of data must be analyzed. For example, large banks employ supercomputers to calculate the risks and returns of various investment strategies, and healthcare organizations use them to analyze giant databases of patient data to determine optimal treatments for various diseases and problems incurring to our country.

# 1.4 See also

• Open-source computing hardware

# 1.5 References

- [1] "Parts of computer". Microsoft. Retrieved 5 December 2013.

- [2] Smither, Roger. "Use of computers in audiovisual archives". UNESCO. Retrieved 5 December 2013.

- [3] von Neumann, John (1945). "First Draft of a Report on the EDVAC".

- [4] Markgraf, Joey D. (2007). "The Von Neumann bottleneck". Retrieved 24 August 2011.

- [5] US B2B Channel sales reach nearly \$62 Billion in 2013, by The NPD Group: https: //www.npd.com/wps/portal/npd/us/news/press-releases/ us-b2bchannel-sales-reach-nearly-62-billion-in-2013-according-to-the-npd-group/

- [6] "How long should a laptop battery last?". Computer Hope. Retrieved 9 December 2013.

- [7] Alba, Davey. "China's Tianhe-2 Caps Top 10 Supercomputers". IEEE. Retrieved 9 December 2013.

# **1.6** External links

- Media related to Computer hardware at Wikimedia Commons

- Learning materials related to Computer hardware at Wikiversity

- "What You Need to Know About Hardware Beta Tests" Centercode.com

# **Chapter 2**

# **Central processing unit**

"CPU" redirects here. For other uses, see CPU (disambiguation).

"Computer processor" redirects here. For other uses, see Processor (computing).

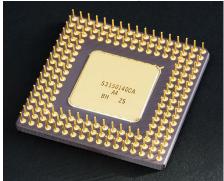

An Intel 80486DX2 CPU, as seen from above

Bottom side of an Intel 80486DX2

A **central processing unit** (**CPU**) is the electronic circuitry within a computer that carries out the instructions of a computer program by performing the basic arithmetic, logical, control and input/output (I/O) operations specified by the instructions. The term has been used in the computer industry at least since the early 1960s.<sup>[1]</sup> Traditionally, the term "CPU" refers to a processor and its control unit (CU), distinguishing these core elements of a computer from external components such as main memory and I/O circuitry.<sup>[2]</sup>

The form, design and implementation of CPUs have changed over the course of their history, but their fundamental operation remains almost unchanged. Principal components of a CPU include the arithmetic logic unit (ALU) that performs arithmetic and logic operations, hardware registers that supply operands to the ALU and store the results of ALU operations, and a control unit that fetches instructions from memory and "executes" them by directing the coordinated operations of the ALU, registers and other components.

Most modern CPUs are microprocessors, meaning they are contained on a single integrated circuit (IC) chip. An IC that contains a CPU may also contain memory, peripheral interfaces, and other components of a computer; such integrated devices are variously called microcontrollers or systems on a chip (SoC). Some computers employ a multi-core processor, which is a single chip containing two or more CPUs called "cores"; in that context, single chips are sometimes referred to as "sockets".<sup>[3]</sup> Array processors or vector processors have multiple processors that operate in parallel, with no unit considered central.

# 2.1 History

Main article: History of general purpose CPUs

Computers such as the ENIAC had to be physically rewired to perform different tasks, which caused these machines to be called "fixed-program computers".<sup>[4]</sup> Since the term "CPU" is generally defined as a device for software (computer program) execution, the earliest devices that could rightly be called CPUs came with the advent of the stored-program computer.

The idea of a stored-program computer was already present in the design of J. Presper Eckert and John William Mauchly's ENIAC, but was initially omitted so that it could be finished sooner. On June 30, 1945, before ENIAC was made, mathematician John von Neumann distributed the paper entitled *First Draft of a Report on the EDVAC*. It was the outline of a stored-program computer that would eventually be completed in August 1949.<sup>[5]</sup> EDVAC was designed to perform a certain number of instructions (or operations) of various types. Significantly, the programs written for EDVAC were to be stored in high-speed computer memory rather than specified by the physical wiring of the computer. This over-

EDVAC, one of the first stored-program computers.

came a severe limitation of ENIAC, which was the considerable time and effort required to reconfigure the computer to perform a new task. With von Neumann's design, the program, or software, that EDVAC ran could be changed simply by changing the contents of the memory. EDVAC, however, was not the first stored-program computer; the Manchester Small-Scale Experimental Machine, a small prototype stored-program computer, ran its first program on 21 June 1948<sup>[6]</sup> and the Manchester Mark 1 ran its first program during the night of 16–17 June 1949.

Early CPUs were custom-designed as a part of a larger, sometimes one-of-a-kind, computer. However, this method of designing custom CPUs for a particular application has largely given way to the development of massproduced processors that are made for many purposes. This standardization began in the era of discrete transistor mainframes and minicomputers and has rapidly accelerated with the popularization of the integrated circuit (IC). The IC has allowed increasingly complex CPUs to be designed and manufactured to tolerances on the order of nanometers. Both the miniaturization and standardization of CPUs have increased the presence of digital devices in modern life far beyond the limited application of dedicated computing machines. Modern microprocessors appear in everything from automobiles to cell phones and children's toys.

While von Neumann is most often credited with the design of the stored-program computer because of his design of EDVAC, others before him, such as Konrad Zuse, had suggested and implemented similar ideas. The socalled Harvard architecture of the Harvard Mark I, which was completed before EDVAC, also utilized a storedprogram design using punched paper tape rather than electronic memory. The key difference between the von Neumann and Harvard architectures is that the latter separates the storage and treatment of CPU instructions and data, while the former uses the same memory space for both. Most modern CPUs are primarily von Neumann in design, but CPUs with the Harvard architecture are seen as well, especially in embedded applications; for instance, the Atmel AVR microcontrollers are Harvard architecture processors.

Relays and vacuum tubes (thermionic valves) were commonly used as switching elements; a useful computer requires thousands or tens of thousands of switching devices. The overall speed of a system is dependent on the speed of the switches. Tube computers like EDVAC tended to average eight hours between failures, whereas relay computers like the (slower, but earlier) Harvard Mark I failed very rarely.<sup>[1]</sup> In the end, tube-based CPUs became dominant because the significant speed advantages afforded generally outweighed the reliability problems. Most of these early synchronous CPUs ran at low clock rates compared to modern microelectronic designs (see below for a discussion of clock rate). Clock signal frequencies ranging from 100 kHz to 4 MHz were very common at this time, limited largely by the speed of the switching devices they were built with.

# 2.1.1 Transistor and integrated circuit CPUs

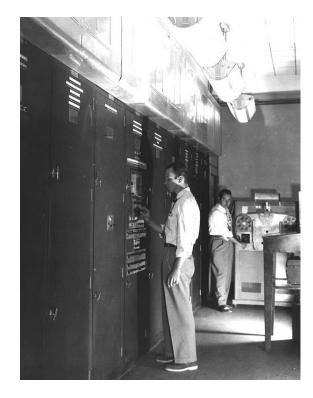

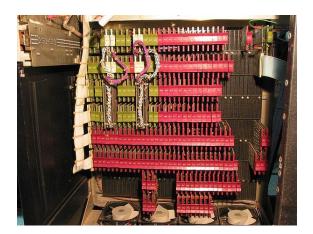

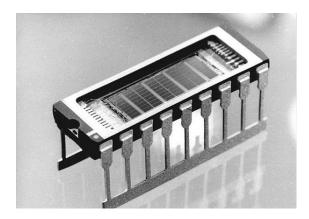

CPU, core memory, and external bus interface of a DEC PDP-8/I. Made of medium-scale integrated circuits.

The design complexity of CPUs increased as various technologies facilitated building smaller and more reliable electronic devices. The first such improvement came with the advent of the transistor. Transistorized CPUs during the 1950s and 1960s no longer had to be built out of bulky, unreliable, and fragile switching elements like vacuum tubes and electrical relays. With this improvement more complex and reliable CPUs were built onto one or several printed circuit boards containing discrete (individual) components.

During this period, a method of manufacturing many interconnected transistors in a compact space was developed. The integrated circuit (IC) allowed a large number of transistors to be manufactured on a single semiconductor-based die, or "chip". At first only very basic non-specialized digital circuits such as NOR gates were miniaturized into ICs. CPUs based upon these "building block" ICs are generally referred to as "smallscale integration" (SSI) devices. SSI ICs, such as the ones used in the Apollo guidance computer, usually contained up to a few score transistors. To build an entire CPU out of SSI ICs required thousands of individual chips, but still consumed much less space and power than earlier discrete transistor designs. As microelectronic technology advanced, an increasing number of transistors were placed on ICs, thus decreasing the quantity of individual ICs needed for a complete CPU. MSI and LSI (medium- and large-scale integration) ICs increased transistor counts to hundreds, and then thousands.

In 1964, IBM introduced its System/360 computer architecture that was used in a series of computers capable of running the same programs with different speed and performance. This was significant at a time when most electronic computers were incompatible with one another, even those made by the same manufacturer. To facilitate this improvement, IBM utilized the concept of a microprogram (often called "microcode"), which still sees widespread usage in modern CPUs.<sup>[7]</sup> The System/360 architecture was so popular that it dominated the mainframe computer market for decades and left a legacy that is still continued by similar modern computers like the IBM zSeries. In the same year (1964), Digital Equipment Corporation (DEC) introduced another influential computer aimed at the scientific and research markets, the PDP-8. DEC would later introduce the extremely popular PDP-11 line that originally was built with SSI ICs but was eventually implemented with LSI components once these became practical. In stark contrast with its SSI and MSI predecessors, the first LSI implementation of the PDP-11 contained a CPU composed of only four LSI integrated circuits.<sup>[8]</sup>

Transistor-based computers had several distinct advantages over their predecessors. Aside from facilitating increased reliability and lower power consumption, transistors also allowed CPUs to operate at much higher speeds because of the short switching time of a transistor in comparison to a tube or relay. Thanks to both the increased reliability as well as the dramatically increased speed of the switching elements (which were almost exclusively transistors by this time), CPU clock rates in the tens of megahertz were obtained during this period. Additionally while discrete transistor and IC CPUs were in heavy usage, new high-performance designs like SIMD (Single Instruction Multiple Data) vector processors began to appear. These early experimental designs later gave rise to the era of specialized supercomputers like those made by Cray Inc.

#### 2.1.2 Microprocessors

Main article: Microprocessor

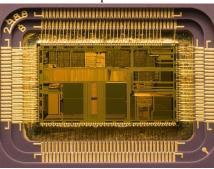

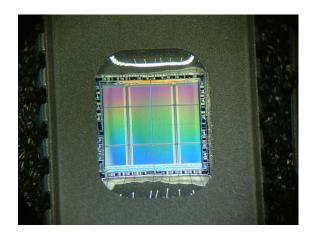

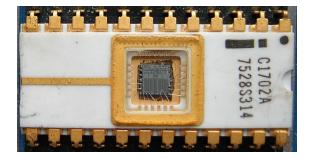

Die of an Intel 80486DX2 microprocessor (actual size: 12×6.75 mm) in its packaging

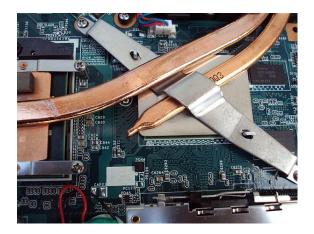

Intel Core i5 CPU on a Vaio E series laptop motherboard (on the right, beneath the heat pipe).

In the 1970s the fundamental inventions by Federico Faggin (Silicon Gate MOS ICs with self-aligned gates along with his new random logic design methodology) changed the design and implementation of CPUs forever. Since the introduction of the first commercially available microprocessor (the Intel 4004) in 1970, and the first widely used microprocessor (the Intel 8080) in 1974, this class of CPUs has almost completely overtaken all other central processing unit implementation methods. Mainframe and minicomputer manufacturers of the time launched proprietary IC development programs to upgrade their older computer architectures, and eventually produced instruction set compatible microprocessors that were backward-compatible with their older hardware and software. Combined with the advent and eventual success of the ubiquitous personal computer, the term CPU is now applied almost exclusively<sup>[lower-alpha 1]</sup> to microprocessors. Several CPUs (denoted 'cores') can be combined in a single processing chip.

Previous generations of CPUs were implemented as discrete components and numerous small integrated circuits (ICs) on one or more circuit boards. Microprocessors, on the other hand, are CPUs manufactured on a very small number of ICs; usually just one. The overall smaller CPU size, as a result of being implemented on a single die, means faster switching time because of physical factors like decreased gate parasitic capacitance. This has allowed synchronous microprocessors to have clock rates ranging from tens of megahertz to several gigahertz. Additionally, as the ability to construct exceedingly small transistors on an IC has increased, the complexity and number of transistors in a single CPU has increased many fold. This widely observed trend is described by Moore's law, which has proven to be a fairly accurate predictor of the growth of CPU (and other IC) complexity.<sup>[9]</sup>

While the complexity, size, construction, and general form of CPUs have changed enormously since 1950, it is notable that the basic design and function has not changed much at all. Almost all common CPUs today can be very accurately described as von Neumann stored-program machines.<sup>[lower-alpha 2]</sup> As the aforementioned Moore's law continues to hold true,<sup>[9]</sup> concerns have arisen about the limits of integrated circuit transistor technology. Extreme miniaturization of electronic gates is causing the effects of phenomena like electromigration and subthreshold leakage to become much more significant. These newer concerns are among the many factors causing researchers to investigate new methods of computing such as the quantum computer, as well as to expand the usage of parallelism and other methods that extend the usefulness of the classical von Neumann model.

# 2.2 Operation

The fundamental operation of most CPUs, regardless of the physical form they take, is to execute a sequence of stored instructions called a program. The instructions are kept in some kind of computer memory. There are three steps that nearly all CPUs use in their operation: fetch, decode, and execute.

After the execution of an instruction, the entire process repeats, with the next instruction cycle normally fetching the next-in-sequence instruction because of the incremented value in the program counter. If a jump instruction was executed, the program counter will be modified to contain the address of the instruction that was jumped to and program execution continues normally. In more complex CPUs, multiple instructions can be fetched, decoded, and executed simultaneously. This section describes what is generally referred to as the "classic **RISC pipeline**", which is quite common among the simple CPUs used in many electronic devices (often called microcontroller). It largely ignores the important role of **CPU cache**, and therefore the access stage of the pipeline.

Some instructions manipulate the program counter rather than producing result data directly; such instructions are generally called "jumps" and facilitate program behavior like loops, conditional program execution (through the use of a conditional jump), and existence of functions.<sup>[lower-alpha 3]</sup> In some processors, some other instructions change the state of bits in a "flags" register. These flags can be used to influence how a program behaves, since they often indicate the outcome of various operations. For example, in such processors a "compare" instruction evaluates two values and sets or clears bits in the flags register to indicate which one is greater or whether they are equal; one of these flags could then be used by a later jump instruction to determine program flow.

## 2.2.1 Fetch

The first step, fetch, involves retrieving an instruction (which is represented by a number or sequence of numbers) from program memory. The instruction's location (address) in program memory is determined by a program counter (PC), which stores a number that identifies the address of the next instruction to be fetched. After an instruction is fetched, the PC is incremented by the length of the instruction so that it will contain the address of the next instruction in the sequence.<sup>[Iower-alpha 4]</sup> Often, the instruction to be fetched must be retrieved from relatively slow memory, causing the CPU to stall while waiting for the instruction to be returned. This issue is largely addressed in modern processors by caches and pipeline architectures (see below).

#### 2.2.2 Decode

The instruction that the CPU fetches from memory determines what the CPU has to do. In the decode step, the instruction is broken up into parts that have significance to other portions of the CPU. The way in which the numerical instruction value is interpreted is defined by the CPU's instruction set architecture (ISA).<sup>[lower-alpha 5]</sup> Often, one group of numbers in the instruction, called the opcode, indicates which operation to perform. The remaining parts of the number usually provide information required for that instruction, such as operands for an addition operation. Such operands may be given as a constant value (called an immediate value), or as a place to locate a value: a register or a memory address, as determined by some addressing mode.

In some CPU designs the instruction decoder is implemented as a hardwired, unchangeable circuit. In others, a microprogram is used to translate instructions into sets of CPU configuration signals that are applied sequentially over multiple clock pulses. In some cases the memory that stores the microprogram is rewritable, making it possible to change the way in which the CPU decodes instructions.

#### 2.2.3 Execute

After the fetch and decode steps, the execute step is performed. Depending on the CPU architecture, this may consist of a single action or a sequence of actions. During each action, various parts of the CPU are electrically connected so they can perform all or part of the desired operation and then the action is completed, typically in response to a clock pulse. Very often the results are written to an internal CPU register for quick access by subsequent instructions. In other cases results may be written to slower, but less expensive and higher capacity main memory.

For example, if an addition instruction is to be executed, the arithmetic logic unit (ALU) inputs are connected to a pair of operand sources (numbers to be summed), the ALU is configured to perform an addition operation so that the sum of its operand inputs will appear at its output, and the ALU output is connected to storage (e.g., a register or memory) that will receive the sum. When the clock pulse occurs, the sum will be transferred to storage and, if the resulting sum is too large (i.e., it is larger than the ALU's output word size), an arithmetic overflow flag will be set.

# 2.3 Design and implementation

Main article: CPU design Hardwired into a CPU's circuitry is a set of basic oper-

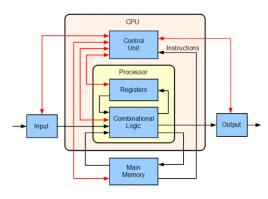

Block diagram of a basic uniprocessor-CPU computer. Black lines indicate data flow, whereas red lines indicate control flow; arrows indicate flow directions.

ations it can perform, called an instruction set. Such operations may involve, for example, adding or subtracting two numbers, comparing two numbers, or jumping to a different part of a program. Each basic operation is represented by a particular combination of bits, known as the machine language opcode; while executing instructions in a machine language program, the CPU decides which operation to perform by "decoding" the opcode. A complete machine language instruction consists of an opcode and, in many cases, additional bits that specify arguments for the operation (for example, the numbers to be summed in the case of an addition operation). Going up the complexity scale, a machine language program is a collection of machine language instructions that the CPU executes.

The actual mathematical operation for each instruction is performed by a combinational logic circuit within the CPU's processor known as the arithmetic logic unit or ALU. In general, a CPU executes an instruction by fetching it from memory, using its ALU to perform an operation, and then storing the result to memory. Beside the instructions for integer mathematics and logic operations, various other machine instructions exists, such as those for loading data from memory and storing it back, branching operations, and mathematical operations on floating-point numbers performed by the CPU's floatingpoint unit (FPU).<sup>[10]</sup>

# 2.3.1 Control unit

#### Main article: Control unit

The control unit of the CPU contains circuitry that uses electrical signals to direct the entire computer system to carry out stored program instructions. The control unit does not execute program instructions; rather, it directs other parts of the system to do so. The control unit communicates with both the ALU and memory.

## 2.3.2 Arithmetic logic unit

Main article: Arithmetic logic unit The arithmetic logic unit (ALU) is a digital circuit within

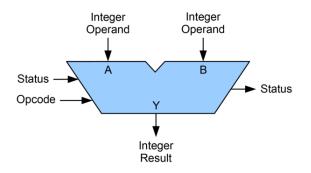

Symbolic representation of an ALU and its input and output signals

the processor that performs integer arithmetic and bitwise logic operations. The inputs to the ALU are the data words to be operated on (called operands), status information from previous operations, and a code from the control unit indicating which operation to perform. Depending on the instruction being executed, the operands may come from internal CPU registers or external memory, or they may be constants generated by the ALU itself.

When all input signals have settled and propagated through the ALU circuitry, the result of the performed operation appears at the ALU's outputs. The result consists of both a data word, which may be stored in a register or memory, and status information that is typically stored in a special, internal CPU register reserved for this purpose.

# 2.3.3 Integer range

Every CPU represents numerical values in a specific way. For example, some early digital computers represented numbers as familiar decimal (base 10) numeral system values, and others have employed more unusual representations such as ternary (base three). Nearly all modern CPUs represent numbers in binary form, with each digit being represented by some two-valued physical quantity such as a "high" or "low" voltage.<sup>[lower-alpha 6]</sup>

#

A six-bit word containing the binary encoded representation of decimal value 40. Most modern CPUs employ word sizes that are a power of two, for example eight, 16, 32 or 64 bits.

Related to numeric representation is the size and precision of integer numbers that a CPU can represent. In the case of a binary CPU, this is measured by the number of bits (significant digits of a binary encoded integer) that the CPU can process in one operation, which is commonly called "word size", "bit width", "data path width", "integer precision", or "integer size". A CPU's integer size determines the range of integer values it can directly operate on.<sup>[lower-alpha 7]</sup> For example, an 8-bit CPU can directly manipulate integers represented by eight bits, which have a range of 256 (2<sup>8</sup>) discrete integer values.

Integer range can also affect the number of memory locations the CPU can directly address (an address is an integer value representing a specific memory location). For example, if a binary CPU uses 32 bits to represent a memory address then it can directly address  $2^{32}$  memory locations. To circumvent this limitation and for various other reasons, some CPUs use mechanisms (such as bank switching) that allow additional memory to be addressed.

CPUs with larger word sizes require more circuitry and consequently are physically larger, cost more, and consume more power (and therefore generate more heat). As a result, smaller 4- or 8-bit microcontrollers are commonly used in modern applications even though CPUs with much larger word sizes (such as 16, 32, 64, even 128-bit) are available. When higher performance is re-

quired, however, the benefits of a larger word size (larger data ranges and address spaces) may outweigh the disadvantages.

To gain some of the advantages afforded by both lower and higher bit lengths, many CPUs are designed with different bit widths for different portions of the device. For example, the IBM System/370 used a CPU that was primarily 32 bit, but it used 128-bit precision inside its floating point units to facilitate greater accuracy and range in floating point numbers.<sup>[7]</sup> Many later CPU designs use similar mixed bit width, especially when the processor is meant for general-purpose usage where a reasonable balance of integer and floating point capability is required.

## 2.3.4 Clock rate

#### Main article: Clock rate

Most CPUs are synchronous circuits, which means they employ a clock signal to pace their sequential operations. The clock signal is produced by an external oscillator circuit that generates a consistent number of pulses each second in the form of a periodic square wave. The frequency of the clock pulses determines the rate at which a CPU executes instructions and, consequently, the faster the clock, the more instructions the CPU will execute each second.

To ensure proper operation of the CPU, the clock period is longer than the maximum time needed for all signals to propagate (move) through the CPU. In setting the clock period to a value well above the worst-case propagation delay, it is possible to design the entire CPU and the way it moves data around the "edges" of the rising and falling clock signal. This has the advantage of simplifying the CPU significantly, both from a design perspective and a component-count perspective. However, it also carries the disadvantage that the entire CPU must wait on its slowest elements, even though some portions of it are much faster. This limitation has largely been compensated for by various methods of increasing CPU parallelism (see below).

However, architectural improvements alone do not solve all of the drawbacks of globally synchronous CPUs. For example, a clock signal is subject to the delays of any other electrical signal. Higher clock rates in increasingly complex CPUs make it more difficult to keep the clock signal in phase (synchronized) throughout the entire unit. This has led many modern CPUs to require multiple identical clock signals to be provided to avoid delaying a single signal significantly enough to cause the CPU to malfunction. Another major issue, as clock rates increase dramatically, is the amount of heat that is dissipated by the CPU. The constantly changing clock causes many components to switch regardless of whether they are being used at that time. In general, a component that is switching uses more energy than an element in a static state. Therefore, as clock rate increases, so does energy consumption, causing the CPU to require more heat dissipation in the form of CPU cooling solutions.

One method of dealing with the switching of unneeded components is called clock gating, which involves turning off the clock signal to unneeded components (effectively disabling them). However, this is often regarded as difficult to implement and therefore does not see common usage outside of very low-power designs. One notable recent CPU design that uses extensive clock gating is the IBM PowerPC-based Xenon used in the Xbox 360; that way, power requirements of the Xbox 360 are greatly reduced.<sup>[11]</sup> Another method of addressing some of the problems with a global clock signal is the removal of the clock signal altogether. While removing the global clock signal makes the design process considerably more complex in many ways, asynchronous (or clockless) designs carry marked advantages in power consumption and heat dissipation in comparison with similar synchronous designs. While somewhat uncommon, entire asynchronous CPUs have been built without utilizing a global clock signal. Two notable examples of this are the ARM compliant AMULET and the MIPS R3000 compatible MiniMIPS.

Rather than totally removing the clock signal, some CPU designs allow certain portions of the device to be asynchronous, such as using asynchronous ALUs in conjunction with superscalar pipelining to achieve some arithmetic performance gains. While it is not altogether clear whether totally asynchronous designs can perform at a comparable or better level than their synchronous counterparts, it is evident that they do at least excel in simpler math operations. This, combined with their excellent power consumption and heat dissipation properties, makes them very suitable for embedded computers.<sup>[12]</sup>

#### 2.3.5 Parallelism

Main article: Parallel computing

The description of the basic operation of a CPU offered

| IF         | ID | EX | MEM | WB |    |    |    |     |    |    |    |    |     |    |

|------------|----|----|-----|----|----|----|----|-----|----|----|----|----|-----|----|

| i          |    |    |     |    | IF | ID | ΕX | MEM | WB |    |    |    |     |    |

| <b>+</b> . |    |    |     |    |    |    |    |     |    | IF | ID | ΕX | MEM | WB |

| t          |    |    |     |    |    |    |    |     |    |    |    |    |     |    |

Model of a subscalar CPU. Notice that it takes fifteen cycles to complete three instructions.

in the previous section describes the simplest form that a CPU can take. This type of CPU, usually referred to as *subscalar*, operates on and executes one instruction on one or two pieces of data at a time.

This process gives rise to an inherent inefficiency in subscalar CPUs. Since only one instruction is executed at a time, the entire CPU must wait for that instruction to complete before proceeding to the next instruction. As a result, the subscalar CPU gets "hung up" on instructions which take more than one clock cycle to complete execution. Even adding a second execution unit (see below) does not improve performance much; rather than one pathway being hung up, now two pathways are hung up and the number of unused transistors is increased. This design, wherein the CPU's execution resources can operate on only one instruction at a time, can only possibly reach *scalar* performance (one instruction per clock). However, the performance is nearly always subscalar (less than one instruction per cycle).

Attempts to achieve scalar and better performance have resulted in a variety of design methodologies that cause the CPU to behave less linearly and more in parallel. When referring to parallelism in CPUs, two terms are generally used to classify these design techniques. Instruction level parallelism (ILP) seeks to increase the rate at which instructions are executed within a CPU (that is, to increase the utilization of on-die execution resources), and thread level parallelism (TLP) purposes to increase the number of threads (effectively individual programs) that a CPU can execute simultaneously. Each methodology differs both in the ways in which they are implemented, as well as the relative effectiveness they afford in increasing the CPU's performance for an application.<sup>[lower-alpha 8]</sup>

#### Instruction-level parallelism

Main articles: Instruction pipelining and Superscalar One of the simplest methods used to accomplish in-

| IF              | ID | ΕX | MEM | WB  |     |     |     |    |

|-----------------|----|----|-----|-----|-----|-----|-----|----|

| ļi              | IF | ID | ΕX  | MEM | WB  |     |     |    |

| $t \rightarrow$ |    | IF | ID  | ΕX  | MEM | WB  |     |    |

|                 |    |    | IF  | ID  | ΕX  | MEM | WB  |    |

|                 |    |    |     | IF  | ID  | ΕX  | MEM | WB |

Basic five-stage pipeline. In the best case scenario, this pipeline can sustain a completion rate of one instruction per cycle.

creased parallelism is to begin the first steps of instruction fetching and decoding before the prior instruction finishes executing. This is the simplest form of a technique known as instruction pipelining, and is utilized in almost all modern general-purpose CPUs. Pipelining allows more than one instruction to be executed at any given time by breaking down the execution pathway into discrete stages. This separation can be compared to an assembly line, in which an instruction is made more complete at each stage until it exits the execution pipeline and is retired.

Pipelining does, however, introduce the possibility for a situation where the result of the previous operation is needed to complete the next operation; a condition often termed data dependency conflict. To cope with this, additional care must be taken to check for these sorts of conditions and delay a portion of the instruction pipeline if this occurs. Naturally, accomplishing this requires additional circuitry, so pipelined processors are more complex than subscalar ones (though not very significantly so). A pipelined processor can become very nearly scalar, inhibited only by pipeline stalls (an instruction spending more than one clock cycle in a stage).

| IF | ID | EX | MEM | WB  |     |     |     |    |

|----|----|----|-----|-----|-----|-----|-----|----|

| IF | ID | ΕX | MEM | WB  |     |     |     |    |

| i  | IF | ID | ΕX  | MEM | WB  |     |     |    |

| t  | IF | ID | ΕX  | MEM | WB  |     |     |    |

| •  |    | IF | ID  | EX  | MEM | WB  |     |    |

|    |    | IF | ID  | EX  | MEM | WB  |     |    |

|    |    |    | IF  | ID  | ΕX  | MEM | WB  |    |

|    |    |    | IF  | ID  | ΕX  | MEM | WB  |    |

|    |    |    |     | IF  | ID  | ΕX  | MEM | WB |

|    |    |    |     | IF  | ID  | EX  | MEM | WB |

A simple superscalar pipeline. By fetching and dispatching two instructions at a time, a maximum of two instructions per cycle can be completed.

Further improvement upon the idea of instruction pipelining led to the development of a method that decreases the idle time of CPU components even further. Designs that are said to be *superscalar* include a long instruction pipeline and multiple identical execution units.<sup>[13]</sup> In a superscalar pipeline, multiple instructions are read and passed to a dispatcher, which decides whether or not the instructions can be executed in parallel (simultaneously). If so they are dispatched to available execution units, resulting in the ability for several instructions to be executed simultaneously. In general, the more instructions a superscalar CPU is able to dispatch simultaneously to waiting execution units, the more instructions will be completed in a given cycle.

Most of the difficulty in the design of a superscalar CPU architecture lies in creating an effective dispatcher. The dispatcher needs to be able to quickly and correctly determine whether instructions can be executed in parallel, as well as dispatch them in such a way as to keep as many execution units busy as possible. This requires that the instruction pipeline is filled as often as possible and gives rise to the need in superscalar architectures for significant amounts of CPU cache. It also makes hazardavoiding techniques like branch prediction, speculative execution, and out-of-order execution crucial to maintaining high levels of performance. By attempting to predict which branch (or path) a conditional instruction will take, the CPU can minimize the number of times that the entire pipeline must wait until a conditional instruction is completed. Speculative execution often provides modest performance increases by executing portions of code that may not be needed after a conditional operation completes. Out-of-order execution somewhat rearranges the order in which instructions are executed to reduce delays due to data dependencies. Also in case of Single Instructions Multiple Data — a case when a lot of data from the same type has to be processed, modern processors can disable parts of the pipeline so that when a single instruction is executed many times, the CPU skips the fetch and decode phases and thus greatly increases performance on certain occasions, especially in highly monotonous program engines such as video creation software and photo processing.

In the case where a portion of the CPU is superscalar and part is not, the part which is not suffers a performance penalty due to scheduling stalls. The Intel P5 Pentium had two superscalar ALUs which could accept one instruction per clock each, but its FPU could not accept one instruction per clock. Thus the P5 was integer superscalar but not floating point superscalar. Intel's successor to the P5 architecture, P6, added superscalar capabilities to its floating point features, and therefore afforded a significant increase in floating point instruction performance.

Both simple pipelining and superscalar design increase a CPU's ILP by allowing a single processor to complete execution of instructions at rates surpassing one instruction per cycle (IPC).<sup>[lower-alpha 9]</sup> Most modern CPU designs are at least somewhat superscalar, and nearly all general purpose CPUs designed in the last decade are superscalar. In later years some of the emphasis in designing high-ILP computers has been moved out of the CPU's hardware and into its software interface, or ISA. The strategy of the very long instruction word (VLIW) causes some ILP to become implied directly by the software, reducing the amount of work the CPU must perform to boost ILP and thereby reducing the design's complexity.

#### **Thread-level parallelism**

Another strategy of achieving performance is to execute multiple programs or threads in parallel. This area of research is known as parallel computing. In Flynn's taxonomy, this strategy is known as Multiple Instructions-Multiple Data or MIMD.

technology used for this purpose was One multiprocessing (MP). The initial flavor of this technology is known as symmetric multiprocessing (SMP), where a small number of CPUs share a coherent view of their memory system. In this scheme, each CPU has additional hardware to maintain a constantly up-to-date view of memory. By avoiding stale views of memory, the CPUs can cooperate on the same program and programs can migrate from one CPU to another. To increase the number of cooperating CPUs beyond a handful, schemes such as non-uniform memory access (NUMA) and directory-based coherence protocols were introduced in the 1990s. SMP systems are limited to a small number of CPUs while NUMA systems have been built with thousands of processors. Initially, multiprocessing was built using multiple discrete CPUs and boards to implement the interconnect between the processors. When the processors and their interconnect are all implemented on a single silicon chip, the technology is known as a

#### multi-core processor.

It was later recognized that finer-grain parallelism existed with a single program. A single program might have several threads (or functions) that could be executed separately or in parallel. Some of the earliest examples of this technology implemented input/output processing such as direct memory access as a separate thread from the computation thread. A more general approach to this technology was introduced in the 1970s when systems were designed to run multiple computation threads in parallel. This technology is known as multi-threading (MT). This approach is considered more cost-effective than multiprocessing, as only a small number of components within a CPU is replicated to support MT as opposed to the entire CPU in the case of MP. In MT, the execution units and the memory system including the caches are shared among multiple threads. The downside of MT is that the hardware support for multithreading is more visible to software than that of MP and thus supervisor software like operating systems have to undergo larger changes to support MT. One type of MT that was implemented is known as block multithreading, where one thread is executed until it is stalled waiting for data to return from external memory. In this scheme, the CPU would then quickly switch to another thread which is ready to run, the switch often done in one CPU clock cycle, such as the UltraSPARC Technology. Another type of MT is known as simultaneous multithreading, where instructions of multiple threads are executed in parallel within one CPU clock cycle.

For several decades from the 1970s to early 2000s, the focus in designing high performance general purpose CPUs was largely on achieving high ILP through technologies such as pipelining, caches, superscalar execution, outof-order execution, etc. This trend culminated in large, power-hungry CPUs such as the Intel Pentium 4. By the early 2000s, CPU designers were thwarted from achieving higher performance from ILP techniques due to the growing disparity between CPU operating frequencies and main memory operating frequencies as well as escalating CPU power dissipation owing to more esoteric ILP techniques.

CPU designers then borrowed ideas from commercial computing markets such as transaction processing, where the aggregate performance of multiple programs, also known as throughput computing, was more important than the performance of a single thread or program.

This reversal of emphasis is evidenced by the proliferation of dual and multiple core CMP (chip-level multiprocessing) designs and notably, Intel's newer designs resembling its less superscalar P6 architecture. Late designs in several processor families exhibit CMP, including the x86-64 Opteron and Athlon 64 X2, the SPARC UltraSPARC T1, IBM POWER4 and POWER5, as well as several video game console CPUs like the Xbox 360's triple-core PowerPC design, and the PS3's 7-core Cell

#### microprocessor.

#### Data parallelism

Main articles: Vector processor and SIMD

A less common but increasingly important paradigm of CPUs (and indeed, computing in general) deals with data parallelism. The processors discussed earlier are all referred to as some type of scalar device. [lower-alpha 10] As the name implies, vector processors deal with multiple pieces of data in the context of one instruction. This contrasts with scalar processors, which deal with one piece of data for every instruction. Using Flynn's taxonomy, these two schemes of dealing with data are generally referred to as SIMD (single instruction, multiple data) and SISD (single instruction, single data), respectively. The great utility in creating CPUs that deal with vectors of data lies in optimizing tasks that tend to require the same operation (for example, a sum or a dot product) to be performed on a large set of data. Some classic examples of these types of tasks are multimedia applications (images, video, and sound), as well as many types of scientific and engineering tasks. Whereas a scalar CPU must complete the entire process of fetching, decoding, and executing each instruction and value in a set of data, a vector CPU can perform a single operation on a comparatively large set of data with one instruction. Of course, this is only possible when the application tends to require many steps which apply one operation to a large set of data.

Most early vector CPUs, such as the Cray-1, were associated almost exclusively with scientific research and cryptography applications. However, as multimedia has largely shifted to digital media, the need for some form of SIMD in general-purpose CPUs has become significant. Shortly after inclusion of floating point execution units started to become commonplace in general-purpose processors, specifications for and implementations of SIMD execution units also began to appear for general-purpose CPUs. Some of these early SIMD specifications like HP's Multimedia Acceleration eXtensions (MAX) and Intel's MMX were integer-only. This proved to be a significant impediment for some software developers, since many of the applications that benefit from SIMD primarily deal with floating point numbers. Progressively, these early designs were refined and remade into some of the common, modern SIMD specifications, which are usually associated with one ISA. Some notable modern examples are Intel's SSE and the PowerPC-related AltiVec (also known as VMX).[lower-alpha 11]

# 2.4 Performance

Further information: Computer performance and Benchmark (computing)

The *performance* or *speed* of a processor depends on, among many other factors, the clock rate (generally given in multiples of hertz) and the instructions per clock (IPC), which together are the factors for the instructions per second (IPS) that the CPU can perform.<sup>[14]</sup> Many reported IPS values have represented "peak" execution rates on artificial instruction sequences with few branches, whereas realistic workloads consist of a mix of instructions and applications, some of which take longer to execute than others. The performance of the memory hierarchy also greatly affects processor performance, an issue barely considered in MIPS calculations. Because of these problems, various standardized tests, often called "benchmarks" for this purpose-such as SPECint - have been developed to attempt to measure the real effective performance in commonly used applications.

Processing performance of computers is increased by using multi-core processors, which essentially is plugging two or more individual processors (called cores in this sense) into one integrated circuit.<sup>[15]</sup> Ideally, a dual core processor would be nearly twice as powerful as a single core processor. In practice, the performance gain is far smaller, only about 50%, due to imperfect software algorithms and implementation.<sup>[16]</sup> Increasing the number of cores in a processor (i.e. dual-core, quad-core, etc.) increases the workload that can be handled. This means that the processor can now handle numerous asynchronous events, interrupts, etc. which can take a toll on the CPU when overwhelmed. These cores can be thought of as different floors in a processing plant, with each floor handling a different task. Sometimes, these cores will handle the same tasks as cores adjacent to them if a single core is not enough to handle the information.

Due to specific capabilities of modern CPUs, such as hyper-threading and uncore, which involve sharing of actual CPU resources while aiming at increased utilization, monitoring performance levels and hardware utilization gradually became a more complex task. As a response, some CPUs implement additional hardware logic that monitors actual utilization of various parts of a CPU and provides various counters accessible to software; an example is Intel's *Performance Counter Monitor* technology.<sup>[3]</sup>

# 2.5 See also

- Accelerated processing unit

- Addressing mode

- CISC

- Computer bus

- Computer engineering

- CPU core voltage

- CPU socket

- Digital signal processor

- Hyper-threading

- List of CPU architectures

- Microprocessor

- Multi-core processor

- Protection ring

- RISC

- Stream processing

- True Performance Index

- Wait state

# 2.6 Notes

- [1] Integrated circuits are now used to implement all CPUs, except for a few machines designed to withstand large electromagnetic pulses, say from a nuclear weapon.

- [2] The so-called "von Neumann" memo expounded the idea of stored programs, which for example may be stored on punched cards, paper tape, or magnetic tape.

- [3] Some early computers like the Harvard Mark I did not support any kind of "jump" instruction, effectively limiting the complexity of the programs they could run. It is largely for this reason that these computers are often not considered to contain a proper CPU, despite their close similarity to stored-program computers.

- [4] Since the program counter counts *memory addresses* and not *instructions*, it is incremented by the number of memory units that the instruction word contains. In the case of simple fixed-length instruction word ISAs, this is always the same number. For example, a fixed-length 32-bit instruction word ISA that uses 8-bit memory words would always increment the PC by four (except in the case of jumps). ISAs that use variable-length instruction words increment the PC by the number of memory words corresponding to the last instruction's length.

- [5] Because the instruction set architecture of a CPU is fundamental to its interface and usage, it is often used as a classification of the "type" of CPU. For example, a "PowerPC CPU" uses some variant of the PowerPC ISA. A system can execute a different ISA by running an emulator.

- [6] The physical concept of voltage is an analog one by nature, practically having an infinite range of possible values. For the purpose of physical representation of binary numbers, two specific ranges of voltages are defined, one for logic '0' and another for logic '1'. These ranges are dictated by design considerations such as noise margins and characteristics of the devices used to create the CPU.

- [7] While a CPU's integer size sets a limit on integer ranges, this can (and often is) overcome using a combination of software and hardware techniques. By using additional memory, software can represent integers many magnitudes larger than the CPU can. Sometimes the CPU's ISA will even facilitate operations on integers larger than it can natively represent by providing instructions to make large integer arithmetic relatively quick. This method of dealing with large integers is slower than utilizing a CPU with higher integer size, but is a reasonable tradeoff in cases where natively supporting the full integer range needed would be cost-prohibitive. See Arbitraryprecision arithmetic for more details on purely softwaresupported arbitrary-sized integers.