# Precise Timing of Digital Signals: Circuits and Applications

by

#### Muhammad A. Nummer

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007 ©Muhammad A. Nummer 2007 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

With the rapid advances in process technologies, the performance of state-of-the-art integrated circuits is improving steadily. The drive for higher performance is accompanied with increased emphasis on meeting timing constraints not only at the design phase but during device operation as well. Fortunately, technology advancements allow for even more precise control of the timing of digital signals, an advantage which can be used to provide solutions that can address some of the emerging timing issues. In this thesis, circuit and architectural techniques for the precise timing of digital signals are explored. These techniques are demonstrated in applications addressing timing issues in modern digital systems.

A methodology for slow-speed timing characterization of high-speed pipelined datapaths is proposed. The technique uses a clock-timing circuit to create shifted versions of a slow-speed clock. These clocks control the data flow in the pipeline in the test mode. Test results show that the design provides an average timing resolution of 52.9ps in  $0.18\mu$ m CMOS technology. Results also demonstrate the ability of the technique to track the performance of high-speed pipelines at a reduced clock frequency and to test the clock-timing circuit itself.

In order to achieve higher resolutions than that of an inverter/buffer stage, a differential (vernier) delay line is commonly used. To allow for the design of differential delay lines with programmable delays, a digitally-controlled delay-element is proposed. The delay element is monotonic and achieves a high degree of transfer characteristics' (digital code vs. delay) linearity. Using the proposed delay element, a sub-1ps resolution is demonstrated experimentally in  $0.18\mu$ m CMOS.

The proposed delay element with a fixed delay step of 2ps is used to design a high-precision all-digital phase aligner. High-precision phase alignment has many applications in modern digital systems such as high-speed memory controllers, clock-deskew buffers, and delay and phaselocked loops. The design is based on a differential delay line and a variation tolerant phase detector using redundancy. Experimental results show that the phase aligner's range is from -264ps to +247ps which corresponds to an average delay step of approximately 2.43ps. For various input phase difference values, test results show that the difference is reduced to less than 2ps at the output of the phase aligner.

On-chip time measurement is another application that requires precise timing. It has applications in modern automatic test equipment and on-chip characterization of jitter and skew. In order to achieve small conversion time, a flash time-to-digital converter is proposed. Mismatch between the various delay comparators limits the time measurement precision. This is demonstrated through an experiment in which a 6-bit, 2.5ps resolution flash time-to-digital converter provides an effective resolution of only 4-bits. The converter achieves a maximum conversion rate of 1.25GSa/s.

#### Acknowledgements

All praise is due to God, Most Gracious, Most Merciful, Whose bounties and blessings are ever dominating throughout my life.

I would like to express my deep gratitude and appreciation to my supervisor, Prof. Manoj Sachdev. Prof. Sachdev has always been an invaluable source of guidance and encouragement. I am extremely grateful to all his support throughout the years I have spent in Waterloo.

Throughout the period I spent doing my Ph.D., I received tremendous support from many people. I am grateful to Prof. David Nairn for his insights on testing and debugging the TDC chip. I am also grateful to Prof. Mark Aagaard and Prof. Cathy Gebotys for allowing me to use their lab equipment for testing my chips. Through many discussions, my colleagues Mohamed El Said, Ayman Hassan, Mohamed Maymandi-Nejad, and Mohamed Hassan shared many ideas and insights related to my research work. David Li helped me design the ROM encoder for my TDC chip. I am grateful to Wendy Boles for her help on administrative issues and to Phil Regier for his great computing resources support.

My appreciation to all my colleagues in the VLSI research group who were of great help and support. We spent wonderful times discussing all kinds of issues, technical and otherwise. In particular I would like to thank Mohamed Elgebaly, Hassan Hassan, and Ahmed Nour.

My wife, Rasha, shared with me every day throughout the course of this work. Her support, patience, and understanding played a major role in helping me finish this thesis. I am also grateful to my sister, Rasha, for her love, support, and encouragement. My daughter, Yumna, and son, Suhayb, brought so much joy to my life which has been and continue to be a great source of encouragement.

My deepest gratitude to my mother and father for their ever continuous support, encouragement, and prayers. No words of appreciation could ever reward them for all they have done for me. I am, and will ever be, indebted to them for all achievements in my life.

To my parents, Gamalaat Elmasry and Ahmed Nummer, with love and appreciation.

## **Table of Contents**

| Ał | ostrac  | t                                                                         | iii |

|----|---------|---------------------------------------------------------------------------|-----|

| Ac | know    | ledgements                                                                | V   |

| De | edicati | on                                                                        | vii |

| Li | st of T | Tables x                                                                  | iii |

| Li | st of F | <b>`igures</b>                                                            | kiv |

| Li | st of A | Abbreviations                                                             | iii |

| 1  | Intro   | oduction                                                                  | 1   |

|    | 1.1     | Motivation                                                                | 1   |

|    | 1.2     | Goals and Contributions                                                   | 2   |

|    | 1.3     | Thesis Organization                                                       | 3   |

|    | Refe    | rences                                                                    | 5   |

| 2  | Slow    | -Speed Timing Characterization and Testing of High-Speed Pipelined Datap- |     |

|    | aths    |                                                                           | 7   |

|    | 2.1     | Introduction                                                              | 7   |

| 2.2   | Review    | v of Techniques for Testing High-Speed Circuits Using Slow-Testers | 9  |

|-------|-----------|--------------------------------------------------------------------|----|

| 2.3   | Testing   | g Pipelines by Clock Shifting                                      | 16 |

| 2.4   | Test Ve   | ehicle: 16-bit Pipelined Multiplier                                | 19 |

| 2.5   | Design    | of the Clock Timing Circuit                                        | 22 |

| 2.6   | Modes     | of Operation                                                       | 26 |

|       | 2.6.1     | Normal Mode                                                        | 26 |

|       | 2.6.2     | DUT Test Mode                                                      | 26 |

|       | 2.6.3     | Clock Timing Circuit Test Mode                                     | 27 |

| 2.7   | Delay     | Fault Simulation Results                                           | 31 |

|       | 2.7.1     | Delay Fault Simulation for the Test Vehicle                        | 31 |

|       | 2.7.2     | Delay Fault Simulation for the Clock Timing Circuit                | 34 |

| 2.8   | Implen    | nentation and Test Setup                                           | 35 |

| 2.9   | Experi    | mental Results                                                     | 38 |

|       | 2.9.1     | Clock-Timing Circuit Test Mode Results                             | 38 |

|       | 2.9.2     | Pipeline Test Mode Results                                         | 39 |

|       | 2.9.3     | Normal Mode Results                                                | 42 |

| 2.10  | Conclu    | isions                                                             | 43 |

| Refe  | rences .  |                                                                    | 45 |

|       | iaitally_ | Controlled Delay Element with Monotonic and Linear Delay Charac    | _  |

| teris |           | Controlicu Delay Element with Monotonic and Elitear Delay Charac   | 47 |

|       |           |                                                                    |    |

| 3.1   |           | v of DCDE Implementation Techniques                                |    |

|       | 3.1.1     | DCDE using adjustable logic threshold                              | 50 |

|       | 3.1.2     | DCDEs using adjustable load capacitance                            | 51 |

|       | 3.1.3     | DCDEs using adjustable (dis)charge resistance                      | 54 |

| 3.2   | DCDE      | Design Considerations                                              | 60 |

3

|   | 3.3  | Proposed DCDE                                                               |

|---|------|-----------------------------------------------------------------------------|

|   | 3.4  | Designing the Proposed DCDE                                                 |

|   |      | .4.1 VCDE Design                                                            |

|   |      | .4.2 DVC Design                                                             |

|   | 3.5  | Simulation Results                                                          |

|   | 3.6  | Experimental Results                                                        |

|   | 3.7  | Conclusions                                                                 |

|   | Refe | nces                                                                        |

| 4 | An A | -Digital Phase Aligner with sub-2ps Resolution for Clock Skew Management 89 |

|   | 4.1  | Clock Skew Management Techniques                                            |

|   | 4.2  | Proposed All-Digital Phase Aligner Design                                   |

|   |      | 2.1 Digitally-Controlled Delay Lines and Related Control Circuitry 96       |

|   |      | .2.2 Phase Detector with Redundancy for PVT Tolerance                       |

|   |      | .2.3 ADPA Controller                                                        |

|   | 4.3  | ADPA Simulation Results                                                     |

|   | 4.4  | Chip Implementation and Experimental Results                                |

|   | 4.5  | Conclusions                                                                 |

|   | Refe | nces                                                                        |

| 5 | A 6- | t Flash Time-to-Digital Converter 117                                       |

|   | 5.1  | Review of Time-to-Digital Converter Implementations                         |

|   | 5.2  | Proposed TDC Architecture                                                   |

|   | 5.3  | Proposed TDC Implementation                                                 |

|   | 5.4  | Chip Implementation and Test Setup                                          |

|   | 5.5  | Experimental Results                                                        |

| Bibliography 1 |                             | 153 |

|----------------|-----------------------------|-----|

| 6              | Conclusions and Future Work | 149 |

|                | References                  | 145 |

|                | 5.6 Conclusions             | 141 |

## **List of Tables**

| 2.1 | Critical path delays through multiplier stages.                            | 22 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Number of delay elements between different nodes in the delay lines        | 27 |

| 2.3 | Test vehicle delay fault simulation results                                | 32 |

| 2.4 | Delay fault simulation results for the clock timing circuit                | 33 |

| 2.5 | Test results for the clock-timing circuit                                  | 37 |

| 2.6 | Test mode results for the test pipeline                                    | 42 |

| 3.1 | Summary of DCDE implementations (table provides reported experimental data |    |

|     | only).                                                                     | 49 |

| 3.2 | Sizes of the transistors in the (a) VCDE and (b) DVC used to design a DCDE |    |

|     | with seven delay steps of 5ps each                                         | 73 |

| 4.1 | Performance data for designs using deskew-based methodology.               | 95 |

# **List of Figures**

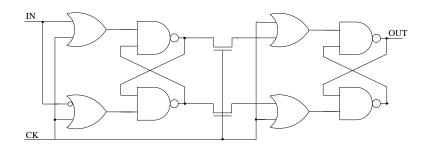

| 2.1  | Pulse-triggered flip-flop [1].                                         | 10 |

|------|------------------------------------------------------------------------|----|

| 2.2  | Controlled delay flip-flop [9]                                         | 11 |

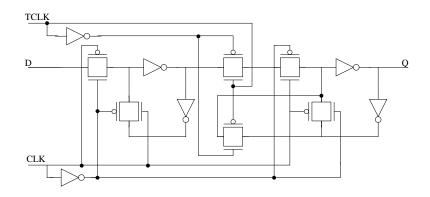

| 2.3  | CDFF operation. (a) Circuit model. (b) Normal mode. (c) Test mode      | 12 |

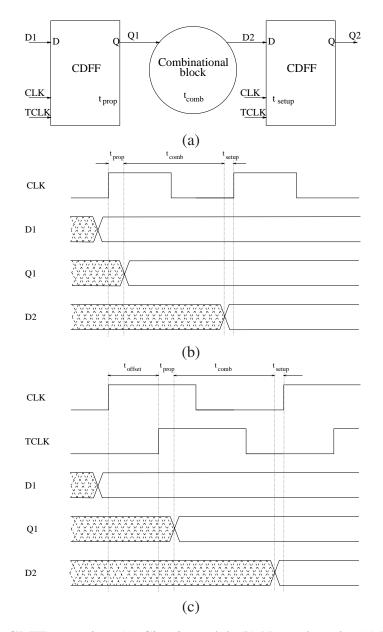

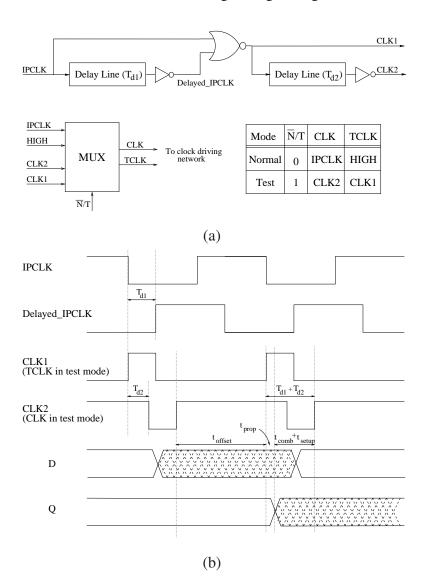

| 2.4  | Generating clock and test clock. (a) Block diagram. (b) Timing diagram | 14 |

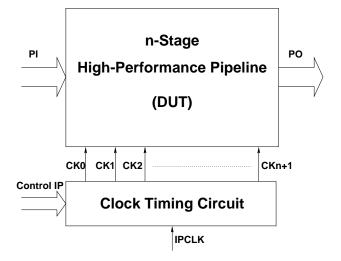

| 2.5  | Block diagram of the DUT and the clock timing circuit                  | 17 |

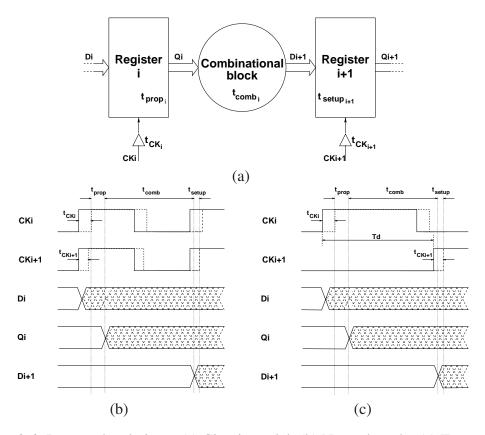

| 2.6  | Proposed technique. (a) Circuit model. (b) Normal mode. (c) Test mode  | 18 |

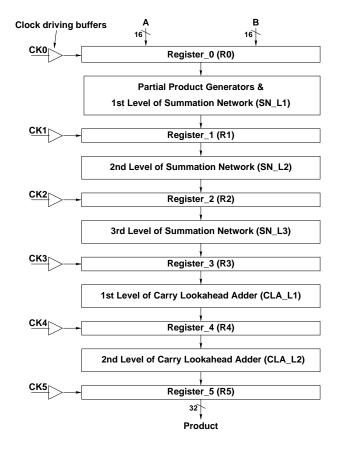

| 2.7  | Block diagram of the pipelined multiplier used as a test vehicle       | 20 |

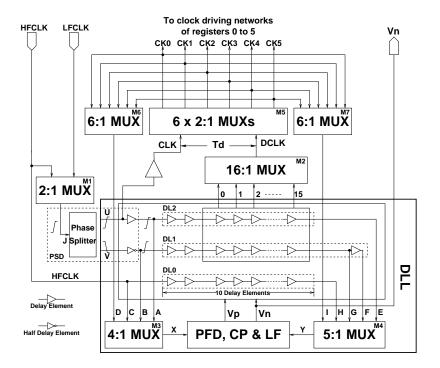

| 2.8  | Clock Timing Circuit (multiplexer select inputs are not shown)         | 23 |

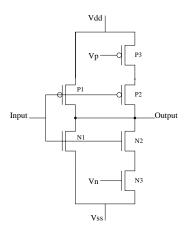

| 2.9  | Schematic diagram of half the delay element.                           | 24 |

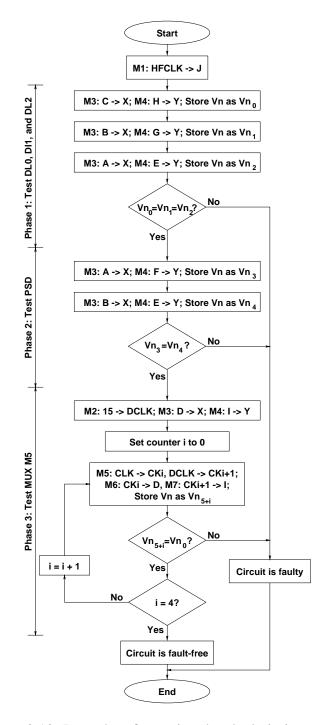

| 2.10 | Procedure for testing the clock timing circuit.                        | 29 |

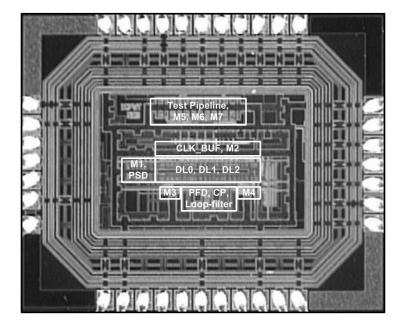

| 2.11 | Chip micrograph.                                                       | 35 |

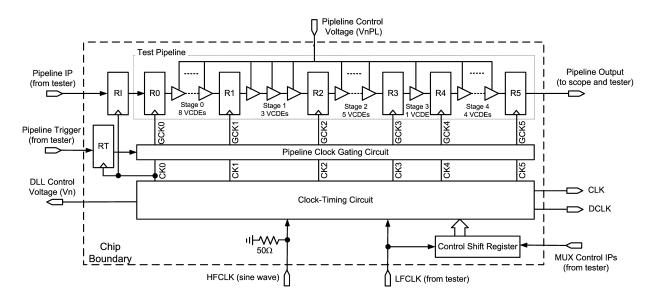

| 2.12 | Chip block diagram showing the schematic of the test pipeline          | 36 |

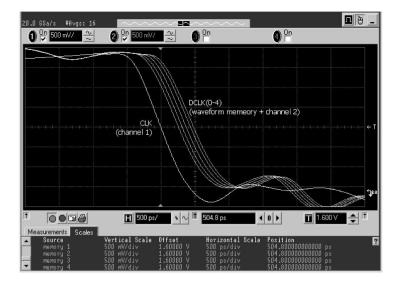

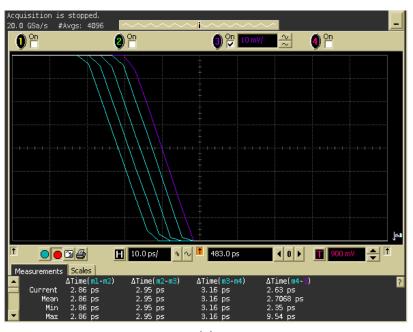

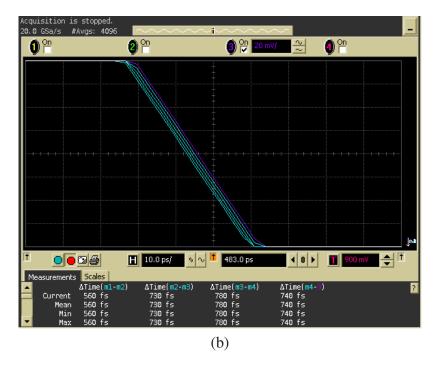

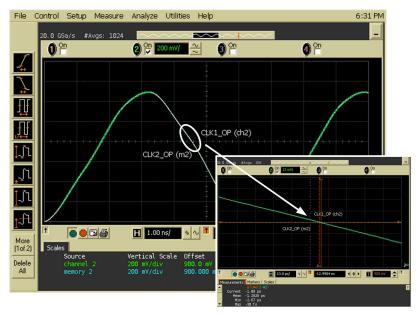

| 2.13 | CLK versus DCLK for taps 0-4 (using scope waveform memory)             | 39 |

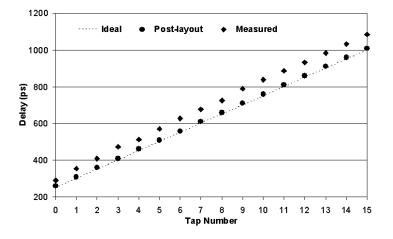

| 2.14 | CLK-DCLK delays for all taps in the clock-timing circuit.              | 40 |

| 2.15 | Pipeline test mode results for stage 3 (LFCLK: 50MHz)                  | 40 |

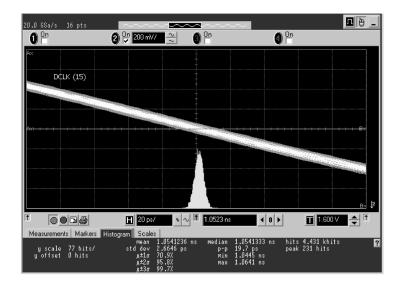

| 2.16 | Jitter histogram for DCLK (tap 15).                                    | 42 |

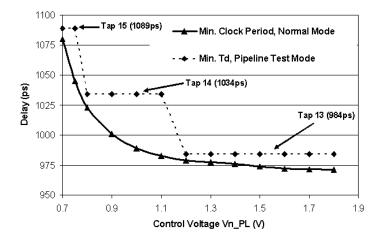

| 2.17 | Timing results for normal and test modes.                              | 43 |

| 3.1  | Schmitt trigger.                                                       | 50 |

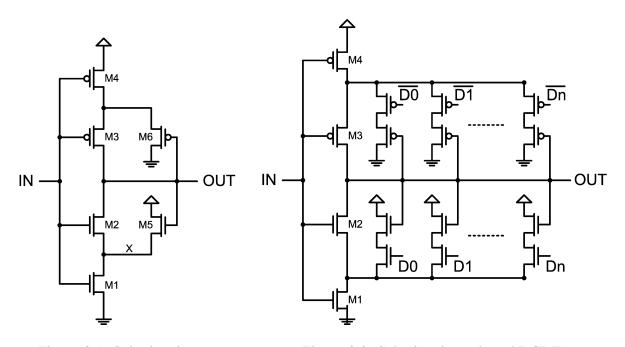

| 3.2  | Schmitt trigger-based DCDE                                                          | 50 |

|------|-------------------------------------------------------------------------------------|----|

| 3.3  | DCDE using bias dependence of gate capacitance                                      | 52 |

| 3.4  | DCDE using shunt capacitors.                                                        | 54 |

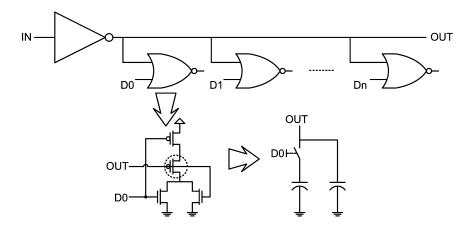

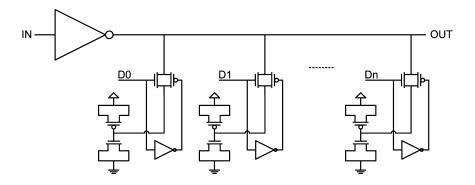

| 3.5  | Tri-state inverter.                                                                 | 55 |

| 3.6  | DCDE using tri-state inverters.                                                     | 55 |

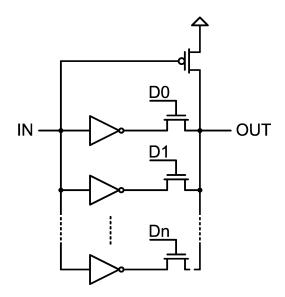

| 3.7  | DCDE using multiplexed inverters                                                    | 57 |

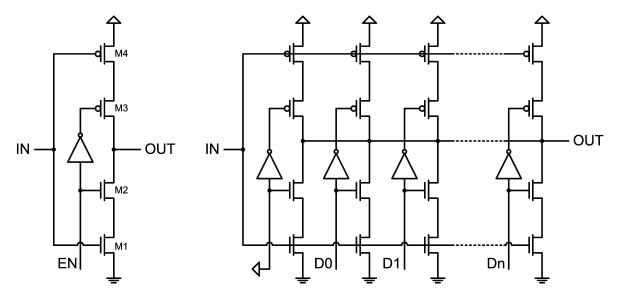

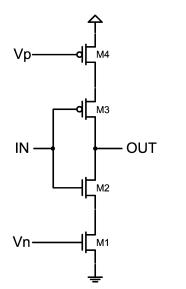

| 3.8  | Voltage-controlled delay element using current-starved inverter.                    | 57 |

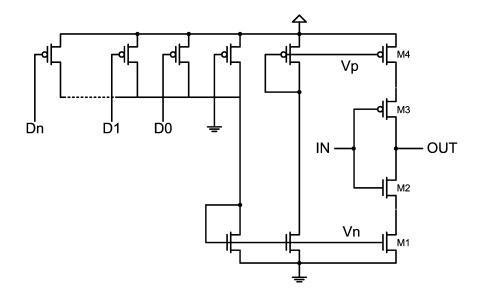

| 3.9  | DCDE using current-starved inverter                                                 | 57 |

| 3.10 | Transfer characteristics of DCDE using current-starved inverters with geometric     |    |

|      | sizing of control transistors [20]                                                  | 59 |

| 3.11 | DCDE using current-starved inverters with indirect delay control using binary-      |    |

|      | weighted transistors.                                                               | 61 |

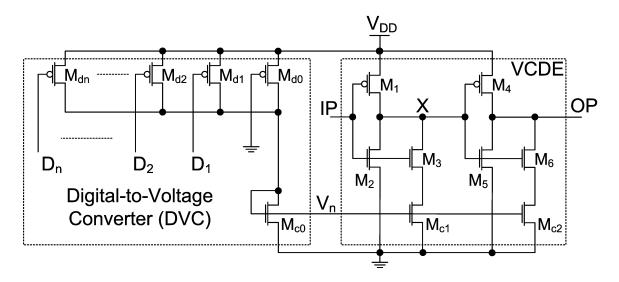

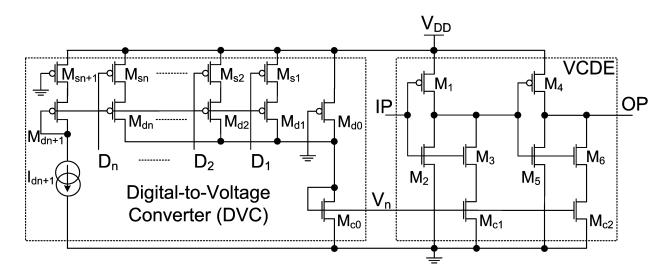

| 3.12 | Schematic diagram of the proposed DCDE                                              | 63 |

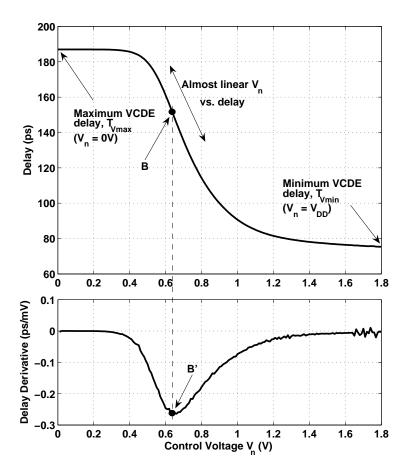

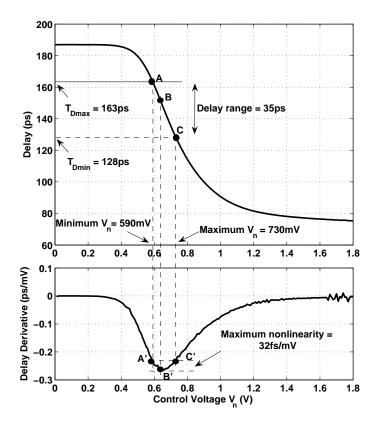

| 3.13 | Voltage-delay characteristics of the VCDE.                                          | 64 |

| 3.14 | VCDE design example.                                                                | 66 |

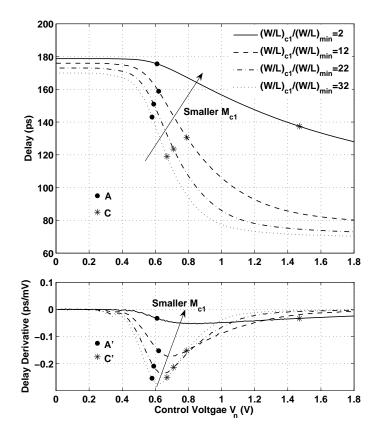

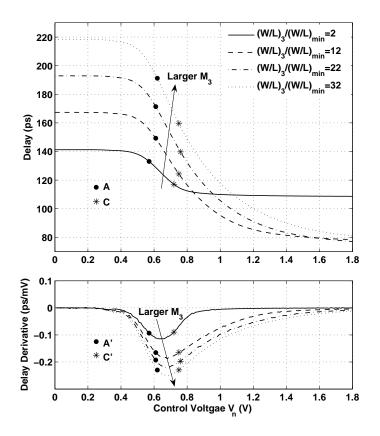

| 3.15 | Impact of the size of $M_{c1}$ on the voltage-delay characteristics of the VCDE for |    |

|      | $(W/L)_3/(W/L)_{min} = 15.$                                                         | 69 |

| 3.16 | Impact of the size of $M_3$ on the voltage-delay characteristics of the VCDE for    |    |

|      | $(W/L)_{c1}/(W/L)_{min} = 15.$                                                      | 70 |

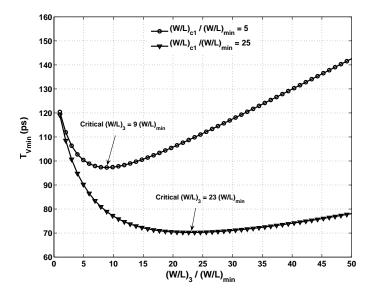

| 3.17 | Impact of the relative size of $M_{c1}$ and $M_3$ on the minimum delay of the VCDE, |    |

|      | $T_{V_{min}}$ ( $V_n = V_{DD}$ ).                                                   | 71 |

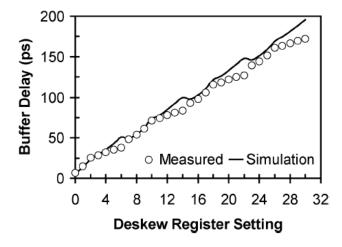

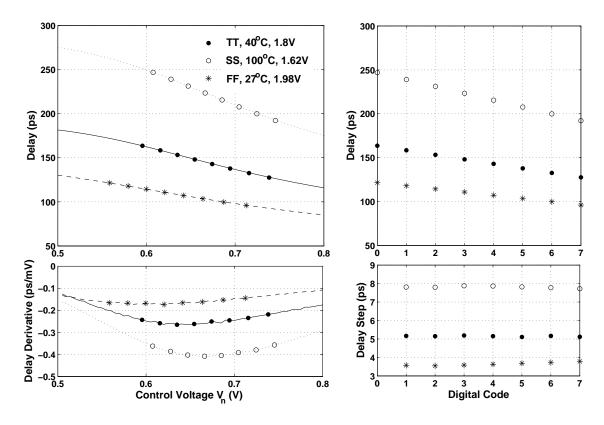

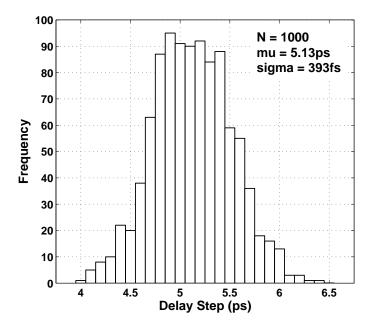

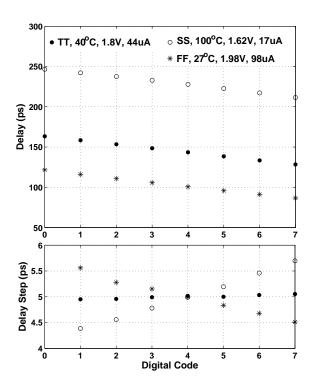

| 3.18 | Delay characteristics of the proposed DCDE.                                         | 74 |

| 3.19 | Monte Carlo analysis of the impact of process variation on the DCDE delay step.     | 75 |

| 3.20 | Schematic diagram of the controlled-current DCDE                                    | 76 |

| 3.21 | Simulation results of the CC-DCDE under typical and extreme PVT conditions                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | with $I_8$ adjusted for an average delay step of 5ps. $\ldots \ldots \ldots$ |

| 3.22 | Simulation results of the CC-DCDE under typical PVT conditions with five val-                                                                                                                |

|      | ues of $I_8$ giving average delay steps of 1, 2, 5, 7, and 8ps                                                                                                                               |

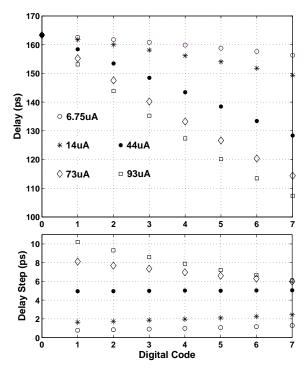

| 3.23 | DCDE and CC-DCDE chip micrograph                                                                                                                                                             |

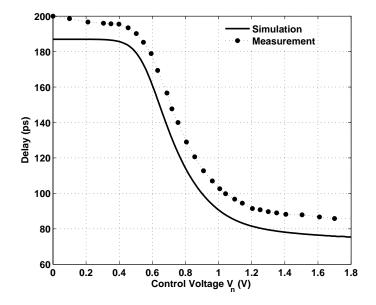

| 3.24 | Simulations vs. measurement results of the voltage-delay characteristics of the                                                                                                              |

|      | VCDE (DE5 on the test chip)                                                                                                                                                                  |

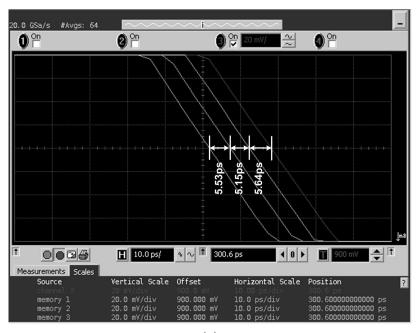

| 3.25 | Measurement results of the DCDE (DE2 on the test chip) for (a) codes 0 to 3 and                                                                                                              |

|      | (b) codes 3 to 7                                                                                                                                                                             |

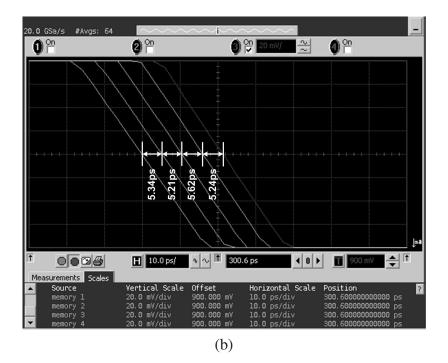

| 3.26 | Measurement results of the CC-DCDE (DE3 on the test chip) for $I_8 = 41 \mu A$ for                                                                                                           |

|      | (a) codes 0 to 3 and (b) codes 3 to 7                                                                                                                                                        |

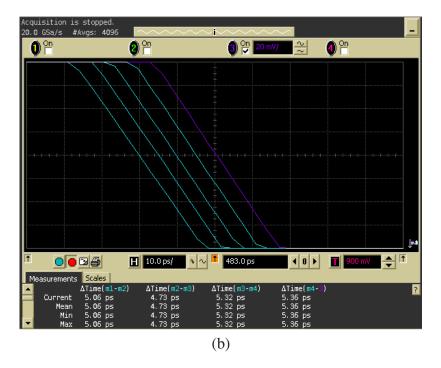

| 3.27 | Measurement results of the CC-DCDE (DE3 on the test chip) for codes 3-7 for                                                                                                                  |

|      | (a) $I_8 = 25\mu A$ and (b) $I_8 = 5\mu A$                                                                                                                                                   |

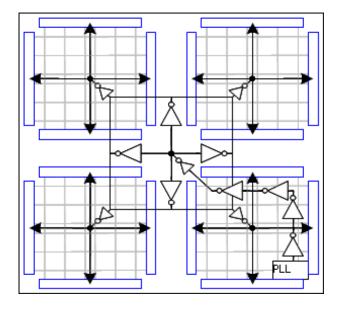

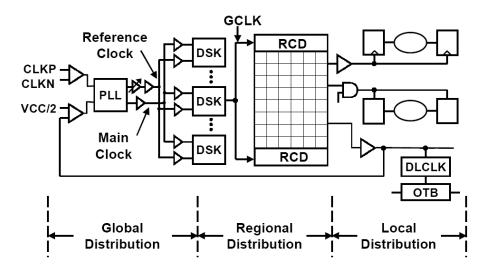

| 4.1  | Clock distribution of the Alpha 21264 microprocessor [1]                                                                                                                                     |

| 4.2  | Clock distribution of the Itanium microprocessor [27]                                                                                                                                        |

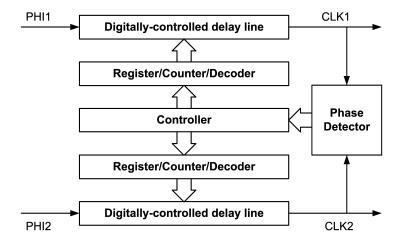

| 4.3  | Basic architecture of an all-digital phase aligner                                                                                                                                           |

| 4.4  | Architecture of proposed all-digital phase aligner                                                                                                                                           |

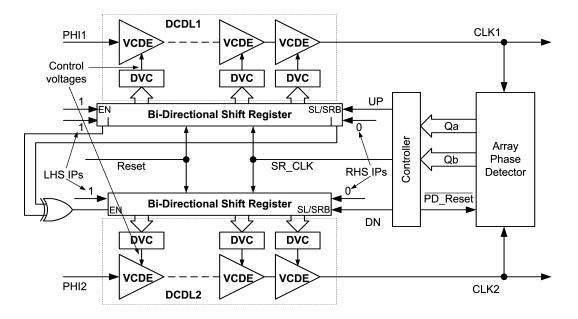

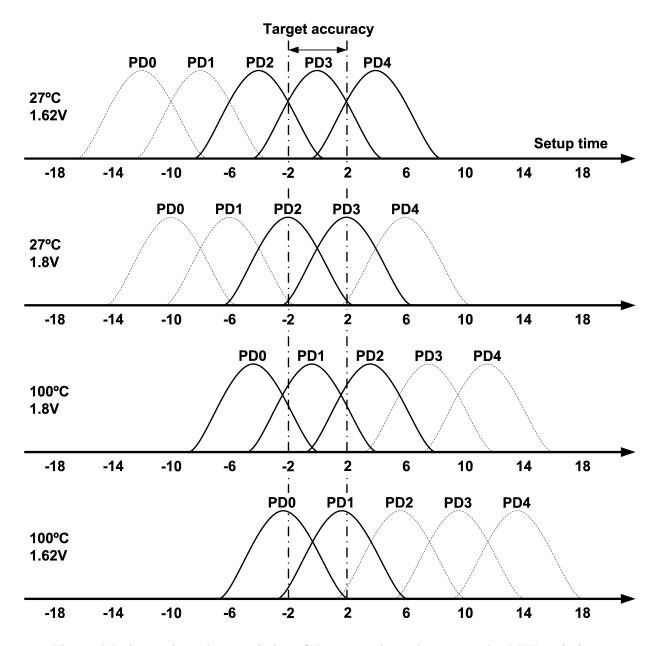

| 4.5  | Basic phase detector                                                                                                                                                                         |

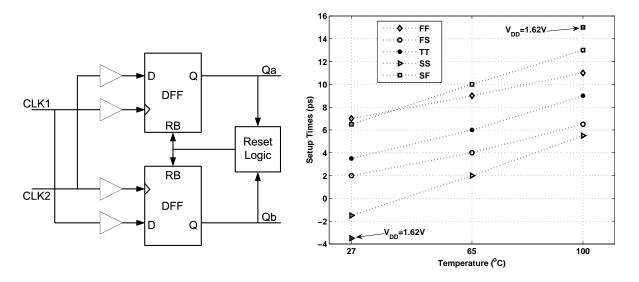

| 4.6  | DFF setup time vs. PVT variations                                                                                                                                                            |

| 4.7  | Setup time characteristics of the array phase detector under PVT variations 104                                                                                                              |

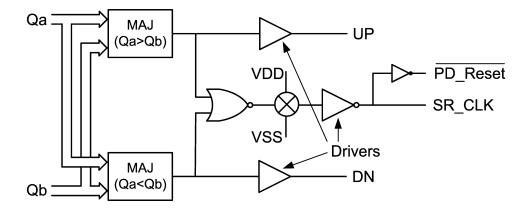

| 4.8  | Schematic of the ADPA controller                                                                                                                                                             |

| 4.9  | Timing relationship between ADPA signals                                                                                                                                                     |

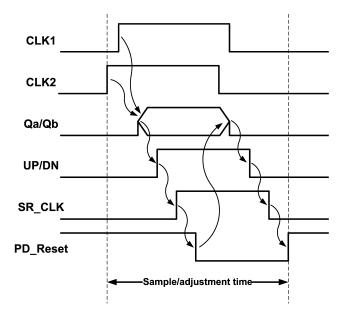

| 4.10 | Simulation example for the ADPA at 1GHz                                                                                                                                                      |

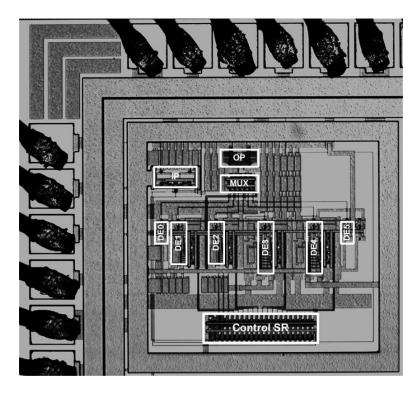

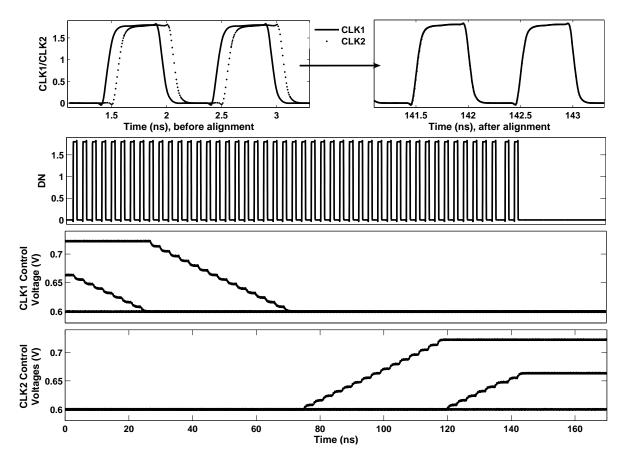

| 4.11 | ADPA test chip micrograph                                                                                                                                                                    |

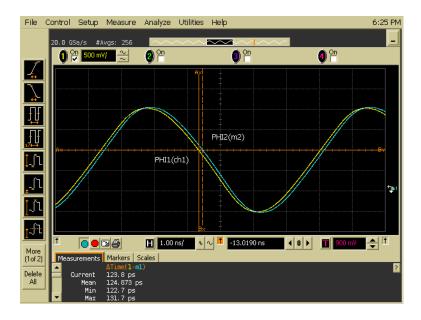

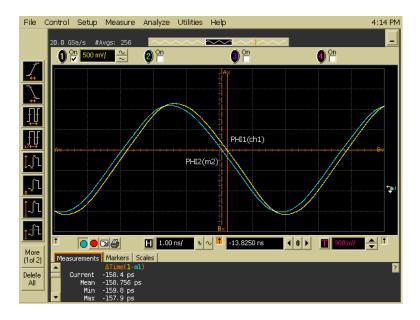

| 4.12 | Measurement results for PHI1 leading PHI2                                                                                                                                                    |

| 4.13 | Measurement results for PHI1 lagging PHI2                                                |

|------|------------------------------------------------------------------------------------------|

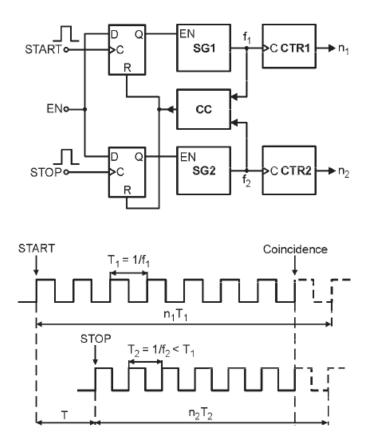

| 5.1  | TDC based on the Vernier delay line [17]                                                 |

| 5.2  | Circuit and operation example for time measurement using the Vernier tech-               |

|      | nique [20]                                                                               |

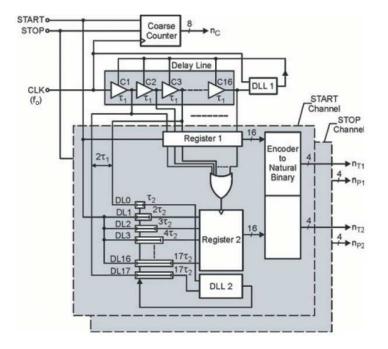

| 5.3  | Block diagram of a TDC with two level interpolating DLLs [20]                            |

| 5.4  | Proposed TDC architecture                                                                |

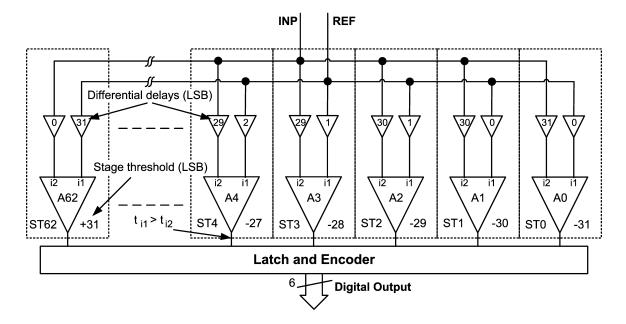

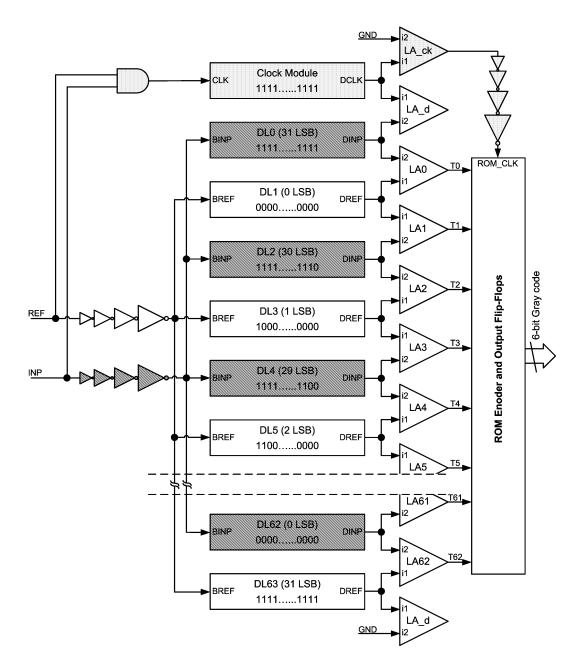

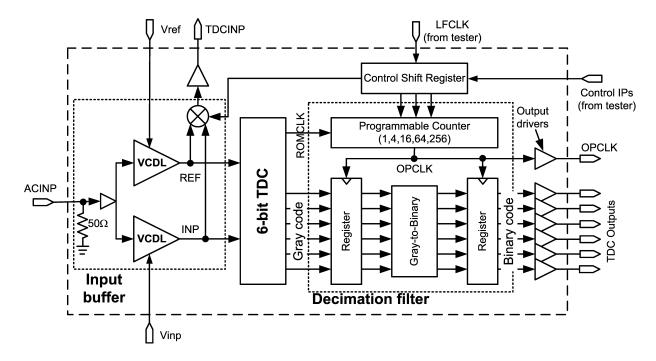

| 5.5  | TDC implementation                                                                       |

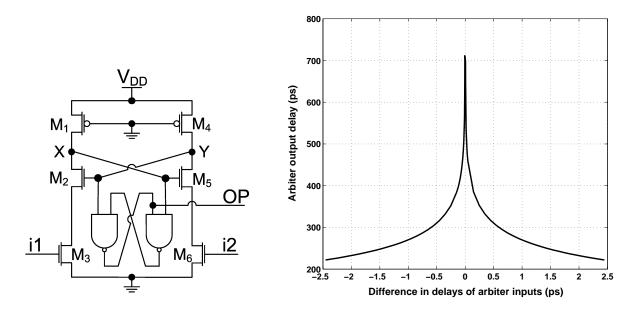

| 5.6  | Schematic of the latched arbiter                                                         |

| 5.7  | Metastability characteristics of the latched arbiter under <i>typical</i> conditions 129 |

| 5.8  | Block diagram of the TDC test chip                                                       |

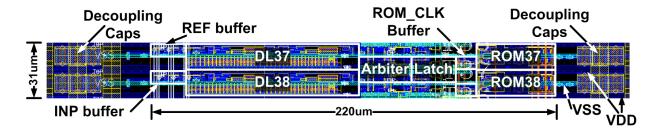

| 5.9  | TDC row layout for rows 37 and 38                                                        |

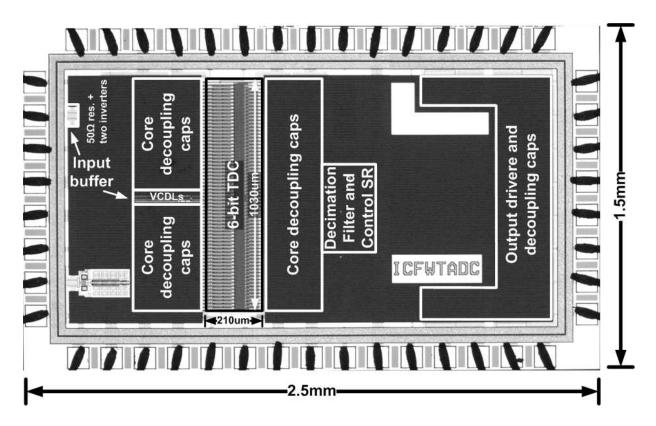

| 5.10 | TDC chip micrograph                                                                      |

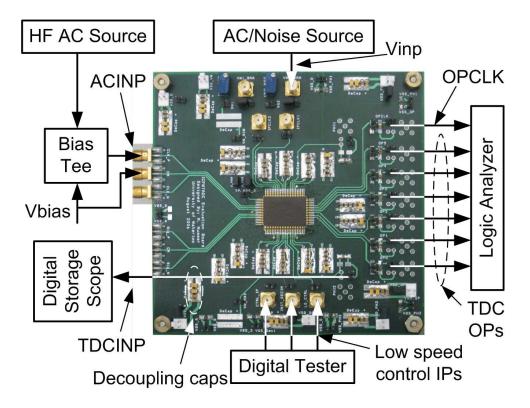

| 5.11 | TDC board and test setup                                                                 |

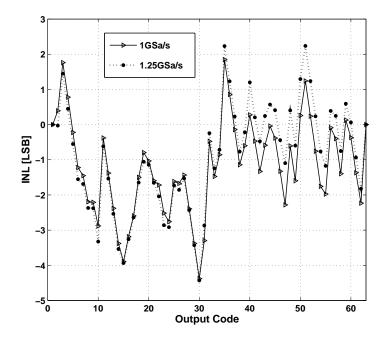

| 5.12 | Measured INL of the TDC at 1GSa/s and 1.25GSa/s                                          |

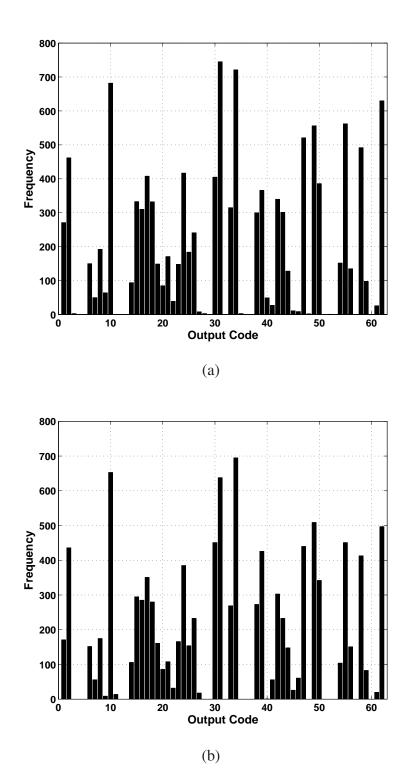

| 5.13 | Code density histograms for the TDC at (a) 1GSa/s and (b) 1.25GSa/s 139                  |

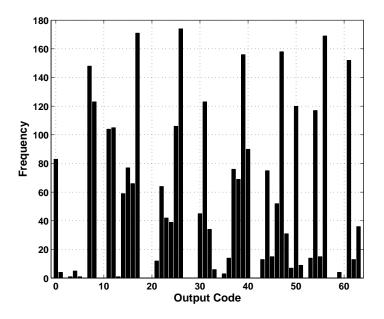

| 5.14 | Example code density histogram obtained using TDC model                                  |

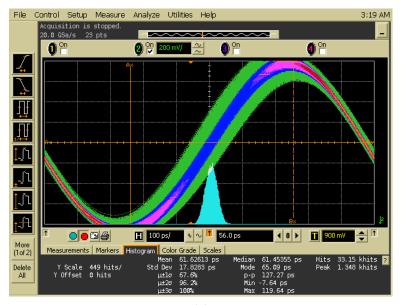

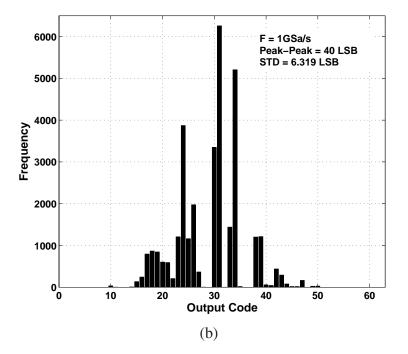

| 5.15 | Gaussian jitter measurement using (a) the scope and (b) the TDC running at 1GSa/s.143    |

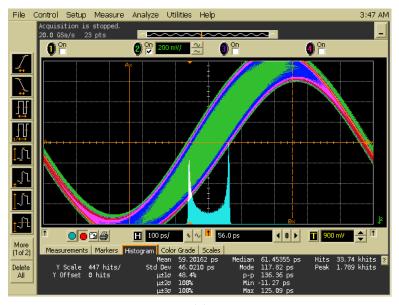

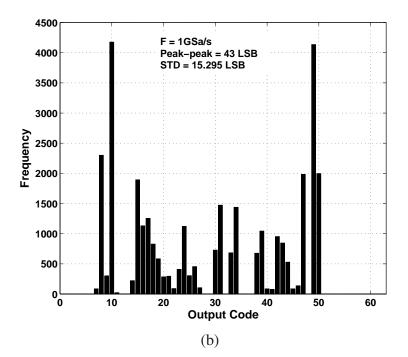

| 5.16 | Sinusoidal jitter measurement using (a) the scope and (b) the TDC running at             |

|      | 1GSa/s                                                                                   |

# **List of Abbreviations**

| ADC  | Analog-to-digital converter.                         |

|------|------------------------------------------------------|

| ADPA | All-digital phase-aligner.                           |

| ATE  | Automatic Test Equipment.                            |

| BIST | Built-in-self-test.                                  |

| CDFF | Controlled-Delay Flip-Flop.                          |

| CMOS | Complementary Metal Oxide Semiconductor.             |

| DCDE | Digitally-controlled delay-element.                  |

| DCDL | Digitally-controlled delay-line.                     |

| DFT  | Design-for-Testability.                              |

| DLL  | Delay-locked loop.                                   |

| DUT  | Device Under Test.                                   |

| IC   | Integrated circuit.                                  |

| INL  | Integral non-linearity.                              |

| ITRS | International Technology Roadmap for Semiconductors. |

| PD   | Phase detector.                                      |

| PLL  | Phase-locked loop.                                   |

| PSD  | Phase splitter and delay.                            |

| PVT  | Process, temperature, and (supply) voltage.          |

|      |                                                      |

- **TDC** Time-to-digital converter.

- **VCDE** Voltage-controlled delay-element.

- VCDL Voltage-controlled delay-line.

- **VDL** Vernier delay line.

- **VLSI** Very Large Scale Integration.

### **Chapter 1**

### Introduction

#### **1.1 Motivation**

Over the past 40 years, scaling of CMOS devices allowed for a steady improvement in performance and increase in the number of transistors integrated on the same die. High-speed microprocessors operating at multi-gigahertz are the norm of our time. Recently, a 9GHz integer execution unit in 65nm CMOS technology was reported [2]. The success of the CMOS processes in improving performance and increasing the level of integration compels manufacturers of high-volume devices to constantly adopt the new "digital" CMOS processes as soon as they are introduced.

The drive for higher performance is accompanied with increased emphasis on meeting timing constraints both at design time and during actual device operation. Timing uncertainties due to random variations and fabrication defects require additional design effort for testing and mitigation. This is becoming even more important with the increased delay variability due to process parameters, voltage, and temperature variations in modern deep-submicron technologies [1].

Fortunately, the advances in the performance of CMOS devices allow for the development

of circuit and architectural techniques that can provide precise control of the timing of digital signals. Such techniques can be used to address and to provide solutions to some of the emerging timing issues, either on the design front or on the characterization and testing fronts.

#### **1.2 Goals and Contributions**

The goals of the work presented in this thesis are to propose circuit and architectural techniques that can be used to achieve precise control of the timing of digital signals. These techniques need to be demonstrated through applications in timing characterization and control for high-speed state-of-the-art digital systems.

The key contributions of this thesis can be summarized in the following.

- 1. Proposed a methodology for slow-speed timing characterization of high-speed pipelined datapaths. The methodology uses a clock timing circuit to adjust the phases of the pipeline clocks in the test mode. An implementation of the clock timing circuit that achieves a timing resolution of 52.9ps in  $0.18\mu$ m CMOS technology is presented. The proposed implementation allows for the testing of the clock timing circuit itself. The basic methodology and the performance and feasibility of the specific implementation have been verified experimentally.

- Presented a comprehensive review of circuit techniques for implementing digitally-controlled delay-elements (DCDEs). A DCDE is used as the basic building block in many techniques that require precise timing of digital signals.

- 3. Proposed a DCDE design that has a monotonic and linear code-delay characteristics. The proposed DCDE maintains its linearity with process, temperature, and supply voltage

(PVT) variations. It also has other features that are considered desirable in many application such as possibility of achieving infinitesimally small delay steps and independently adjusting the delays of rising and falling inputs. Detailed analysis of the DCDE design tradeoffs has been presented. Two variations of the DCDE have been implemented on a test chip. Experimental results verify the linearity of the DCDE characteristics and the possibility of achieving infinitesimally (sub-1ps) small delay steps.

- 4. Proposed a design technique for achieving PVT tolerance in phase detectors using redundancy. The technique has been used to design an array phase detector (APD) with redundancy based on a basic phase detector (PD) structure.

- 5. Implemented an all-digital phase-aligner (ADPA) using the proposed DCDE with 2ps nominal resolution and an APD. The ADPA is designed for clock deskewing as the target application. The measured phase alignment range is from -264ps to +247ps which corresponds to an average DCDE step of 2.43ps. Phase alignment results demonstrate the effectiveness of the ADPA in achieving sub-2ps precision phase alignment.

- 6. Proposed a true flash architecture for implementing high-speed time-to-digital converters (TDCs) for real-time on-chip time measurement. The design uses the proposed DCDE with a delay step of 2.5ps. The architecture uses a self-timed approach for generating the internal clock used by the converter. Using this architecture, a conversion rate of 1.25GSa/s has been demonstrated experimentally in 0.18 $\mu$ m CMOS technology.

#### **1.3 Thesis Organization**

Following this introduction, the thesis has five chapters. Chapters 2, 3, 4, and 5 are dedicated to presenting the circuit and architectural techniques proposed by this work. Each of these four

chapter starts with a review of relevant background and previous work on the topic presented in the chapter and ends with a set of relevant references.

Chapter 2 presents a clock timing technique for slow-speed timing characterization of high speed pipelined datapaths. Design details of the clock timing circuit are presented. The viability of the proposed methodology is verified by performing delay fault simulations on a 16-bit pipelined multiplier. The chapter ends with presenting chip implementation details and experimental results.

Chapter 3 starts by reviewing DCDE application areas and previous implementations. The proposed DCDE implementation is then presented, along with detailed design methodology. The chapter ends with simulation as well as experimental results demonstrating the linearity and precision of the delay step obtainable using the proposed DCDE.

In chapter 4, a high-precision all-digital phase aligner design that uses the proposed DCDE and a PVT tolerant phase detector is presented. PVT tolerance is achieved using redundancy in the phase detector followed by majority voting. Simulation results are presented, followed by experimental results.

A TDC architecture based on the flash architecture used for analog-to-digital (ADC) converters is proposed in chapter 5. The chapter presents details of the proposed implementation and chip design followed by experimental results.

The thesis ends with a concluding chapter followed by a comprehensive bibliography of all references cited throughout the thesis.

Introduction

#### References

- [1] T.C. Chen. Where CMOS is Going: Trendy Hype vs. Real Technology. In *International Solid-State Circuits Conference Digest of Technical Papers*, pages 1–7, February 2006.

- [2] S.B. Wijeratne et al. A 9-GHz 65-nm Intel Pentium 4 Processor Integer Execution Unit. *IEEE Journal of Solid-State Circuits*, 42(1):26–37, January 2007.

### Chapter 2

# Slow-Speed Timing Characterization and Testing of High-Speed Pipelined Datapaths

#### 2.1 Introduction

Modern microprocessor and digital signal processor designs rely on high-speed pipelined datapaths to achieve performance goals. With the rapid advances in process technologies, the complexity of start-of-the-art integrated circuits is increasing steadily. Moreover, the drive for higher performance requires greater emphasis on cost-effective performance characterization and delayfault testing. The purpose of testing a VLSI device is to ensure, with reasonable confidence, that the device functions according to the design specifications. This testing must be achievable within certain economic constraints to keep the cost per device as low as possible.

Fundamentally, there are two ways in which a VLSI device can fail. It can fail *parametrically* in that the technology dependent electrical parameters such as voltage, current, capacitance, speed, or gain are out of the specifications. Or, it can fail *functionally* such that the device, independent of its electrical characteristics, performs an incorrect logic function. The objective

of most functional and parametric test techniques is to detect chips that are not working according to design specifications. If an IC passes both functional and parametric tests, it is assumed to be functional.

However, some of the "functional" ICs may be in fact marginal ICs. Marginal ICs contain flaws; defects in a chip that do not cause failures at normal operating conditions but degrade chip performance, reduce noise immunity, or draw excess supply current [2, 4]. Marginal ICs cause problems with reliability and must be detected before they are shipped. These chips can cause intermittent failures in the sense that even if they may pass production tests, they can fail to work in the field at different operating conditions. They may cause problems if the supply voltage changes during operation due to IR drops or simultaneous switching noise. If these chips are used for low-power applications, and if the defect inside the chip is causing abnormal static current flow, this may have serious consequences. The excess static current can cause early-life failures and accelerated chip wearout.

The most noticeable effects of marginal ICs on chip performance are timing failures in the form of delay flaws. Timing failures occur when the delay of the manufactured component is different from the designed delay. If the timing failure is such that the circuit fails to work at the designed speed but continues to be functional at a lower speed, it is called a delay fault. On the other hand, a circuit has a delay flaw (non-operational delay failure) if there is a timing failure but the circuit continues to work at the designed speed [3].

There are many test techniques that can be used for detecting marginal ICs. The common procedure in most of these techniques is to change the operating environment so as to provoke the flaws within the chip. A review of such techniques was presented in [4].

### 2.2 Review of Techniques for Testing High-Speed Circuits Using Slow-Testers

Following Moore's Law for the past three decades, the silicon die cost of integrated circuits has decreased as the number of transistors per die has continued to increase. In contrast, during the same period, the cost of testing integrated circuits in high-volume manufacturing has been steadily increasing. It is predicted that the cost of testing transistors may actually surpass the cost of fabricating them within the next one or two decades [8]. As ICs become more highly integrated, the job of diagnosing failures becomes increasingly difficult. Marching into the deep submicron regime poses many challenges to the testing problem. With smaller geometries, higher speeds, and increased interconnects, it is more likely to have an increase in the tendency for small imperfections in the fabrication process to result in actual failures. That is why it is necessary to use advanced test techniques that enable the testing process to cope with advances in semiconductor technology.

Using DFT/BIST techniques that allow testing high-performance circuits with slow-speed testers is one way to tackle the problem of high-performance circuit testing. The creation of a low frequency test mode in digital circuits was first introduced by Agrawal and Chakraborty [1]. In their proposal, a quantifiable, externally controlled delay is added such that high-performance testing can be carried out with relatively slow-speed testers. They used a pulse-triggered flip-flop in which a dynamic latch is introduced inside a traditional master-slave flip-flop as shown in Figure 2.1. The resulting three-latch structure has two modes of operation; normal mode and test mode. In normal mode, the intermediate latch must hold data for most of the clock period while the other two latches remain transparent. In test mode, flip-flop delay can be modulated by changing clock's pulse width. This allows for testing combinational logic and interconnects for delay faults with a lower clock frequency. Although the concept of adding delay in test mode is

Figure 2.1: Pulse-triggered flip-flop [1].

elegant, this implementation has some important shortcomings as the dynamic latch makes the flip-flop operation sensitive and timing critical.

Shashaani and Sachdev proposed the controlled delay flip-flop (CDFF) as an alternative to the pulse-triggered flip-flop [9]. In this technique an additional test mode clock is used to control the delay of the flip-flop. The main advantages of the CDFF over the pulse-triggered flip-flop are the stable operation and improved performance in normal mode.

Figure 2.2 illustrates a gate level implementation of the CDFF. The transfer of data from the master latch to the slave latch is controlled through a control logic and depends on the relative timing of the clock (CLK) and the test clock (TCLK). To illustrate the operation of the CDFF, a simple model of digital VLSI circuits is depicted in Figure 2.3(a). In this model, a combinational block is sandwiched between two sequential blocks (registers, flip-flops,...etc). In normal mode, TCLK is kept high ensuring normal flip-flop operation (Figure 2.3(b)). Under this condition, the normal mode clock period ( $T_{NM}$ ) is given by:

$$T_{NM} = t_{prop} + t_{comb} + t_{setup}$$

(2.1)

where  $t_{prop}$  is the propagation delay of the flip-flop,  $t_{comb}$  is the time window allowed for the combinational block to evaluate its input,  $Q_1$ , and produce the input of the next sequential block,

Figure 2.2: Controlled delay flip-flop [9].

$D_2$ , and  $t_{setup}$  is the setup time of the flip-flop.

In test mode, a tester programmed time offset of the clock is used to generate TCLK. Consequently, flip-flop output,  $Q_1$ , appears after an additional delay equal to the time offset between the two clocks. This scenario is illustrated in Figure 2.3(c). Under this condition, the test mode clock period is given by:

$$T_{TM} = t_{prop} + t_{comb} + t_{setup} + t_{offset}$$

(2.2)

where  $t_{offset}$  is the time offset between the clock and the test clock. The test mode clock period should be large enough to accommodate all delay terms in Equation 2.2. It is clear from this equation that increasing  $t_{offset}$  allows the circuit to be tested at a frequency lower than the normal mode frequency. In other words, clock frequency can be reduced while the combinational circuit delays are tested with the same delay margins.

In 2001, Nummer and Sachdev [6] proposed a methodology for generating the clock and the test clock for a device using CDFFs in a way that allows the test mode clock frequency to be reduced arbitrarily. This is done through an on-chip clock generation circuit. When generating the clock and the test clock for a circuit using CDFF to improve testability, one has to take into consideration the timing requirements for correct operation. For the CDFF to function properly, the timing of the clock and the test clock must be carefully adjusted to accommodate both the

Figure 2.3: CDFF operation. (a) Circuit model. (b) Normal mode. (c) Test mode.

setup time  $(t_{setup})$  and the propagation delay  $(t_{prop})$  of the flip-flop. For the combinational block, it is necessary to have the flexibility to change the value of  $t_{comb}$  so as to determine, with reasonable accuracy, the delay through this block and test the circuit for delay faults. This is also important in order to enable performance binning<sup>1</sup> to know how well the circuit meets its timing specifications.

In test mode, reducing clock frequency while maintaining correct timing operation for all parts of the circuit means that, if the clock frequency becomes very low,  $t_{offset}$  has to be extremely large. As suggested in [9], the test clock can be generated as a delayed version of the clock with a delay of  $t_{offset}$ . The problem with this approach is that a slow tester is a low specification device. It is normally difficult for such a device to provide very large time offset with state-of-the-art timing accuracy. As an alternative, H. Speek et al. [10] suggested the use of two programmable duty-cycle controllers and a programmable delay line to generate the clock and the test clock in test mode. Using their design, reducing the test mode clock frequency to a very small value requires a large delay line to generate the required delay with appropriate timing resolution.

Careful examination of the timing diagram in Figure 2.3(c) shows that, instead of generating the test clock by delaying the clock in test mode, the clock can be generated by delaying and inverting the test clock. Generating the clock this way makes  $t_{offset}$  (which is the key factor in reducing the test mode clock frequency) independent on the relative timing of the two clocks and allows its value to be increased arbitrarily. Increasing  $t_{offset}$  while keeping all the other terms in Equation 2.2 unchanged implies a reduction in test mode clock frequency without affecting the time window allowed for the evaluation of the combinational block. It is clear that by doing this, the test mode clock frequency can be reduced with no lower limit.

Figure 2.4(a) depicts a block diagram of a system for generating the clock and the test clock. The input clock, IPCLK, is a rated frequency signal in normal mode and a low frequency, 50%

<sup>&</sup>lt;sup>1</sup>Performance binning is a test procedure used to segregate devices in a number of bins depending on their maximum operating frequency.

Figure 2.4: Generating clock and test clock. (a) Block diagram. (b) Timing diagram.

duty cycle signal in test mode. A multiplexer (MUX) is used to select the mode of operation through the mode select input  $(\overline{N}/T)$ . For normal mode operation  $(\overline{N}/T=LOW)$ , IPCLK passes through the MUX to the CLK driving network while TCLK is kept high. In test mode  $(\overline{N}/T=HIGH)$ , two delay lines are used to generate both CLK and TCLK. This is illustrated by the timing diagram in Figure 2.4(b). A delay line is used to generate a clock with pulse width  $T_{d1}$  (CLK1). This clock is selected by the MUX to be the test clock, TCLK. CLK1 passes through the second delay line (with delay  $T_{d2}$ ), resulting in CLK2. The MUX selects CLK2 to be CLK in test mode. Figure 2.4(b) also shows the D and Q signals of a CDFF to illustrate the relationships amongst the various timing parameters of the system in Figure 2.3(a) on one side and the delays  $T_{d1}$  and  $T_{d2}$  and the frequency of IPCLK, *f*, on the other side . These relationships can be expressed by the following two equations.

$$T_{d1} + T_{d2} = t_{prop} + t_{comb} + t_{setup}$$

$$\tag{2.3}$$

$$1/f = T_{d1} + T_{d2} + t_{offset} (2.4)$$

Assuming fixed f,  $t_{prop}$ , and  $t_{setup}$ , these equations suggest that a change in either  $T_{d1}$ ,  $T_{d2}$ , or both, leads to an equal change in  $t_{comb}$ . This allows the combinational block to be tested for delay faults by changing the time slot allowed for the evaluation of its inputs. For constant  $T_{d1}$  and  $T_{d2}$ , changing f causes only  $t_{offset}$  to change without affecting the operation of neither the flip-flop or the combinational block.

Although using CDFFs can considerably facilitate the testing process, there are two main concerns associated with this technique.

- The need for two clocks requires the creation of two clock propagation networks. Both

networks need to have the same high-performance characteristics (small propagation delays, minimum clock skew, etc.). This is important to maintain the delay between the two

clocks. The need for two high-performance clocks can result in an increase in the cost of

the chip and complicates the process of clock generation and propagation.

- 2. Careful examination of the structure of the CDFF in Figure 2.2 shows that the path of dataflow is different in test mode when compared to normal mode operation. This means

that the CDFF propagation delays being tested in test mode is not the actual normal mode propagation delay.

In this chapter, a methodology for testing high-performance pipelines using slow-speed testers is proposed. The technique depends on creating shifted versions of a low-speed clock in test mode. The technique adds no extra hardware in the data path of the pipeline and therefore has virtually no performance penalty.

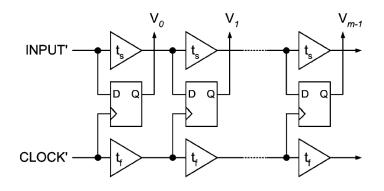

#### 2.3 Testing Pipelines by Clock Shifting

The basic idea in the proposed technique is demonstrated in Figure 2.5. In this study, it is assumed that the registers in the pipeline use a single phase common clock and are built using flip-flops as the storage element. A clock timing circuit is used to control clocks driving all registers in the pipeline. The idea is to use shifted version(s) of the input clock, IPCLK, to control the timing of data flow through the pipeline in the test mode. In order to achieve that, each register in the pipeline has to have a separately routed clock, as shown in Figure 2.5. This results in higher complexity of clock generation and propagation. The clock net of a pipelined circuit normally consists of a tree of buffers. Special care should be given to balance the load of the different clock tree branches in order to keep the skew between the different clock signals within acceptable limits. In the proposed technique, only those buffers close to the clock timing circuit require extra design and layout effort. Due to the small number of these upstream buffers, the extra effort imposed by the technique would not be substantial.

The normal and test mode operation of the circuit is illustrated in Figure 2.6, showing stage *i* in the pipeline  $(0 \le i \le n)$ . In normal mode, a single phase high-frequency clock is used for all registers in the pipeline. This is shown in Figure 2.6(b). As a result, the operation of the circuit

Figure 2.5: Block diagram of the DUT and the clock timing circuit.

depends on the period of this clock. The delay of stage i,  $t_{d_i}$ , can be expressed using

$$t_{d_i} = t_{prop_i} + t_{comb_i} + t_{setup_{i+1}} + (t_{CK_i} - t_{CK_{i+1}})$$

(2.5)

where  $t_{prop_i}$  is the propagation delay of register *i*,  $t_{comb_i}$  is the delay of the *ith* stage combinational block,  $t_{setup_{i+1}}$  is the setup time of register i + 1, and  $(t_{CK_i} - t_{CK_{i+1}})$  is the difference between the delays through the clock driving networks of registers *i* and i + 1. For the pipeline to function correctly, the normal mode clock period,  $T_{NM}$ , has to be at least equal to the largest stage delay, i.e.

$$T_{NM} \ge MAX_{i=0}^{n}(t_{d_i}) \tag{2.6}$$

In the test mode, a delayed version of the clock is used to test the pipeline. This is illustrated in Figure 2.6(c). In order to test stage *i*, a delayed version of the input clock, IPCLK, with delay  $T_d$  is applied to register *i* + 1, while the original clock is used for all other registers. The test mode clock period,  $T_{TM}$ , has to be at least equal to the normal mode clock period. It is clear that

Figure 2.6: Proposed technique. (a) Circuit model. (b) Normal mode. (c) Test mode.

using a larger value of  $T_{TM}$  means that it is possible to test the pipeline in the test mode using a slow-speed tester. Setting  $T_d$  to be equal to  $t_{d_i}$  allows the *ith* stage to operate within its normal mode timing constraints while the whole circuit is running at a lower frequency. As a result, a slow-speed tester can be used for performance binning and delay-fault testing. In the test mode, the tester supplies a slow-speed input clock as well as test vectors for the target stage. These vectors are supplied at the rate of the slow-speed clock. After a pre-determined number of clock cycles, the tester reads the results at the same rate of the slow-speed clock. This technique does not require any changes in the design of the registers or the combinational blocks and therefore has virtually no performance penalty.

For the proposed technique to achieve its goals, it is essential for the value of  $T_d$  to be controllable within state-of-the-art timing accuracy. Furthermore, the design should provide the ability to program  $T_d$  in order to bin the device under test (DUT) for performance. This feature also allows different stages in the pipeline to be tested even if they have unbalanced delays. For these reasons, an on-chip clock timing circuit is used to generate the delayed version of the input clock and to control the clocks propagated to the different stages in the pipeline.

# 2.4 Test Vehicle: 16-bit Pipelined Multiplier

In order to verify the benefits of the proposed technique, a 16-bit pipelined multiplier is designed and utilized as a test vehicle. Parallel multiplication is done in three steps. In the first step, the two operands are used to generate partial products whose number depends on the type of encoding algorithm used. The second step is to add the partial products together in a summation network which reduces the partial products to two operands. The product is generated in the final step by adding the resulting two operands using a carry propagate adder.

In our design, no encoding is used to generate the partial products. This results in a number

Figure 2.7: Block diagram of the pipelined multiplier used as a test vehicle.

of partial products equal to the size of the multiplier (16). These partial products are added in the summation network using 4-2 compressors as the main component. A 4-2 compressor accepts 4 partial sums and reduces them to two [5]. In order to reduce the 16 partial products to 2 operands, this has to be done in three levels of 4-2 compression. A carry-lookahead adder with conditional sum select [7] is used to generate the product from these two operands.

The multiplier is implemented with five pipelined stages, as shown in Figure 2.7. The first stage is used to generate the 16 partial products and reduce them to 8 partial sums after the first level of the summation network. The second and third levels of the summation network are implemented in the second and third stages of the pipeline. The final addition is done in the last two stages.

Pipeline stages are separated by registers to control the timing of data flow through the multiplier. Static flip-flops are used as the storage elements in all registers. As shown in Figure 2.7, each register is controlled by a separate clock provided by the clock timing circuit. Details of the design of this circuit are given in the next section.

Performance characterization of the multiplier is carried out in order to find its maximum operating frequency and the critical path through each stage of the pipeline. These results are shown in Table 2.1. The delays shown include the propagation delay of the register feeding the stage, the setup time of the register accepting the output of the stage, and the difference in delays of the clock driving networks of the input and output registers (refer to Equation 2.5). As shown in Table 2.1, the first stage (SN\_L1) has the largest delay and the operating frequency of the multiplier is determined by this stage. This delay is equal to 715ps which translates to a maximum operating frequency of 1.4GHz.

| Pipeline stage | Critical path delay (ps) |

|----------------|--------------------------|

| SN_L1          | 715                      |

| SN_L2          | 655                      |

| SN_L3          | 655                      |

| CLA_L1         | 665                      |

| CLA_L2         | 615                      |

Table 2.1: Critical path delays through multiplier stages.

# 2.5 Design of the Clock Timing Circuit

This section provides design details of the clock timing circuit used for the test vehicle. A number of issues have to be taken into account in the design of the clock timing circuit in order to ensure proper delay-fault testability of the pipeline.

- 1. **Programmability and resolution:** The delay,  $T_d$ , should be programmable for two reasons: (i) to allow DUT performance binning , and (ii) to allow paths of different delays to be tested for delay faults. The resolution with which  $T_d$  is varied should be high enough to allow the detection of small delay faults.

- 2. Timing accuracy: Process, temperature, and supply voltage variations have a large effect on the delays of the circuit. The design should compensate for these effects such that the value of  $T_d$  will be as desired regardless of these variations.

- 3. **Tester edge placement inaccuracy (jitter):** A slow-speed tester is generally a low specification device. It has a low timing resolution and high edge placement inaccuracy, or jitter. The design should have the ability to suppress the tester's jitter in order to minimize its effect on the timing resolution and accuracy of the clock timing circuit.

- 4. **Testability:** Adding hardware to enhance testability begs the question: how can we ensure the functionality of the extra hardware? is it testable? Answering these questions is very

Figure 2.8: Clock Timing Circuit (multiplexer select inputs are not shown).

important and is a challenge to most design-for-testability techniques.

Figure 2.8 shows the clock timing circuit used in this design (multiplexer select inputs are not shown). This circuit is designed using CMOS  $0.18\mu$ m technology provided through TSMC. It comprises three delay lines, a phase splitter & delay circuit, a DLL, and a number of multiplexers. The design allows  $T_d$  to vary between 250ps and 1000ps with 50ps increments (resolution). These are design variables and it is up to the designer to choose the values suiting a specific circuit or application. For our test vehicle, the range of  $T_d$  is reasonable to allow us to do performance binning and test for delay faults. A 50ps timing resolution is high enough considering the maximum operating frequency of the multiplier. The design and operation of the different blocks used in the clock timing circuit is described below.

Figure 2.9: Schematic diagram of half the delay element.

The delay element used in the delay lines is built using static inverters connected in parallel with current-starved inverters. Delay line DL0 and the high-speed clock, HFCLK, are used to calibrate delay lines DL1 and DL2 in order to generate the required values of  $T_d$ . The calibration process ensures correct test mode timing regardless of PVT (process, temperature, and/or supply voltage) variations. Ideally, HFCLK should be generated on-chip through a phase-locked loop. For the purpose of this study, HFCLK is supplied from an external source which allows us to adjust the frequency of this clock in order to gain insight into the performance and the functionality of our design.

The design goal is to achieve a timing resolution of 50ps. Using the DLL to calibrate the delay lines requires a relatively balanced rising- and falling-edge delays, otherwise the clock might disappear before reaching the end of the delay line. Using the target technology ( $0.18\mu$ m CMOS), it was not possible to design a balanced delay element that achieves 50ps delay regardless of PVT variations (i.e. for all possible extreme cases). We achieved a timing resolution of 50ps using the PSD circuit and the two delay lines DL1 and DL2. The delay element is designed to have a delay of 100ps and the PSD circuit adjusts the delay between the inputs to DL1 and DL2 to 50ps (half delay-element delay) to achieve a timing resolution of 50ps.

With 10 delay elements in DL0, setting the period of HFCLK to 1ns and closing the DLL loop using this delay line results in control voltages  $V_n$  and  $V_p$  that adjust the total delay across DL0 to one clock period. Since these voltages control all three delay lines, the delays of all delay elements in the circuit are thus adjusted to 100ps. DL1 and DL2 consist of 11 and 10 delay elements, respectively. The main function of these two delay lines is to generate a delayed clock signal, DCLK, with programmable delays with respect to the reference clock, CLK (Fig. 2.8). Programmability is achieved through multiplexer M2.

Multiplexer M5 consists of six 2:1 multiplexers. It is used to control the clocks feeding all registers in the pipeline (CK0 to CK5). Depending on the mode of operation and the pipeline stage to be tested, M5 sets the clock of each register to either CLK or DCLK.

Closing the DLL loop using various combinations of the inputs to multiplexers M3 and M4 allows great flexibility for testing the clock-timing circuit itself. As a result, most of the extra hardware in our design can be tested simply by comparing values of the DLL output,  $V_n$ , when different signals are used to close the loop. This is achieved using multiplexers M1, M3, M4, M6, and M7 as is illustrated in the next section. The number of stages that can be tested using the proposed clock-timing circuit depends only on the design of multiplexer M5. As a result this design can be easily scaled depending on the pipeline to be tested. Depending on the size of M5 and in order to facilitate its testing, M6 and M7 need to be designed accordingly.

The proposed clock timing circuit takes into account all the issues mentioned at the beginning of this section. Programmability is achieved through DL1, DL2, and the multiplexer M2. Using a DLL allows the design to achieve the same timing accuracy regardless of process, temperature, and/or supply voltage variations. The DLL with a number of multiplexers help ensure the functionality of the clock timing circuit itself. With the help of the PLL, tester clock jitter is not allowed to propagate to DL0. It also has no effect on the timing accuracy of signals generated from DL1 and DL2. The area overhead due to this design is estimated to be 100 gates per pipeline stage. This should be acceptable for medium to large pipelined circuits. It is important to note that matching between the different components in the design is essential to ensure correct timing even with small local process, temperature and/or supply voltage variations. This can be achieved through circuit layout techniques similar to those used for analog circuits.

# 2.6 Modes of Operation

The clock timing circuit operates in three modes. In *normal mode* the pipeline is used to perform the function it is designed for. In the *DUT test mode*, the clock timing circuit is used to verify the performance of the DUT and to test it for delay faults. In the *clock timing circuit test mode*, the clock timing circuit is tested to ensure its ability to give a correct image about the performance of the pipeline.

#### 2.6.1 Normal Mode

In normal mode, the control inputs of multiplexers M1 and M5 are set such that IPCLK propagates to all registers in the pipeline. As a result, the whole pipeline runs using the same clock ensuring normal operation. The remaining part of the clock timing circuit serves no function in normal mode, and can be turned off. This is important to reduce the effect the clock timing circuit has on normal mode power consumption of the chip.

#### 2.6.2 DUT Test Mode

This mode is used to verify the performance of the DUT and test it for delay faults. The pipeline is tested one stage at a time. For every target path, two vectors are used to test the circuit. The first vector initializes the DUT, while the second vector activates the target path of the stage to be

| Nodes   | # of delay elements |

|---------|---------------------|

| A and E | 10                  |

| B and G | 10                  |

| C and H | 10                  |

| A and F | $10\frac{1}{2}$     |

| B and E | $10\frac{1}{2}$     |

Table 2.2: Number of delay elements between different nodes in the delay lines.

tested. Using multiplexer M2,  $T_d$  is set according to the expected delay of that path. Depending on the stage to be tested, multiplexer M5 is configured to set one of the register's clocks to DCLK and all other clocks to CLK. For example, to test stage 3 in the pipeline, clocks CK0, CK1, CK3, and CK5 are set to CLK while CK4 is set to DCLK. As a result, data flows between registers 3 and 4 within normal mode timing constraints. For all other stages, the low frequency clock allows operation under relaxed timing. This is important to ensure that delay faults in these stages do not affect the target path and hence the stage under test. This procedure is repeated for every path to be tested until the DUT is tested completely.

#### 2.6.3 Clock Timing Circuit Test Mode

In this mode, the DLL, with the help of multiplexers M1, M3, M4, M6, and M7, is used to characterize and verify the performance of the clock timing circuit. Multiplexer M1 is set to allow the high-frequency clock, HFCLK, to propagate through DL1 and DL2. The clock timing circuit is tested in three phases as shown in Figure 2.10. In the first phase, all three delay lines (excluding the last delay element in DL1) are tested. The second phase is used to test the PSD circuit. This is done by verifying that the delay between nodes A and B is equal to half delay-element delay. The third phase is used mainly to test multiplexer M5. This phase also covers multiplexers M6, M7, and a small part of M2. Each of the three phases cover parts of multiplexers M3 and M4, such that these two multiplexers are fully testable. In this design, only M1 and most

of M2 are not testable. Compared to the rest of the clock timing circuit and the DUT, this is a very small area of the circuit. Additionally, delay faults in M1 do not impact the operation of the circuit. Fully testing M2 would require additional hardware which itself may not be testable.

#### Phase 1: Testing DL0, DL1, and DL2

In this phase, delay lines DL0, DL1, and DL2 are tested between nodes C and H, B and G, and A and E, respectively. Table 2.2 gives the number of delay elements between the different nodes in the clock timing circuit. The first three entries in the table have the same number of delay elements. As a result, closing the DLL loop with these node pairs one at a time, should result in very close values of  $V_n$  (monitored off-chip) for all three configurations. As shown in Figure 2.10, the test in this phase is done in four steps:

- 1. Close the DLL loop using C and H ( $M3 : C \to X; M4 : H \to Y$ ). Measure  $V_n$  and record it as  $V_{n_0}$ .

- 2. Close the DLL loop using B and G (M3 :  $B \rightarrow X$ ; M4 :  $G \rightarrow Y$ ). Measure  $V_n$  and record it as  $V_{n_1}$ .

- Close the DLL loop using A and E (M3 : A → X; M4 : E → Y). Measure V<sub>n</sub> and record it as V<sub>n2</sub>.

- 4. Compare  $V_{n_0}$ ,  $V_{n_1}$ , and  $V_{n_2}$ . If the differences between the three values are within acceptable limits, the three delay lines are considered to be free of delay faults.

Ideally, the three values should be equal. Mismatch between the delay elements and the different components in the DLL would result in some differences. Characterization is necessary to define how much difference due to mismatch and process variations is acceptable. In this context, it is assumed that only a single delay fault exists in the circuit. It is worth noting that it

Figure 2.10: Procedure for testing the clock timing circuit.

is highly unlikely to have the exact same amount of delay fault in two of or all three delay lines. In addition to DL0, DL1, and DL2, the test in this phase covers paths through multiplexers M3 and M4 used to close the DLL loop (A-X, B-X, C-X, E-Y, G-Y, and H-Y).

#### Phase 2: Testing the Phase Splitter & Delay Circuit

Referring to Table 2.2, the delay between nodes A and F on one side and nodes B and E on the other are both equivalent to  $10\frac{1}{2}$  delay elements. This is only true if the two outputs of the PSD circuit (A and B) are exactly half delay-element delay apart. These observations are used to test the PSD circuit for delay faults. As shown in Figure 2.10, the test is done first by closing the DLL loop using nodes A and F. When locked, DLL output  $V_n$  is recorded as  $V_{n_3}$ . Similarly,  $V_{n_4}$  is obtained by closing the DLL loop through nodes B and E. For fault-free PSD, the difference between  $V_{n_3}$  and  $V_{n_4}$  should be within acceptable limits (defined through characterization). The test in this phase covers the G-F-Y path as well.

#### Phase 3: Testing Multiplexer M5

Phase 3 of the clock timing circuit test procedure is used to test multiplexer M5. This is done with the help of multiplexers M6 and M7. The main idea is to set the delay between CLK and DCLK ( $T_d$ ) to one cycle of HFCLK (1ns). The different paths in M5 are tested two at a time. As shown in Figure 2.10, to test the paths from CLK to  $CK_i$  and DCLK to  $CK_{i+1}$  (where *i* is any number between 0 and 4), M5 is set accordingly and M6 and M7 are used to close the DLL loop using nodes  $CK_i$  and  $CK_{i+1}$ . Under these conditions, if all signal paths are free of delay faults, when locked, the DLL output,  $V_n$ , should be equal to the values obtained in phase 1 of the test procedure (for fault free DL0, DL1, and DL2). In addition to M5, the test in this phase covers M6, M7, the 15-DCKL path in M2, the D-X path in M3, the I-Y path in M4, and the buffer used for CLK.

# **2.7 Delay Fault Simulation Results**

Several simulations were carried out to test the proposed design and to verify the possibility of testing the DUT and detecting small delay faults at low frequency. Furthermore, delay fault simulations for the clock timing circuit are done in order to demonstrate the ability to test and characterize this circuit. In all such simulations, delay faults are inserted using buffers and delay elements. Using active elements to add extra delays ensures the existence of a pre-determined delay fault without degrading the quality (rise and fall times) of the delayed signals.

#### 2.7.1 Delay Fault Simulation for the Test Vehicle

Delay faults are inserted in the test vehicle one at a time using buffers. Simulations are carried out on a number of paths in the DUT. For every target path, two vectors are used to test the circuit. The first vector initializes the DUT while the second vector activates the target path. The delay of a given path depends on the input vectors of the circuit. As a result, for every stage in the pipeline, the critical path and its delay might change depending on the applied vectors. For all paths tested in the simulations, activation vectors are chosen such that these paths are the critical paths in their pipeline stage for these vectors. As mentioned before, the design allows adjustment of  $T_d$  such that paths of different delays can be tested for small delay faults.

Delay fault simulation results for the test vehicle are shown in Table 2.3. The test is done at an input clock frequency of 100MHz. Delay faults of 50ps are inserted in each path one at a time.  $T_d$  from the clock timing circuit is set to the next higher value compared to the delay of the target path. Under these conditions, the multiplier gives incorrect output for all paths tested in our simulations, as shown in Table 2.3. The left half of the table gives the delays of the different paths and the value of  $T_d$  used to detect a 50ps delay fault in each path. The right half of the table gives the test vectors used for each path as well as the fault-free and faulty products of the

| Path # | Pipeline | Path       | $T_d$ | Vector | Input | Input | Product      | Product   |

|--------|----------|------------|-------|--------|-------|-------|--------------|-----------|

|        | stage    | delay (ps) | (ps)  | type   | А     | В     | (fault-free) | (faulty)  |

| 1      | SN_L1    | 715        | 750   | Init.  | 0002  | FFFF  | 0001 FFFE    | 0001 FFFE |

|        |          |            |       | Activ. | 0000  | FFFF  | 0000 0000    | 0000 0008 |

| 2      | SN_L1    | 685        | 700   | Init.  | 000C  | FFFF  | 000B FFF4    | 000B FFF4 |

|        |          |            |       | Activ. | 0008  | FFFF  | 0007 FFF8    | 0007 FFF0 |

| 3      | SN_L2    | 655        | 700   | Init.  | 0001  | FFFF  | 0000 FFFF    | 0000 FFFF |

|        |          |            |       | Activ. | 0000  | FFFF  | 0000 0000    | 0000 0040 |

| 4      | SN_L2    | 620        | 650   | Init.  | 0070  | FFFF  | 006F FF90    | 006F FF90 |

|        |          |            |       | Activ. | 0040  | FFFF  | 003F FFC0    | 003F FF80 |

| 5      | CLA_L1   | 665        | 700   | Init.  | 0000  | FFFF  | 0000 0000    | 0000 0000 |

|        |          |            |       | Activ. | FFFF  | FFFF  | FFFE 0001    | FFFD 0001 |

| 6      | CLA_L1   | 425        | 450   | Init.  | FFFF  | FFFF  | FFFE 0001    | FFFE 0001 |

|        |          |            |       | Activ. | 0000  | FFFF  | 0000 0000    | 0001 0000 |

| 7      | CLA_L2   | 615        | 650   | Init.  | 0000  | FFF0  | 0000 0000    | 0000 0000 |

|        |          |            |       | Activ. | FFE0  | FFF0  | FFD0 0200    | FFC0 0200 |

| 8      | CLA_L2   | 415        | 450   | Init.  | FFE0  | FFF0  | FFD0 0200    | FFD0 0200 |

|        |          |            |       | Activ. | 0000  | FFF0  | 0000 0000    | 0010 0000 |

Table 2.3: Test vehicle delay fault simulation results.

multiplier. The extent of delay fault that goes undetected is a function of the slack between the delay of the path and the value of  $T_d$  used to test it. A path with larger slack will have a larger undetectable delay fault. For example, in the case of path #2, it is expected that delay faults as small as 15ps should be detectable using the same value of  $T_d$ . On the other hand, for path #3, it will take a delay fault of at least 45ps to cause the timing failure. The situation is worse if the target path is not the critical path for the applied vectors. In general, delay fault detection is dependent on the target path delay. Most of the delay fault testing techniques have similar limitations. Balancing path delays is the most commonly used method to alleviate this problem.

| Fault # | Fault    | Faulty | Delay      | $V_{n_0}$ | $V_{n_1}$ | $V_{n_2}$    | $\triangle V_n$ |

|---------|----------|--------|------------|-----------|-----------|--------------|-----------------|

|         | location | Path   | fault (ps) | mV        | mV        | mV           | mV              |

| F1      | DL0      | C-H    | 60         | 633       | 611.5     | 611.5        | 21.5            |

| F2      | DL1      | B-G    | 100        | 611.5     | 649       | 611.5        | 37.5            |

| F3      | DL2      | A-E    | 200        | 611.5     | 611.5     | <b>691.7</b> | 80.2            |

| F4      | M3       | A-X    | 60         | 611.5     | 611.5     | 594.2        | -17.3           |

| F5      | M3       | B-X    | 100        | 611.5     | 583.3     | 611.5        | -28.2           |

| F6      | M3       | C-X    | 200        | 554       | 611.5     | 611.5        | -57.5           |

| F7      | M4       | E-Y    | 60         | 611.5     | 611.5     | 634          | 22.5            |

| F8      | M4       | G-Y    | 100        | 611.5     | 648.7     | 611.5        | 37.2            |

| F9      | M4       | H-Y    | 200        | 697       | 611.5     | 611.5        | 85.5            |

(a) Faults detected in phase 1 (fault-free  $V_n$  is 611.5mV)

| Fault # | Fault    | Faulty | Delay      | $V_{n_3}$ | $V_{n_4}$ | $\triangle V_n$ |

|---------|----------|--------|------------|-----------|-----------|-----------------|

|         | location | Path   | fault (ps) | mV        | mV        | mV              |

| F10     | PSD      | J-A    | 60         | 609.8     | 651.5     | -41.7           |

| F11     | PSD      | J-B    | 100        | 669       | 597.9     | 89.1            |

| F12     | M4       | F-Y    | 200        | 720       | 628.6     | 91.4            |

(b) Faults detected in phase 2 (fault-free  $V_n$  is 628.6mV)

| Fault # | Fault    | Faulty   | Delay      | $V_n$ | $\triangle V_n$ |

|---------|----------|----------|------------|-------|-----------------|

|         | location | Path     | fault (ps) | mV    | mV              |

| F13     | M2       | 15-DCLK  | 60         | 633.2 | 21.7            |

| F14     | M5       | DCLK-CK4 | 100        | 647   | 35.5            |

| F15     | Buffer   | U-CLK    | 200        | 554.8 | -56.7           |

(c) Faults detected in phase 3 (fault-free  $V_n$  is 611.5mV)

Table 2.4: Delay fault simulation results for the clock timing circuit.

#### 2.7.2 Delay Fault Simulation for the Clock Timing Circuit

Delay fault simulations for the clock timing circuit were carried out in order to verify the ability to characterize the performance of the circuit. 15 delay faults are inserted in different locations of the circuit one at a time. These fault are generated using the same delay element used in the design. The delay of the delay element is at its minimum value when  $V_p = V_{ss}$  and  $V_n = V_{dd}$ . This value is 60ps, and hence the smallest delay fault used in the simulations is 60ps. Larger delays are achieved using larger values of  $V_p$  and smaller values of  $V_n$ . The test is done according to the procedure in Figure 2.10. The results are shown in Tables 2.4(a), (b), and (c), showing faults detected in each phase of the clock timing circuit test procedure.

A fault detectable in phase 1 or phase 3 of the test procedure causes only one value of  $V_n$  ( $V_{n_0}$ ,  $V_{n_1}$ , or  $V_{n_2}$  for phase 1 or  $V_{n_{5+i}}$  for phase 3) to deviate from the fault-free value. That is why for faults detected in phase 1 and phase 3, the last column in each table gives the difference in  $V_n$  compared to the fault-free value. This is different from faults detectable in phase 2, where the fault causes both  $V_{n_3}$  and  $V_{n_4}$  to deviate in opposite directions from the fault free value. For faults detected in phase 2,  $\triangle V_n$  in Table 2.4(b) is computed as the difference between  $V_{n_3}$  and  $V_{n_4}$ .

A positive  $\triangle V_n$  indicates that the delay seen by the DLL is larger than it should be. As a result, the DLL causes the voltage to increase in to order to compensate for the extra delay. The opposite is true for negative  $\triangle V_n$ . For a certain delay fault, the larger the value of  $\triangle V_n$ , the easier it is to observe the error due to the fault. As shown in Table 2.4, the smallest value of  $\triangle V_n$  is 17.3mV which can be easily measured off-chip. These results demonstrate our ability to test the clock timing circuit for delay faults. This is important to ensure its ability to give a true image about the operation and performance of the DUT.

Figure 2.11: Chip micrograph.

# 2.8 Implementation and Test Setup

The clock-timing circuit in Fig. 2.8 has been implemented in  $0.18\mu$ m CMOS technology. The chip micrograph is shown in Fig. 2.11 and Fig. 2.12 illustrates its block diagram. The layout of the chip is done such that the delay elements and the various components in the clock-timing circuit are closely matched. The core area of the chip is  $700 \times 500\mu m^2$ , out of which  $500 \times 300\mu m^2$  is dedicated to the clock-timing circuit. At a supply voltage of 1.8V, a 1GHz HFCLK, and a 50MHz LFCLK, the clock-timing circuit consumes 13.6mW.