### **ASP-DAC 2004** Contents

Highlighte

| riigiiiigiito                            | _  |

|------------------------------------------|----|

| Welcome to ASP-DAC 2004                  | 6  |

| Sponsorship                              | 7  |

| Organizing Committee                     | 8  |

| Technical Program Committe               | 10 |

| University LSI Design Contest Committee  | 16 |

| Steering Committee                       | 17 |

| University LSI Design Contest            | 19 |

| Electronic Design and Solution Fair 2004 | 20 |

| Invitation to ASP-DAC 2005               | 22 |

| Keynote Addresses                        | 23 |

| Technical Program                        | 25 |

| Tutorials                                | 52 |

| ASP-DAC 2004 at a Glance                 | 57 |

| Registration                             | 61 |

| Registration Form                        | 63 |

| Information                              | 66 |

| Accommodations                           | 69 |

| Hotel Reservation Form                   | 71 |

| Access to Pacifico Yokohama              | 73 |

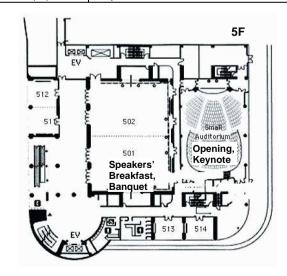

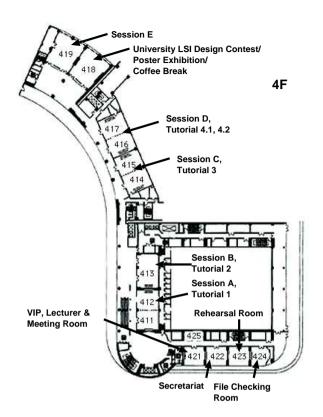

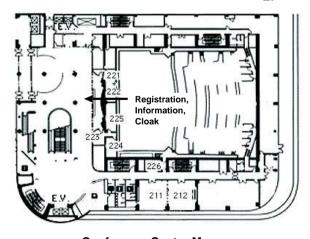

| Venue Map/ Room Assignment               | 74 |

### **Highlights**

### **Keynote Addresses**

2

Wednesday, January 28, 9:00-10:00

"CITRIS: The Center for Information Technology Research in the Interest of Society at the University of California"

Dr. Gary L. Baldwin - Executive Director, CIT-RIS. University of California. Berkeley. USA

Friday, January 30, 9:00-10:00

"System Level Design Technology for Realizing an Ambient Intelligent Environment" Dr. Rudy Lauwereins - Vice President, IMEC. Belgium

### **Special Sessions**

1A: Wednesday, January 28, 10:15-12:15, Room 411/412 "Invited Talks: Selected European Activities in SoC Low Power Design Methodologies and Research Networking" **2A:** Wednesday, January 28, 13:30-15:30, Room 411/412 "Embedded Tutorial + Reguler Session: Embedded System Applications"

**3E:** Wednesday, January 28, 16:00-18:00, Room 419 "Panel Discussion: Opportunities with the Open Architecture Test System"

Organizers: K. Hatayama - Renesas Technology

R. Raisuman -Advantest America R&D

Center

Moderator: C. Wu - National Tsing Hua University R. Rajsuman -Advantest America R&D Panelists:

Center

Y. Nishimura - Renesas Technology S. Chakradhar -NEC Laboratories of America

A. Merschon - Guide Technologies

D. Petrich - Wavecrest

T. Tada - Tokushima Bunri University

K. Cheng - University of California Santa Firing

Lines: Barbara

> Y. Okuda -ITC Asian Subcommittee member, Sony

**4A:** Thursday, January 29, 9:00-10:30, Room 411/412 "Invited Talks: C-Based Design Examples"

**6A:** Thursday, January 29, 13:30-15:30, Room 411/412 "Embedded Tutorial: RF Modeling and Design Methodoloav"

6C: Thursday, January 29, 13:30-15:30, Room 414/415 "Presentation + Poster Disscussion: University Design Contest"

**7A:** Thursday, January 29, 16:30-18:00, Room 411/412 "Invited Talks: Future of ITS Technologies in the Ubiquitous Society"

7A-1: The Integration of Vehicles Into a Ubiguitous Computing Environment -Computing and **Networking Technologies for Vehicles-**

N. Tokitsu (Internet ITS Consortium, Japan)

**9A:** Friday, January 30, 13:30-15:30, Room 411/412

"Embedded Tutorial: DFM in nm-Process Generation"

9C: Friday, January 30, 13:30-15:30, Room 414/415

"Panel Discussion: Future Reconfigurable Computing System"

Organizers: M. Kawamura - Toshiba

H. Amano - Keio University

Moderator: **S. Goto** -Waseda University

M. Motomura -NEC Panelists:

T. Sato -IP Flex

S. Trimberger -Xilinx

B. Plunkett -Quick Silver

R. Lauwereins - IMEC

### **Embedded Invited Talks**

**1A-1:** Wednesday, January 28, 10:15-10:55

Fast, Predictable, and Low-energy Memory References through Architecture-aware Compilation

P. Marwedel, M. Verma, L. Wehmever (Univ. of Dortmund, Germany), S. Steinke (KOSTAL GmbH & Co. KG. Luedenscheid, Germany), U. Helmig (Univ. of Dortmund, Germany)

**1A-2:** Wednesday, January 28, 10:55-11:35

Predictable Design of Low Power Systems by Pre-Implementation Estimation and Optimiza-

W. H. Nebel (Oldenburg Univ. and OFFIS, Germany)

1A-3: Wednesday, January 28, 11:35-12:15

EuroSoC: Towards a Joint University/Industry Research Infrastructure for System on Chip and System in Package

A. A. Jerraya (TIMA Laboratory, France)

4A-1: Thursday, January 29, 9:10-9:50

C-based Behavioral Synthesis and Verification Analysis on Industrial Design Examples

K. Wakabayashi (NEC, Japan)

**4A-2:** Thursday, January 29, 9:50-10:30

Using C Based Logic Synthesis to Bridge the Productivity Gap

C. Sullivan, A. Wilson, S. Chappell (Celoxica Ltd, England, UK)

### **Embedded Tutorials**

2A-1: Wednesday, January 28, 13:30-14:30

**Toward Mobile Phone Linux**

Y. Nakamoto (NEC, Japan)

6A-1: Thursday, January 29, 13:30-14:30

MOSFET Modeling for RF-CMOS Design

M. Miura-Mattausch (Hiroshima Univ., Japan)

**6A-2:** Thursday, January 29, 14:30-15:30

RF Design Methodologies Bridging System-IC-Module Design

R. A. Mullen (Cadence Design Systems, Inc., USA)

**9A-1:** Friday, January 30, 13:30-14:10

Toward Stochastic Design for Digital Circuits – Statistical Static Timing Analysis –

S. Tsukiyama (Chuo Univ., Japan)

**9A-2:** Friday, January 30, 14:10-14:50

Physical CAD Changes to Incorporate Design for Lithography and Manufacturability

L. Scheffer (Cadence Design System, USA)

**9A-3:** Friday, January 30, 14:50-15:30

Design-Manufacturing Interface for .13 um and Below

A. J. Strojwas (CCMU and PDF Solutions, USA)

### Three Full-Day and Two Half-Day Tutorials

**FULL-DAY Tutorials:**

Tuesday, January 27, 2004, 9:00-17:00

1 Recent Advances and Future Challenges in Design Verification Organizer: D. Pradhan - Univ. of Bristol, UK

Speakers: D. Pradhan -Univ. of Bristol , M. Abadir

-Motorola , R. Drechsler -Univ. of Bremen

2 Design and Runtime Techniques for Leakage Control and Minimization of CMOS VLSI Circuits in Active and Sleep Modes

Organizer: M. Pedram, -USC

Speakers: F. Fallah -FLA, Fujitsu , M. Pedram -USC

3 System-Level Design Methodology for SoC Design

Organizer: D. Gajski -UCI

Speakers: *M. Fujita* -Univ. of Tokyo , *D. Gajski* -UCI , *T. Hasegawa* -Fujitsu Ltd. , *T. Imai* -Renesas Tech-

nology.

**HALF-DAY Tutorials:**

Tuesday, January 27, 2004, 9:00-12:00

4.1 Low Power Design Techniques and Tools

Organizer: S. Chattoapdhyay -Intel Corp.

Speakers: Subhomoy Chattoapdhyay -Intel Corp. ,

R. Patel -Intel Corp.

Tuesday, January 27, 2004, 13:30-16:30

4.2 Energy, Fault-torelance, and Scalability Issues in Designing Networks-on-chip

Organizer: *R. Marculescu* -Carnegie Mellon University. USA

Speaker: R. Marculescu - Carnegie Mellon University

### Welcome to ASP-DAC 2004

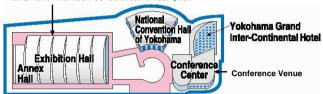

It is my pleasure and honor, on behalf of the Organizing Committee, to welcome you to the Asia and South Pacific Design Automation Conference 2004 (ASP-DAC 2004), a sister conference of DAC, DATE, and ICCAD. ASP-DAC 2004 will be held at Pacifico Yokohama, Kanagawa Prefecture, Japan from January 27 through 30, 2004. This year's ASP-DAC will be held again in the Pacifico Yokohama, Japan, jointly with Electronic Design and Solution Fair 2004. Because Yokohama area has many electronics industries and EDA companies, and many conferences and exhibitions are held here, Pacifico Yokohama is a familiar place for many of us.

The goal of the ASP-DAC is to provide the researchers and engineers working in the area of SoC/ VLSI/Embedded System design and EDA/CAD technologies, with the access to global level leading edge information and opportunities for discussion and information exchange on these topics.

We are preparing outstanding Keynote Addresses on ubiquitous computing, ITS (Intelligent Transport Systems), and future electronic systems and EDA Technologies, by the authorities of these areas. The details will be announced soon.

The Technical Program Committee, under the leadership of Prof's. Hidekazu Terai, Nikil Dutt, Xianlong Hong, and Masahiro Fujita, have reviewed 291 papers from 28 countries to organize the outstanding program. After careful selection, 148 papers are selected for presentation in the Conference. The selected papers cover the wide variety of hot topics from system level design to physical design including embedded systems, reconfigurable systems, analog circuits, and TCAD.

The program also includes a session for design examples and panel discussions. The University LSI Design Contest is also an important event of ASP-DAC, which focuses on a real chip design in academia. The Design Contest Committee, chaired by Prof's Makoto Ikeda and Xiaoyang Zeng, selected excellent designs for presentation.

On Tuesday, tutorials are scheduled to give complete introductions to the state-of-the-art SoC design and CAD topics.

ASP-DAC 2004 will be a precious opportunity for you to find valuable information by exchanging ideas with researchers and engineers working on SoC/VLSI design technologies.

We would be more than happy if we could provide you with a valuable and enjoyable experience in this conference. We look forward to meeting with you in Yokohama.

Marchan In

**Masaharu Imai** General Chair ASP-DAC 2004

### **Sponsorship**

### Sponsored by:

IEEE Circuits and Systems Society http://www.ieee-cas.org

ACM/SIGDA http://www.sigda.org

IEICE ESS (Institute of Electronics, Information and Communication Engineers - Engineering Sciences Society) http://www.ieice.org

IPSJ SIGSLDM (Information Processing Society of Japan - SIG System LSI Design Methodology) http://www.ipsi.or.ip

### Supported by:

JEITA (Japan Electronics and Information Technology Industries Association) http://www.jeita.or.jp

STARC (Semiconductor Technology Academic Research Center) http://www.starc.jp

TAF (The Telecomminucation Advancement Foundation) http://www.taf.or.jp

City of Yokohama http://www.city.yokohama.jp/en/

7

### In Cooperation with:

JIEP (Japan Institute of Electronics Packag-

http://www.jiep.or.jp/jiepweb/english/jiepe.html

### **Organizing Committee**

### **General Chair**

### Masaharu Imai

Osaka University

1-3 Machikane-yama, Toyonaka, Osaka, 560-8531 Japan Phone: 06-6850-6625 FAX: 06-6850-6627 imai@ist.osaka-u.ac.ip

Past Chair/ SC Chair Hiroto Yasuura

Kvushu University

**Secretaries** Yoshinori Takeuchi

Osaka University

Kazuhito Ito

Saitama University

Hiroyuki Tomiyama

Nagoya University

**TPC Co-Chairs** Hidekazu Terai

Ritsumeikan University

**Nikil Dutt**

University of California, Irvine

Xianlong Hong

Tsinghua University

**TPC Vice Chair** Masahiro Fuiita

University of Tokyo

**TPC Secretaries** Kiyoharu Hamaquchi

Osaka University

Keishi Sakanushi

Osaka University

Masahiro Fukui

Ritsumeikan University

**Design Contest Co-Chairs** Makoto Ikeda

University of Tokyo

Zeng Xiaoyang

Fudan University

**Design Contest Vice Chair**

Hideki Yamauchi

Sanyo Electric Co.

**Tutorial Co-Chairs** Shinji Kimura

Waseda University

Yang Haigang

Lattice Semiconductor

Finance Co-Chairs Nagisa Ishiura

Kwansei Gakuin University

Tsuneo Nakata

FUJITSU LABORATORIES LTD.

**Publicity Co-Chairs**

**Tsutomu Sasao**

Kyushu Institute of Technology

Yukihiro Iquchi

Meiji University

**Publication Chair** Kazutoshi Kobayashi

University of Tokyo

**Audio Visual Chair** Youichi Shiraishi

**Gunma University**

**Local Arrangement Chair** Atsushi Takahashi

Tokvo Institute of Technology

Local Arrangement Secretary

Masato Inagi

Tokyo Institute of Technology

**Registration Chair** Kunihiro Fujiyoshi

Tokyo University of Agriculture JEITA/EDA TC Rep.

and Technology

**Promotion Chair** Yusuke Matsunaga

Kyushu University

**Marketing Advisory Chair**

Hiromitsu Fuiii

Nihon Synopsys Co., Ltd.

ASP-DAC Japan Council Rep.

Tokinori Kozawa

STARC

Kenii Yoshida

Cadence Design Systems, Japan

ASP-DAC Rep. at DAC Hidetoshi Onodera

Kvoto University

ASP-DAC Rep. at DATE

Masaharu Imai Osaka University

IEICE/CAS Rep.

Tokinori Kozawa

STARC

IEICE/ICD Rep.

Michitaka Kameyama

Tohoku University

IEICE/VLD Rep.

Masao Yanaqisawa

Waseda University

IPSJ/SLDM Rep. Hidekazu Terai

JIEP Rep.

Akinori Kanasugi Tokyo Denki University

Ritsumeikan University

IWCM Rep.

Mitiko Miura-Mattausch Hiroshima University, Japan

Mitsuru Nadaoka

Oki Electric Industy

**EDSF Chair** Masaki Hayashi

Sharp

ation

Secretariats Jirou Irie

Japan Electronics Show Associ-

Yoshinori Ishizaki

Japan Electronics Show Association

Mieko Mori

Japan Electronics Show Association

Kohei Torikai

Japan Electronics Show Association

Yuka Arikawa

9

Japan Electronics Show Association

### **Technical Program Committe**

### **Co-Chairs**

Hidekazu Terai

**Nikil Dutt**

Ritsumeikan University University of California, Irvine terai@se.ritsumei.ac.jp dutt@uci.edu

Xianlong Hong

Tsinghua University hxl-dcs@tsinghua.edu.cn

> **Vice Chair** Masahiro Fuiita

University of Tokyo fujita@ee.t.u-tokyo.ac.jp

### **Secretaries**

Keishi Sakanushi Osaka University

Kiyoharu Hamaguchi

sakanusi@ist.osaka-u.ac.jp

Osaka University hama@ics.es.osaka-u.ac.jp

Masahiro Fukui

Ritsumeikan University mfukui@se.ritsumei.ac.jp

### **Subcommittees**

(\*/† indicate the subcommitte chair/vice-chair.)

[1] System Level Design Methodology

\* Kazutoshi Wakabayashi Wayne Luk NFC Imperial College † Dai Araki Radu Marculescu

InterDesign Technologies, Carnegie Mellon University

Hiroshi Nakamura Inc. Jun-Dong Cho University of Tokyo

SungKyunKwan University Loganath Ramachandran

**Tony Givargis** Synopsys

University of California, Irvine Wolfgang Rosenstiel Joerg Henkel University Tubingen NEC Lab. Katsuharu Suzuki

Tohru Ishihara NEC Corp. Fuiitsu Laboratories of Amer- Wavne Wolf

ica, Inc. Princeton University Allen C. -H. Wu Nagisa Ishiura Kwansei Gakuin University Tsing Hua University

Akira Kawaguchi Qiang Zhu **GAIA System** Fuiitsu Labs.

[2] Embedded and Real-Time Systems \* Hiroaki Takada **Akihiko Inoue**

Nagova University Matsushita Electric Industrial

† Hiroyuki Tomiyama Co. Ltd.

Nagova University **Ahmed Amine Jerraya**

TIMA/INPG **Naehyuck Chang** Seoul National University Tatsuo Nakajima Pai Chou Waseda University University of California, Irvine Preeti Ranjan Panda

Xiaobo Sharon Hu Indian Institute of Technology,

University of Notre Dame Delhi

Ing-Jer Huang

National Sun Yat-Sen Univer-

sity

[3] Behavioral/Logic Synthesis and Optimization

\* Yusuke Matsunaga Raieev Murgai

Kyushu University Fujitsu Laboratories of Amer-

**Rolf Drechsler** ica

University of Bremen Hirovuki Ochi

Hiroyuki Higuchi Hiroshima City University

Fuiitsu Laboratories Tsutomu Sasao

Yuji Kukimoto Kyushu Institute of Technol-

Cadence Design Systems

**Wolfgang Kunz** Shigeru Yamashita

University of Kaiserslautern NAIST

Shin-ichi Minato NTT

[4] Validation and Verification for Behavioral/Logic Design

\* Kazuhiko Equchi

Aichi Institute of Technology

† Masahiko Tovonaga Kochi University

Stephen P. G. Chappell

Celoxica Ltd. **Atsuo Hotta**

Aichi Institute of Technology

Minoru Inamori

NTT Cyber Space Laborato- versity

ries

Satoshi Kojima Mentor Graphics Japan Co. Atsushi Takahara Ltd

Tsu-wei Ku Apex Design Systems, Inc.

Yuichiro Mori Kochi University Kouichi Nagami

Network Innovation Laborato-

ries

S. K. Nandy

Indian Institute of Science

Goro Suzuki

The University of Kitakyushu Chang Joseph Sylvester

Nanyang Technological Uni-

Kazuyoshi Takagi Nagova University

NTT BizLink, Inc. **Tomohiro Yoneda**

Tokyo Institute of Technology

[5] Optimization and Verification in Circuit and Chip

\* Masanori Hashimoto Kvoto University

Charlie Chung-ping Chen

National Taiwan University

Chung-kuan Chena University of California. San Toshiba Microelectronics Diego

Atsushi Kurokawa

STARC

David Z. Pan

Austin

\* Takahiro Watanabe

Waseda University

† Kazuhiko Takamizawa

Wayne Dai

**UC Santa Cruz Toshihiro Hattori** SuperH (Japan), Ltd.

Xianlong Hong Tsinghua University

Mineo Kaneko

**JAIST**

Kaoru Kawamura Fujitsu lab.

Hitoshi Kitazawa

ture and Technology

Cheng-kok Koh **Purdue University**

**Tetsushi Koide**

Hiroshima University

Shigetoshi Nakatake The University of Kitakyushu Takeshi Yoshimura Michiroh Ohmura

Hiroshima Institute of Tech-

nology

Sachin Sapatnekar University of Minnesota

Takashi Sato

Renesas Technology Corp.

Masaaki Yamada

Ryuichi Yamaquchi

Matsushita Electric Industrial

Co. Ltd.

Janet Meling Wang

The University of Texas at University of Arizona at Tuc-

son

[6] Performance Driven Physical Design

**Nobuto Ono** SII EDA Technologies Inc.

Shunii Saika

Euphonic Technologies, Inc. Matsushita Electric Industrial

Co. Ltd.

Youichi Shiraishi **Gunma University** Atsushi Takahashi

Tokvo Institute of Technology

Yasuhiro Takashima

**FAIS**

Shuii Tsukivama Chuo University Masahiko Toyonaga Kochi University

Tokyo University of Agricul-Shin'ichi Wakabayashi Hiroshima City University

> Masaaki Yamada Toshiba Microelectronics

Yan Zhang

University of California, Los

Angels

Waseda University

[7] Test Technology and Design for Testability

\* Terumine Hayashi Yukiva Miura

Mie University Tokyo Metropolitan Univeristy

† Koji Nakamae Alex Orailoglu

Osaka University University of California, San

Takashi Aikvo Diego

Fujitsu Ltd. **Rochit Rajsuman**

Kazumi Hatayama Advantest America R&D Cen-Renesas Technology Corp. ter. Inc. Toshinori Hosokawa Yasuo Sato Nihon University **STARC**

Michiko Inoue Chauchin Su NAIST National Chiao Tung Unver-

**Kuen-Jona Lee** sity

National Cheng Kung Univer- Hiroshi Takahashi sity

**Ehime University** Masaaki Yoshida

NEC electronics corporation

South

[8] Analog and RF Circuit Design

\* Koichiro Mashiko Haruo Kobavashi STARC **Gunma University** † Shoii Kawahito Seiiiro Morivama Shizuoka University Innotech Corporation Akira Hyogo **Makoto Nagata** Tokyo University of Science Kobe University

Masao Ito Sri Parameswaran Renesas Technology Corp. University of New

Wing-Hung Ki

**HKUST**

[9] Design for Manufacturability (TCAD)

\* Hiroo Masuda Kenichiro Sonoda **STARC** Renesas Technology Corp.

**Uwe Feldmann Albert Wang**

Infineon Technologies ILLINOIS INSTITUTE OF

Wales

Yasunori Iwatsu **TECHNOLOGY** Toshiba Microelectronics Masaharu Yamamoto

Center STARC Kenii Nishi Zhipina Yu

Kinki University Tech. College Tsinghua University

[10] Reconfigurable Systems

\* Masahiko Kawamura Toshiba Corp. † Hideharu Amano

Keio University

Yao-wen Chang National Taiwan University

**Kamal Chaudhary**

Xilinx Corp. **Kiyoung Choi**

Seoul Naitonal University

Andre' DeHon Caltech

**Thomas Huang**

Reiner W. Hartenstein University of Kaiserslautern

Nobuki Kaiihara

NEC

Maiid Sarrafzadeh

University of California, Los

Angeles **Gary Spivey**

George Fox University Joshua Walstrom

Altera Corp. Takashi Yokota

Utsunomiya University

Aptix Corp.

[11] Leading-Edge Design Experiments

\* Takao Onove Osaka University † Hiroyuki Okuhata Synthesis Corporation

Hideki Ando Nagova University Seongsoo Lee

Soongsil University

Satoshi Matsushita **NEC Corporation** Takashi Miyamori Toshiba Corporation

Yulu Yang Nankai University

### **University LSI Design Contest Committee**

### Co-Chairs

Makoto Ikeda University of Tokyo ikeda@silicon.u-tokyo.ac.ip Zeng Xiaoyang Fudan University xyzeng@fudan.edu.cn

### Vice Chair Hideki Yamauchi Sanyo Electric Co.

Sanyo Electric Co. yamauchi@ul.rd.sanyo.co.jp

Chi-Ying Tsui

The Hong Kong Ur

The Hong Kong University of Science and technology **Hideharu Amano**

Keio Univ. **Hideo Owada**

Fujitsu Lab. Hidetoshi Onodera

Kyoto University

Yasuyuki Matsuya

Yasuyuki Matsuya

**Ingrid Verbauwhede**University of California, Los

Angeles

Kang Hyeon Rhee Chosun University

**Kazuaki Murakami** Kyushu University

Koji Kotani

Tohoku University

Makoto Nagata Kobe University **Masato Motomura**

NEC

Minkyu Song Dongguk Univ.

Nobukazu TAKAI

Tokyo Polytechnic University

**Shoji Kawahito** Shizuoka University

Shyh-Jye Jou

National Central University

Takafumi Aoki Tohoku University

Takao Onoye

Osaka Univ.

Tomohisa Wada University of the Ryukyu

Toshiro Tsukada

STARC

Vojin G Oklobdzija University of California

### **Steering Committee**

### Chair

### Hiroto Yasuura

Kyusyu University vasuura@c.csce.kyushu-u.ac.jp

Vice Chair Takeshi Yoshimura

Waseda University E-mail: t-yoshimura@waseda.jp

Secretary Toshihiro Hattori

SuperH Japan, Ltd. toshihiro.hattori@superh.com

ASP-DAC 2002 General Chair Sunil D. Sherlekar

Tata Consultancy Services

ASP-DAC 2001 General Chair

Satoshi Goto

Waseda University

ACM SIGDA Rep. Nikil Dutt

University of California at Irvine

IEEE CAS Rep.

Ellen J. Yoffa

IBM Corporation

DAC Rep.

lan Getreu

DATE Rep.

Peter Marwedel

University of Dortmund

JEITA/EDA TC Rep.

Mitsuru Nadaoka

Oki Electric Industy

EDSF chair Masaki Hayashi

IEICE TGCAS Chair Kozawa Tokinori

Semiconductor Technology Academic Research Center

IEICE TGVLD Chair Masao Yanagisawa Waseda University **Secretary**

Kazutoshi Wakabayashi

NEC Corporation wakaba@ccm.cl.nec.co.ip

manaza e conmonitocico,

IEICE TGICD Chair Mihcitaka Kameyama

Tohoku University

IPSJ SIG SLDM Chair Hidekazu Terai

Ritsumeikan University

STARC Rep.

Tokinori Kozawa

Semiconductor Technology Academic Research Center

JIEP Rep.

Akinori Kanasugi Tokyo Denki University

International Members

Richard M.M. Chen

City University of Hong Kong

Graham R. Hellestrand

VaST Systems Technology Corporation

Xian-Long Hong Tsinghua University, Beijing

Chong-Min Kyung

Korea Advanced Institute of Science and Technology

Youn-Long Steve Lin Tsing Hua University, Hsin-Chu Alexander Stempkovsky Russin Academy of Sciences

Qianling Zhang

Fudan University

### **Advisory Members**

Basant R. Chawla

Genentech

Hideo Fujiwara

Nara Institute of Science and Technology

**Fumiyasu Hirose**

Cadence Design Systems, Japan

Masaharu Imai

Osaka University

Takashi Kambe

Kinki University

Hiroaki Kunieda

Tokyo Institute of Technology

Hidetoshi Onodera

Kvoto University

Isao Shirakawa

Professor Emeritus of Osaka University

Kenji Yoshida

Cadence Design Systems, Japan

### **University LSI Design Contest**

The University LSI Design Contest was conceived as a unique program of ASP-DAC Conference. The purpose of the Contest is to encourage education and research in LSI design, and its realization on chips at universities, and other educational organizations by providing opportunities to present and discuss innovative and stateof-the-art designs at the conference. Application areas and types of circuits include (1) Analog and Mixed-Signal Circuits. (2) Digital Signal processing, (3) Microprocessors, and (4) Custom Application Specific Circuits. Methods or technology used for implementation include (a) Full Custom and Cell-Based LSIs, (b) Gate Arrays, and (c) Field Programmable Devices, including FPGA/PLDs.

This year, twenty-eight selected designs from seven countries/areas will be disclosed in Session 6C with a short presentations followed by live discussions in front of posters. Submitted designs were reviewed by the members of the University Design Contest Committee based on the following criteria: Reliability of design and implementation, Quality of implementation, Performance of the design. Novelty, and Additional special features. In the selection process, emphasis was placed more on reliability, quality, and performance. As a result, the twenty-eight designs were selected. Also, we have instituted one outstanding design award.

It is with great pleasure that we acknowledge the contributions to the Design Contest, and it is our earnest belief that it will promote and enhance research and education in LSI design in academic organizations. It is also our hope that many people not only in academia but in industry will attend the contest and enjoy the stimulating discussions.

19

University LSI Design Contest Committee

Makoto Ikeda

Univ. of Tokyo

Co-Chair

Zeng Xiaoyang

Fudan University

Vice Chair

Hideki Yamauchi

Hideki Yamauchi

Makoto Ikeda

Hideki Yamauchi Sanvo Electric Co.

### **Electronic Design and Solution Fair 2004**

Broadband communications are propelling our society toward an age in which anyone anywhere will be able to easily relay and receive information of all kinds. In the home, electronic equipment will be linked together into far-reaching digital networks. Semiconductors are at the heart of this "digital revolution." Semiconductors must rapidly improve in performance and energy efficiency, breaking through the boundaries of what is possible today to reach new heights. Japan's Semiconductor MIRAI Project-a national R&D project for next-generation technologies-and a variety of other research and development efforts are being promoted to establish process and design technologies for SoC (Systemson-Chip). In line with these efforts, needs are growing for higher-level electronic circuit design technologies, and solutions technologies such as software. In its 4th year, Electronic Design and Solution Fair 2004 (EDSFair2004) is Asia's Leading Exhibition of Essential Design Solution for SoC Technologies. Here, you will find new design and solutions technologies combining cutting-edge electronic design automation (EDA), device and IP (intellectual property) design service technologies. Since 2001, when a cooperative partnership was launched with the Electronic Design Automation Consortium (EDAC) of the United States. EDSFair has risen to prominence as an international convention on a par with the Design Automation Conference (DAC) in America and Design, Automation and Test in Europe (DATE). EDSFair has also won strong global acclaim as the largest exhibition of its kind in Asia. EDSFair2004 will be held on January 29 and 30, 2004, in Pacifico Yokohama. Simultaneous events, such as the FPGA/PLD Design Conference, University Plaza and ASP-DAC (Asia and South Pacific Design Automation Conference), will enrich and enhance the EDSFair's effectiveness as a place for technological interchange between industry, academia and government organizations. I am confident that this event will provide exhibitors and visitors alike with unique opportunities for information exchange and new business development. All of us involved with the Fair look forward to your active participation.

### **General Information**

#### Name:

Electronic Design and Solution Fair 2004

### Period:

Thursday, January 29 - Friday, January 30, 2004

### Place:

Pacifico Yokohama

1-1-1. Minato Mirai. Nishi-ku. Yokohama 220-0012. Japan

### Hours:

10:00 a.m. to 6:00 p.m.

#### **Admission Fees:**

Exhibition: Free (registration required at show entrance) Conferences: Fees will be charged for some conferences

### Sponsor:

Japan Electronics and Information Technology Industries Association (JEITA)

### Cooperation:

Electronic Design Automation Consortium (EDAC)

### Support (expected):

Ministry of Economy, Trade and Industry, Japan Embassy of the United States of America in Japan U.S. Semiconductor Industry Association (SIA) Distributors Association of Foreign Semiconductors (DAFS)

### Assistance (expected):

Institute of Electronics, Information and Communication Engineers (IEICE)

Information Processing Society of Japan (IPSJ) Japan Printed Circuit Association (JPCA)

21

### Management:

Japan Electronics Show Association (JESA)

### **URL:**

http://www.edsfair.com

### **Invitation to ASP-DAC 2005**

On behalf of the Organizing Committee, it is my great pleasure and honor to invite all of you to ASP-DAC 2005, which is the 10th event of this conference series. The conference will be held from January 18 to 21, 2005 at Hotel Equatorial , Shanghai, China. This time, TPC Co-chairs of the Conference are Professor Xianlong Hong from Tsinghua Univ., Beiiing: Professor Hidekazu Terai from Ritsumeikan University. Japan; Professor C.K.Cheng from UCSD, U.S.A and Professor Youn-Long Lin from Tsinghua Univ. , Hsinchu . Their research fields cover almost all the main technical aspects of IC design from system level design methodology to physical design of System LSI or SoC. In order to make this conference more attractive and successful, we do need your help and cooperation. The conference has traditionally a strong impact on both industries and academia. We hope the excellent tradition can be deepened and carried forward through this conference.

As you know, Shanghai is becoming one of the most important microelectronic industrial bases in China, even in the world several years later. Now, a lot of worldwide famous corporations enter and be stationed in Shanghai and nearby area. Those enterprises involved IC manufacturing; design, testing and packaging have sprung up like mushroom. A complete IC industry chain is being grown up in Yangtze River Delta region of China. Taking the opportunity of ASP-DAC 2005, we sincerely welcome the attendees from various countries and regions to visit our universities, institutes and enterprises to further carry out technology and academic exchange. It will certainly promote the development of IC industry in China and collaboration between us. By the way. Shanghai is also a good place for sightseeing. You can go to those scenery points as the Bund. Yu Garden, Shanghai Museum, Shanghai Grand TheaterCXin Tian Di and so on.

ASP-DAC 2005 is waiting for you! Shanghai is waiting for you! Wish you have a good time in China!

### **Keynote Addresses**

Keynote Address I

Wednesday, January 28, 9:00-10:00

"CITRIS: The Center for Information

Technology Research in the Interest

of Society at the University of California"

Dr. Gary L. Baldwin

Executive Director, CITRIS, University of California, Berkeley, USA

The Center for Information Technology in the Interest of Society (CITRIS) was founded on July 1, 2001, as a collaboration among the University of California at Berkeley (UCB), Davis (UCD), Merced (UCM) and Santa Cruz (UCSC). The CITRIS mission is to sponsor and house collaborative information technology (IT) research to provide solutions to grand-challenge social and commercial problems affecting the quality of life of individuals and organizations. CITRIS is one of four California Institutes of Science and Innovation established by Governor Gray Davis to create a partnership between the University of California and state's leading-edge businesses to lay the foundation for the "next New Economy."

The CITRIS research agenda now embraces more than 200 faculty members from over 50 departments among the four participating U.C. campuses. It encompasses over 150 separate research activities, sponsored both by external funding agencies as well as through CITRIS seed funds. CITRIS has identified Societal-Scale Information Systems (SISs) as core research vehicles for addressing many of the societal problems of large scale that we face today and anticipate in the future. In this context, "societal"; refers both to the size and impact of the proposed system, as well as one of our most important metrics of success - it must improve people's lives and the lives of organizations.

Whether it involves

- the simple act of buying an energy-efficient refrigerator or source of illumination, or monitoring buildings, bridges, and highways for structural integrity during an earthquake, or

- monitoring the status and delivering medications in home health care devices for the elderly, or

- delivering educational course materials over diverse geographies, or

- aiding fi re and rescue teams in navigating safely through smoke-fi lled buildings, or

- guarding the quality of our food and water,

an SIS can be applied to collect, understand, and help people with the vast quantities of information needed to address these problems. This partial list of societal-scale applications is being addressed by an extensive, evolving, and diverse set of research projects within CITRIS, all linked by their relevance to societal impact.

Our initial vision for one of the most important SISs is that it will integrate vast numbers of tiny wireless sensors, hand-held information devices, large computing clusters, and large data sets into systems that make it easy for all citizens to monitor and gather data. The sensors themselves must be very cheap and operate without batteries so that they become widely used and require no maintenance. There must be a reliable network to connect the sensors to monitoring systems in a way that requires no action on the part of the user to install, activate or maintain. The network must be secure, so that privacy is respected and malicious use cannot occur. By thinking through these system requirements, from the highest user interface to basic device and algorithmic structures, the CITRIS project portfolio is embracing all of these challenges and more.

CITRIS is a public-private partnership whose long-term success depends upon fostering an open and collaborative relationship between the State of California and the federal government (through grants and contracts), CITRIS industrial partners, and CITRIS University partners.

This is a dangerous number to quote. I'm sure we wouldn't be precise. Does it include the CITRIS seeded projects as well as federal and state funded? We'd never get this right. I suggest leaving it out. GLB

Keynote Address II

Friday, January 30, 9:00-10:00

"System Level Design Technology

for Realizing an Ambient

Intelligent Environment"

Dr. Rudy Lauwereins

Vice President, IMEC, Belgium

The advent of the intelligent environment or "ambient intelligence" is a serious challenge for the systems designer. The systems of the future are small, complex, flexible and consume little energy. These conflicting requirements require new ways of designing that differ radically from conventional methods. This keynote presentation presents a vision towards the ambient intelligent environment, describes the properties of the systems we need to build and derives the design challenges we are facing.

### **Technical Program**

Posters are exhibited in Room 418 if \* after the paper ID

### Wednesday, January 28, 8:30-10:00

| Wednesday, January 28, 8:30-9:00 Opening Session:           | Small Auditorium |

|-------------------------------------------------------------|------------------|

| Wednesday, January 28, 9:00-10:00 <b>Keynote Address I:</b> | Small Auditorium |

CITRIS: The Center for Information Technology Research in the Interest of Society at the University of California

*Dr. Gary L. Baldwin* - Executive Director, CITRIS, University of California. Berkeley, USA

### Wednesday, January 28, 10:15-12:15

Wednesday, January 28, 10:15-12:15 Room 411/412

Session 1A: (Special Session) Selected European Activities in SoC Low Power Design Methodologies and Research Networking

Co Chairs: W. Rosenstiel – Univ. of Tuebingen, Germany

M. Fujita - Univ. of Tokyo, Japan

- 1A-1 (Embedded Invited Talk): Fast, Predictable, and Low-energy Memory References through Architecture-aware Compilation

- P. Marwedel, M. Verma, L. Wehmeyer (Univ. of Dortmund, Germany), S. Steinke (KOSTAL GmbH & Co. KG, Luedenscheid, Germany), U. Helmig (Univ. of Dortmund, Germany)

- 1A-2 (Embedded Invited Talk): Predictable Design of Low Power Systems by Pre-Implementation Estimation and Optimization

W. H. Nebel (Oldenburg Univ. and OFFIS, Germany)

1A-3 (Embedded Invited Talk): EuroSoC: Towards a Joint University/Industry Research Infrastructure for System on Chip and System in Package

A. A. Jerraya (TIMA Laboratory, France)

Wednesday, January 28, 10:15-12:15 Room 413

Session 1B: Floorplanning

Co Chairs: X. Hong – Tsinghua Univ., China

K. Takamizawa – Euphonic Technologies,

Inc., Japan

- 1B-1 Abstraction and Optimization of Consistent Floorplanning with Pillar Block Constraints

N. Fu, S. Nakatake, Y. Takashima, Y. Kajitani (Univ. of Kiatakyushu, Japan)

- 1B-2 Space Planning: Placement of Modules with Controlled Empty Area by Single Sequence

X. Zhang (SII EDA Technologies Inc., Japan), Y. Kajitani (The Univ. of Kitakyushu, Japan)

- 1B-3 Layer Assignment for Reliable System-on-Package

J. R. Minz, S. K. Lim (Georgia Inst. of Tech., Atlanta, USA)

- 1B-4s On Handling Arbitrary Rectilinear Shape Constraint

X. Tang (Cadence, USA), M. Wong (Univ. of Illinois, USA)

- 1B-5s Robust Fixed-outline Floorplanning through Evolutionary Search

C. Lin, D. Chen, Y. Wang (Feng-Chia Univ., Taiwan)

Wednesday, January 28, 10:15-12:15 Room 414/415 **Session 1C: Modeling for Analog Circuits**

Co Chairs: Y. Huang – National Chiao Tung Univ., Taiwan

M. Nagata - Kobe Univ., Japan

- 1C-1 Analog Circuit Behavioral Modeling via Wavelet Collocation Method with Auto-Companding J. Wang, J. Tao, X. Zeng (Fudan Univ., China), C. Chiang (Synopsys Inc., USA), D. Zhou (Univ. of Texas at Dallas. USA)

- 1C-2 High-level Modeling of Continuous-Time  $\Delta\Sigma$  A/D-Converters Using Formal Models E. S. Martens, G. Gielen (KU Leuven, Belgium)

- 1C-3 High-Frequency Noise in RF Active CMOS Mixers P. Heydari (Univ. of California, Irvine, USA)

- 1C-4 On Mismatch in the Deep Sub-Micron Era from Physics to Circuits

R. O. Topaloglu, A. Orailoglu (UCSD, USA)

Wednesday, January 28, 10:15-12:15 Room 416/417 **Session 1D: Behavioral Synthesis**

Co Chairs: **P. Chou** – Univ. of California, Irvine, USA **A. Yamada** – Sharp, Japan

- 1D-1 Register Binding and Port Assignment for Multiplexer Optimization

D. Chen, J. Cong (UCLA, USA)

- 1D-2 A Thread Partitioning Algorithm in Low Power High-Level Synthesis

J. Uchida (Waseda Univ., Japan), N. Togawa (The Univ. of Kitakyushu, Waseda Univ., Japan), M. Yanagisawa, T. Ohtsuki (Waseda Univ., Japan)

- 1D-3 Minimization of Fractional Wordlength on Fixed-Point Conversion for High-Level Synthesis

N. Doi (Waseda Univ., Japan), T. Horiyama (Kyoto Univresity, Japan), M. Nakanishi (NAIST, Japan),

S. Kimura (Waseda Univ., Japan)

- 1D-4 A Procedure for Obtaining a Behavioral Description for the Control Logic of a Non-linear Pipeline

H. H. Naiaf-abadi (Sharif Univ. of Tech., Iran)

Wednesday, January 28, 10:15-12:15 Room 419

Session 1E: Delay Test and BIST

Co Chairs: **S. Chakradhar** – NEC Labs. America, USA

*H. Takahashi* – Ehime Univ., Japan

- 1E-1 TranGen: A SAT-Based ATPG for Path-Oriented Transition Faults

K. Yang, K. Cheng, L. Wang (UC-Santa Barbara,

- 1E-2 Longest Path Selection for Delay Test under Process Variation

X. Lu, Z. Li, W. Qiu, D. M. Walker, W. Shi (Texas A&M Univ., USA)

- **Development**R. Huang, Y. Lai, Y. Chou, C. Wu (National Tsing Hua Univ., Taiwan)

1E-3 SRAM Delay Fault Modeling and Test Algorithm

- 1E-4s An Efficient Design of Non-linear CA Based PRPG for VLSI Circuit Testing

- S. Das, D. Dey, B. K. Sikdar, P. Pal Chaudhuri (B E College, India)

### 1E-5s Combinatorial Group Testing Methods for the BIST Diagnosis Problem

A. B. Kahng, S. Reda (UCSD, USA)

### Wednesday, January 28, 13:30-15:30

Wednesday, January 28, 13:30-15:30 Room 411/412

Session 2A: (Special Session) Embedded System Applications

Co Chairs: *H. Tomiyama* – Nagoya Univ., Japan *A. A. Jerraya* – TIMA Laboratory, France

- 2A-1 (Embedded Tutorial): Toward Mobile Phone Linux

Y. Nakamoto (NEC, Japan)

2A-2 Power Control of CDMA Systems with Successive

- Interference Cancellation Using the Knowledge of Battery Power Capacity

Y. Wang (ASTRI, Hong Kong), C. Tsui, S. R. Cheng, W. Mow (The Hong Kong Univ. of Science and Tech., Hong Kong)

- 2A-3 Rate Analysis for Streaming Applications with On-Chip Buffer Constraints

A. Maxiaguine, S. Kuenzli (ETH Zurich, Switzerland), S. Chakraborty (NUS Singapore, Singapore), L. Thiele (ETH Zurich, Switzerland)

Wednesday, January 28, 13:30-15:30

Room 413

Session 2B: Placement

Co Chairs: *M. Wong* – Univ. of Illinois, USA *T. Sato* – Renesas Tech. Corp., Japan

2B-1 Performance-driven Global Placement via Adaptive Network Characterization

M. Ekpanyapong, S. K. Lim (Georgia Inst. of Tech., USA)

2B-2 Temperature-Aware Global Placement

B. Obermeier, F. Johannes (Technical Univ. of Munich, Germany)

- 2B-3 High Speed Layout Synthesis for Minimum-Width CMOS Logic Cells via Boolean Satisfiability

T. lizuka, M. Ikeda, K. Asada (Univ. of Tokyo, Japan)

- 2B-4s An Integrated Approach to Timing-Driven Synthesis and Placement of Arithmetic Circuits

K. Shin, T. Kim (KAIST, South Korea)

2B-5s Layer Assignment for Crosstalk Risk Minimization

D. Wu, J. Hu, R. N. Mahapatra (Texas A&M Univ., USA), M. Zhao (Motorola Inc., USA)

Wednesday, January 28, 13:30-15:30 Room 414/415 Session 2C: RF Design Methodology

Co Chairs: W. Ki – HKUST, Hong Kong

A. Matsuzawa - Tokyo Inst. Tech., Japan

- 2C-1 CrtSmile: A CAD Tool for CMOS RF Transistor Substrate Modeling Incorporating Layout Effects Z. Li (Univ. of Washington, USA), R. Suravarapu (Oregon State Univ., USA), R. Hartono, S. Bhattacharya (Univ. of Washington, USA), K. Mayaram (Oregon State Univ., USA), R. Shi (Univ. of Washington, USA)

- 2C-2\* NSGA-Based Parasitic-Aware Optimization of a 5GHz Low-Noise VCO M. Chu, D. J. Allstot (Univ. of Washington, USA), J. M. Huard, K. Y. Wong (National Semiconductor Corp., USA)

- 2C-3 Analytical Expressions for Phase Noise Eigenfunctions of LC Oscillators

P. Ghanta (Univ. of Arizona, USA), Z. Li, J. Roychowdhury (Univ. of Minnesota, USA)

- 2C-4 Analysis of MOS Cross-Coupled LC-Tank Oscillators Using Short-Channel Device Equations

M. M. Mansour (Berkeley Design Automation, USA),

M. M. Mansour (American Univ. of Beirut, Lebanon),

A. Mehrotra (Univ. of Illinois at Urbana-Champaign, USA)

Wednesday, January 28, 13:30-15:30 Room 416/417 Session 2D: Practical Issues in Logic Synthesis

Co Chairs: Y. Kukimoto – Cadence, USA

Y. Matsunaga – Kyushu Univ., Japan

2D-1 Timing Optimization by Replacing Flip-Flops to Latches

K. Yoshikawa, K. Kanamaru, Y. Hagihara, S. Inui, Y. Nakamura (NEC Corp., Japan), T. Yoshimura (Waseda Univ., Japan)

2D-2 Enhancing the Performance of Multi-Cycle Path Analysis in an Industrial Setting

H. Higuchi (Fujitsu Laboratories Ltd, Japan), Y. Matsunaga (Kyushu Univ., Japan)

2D-3 An Approach for Reducing Dynamic Power Consumption in Synchronous Sequential Digital Designs

N. Chabini (Royal Military College of Canada, Canada), W. Wolf (Princeton Univ., USA)

- **2D-4s Low Power Design Using Dual Threshold Voltage** Y. Ho, T. Hwang (Tsing Hua Univ., Taiwan)

- 2D-5s Technology Mapping and Packing for Coarsegrained Anti-fuse Based FPGAs

C. Kang, A. Iranli, M. Pedram (Univ. of Southern Cal-

Wednesday, January 28, 13:30-15:30 Room 419

Session 2E: Effective Test and Diagnosis

ifornia, USA)

Co Chairs: K. Cheng – Univ. of California, Santa Barbara, USA

T. Inoue – Hiroshima City Univ., Japan

- 2E-1 Efficient RT-level Fault Diagnosis Methodology

O. Sinanoglu, A. Orailoglu (UC San Diego, USA)

- 2E-2\* Design Diagnosis Using Boolean Satisfiability

A. Smith, A. Veneris, A. Viglas (Univ. of Toronto, Canada)

- 2E-3 Testable Design of GRM Networks with EXOR Tree for Detecting Stuck-at and Bridging Faults

H. Rahaman (B.E.College (D.U.), India), D. K. Das (Jadavpur Univ., India), B. B. Bhattacharya (Indian Statistical Inst., India)

- 2E-4s Test Data Compression Technique Using Selective Don't-Care Identification

T. Hayashi, H. Yoshioka, T. Shinogi, H. Kita, H. Takase (Mie Univ., Japan)

- **2E-5s** Re-configurable Embedded Core Test Protocol S. Wang, S. T. Chakradhar (NEC Labs., America, USA), K. J. Balakrishnan (Univ. of Texas at Austin, USA)

### Wednesday, January 28, 16:00-18:00

Wednesday, January 28, 16:00-18:00 Room 411/412 Session 3A: System-Level Design Methodology

Co Chairs: *V. Mooney* – Georgia Inst. of Tech., USA *D. Araki* – Inter Design Technologies,

Japan

3A-1\* Object-Oriented Modeling and Synthesis of SystemC Specifications

C. Schulz-Key, M. Winterholer, T. Schweizer, T. Kuhn, W. Rosenstiel (Univ. of Tuebingen, Germany)

3A-2 Application of UML for Hardware Design Based on Design Process Model

R. Damasevicius, V. Stuikys (Kaunas Univ. of Tech., Lithuania)

3A-3 A Cosynthesis Algorithm for Application Specific Processors with Heterogeneous Datapaths

Y. Miyaoka (Waseda Univ., Japan), N. Togawa (The Univ. of Kitakyushu, Japan), M. Yanagisawa, T. Ohtsuki (Waseda Univ., Japan)

3A-4 Design Methodology for SoC Architectures Based on Reusable Virtual Cores

M. Muraoka, H. Nishi, R. K. Morizawa, H. Yokota, H. Hamada (STARC, Japan)

Wednesday, January 28, 16:00-18:00 Room 413

Session 3B: Advanced Design and Modeling Techniques

Co Chairs: L. Scheffer – Cadence, USA F. Minami – Toshiba, Japan

3B-1 A Mulitple Level Network Approach for Clock Skew Minimization with Process Variations M. Mori, H. Chen, B. Yao, C. Cheng (UCSD, USA)

3B-2 Layout Techniques for On-Chip Interconnect Inductance Reduction

S. Tu, J. Jou (National Chiao-Tung Univ., Taiwan), Y. Chang (National Taiwan Univ., Taiwan)

3B-3 Piecewise Quadratic Waveform Matching with Successive Chord Iteration

Z. Wang, J. Zhu (Univ. of Toronto, Canada)

3B-4s Optimal Design of High Fan-In Multiplexers via Mixed-Integer Nonlinear Programming

H. Huang, C. Wang, J. Jou (National Chiao Tung Univ., Taiwan)

3B-5s Adaptive Supply Voltage Technique for Low Swing Interconnects

W. Jeong, B. C. Paul, K. Roy (Purdue Univ., USA)

Wednesday, January 28, 16:00-18:00 Room 414/415 **Session 3C: Analog Design and Evaluation**

Co Chairs: **S.** *Kawahito* – Shizuoka Univ., Japan *T. Tsukada* – STARC, Japan

3C-1 A Large-Current-Output Boosted Voltage Generator with Non-Overlapping Clock Control for Sub1-V Memory Applications

K. Min (Kookmin Univ., South Korea), Y. Kim (Changwon National Univ., South Korea), D. Kim, D. Kim (Kookmin Univ., South Korea), J. Ahn (Hynix Semiconductor Inc., South Korea)

3C-2 Effects of Noise and Nonlinearity on the Calibration of a Non-Binary Capacitor Array in a Successive Approximation Analog-to-Digital Converter J. Gan (Cirrus Logic, Inc., USA), S. Yan, J. Abraham (The Univ. of Texas at Austin, USA)

3C-3\* Jitter Spectral Extraction for Multi-gigahertz Signal

C. Ong. D. Hong. K. Cheng. L. -C. Wang (Univ. of

C. Ong, D. Hong, K. Cheng, L. -C. Wang (Univ. of California Santa Barbara, USA)

3C-4s A 35 dB-Linear Exponential Function Generator for VGA and AGC Applications

H. Q. Duong (Information and Communication Univ., South Korea)

3C-5s A High Efficiency 0.5W BTL Class-D Audio Amplifier with RWDM Technique

S. C. Li (National Yunlin Univ. of Science and Tech., Taiwan)

Wednesday, January 28, 16:00-18:00 Room 416/417

Session 3D: System Design Verification

Co Chairs: *K. Eguchi* – Aichi Inst. of Tech., Japan *M. Toyonaga* – Kochi Univ., Japan

3D-1 Efficient Translation of Boolean Formulas to CNF in Formal Verification of Microprocessors

M. N. Velev (Carnegie Mellon Univ., USA)

3D-2 Using Positive Equality to Prove Liveness for Pipelined Microprocessors

M. N. Velev (Carnegie Mellon Univ., USA)

3D-3 On Deriving Equivalent Architecture Model from System Specification

S. Abdi, D. Gajski (Univ. of California, Irvine, USA)

3D-4 On Compliance Test of On-Chip Bus for SOC H. Lin, C. Yen, C. Shih, J. Jou (National Chiao Tung Univ. Taiwan)

Wednesday, January 28, 16:00-18:00 Room 419

Session 3E: (Special Session) Panel Discussion: Opportunities with the Open Architecture Test System

Organizers: K. Hatayama – Renesas Tech., Japan

R. Rajsuman - Advantest America R&D

Center, USA

Moderator: **C. Wu** – National Tsing Hua Univ., Taiwan Panelists: **R. Raisuman** – Advantest America R&D

Center, USA

Y. Nishimura - Renesas Tech., Japan

S. Chakradhar - NEC Laboratories of

America, USA

A. Merschon - Guide Technologies, USA

D. Petrich - Wavecrest, USA

T. Tada – Tokushima Bunri Univ., Japan

Firing Lines: K. Cheng - Univ. of California Santa Bar-

bara, USA

Y. Okuda – ITC Asian Subcommittee Mem-

ber, Sony, Japan

### Thursday, January 29, 9:00-10:30

Thursday, January 29, 9:00-10:30 Room 411/412

Session 4A: (Special Session) C-Based Design Examples

Chair: *H. Yasuura* – Kyushu Univ., Japan

4A-1 (Embedded Invited Talk): C-based Behavioral Synthesis and Verification Analysis on Industrial Design Examples

K. Wakabayashi (NEC, Japan)

4A-2 (Embedded Invited Talk): Using C Based Logic Synthesis to Bridge the Productivity Gap

C. Sullivan, A. Wilson, S. Chappell (Celoxica Ltd, England, UK)

Thursday, January 29, 9:00-10:30

**Session 4B: Buffered Tree Construction**

Co Chairs: **C. Koh** – Purdue Univ., USA **T. Okamoto** – NEC, Japan

4B-1 A Place and Route Aware Buffered Steiner Tree Construction

C. Sze, J. Hu (Texas A&M Univ., USA), C. J. Alpert (IBM Austin Research Laboratory, USA)

4B-2 An Efficient Routing Tree Construction Algorithm with Buffer Insertion, Wire Sizing and Obstacle Considerations

S. Dechu (Micron, Inc., USA), Z. C. Shen, C. Chu (Iowa State Univ., USA)

- 4B-3 Modeling of Coplanar Waveguide for Buffered Clock Tree

- J. Chen, L. He (Univ. of California, Los Angeles, USA)

Thursday, January 29, 9:00-10:30

Room 414/415

Room 413

Session 4C: Power-Aware Approach for Microprocessor Design

Co Chairs: **C. Wu** – National Tsing Hua Univ., Taiwan **T. Miyamori** – Toshiba, Japan

- 4C-1 Decode Filter Cache for Energy Efficient Instruction Cache Hierarchy in Super Scalar Architectures

- K. Vivekanandarajah, T. Srikanthan, S. Bhattacharyya (Nanyang Technological Univ., Singapore)

- 4C- Mixed-Clock Issue Queue Design for Energy

2s\* Aware, High-Performance Cores

V. S. Rapaka (Mentor Graphics Corp., USA), E. Talpes, D. Marculescu (Carnegie Mellon Univ., USA)

- 4C-3s Power-Performance Trade-off Using Pipeline Delays

- G. Surendra, S. Banerjee, S. Nandy (Indian Inst. of Science, India)

- 4C-4s Exploiting Program Execution Phases to Trade Power and Performance for Media Workload

S. Banerjee, G. Surendra, S. K. Nandy (Indian Inst. of Science, India)

- 4C- LPRAM: A Low Power RAM Design with Testabil-

- 5s∗ ity

D. K. Pradhan (Univ. of Bristol, England, UK)

Thursday, January 29, 9:00-10:30

Room 416/417

Session 4D: Analog Layout Techniques

Co Chairs: J. Roychowdhury – Univ. of Minnesota, USA

H. Onodera - Kyoto Univ., Japan

4D-1 Multiple Specifications Radio-Frequency Integrated Circuit Design with Automatic Template-Driven Layout Retargeting

N. Jangkrajarng, S. Bhattacharya, R. Hartono, C. Shi

N. Jangkrajarng, S. Bhattacharya, R. Hartono, C. Sh (Univ. of Washington, USA)

- 4D-2 Hierarchical Extraction and Verification of Symmetry Constraints for Analog Layout Automation

S. Bhattacharya, N. Jangkrajarng, R. Hartono, R. Shi

(Univ. of Washington, USA)

- 4D-3 Multi-Level Placement with Circuit Schema Based Clustering in Analog IC Layouts

T. Nojima, X. Zhu (SII EDA Technologies Inc., Japan),

Y. Takashima, S. Nakatake, Y. Kajitani (The Univ. of Kitakyushu, Japan)

### Thursday, January 29, 10:45-12:15

Thursday, January 29, 10:45-12:15 Room 411/412 Session 5A: Formal Verification

Co Chairs: *F. Tao* – Univ. of California, Santa Barbara, USA

K. Takagi - Nagoya Univ., Japan

- 5A-1 Model Checking on State Transition Diagram

B. Das, D. Sarkar (CSE Deptt., IIT Kharagpur, 721302, India, India), S. Chattopadhyay (CSE Deptt., IIT Guwahati, India, India)

- 5A-2 Efficient Reachability Checking Using Sequential SAT

G. Parthasarathy, M. K. Iyer, K. Cheng, L. C. Wang (UC-Santa Barbara, USA)

5A-3 Exploiting State Encoding for Invariant Generation in Induction-based Property Checking

M. Wedler, D. Stoffel, W. Kunz (Univ. of Kaiserslautern, Germany)

Thursday, January 29, 10:45-12:15

Room 413

Session 5B: Routing Methodology

Co Chairs: T. Kim - KAIST, Korea

**S. Saika** – Matsushita Electric Industrial Co.,Ltd., Japan

5B-1s Tradeoff Routing Resource, Runtime and Quality in Buffered Routing

X. Tang (Cadence, USA), M. Wong (Univ. of Illinois, USA)

- 5B- Practical Methodology of Post-layout Gate Sizing

- Ps\* for 15 % More Power Saving

N. Miura (Keio Univ., Japan), N. Kato (Hitachi, Ltd., Japan), T. Kuroda (Keio Univ., Japan)

- 5B-3 Interconnect Design Methods for Memory Design C. Hwang, M. Pedram (Univ. of Southern California, USA)

- 5B-4 Optimal Planning for Mesh-Based Power Distribution

- C. Cheng, H. Chen, A. B. Kahng (UCSD, USA), M. Mori (Fujitsu Limited, Japan), Q. Wang (UCSD, USA)

Thursday, January 29, 10:45-12:15 Room 414/415

Session 5C: Exploration for Advanced SoC Design

Co Chairs: S. Lee – Soongsil Univ., Korea

H. Okuhata – Synthesis Corp., Japan

5C-1 2.5D System Integration: A Design Driven System Implementation Schema

Y. Deng, W. Maly (Carnegie Mellon Univ., USA)

- 5C-2 Canceled

- 5C-3s An HMAC Processor with Integrated SHA-1 and MD5 Algorithms

M. Wang, C. Su, C. Huang, C. Wu (National Tsing Hua Univ., Taiwan)

5C-4s Design Methodology for IRA Codes

F. Kienle, N. Wehn (Univ. of Kaiserslautern, Germany)

Thursday, January 29, 10:45-12:15

Room 416/417

Session 5D: Embedded Software

Co Chairs: **P. Chou** – Univ. of California, Irvine, USA **A. Fukuda** – Kyushu Univ., Japan

- 5D-1 Embedded Software Generation from System

Level Design Languages

H. Yu, R. Doemer, D. Gajski (UC Irvine, USA)

- 5D-2 Fast and Accurate Timed Execution of High Level Embedded Software Using HW/SW Interface Simulation Model

A. Bouchhima, S. Yoo, A. A. Jerraya (TIMA Laboratory, France)

- 5D- Energy Efficient Code Generation Exploiting Re-3s\* duced Bit-width Instruction Set Architectures

- (rISA)

A. Shrivastava, N. Dutt (Univ. of California, Irvine,

- 5D-4s Memory Access Driven Storage Assignment for Variables in Embedded System Design Y. Choi. T. Kim (KAIST. South Korea)

### Thursday, January 29, 13:30-15:30

Thursday, January 29, 13:30-15:30

USA)

Room 411/412

Session 6A: (Special Session) RF Modeling and Design Methodology

Chair: S. Moriyama – Innotech Corp., Japan

- 6A-1 (Embedded Tutorial): MOSFET Modeling for RF-CMOS Design

- M. Miura-Mattausch (Hiroshima Univ., Japan)

- 6A-2 (Embedded Tutorial): RF Design Methodologies Bridging System-IC-Module Design

R. A. Mullen (Cadence Design Systems, Inc., USA)

Thursday, January 29, 13:30-15:30

Room 413

Session 6B: Power Grid Analysis and Design

Co Chairs: **C. Chen** – National Taiwan Univ., Taiwan **M. Yamada** – Toshiba Microelectronics, Japan

6B-1\* Hierarchical Random-walk Algorithms for Power Grid Analysis

H. Qian, S. S. Sapatnekar (Univ. of Minnesota, USA)

6B-2 A Fast Decoupling Capacitor Budgeting Algorithm for Robust On-Chip Power Delivery

J. Fu, Z. Luo, X. Hong, Y. Cai (Tsinghua Univ., China),

S. Tan (UC Riverside, USA), Z. Pan (Tsinghua Univ.,

China)

- 6B-3\* Large-scale Linear Circuit Simulation with an Inversed Inductance Matrix

C. Mizuta, J. Iwai, K. Machida (Mathematical Systems Inc., Japan), T. Kage, H. Masuda (STARC, Japan)

- 6B-4 DEPOGIT: Dense Power-Ground Interconnect Architecture for Physical Design Integrity

A. Kurokawa (STARC, Japan), N. Ono (SII Technologies, Japan), T. Kage, H. Masuda (STARC, Japan)

Thursday, January 29, 13:30-15:30 Room 414/415

Session 6C: (Special Session) University Design Contest

Co Chairs: **X. Zeng** – Fudan Univ., China **M. Ikeda** – Univ. of Tokyo, Japan

- 6C-1 Design of Real-Time VGA 3-D Image Sensor Using Mixed-Signal Techniques

Y. Oike, M. Ikeda, K. Asada (Univ. of Tokyo, Japan)

- 6C-2 A Bandwidth and Memory Efficient MPEG-4

Shape Encoder

K. Lee, N. Y. Chang, H. Chin, H. Hsu, C. Jen (National Chiao Tung Univ., Taiwan)

- 6C-3 A Sub-mW MPEG-4 Motion Estimation Processor Core for Mobile Video Application Y. Kuroda, J. Miyakoshi, M. Miyama, K. Imamura, H. Hashimoto, M. Yoshimoto (Kanazawa Univ., Japan)

- 6C-4 Analog LSI for Motion Detection of Approaching Object with Simple-Shape Recognition Based on Lower Animal Vision K. Nishio, H. Yonezu, S. Sawa, Y. Furukawa (Toyohashi Univ. of Tech., Japan)

- 6C-5 350nm CMOS Test-Chip for Architecture Verification of Real-Time QVGA Color-Video Segmentation at the 90nm Technology Node

T. Morimoto, Y. Harada, T. Koide, H. J. Mattausch (Hiroshima Univ., Japan)

- 6C-6 A Low-Power Graphics LSI Integrating 29Mb Embedded DRAM for Mobile Multimedia Applications R. Woo, S. Choi, J. Sohn, S. Song, Y. Bae, H. Yoo (KAIST, South Korea)

- 6C-7 A High Efficiency 0.5W BTL Class-D Audio Amplifier with RWDM Technique

S. C. Li (National Yunlin Univ. of Science and Tech., Taiwan)

- A Small-Area High-Performance 512-Point 2-Dimensional FFT Single-Chip Processor

N. Miyamoto, L. Karnan (Tohoku Univ., Japan),

K. Maruo (Advantest Laboratories Ltd., Japan),

K. Kotani, T. Ohmi (Tohoku Univ., Japan)

- 6C-9 Fast Adaptive DC-DC Conversion Using Dual-Loop One-Cycle Control in Standard Digital CMOS Process D. Ma, W. Ki, C. Tsui (HKUST, Hong Kong)

- 6C-10 A Dual-band Image-reject Mixer for GPS with 64dB Image Rejection Y. Utsurogi, M. Haruoka, T. Matsuoka, K. Taniguchi (Osaka Univ., Japan)

- 6C-11 Associative Memory with Fully Parallel Nearest-Manhattan-Distance Search for Low-Power Real-Time Single-Chip Applications Y. Yano, T. Koide, H. Mattausch (Hiroshima Univ., Japan)

- 6C-12 A Performance Comparison of PLLs for Clock Generation Using Ring Oscillator VCO and LC Oscillator in a Digital CMOS Process T. Miyazaki, M. Hashimoto, H. Onodera (Kyoto Univ., Japan)

- 6C-13 A Reliable Low-Power Fast Skew-Compensation Circuit

Y. Wang, J. Wang (Chung-Cheng Univ., Taiwan)

6C-14 A Retinal Prosthetic Device Using a Pulse-frequency-modulation CMOS Image Sensor

J. Ohta, T. Furumiya, D. C. Ng, A. Uehara, K. Kagawa, T. Tokuda, M. Nunoshita (NAIST, Japan)

## 6C-15 Compact 12-Port Multi-Bank Register File Test-Chip in $0.35\mu m$ CMOS for Highly Parallel Processors

T. Sueyoshi, H. Uchida (Hiroshima Univ., Japan), Y. Mitani (Hiroshima City Univ., Japan), H. J. Mattausch, T. Koide (Hiroshima Univ., Japan), T. Hironaka (Hiroshima City Univ., Japan)

### 6C-16 A Low Power Asynchronous Java Processor for Contactless Smart Card

C. Yu, C. Choy (The Chinese Univ. of Hong Kong, Hong Kong), H. Min (Fudan Univ., China), C. Chan, K. Pun (The Chinese Univ. of Hong Kong, Hong Kong)

# 6C-17 An Image-sensor-based Optical Receiver Fabricated in a Standard 0.35-um CMOS Technology for Free-space Optical Communications

K. Kagawa, T. Kawakami, H. Asazu, T. Ikeuchi, A. Fuiuchi, J. Ohta, M. Nunoshita (NAIST, Japan)

### 6C-18 The Flexible Processor - An Approach for Single-Chip Hardware Emulation by Dynamic Reconfiguration

T. Ohkawa, T. Nozawa, M. Fujibayashi, N. Miyamoto, L. Karnan, S. Kita, K. Kotani, T. Ohmi (Tohoku Univ., Japan)

### 6C-19 A VDD and Temperature Independent CMOS Voltage Reference Circuit

T. Matsuda, R. Minami, A. Kanamori, H. Iwata (Toyama Prefectural Univ., Japan), T. Ohzone (Okayama Prefectural Univ., Japan), S. Yamamoto, T. Ihara, S. Nakajima (Shikino Hightech Co., Ltd., Japan)

### 6C-20 A Dual Band Switching Digital Controller for a Buck Converter

Y. M. Chui, W. Ki, C. Tsui (The Hong Kong Univ. of Science and Tech., Hong Kong)

### 6C-21 Golay and Wavelet Error Control Codes in VLSI

A. Balasundaram, A. Pereira, J. Park, V. J. Mooney III (Georgia Inst. of Tech., USA)

### 6C-22 Timing Measurement Unit with Multi-Stage TVC for Embedded Memories

K. J. Mo, S. S. Yang, T. Y. Chang (National Tsing Hua Univ., Taiwan)

### 6C-23 Development of a Waveform Sampling Front-End ASIC for PET

J. Yeom, T. Ishitsu, H. Takahashi (Univ. of Tokyo, Japan)

### 6C-24 A Dynamic Element Matching Circuit for Multi-bit Delta-Sigma Modulators

R. Katoh, S. Kobayashi, T. Waho (Sophia Univ., Japan)

### 6C-25 Design of POP11 (PDP-11 on Programmable Chip) Y. Iida, N. Shimizu (Tokai Univ., Japan)

### 6C-26 A Closed Caption TV Microcontroller

E. Leelarasmee (Chulalongkorn Univ., Thailand), K. Pengwon (Chiang Mai Univ., Thailand)

### 6C-27 Improvement of Saturation Characteristics of a Frequency-demodulation CMOS Image Sensor

J. Ohta, K. Yamamoto, Y. Oya, K. Kagawa, T. Tokuda, M. Nunoshita (NAIST, Japan), K. Watanabe (Microsignal Co. Ltd., Japan)

### 6C-28 Design and Implementation of a Secret Key Steganographic Micro-Architecture Employing FPGA

M. M. Saeb, H. A. Abdul Moneim (Arab Academy for Science, Tech. and Maritime Transport, Egypt)

Thursday, January 29, 13:30-15:30 Room 416/417 Session 6D: Novel Techniques in Logic Synthesis

Co Chairs: **R. Drechsler** – Univ. of Bremen, Germany **H. Higuchi** – Fujitsu Labs., Japan

### 6D-1 Preserving Synchronizing Sequences of Sequential Circuits After Retiming

M. Mneimneh, K. Sakallah (Univ. of Michigan, USA), J. Moondanos (Intel Corp., USA)

### 6D-2 A Fast Method to Derive Minimum SOPs for Decomposable Functions

T. Sasao (Kyushu Inst. of Tech., Japan), J. T. Butler (Naval Postgraduate School, USA)

### 6D-3 Efficient Computation of Canonical Form for Boolean Matching in Large Libraries

D. Debnath (Oakland Univ., USA), T. Sasao (Kyushu Inst. of Tech., Japan)

### 6D-4s Disjoint-Support Boolean Decomposition Combining Functional and Structural Methods

A. Martinelli, R. Krenz, E. Dubrova (KTH, Sweden)

### 6D-5s Transduction Method for Design of Logic Cell Structure

K. Tanaka, Y. Kambayashi (Kyoto Univ., Japan)

### Thursday, January 29, 16:30-18:00

Thursday, January 29, 16:30-18:00 Room 411/412

Session 7A: (Special Session) Future of ITS Technologies in the Ubiquitous Society

Chair: *M. Imai* – Osaka Univ., Japan

# 7A-1 (Invited Talk): The Integration of Vehicles Into a Ubiquitous Computing Environment –Computing and Networking Technologies for Vehicles–

N. Tokitsu (Internet ITS Consortium, Japan)

Thursday, January 29, 16:30-18:00 Room 413

Session 7B: Buffer Planning

Co Chairs: J. Hu – Texas A&M Univ., USA

**S.** Wakabayashi – Hiroshima City Univ., Japan

# 7B-1 Complexity Analysis and Speedup Techniques for Optimal Buffer Insertion with Minimum Cost W. Shi, Z. Li (Texas A&M Univ., USA), C. J. Alpert (IBM Corp., USA)

### 7B-2 A Buffer Planning Algorithm with Congestion Opimization

S. Chen (Tsinghua Univ., China), X. Hong (Tinghua Univ., China), S. Dong, Y. Ma, Y. Cai (Tsinghua Univ., China), C. Cheng (UCSD, USA), J. Gu (Science and Tech. Univ. of HongKong, Hong Kong)

### 7B-3s Buffer Allocation Algorithm with Consideration of Routing Congestion

Y. Ma, X. Hong, S. Dong, S. Chen, Y. Cai (Tsinghua Univ., China), C. Cheng (UCSD, USA), J. Gu (Science and Tech. Univ. of HongKong, Hong Kong)

### 7B-4s Integrating Buffer Planning with Floorplanning for Simultaneous Multi-objective Optimization

Y. Cheng (Synopsys, Taiwan), Y. Chang (National Taiwan Univ., Taiwan)

Thursday, January 29, 16:30-18:00

Room 414/415

Session 7C: Design Verification and Simulation

Co Chairs: S. Abdi – Univ. of California, Irvine, USA

G. Suzuki – The Univ. of Kitakyushu,

Japan

- 7C-1 $\ast$  Verification of Timed Circuits with Symbolic Delays

- R. Clariso, J. Cortadella (Universitat Politècnica De Catalunya, Spain)

- 7C-2 Improved Symbolic Simulation by Functional-Space Decomposition F. Tao. L. Wang, K. Cheng (UC-Santa Barbara, USA)

- Improving Simulation-Based Verification by

- 3s\* Means of Formal Methods

G. Fey, R. Drechsler (Univ. of Bremen, Germany)

7C-4s Parallel Verilog Simulation: Architecture and Circuit Partition

T. Li, Y. Guo, S. Li, F. Ao, G. Liu (National Univ. of Defense Tech., China)

Thursday, January 29, 16:30-18:00 F Session 7D: Task Scheduling with DVS

Room 416/417

Co Chairs: *R. Marculescu* – Carnegie Mellon Univ., USA

Y. Nakamoto - NEC, Japan

- 7D-1 Minimizing Energy Consumption of Multiple-Processor-Core Systems with Simultaneous Task Allocation, Scheduling and Voltage Assignment L. Leung, C. Tsui, W. Ki (The Hong Kong Univ. of Science and Tech., Hong Kong)

- 7D-2 Dynamic Voltage Scaling of Periodic and Aperiodic Tasks in Priority-Driven Systems

D. Shin, J. Kim (Seoul National Univ., South Korea)

- 7D-3s Fast and Efficient Voltage Scheduling by Evolutionary Slack Distribution

B. Gorji-ara, P. Chou, N. Bagherzade, M. Reshadi (Univ. of California, Irvine, USA), D. Jensen (Rockwell Collins Inc., USA)

7D-4s Minimizing Energy Consumption of Hard Real-Time Systems with Simultaneous Tasks Scheduling and Voltage Assignment Using Statistical Data

L. Leung, C. Tsui, W. Ki (The Hong Kong Univ. of Science and Tech., Hong Kong)

### Friday, January 30, 9:00-10:00

Friday, January 30, 9:00-10:00 **Keynote Address II:**

Small Auditorium

System Level Design Technology for Realizing an Ambient Intelligent Environment

Dr. Rudy Lauwereins - Vice President, IMEC, Belgium

### Friday, January 30, 10:15-12:15

Friday, January 30, 10:15-12:15

Room 411/412

Session 8A: Global Routing

Co Chairs: **C. Cheng** – Univ. of California, San Diego, USA

T. Shibuya - Fujitsu Lab. Ltd., Japan

- 8A-1 A Fast Congestion Estimator for Routing with Bounded Detours

- L. Cheng (Univ. of Colorado at Boulder, USA), X. Song, G. Yang, Z. Tang (Portland State Univ., USA)

- 8A-2 Accurate and Efficient Flow Based Congestion Estimation in Floorplanning

Z. C. Shen, C. Chu (Iowa State Univ., USA)

- 8A-3 A Coupling and Crosstalk Considered Timing-Driven Global Routing Algorithm for High Performance Circuit Design

- J. Xu, X. Hong, T. Jing, L. Zhang (Tsinghua Univ., China), J. Gu (Hong Kong Univ. of Science and Tech., Hong Kong)

- 8A-4s Timing-Constrained Congestion-Driven Global Routing

- J. Yan, S. Lin (Chung-Hua Univ., Taiwan)

- 8A-5s Efficient Octilinear Steiner Tree Construction Based on Spanning Graphs

- Q. Zhu (Tsinghua Univ., China), H. Zhou (Northwestern Univ., USA), T. Jing, X. Hong, Y. Yang (Tsinghua Univ., China)

Friday, January 30, 10:15-12:15

Room 413

**Session 8B: Interconnect and ESD Extraction**

Co Chairs: A. Wang – Illinois Inst. of Tech., USA

K. Nishi – Kinki Univ. Technical College,

Japan

8B-1\* Representative Frequency for Interconnect R(f)L(f)C Extraction

A. Tsuchiya, M. Hashimoto, H. Onodera (Kyoto Univ., Japan)

8B-2 A Mixed-mode Extraction Flow for High Performance Microprocessors

T. Jiang, E. Pettus, D. Lehther (Motorola Inc., USA)

8B-3 An Efficient Method MEGCR for Solving Systems with Multiple Right-hand Sides in 3-D Parasitic Inductance Extraction

L. Yang, X. Guo, Z. Wang (Tsinghua Univ., China)

8B-4s Fast and Accurate Extraction of 3-D Interconnect Resistance: Improved Quasi-Multiple Medium Accelerated BEM Method

X. Wang (Tsinghua Univ. Beijing, China), D. Liu (UCSC, USA), W. Yu, Z. Wang (Tsinghua Univ. Beijing, China)

8B-5s Concept and Extraction Method of ESD-critical Parameters for Function-Based Layout Level ESD Protection Circuit Design Verification

R. Zhan, H. Feng, Q. Wu, X. Guan, G. Chen, H. Xie, A. Wang (Illinois Inst. of Tech., USA)

Friday, January 30, 10:15-12:15

Room 414/415

Session 8C: Reconfigurable Systems

Co Chairs: **Y. Chang** – National Taiwan Univ., Taiwan **N. Kajihara** – NEC, Japan

- **8C-1** Interconnect Capacitance Estimation for FPGAs J. H. Anderson, F. N. Najm (Univ. of Toronto, Canada)

- 8C-2 Area-Minimal Algorithm for LUT-Based FPGA Technology Mapping with Duplication-free Restriction

C. Kao (National Pingtung Inst. of Commerce, Taiwan), Y. Lai (National Cheng Kung Univ., Taiwan)

8C-3 Temporal Floorplanning Using 3D-subTCG

P. Yuh, C. Yang, Y. Chang (National Taiwan Univ., Taiwan), H. Chen (Etron Tech. Inc., Taiwan)

8C-4s ReCSiP: a Reconfigurable Cell Simulation Platform

Y. Osana, T. Fukushima, H. Amano (Keio Univ., Japan)

8C-5s SmartGlue: An Interface Controller with Auto Reconfiguration for Field Programmable Computing Machine

Y. Kim (KAIST, South Korea), B. Park (Dynalith Systems, South Korea), J. Lee, C. Kyung (KAIST, South Korea)

Friday, January 30, 10:15-12:15

Room 416/417

Session 8D: HW/SW Co-Design

Co Chairs: **R. Marculescu** – Carnegie Mellon Univ., USA

N. Ishiura - Kwansei Univ., Japan

8D-1 An SoC Architecture and Its Design Methodology Using Unifunctional Heterogeneous Processor Array

Y. Yuyama, M. Aramoto (Kyoto Univ., Japan), K. Kobayashi (Univ. of Tokyo, Japan), H. Onodera (Kyoto Univ., Japan)

8D-2 Instruction Set and Functional Unit Synthesis for SIMD Processor Cores

N. Togawa (Univ. of Kitakyushu, Japan), K. Tachikake, Y. Miyaoka, M. Yanagisawa, T. Ohtsuki (Waseda Univ., Japan)

8D-3 A High Performance Bus Communication Architecture through Bus Splitting

R. Lu, C. Koh (Purdue Univ., USA)

8D-4s Automatic Generation of Bus Functional Models from Transaction Level Models

D. Shin, S. Abdi, D. Gajski (Univ. of California, Irvine, USA)

8D-5s A Global Bus Power Optimization Methodology for Physical Design of Memory Dominated Systems by Coupling Bus Segmentation and Activity Driven Block Placement

H. Wang (IMEC/Katholieke Universiteit Leuven, Belgium), A. Papanikolaou, M. Miranda (IMEC, Belgium), F. Catthoor (IMEC/Katholieke Universiteit Leuven, Belgium)

### Friday, January 30, 13:30-15:30

Friday, January 30, 13:30-15:30

Room 411/412

Session 9A: (Special Session) DFM in nm-Process

Generation

Co Chairs: **H. Masuda** – STARC, Japan **K. Yoshida** – Cadence, Japan

9A-1 (Embedded Tutorial): Toward Stochastic Design for Digital Circuits – Statistical Static Timing Analysis –

S. Tsukiyama (Chuo Univ., Japan)

9A-2 (Embedded Tutorial): Physical CAD Changes to Incorporate Design for Lithography and Manufacturability

L. Scheffer (Cadence Design System, USA)

9A-3 (Embedded Tutorial): Design-Manufacturing Interface for .13 um and Below

A. J. Strojwas (CCMU and PDF Solutions, USA)

Friday, January 30, 13:30-15:30

Room 413

Session 9B: Advanced Interconnect Analysis

Co Chairs: L. He – Univ. of California, Los Angels, USA

T. Sato - Renesas Tech. Corp., Japan

9B-1 Parametric Reduced Ordering Modeling for Interconnect Analysis

G. Shi, C. R. Shi (Univ. of Washington, USA)

9B-2 Realizable Parasitic Reduction for Distributed Interconnects Using Matrix Pencil Technique

J. Wang, O. Hafiz (Univ. of Arizona, USA)

9B-3 Spice Compatible Circuit Models for Partial Reluctance K

H. Ji (Univ. of California, Santa Cruz, USA), Q. Yu (Cadence Design Systems, Inc., USA), W. W. Dai (Univ. of California, Santa Cruz, USA)

9B-4 Frequency-Dependent Reluctance Extraction C. Luk, T. Chen (Univ. of Wisconsin-Madison, USA), Friday, January 30, 13:30-15:30

Room 414/415

Session 9C: (Special Session) Panel Discussion: Future Reconfigurable Computing System

Organizers:

M. Kawamura - Toshiba, Japan

H. Amano - Keio Univ., Japan

Moderator:

S. Goto - Waseda Univ., Japan

Panelists:

M. Motomura - NEC. Japan

T. Sato - IP Flex, Japan

S. Trimberger - Xilinx, USA

B. Plunkett - Quick Silver, USA

R. Lauwereins - IMEC, Belgium

Friday, January 30, 13:30-15:30

Room 416/417

Session 9D: System-Level Architecture

Co Chairs: A. Orailoglu - Univ. of California. San

Diego, USA

S. Chakradhar - NEC Labs. America.

USA

9D-1 Enabling On-Chip Diversity through Architectural **Communication Design**

> T. Dumitras, S. Kerner, R. Marculescu (Carnegie Mel-Ion Univ, USA)

9D-2 Bandwidth Tracing Arbitration Algorithm for Mixed-Clock SoC with Dynamic Priority Adapta-

Y. Kwon, J. Lee, C. Kyung (KAIST, South Korea)

9D-3 A Novel Memory Size Model for Variable-Mapping in System Level Design

> L. Cai, H. Yu, D. Gajski (Univ. of California, Irvine, USA)

9D-4\* A Compressed Frame Buffer to Reduce Display **Power Consumption in Mobile Systems**

> H. Shim, N. Chang (Seoul National Univ., South Korea), M. Pedram (Univ. of Southern California, USA)

### Friday, January 30, 16:30-18:00

Friday, January 30, 16:30-18:00

Room 411/412

Session 10A: Embedded System Architectures

N. Chang - Seoul National Univ., Korea Co Chairs:

A. Inoue - Matsushita Electric Industrial

Co., Ltd., Japan

10A-1 Instruction Buffering Exploration for Low Energy **VLIWs with Instruction Clusters**

> T. Vander Aa. M. Javapala, F. Barat, G. Deconinck (K. U. Leuven, Belgium), R. Lauwereins, F. Catthoor (IMEC, Belgium), H. Corporaal (TU Eindhoven. Netherlands)

10A- A Static and Dynamic Energy Reduction Technique for I-Cache and BTB in Embedded Proces-

> H. Sato (Kyushu Inst. of Tech., Japan), T. Sato (Japan Science and Tech. Agency, Japan)

10A- Resource-Constrained Low-Power Bus Encoding with Crosstalk Delay Elimination

M. Cha, C. Lyuh, T. Kim (KAIST, South Korea)

10A- Compiler Based Exploration of DSP Energy Sav-

ings by SIMD Operations

M. Lorenz, P. Marwedel (Univ. of Dortmund, Germany), T. Draeger, G. P. Fettweis (TU Dresden, Germany), R. Leupers (RWTH Aachen, Germany)

10A- Synthesizable HDL Generation Method for Con-

figurable VLIW Processors

Y. Kobayashi, S. Kobayashi, K. Okuda, K. Sakanushi. Y. Takeuchi, M. Imai (Osaka Univ., Japan)

Friday, January 30, 16:30-18:00

Room 413

Session 10B: Crosstalk Noise Analysis

Chair: M. Hashimoto – Kyoto Univ., Japan

10B-1 A Non-iterative Model for Switching Window Computation with Crosstalk Noise

J. Wang, O. Hafiz (Univ. of Arizona, USA)

10B-2 Gate Delay Calculation Considering the Crosstalk Capacitances

S. Abbaspour, M. Pedram (Univ. of Southern Califor-

10B-3 A Simplified Transmission-Line Based Crosstalk Noise Model for On-Chip RLC Wiring

K. B. Agarwal, D. Sylvester, D. Blaauw (Univ. of Michigan, USA)

Friday, January 30, 16:30-18:00

Room 414/415

Session 10C: Expressions for Boolean Functions

Co Chairs: M. N. Velev - Carnegie Mellon Univ., USA M. Muraoka - STARC, Japan

10C- Minimization of the Expected Path Length in **BDDs Based on Local Changes**

R. Ebendt (Univ. of Bremen, Germany), W. Guenther (Infineon Technologies, Germany), R. Drechsler (Univ. of Bremen, Germany)

10C- Minimization of Memory Size for Heterogeneous

2s\* **MDDs**

> S. Nagayama, T. Sasao (Kyushu Inst. of Tech., Japan)

10C- Combining Ordered Best-First Search with

Branch and Bound for Exact BDD Minimization R. Ebendt (Univ. of Bremen, Germany), W. Guenther (Infineon Technologies, Germany), R. Drechsler

10C- Satisfiability and Integer Programming as Com-

plementary Tools

(Univ. of Bremen, Germany)

R. Li, D. Zhou (Univer of Texas at Dallas, USA), D. Du (Univ. of New Brunswick, Canada)

10C- ShatterPB: Symmetry-Breaking for Pseudo-

**Boolean Formulas**

F. A. Aloul (American Univ. in Dubai, United Arab Em), A. Ramani, I. L. Markov, K. A. Sakallah (Univ. of Michigan, USA)