SPONSORED BY: SIG

IN TECHNICAL COOPERATION WITH

DESIGN, AUTOMATION AND TEST IN EUROPE THE EUROPEAN EVENT FOR ELECTRONIC SYSTEM DESIGN & TEST

## 25 – 27 MARCH 2024 VALENCIA, SPAIN

PALACIO DE CONGRESOS VALENCIA

DATE 2024 adopts the renewed format that was introduced in 2023. This means that DATE 2024 again uses an intensive three-day format, focussing on interaction as well as further strengthening the community. The vast majority of regular papers will be presented in technical sessions using short flash-presentations, where the emphasis is on poster-supported live interactions (in addition to the common full-length presentation videos available before, during and after the conference). By this, we make sure that the community can actually do what conferences are for: meeting, discussing and exchanging.

WWW.DATE-CONFERENCE.COM

TECHNICAL CO-SPONSORS IEEE Computer Society Test Technology Technical Community [TTTC] IEEE Solid-State Circuits Society [SSCS] IEEE Computer Society [IEEE CS]

## HIGHLIGHTS:

- The 27th edition of the main European event bringing together designers and design automation users, researchers and vendors, as well as specialists in the design, test and manufacturing of electronic circuits and systems hardware and software

- > Keynote speakers from academia and industry

- Research paper presentations

- > Late Breaking Results paper presentations

- Special days on emerging topics:

- > Responsible and Robust Al

- Sustainable Computing

- > Special Initiative on Autonomous Systems Design

- Focus Sessions on a broad range of hot academic and industrial topics

- >Unplugged Sessions

- >Embedded Tutorials

- Half-day workshops on specialised and novel topics

- Multi-Partner Project sessions

- Young People Programme (PhD Forum, Careers Fair - Industry & Student Teams Fair & Design Contest, Careers Fair - Academia & Univeristy Fair)

## DEAR COLLEAGUES AND FRIENDS,

#### Welcome to the 60th edition of DAC!

It was in May 1964 when the success story of this conference began, at that time called the SHARE design automation workshop with 17 presentations (on record) in two days.

Presentations like:

- "Verbal and graphical language for the AED system: A progress report" by Ross and Feldman,

- "A method for the best geometric placement of units on a plane" by M. Weindling,

- "AUTO CARD automated printed circuit board design" by F. B. Lavering,

- "Automatic test equipment production test in the design automation system" by C. M. Weems,

and others that defined what we understand today under the term Electronic Design Automation (EDA).

To put in perspective how visionary the founders and presenters of this first DAC edition were, we need to realize that the first commercially produced microprocessor would not be released until seven years after the first DAC. Even the first moon landing was still five years away.

There were several landmark inventions that had triggered the need for design automation:

- The first planar monolithic integrated circuit chip was demonstrated in 1960 and credited to Kilby and Noyce.

- The Quine–McCluskey algorithm for minimization of Boolean functions was developed from 1952-1956.

- In 1959 D. Engelbart studied the downscaling of integrated circuit size

- And in 1965, Gordon M. Moore presented his famous publication "Cramming more components onto integrated circuits".

That was the ground on which DAC was built and the success story began. By the mid 1970s, the first place and route tools were developed and were published at DAC. In the late 1970s, the Mead–Conway VLSI chip design revolution began; the approach to specify a behaviour in a textual programming language and have the tools derive a specific physical design is still the basis of chip design today. Among the early landmark EDA tools was the ESPRESSO logic minimizer by Bob Brayton et al. in 1982. The success of this and other early academic EDA tools led to the first ever trade show for EDA – at DAC in 1982. Many inventions – EDA algorithms, methods and tools – have first been presented and published at DAC.

Now, with the 60th edition of the Design Automation Conference, DAC presents itself in the best shape ever: For the first time, the paper submissions have surpassed the 1,000 threshold – 1,156 to be precise.

In numerous international rankings, DAC is regarded the top conference in the EDA field. That is due to the true international character of DAC, with strong contributions from academic and industrial institutions alike, and with major contributions from the Americas, Asia and Europe.

Besides the technical program, DAC has a world-class trade show, and it has Engineering Tracks that bridge the academic world with the industrial world – the recipe for impactful, long-lasting success.

60 DAC has some novelties from which I want to introduce a few: The Most Influential Paper Award is presented for the first time this year. Given the impactful history of DAC, the award recognizes previously published DAC research papers that have shown long lasting impact in one or more of DAC's core topics and that were published more than ten years ago. A novelty in the technical program are lightning talks that precede technical sessions and are given by recognized experts in the field; these serve as an introduction to the research area behind a technical session. On the exhibit floor, we'll have over 130+ exhibitors showcasing their latest innovations and solutions. The RISC-V Zone will feature our community of designers, executives, researchers, and developers harnessing the power of the RISC-V open-source architecture for AIC- and FPGA-based designs. Al Hardware Alley will be a showcase of our exhibitors who are capitalizing on the growing artificial intelligence trends and the hardware that will accompany them.

## WELCOME TO THE 60<sup>th</sup> Edition of DAC!

Innovation at DAC is currently driven by machine learning and AI techniques that have opened new opportunities and that can provide significant improvements to EDA, as well as design tools and methods. Due to the success of machine learning and AI during the past five years at DAC, we now have a dedicated research tracks on AI/ML, which establishes DAC as a major conference for applied ML/AI.

We have four keynotes and four visionary talks as well as technical SKYTalk and TechTalk presentations. In total we have more than 100 sessions, including:

- 26 sessions on design (from heterogeneous SoCs, architectures, circuits, to emerging technologies)

- Sessions on AI/ML (software and system designs of neural network accelerators as well as the application of AI/ machine learning techniques to advancing electronic design automation)

- More than 20 sessions on embedded software and systems (IoT, CPS, embedded memory, and edge computing)

- 12 sessions on cloud (design on cloud, ML, orchestration, and device life cycle management)

Please also visit the DAC Young Fellows Presentations, the DAC PhD Forum, plus the exciting educational sessions hosted at the DAC Pavilion that you can read more about in this program book.

DAC's unique exhibition will provide you the newest vendor developments in design and automation. With our twice-daily coffee breaks on the exhibition floor, you will be able to visit more than 120 exhibitors and the popular DAC Pavilion (Booth 2259) and Transformative Technologies Theater (Booth 1358). Please check out these other informative areas and activities:

- Design Infrastructure Alley

- RISC-V Zone

- Poster Gladiator Battles

Don't forget to download DAC's mobile app. It not only makes it easier for you to manage your schedule and activities at the show but also navigate the three floors of Moscone West.

Finally, I want to thank all who have helped to make 60 DAC possible: many thanks to my colleagues from the DAC EC, the TPC members of both the research and the Engineering Tracks, and all the volunteers and employees from the sponsor's societies/councils as well as the management companies.

I look forward to celebrating with you and meeting you in San Francisco in person!

JÖRG HENKEL 60 DAC General Chair

## TABLE OF CONTENTS

| Conference Information                            |

|---------------------------------------------------|

| DAC Directory Maps                                |

| Networking Receptions 11                          |

| Visionary Presentations                           |

| Keynotes Presentations                            |

| SKYTalk Presentations                             |

| TechTalk Presentations                            |

| In Memoriam                                       |

| 2023 Awards                                       |

| DAC Pavilion – Booth #2259                        |

| Technical Program                                 |

| Sunday                                            |

| Monday                                            |

| Tuesday                                           |

| Wednesday                                         |

| Thursday                                          |

| Additional Meetings                               |

| I LOVE DAC                                        |

| Transformative Technologies Theater – Booth #1359 |

| RISC-V Zone Theater Schedule – Booth #2335 115    |

| Industry Sponsorships                             |

| Exhibitor List                                    |

| Committees                                        |

• • •

## **CONFERENCE INFORMATION**

## **Exhibit Hours**

#### Exhibit Halls on Level 1 and Level 2

Monday Exhibits Open: 10:00 am – 6:00 pm

Tuesday Exhibits Open: 10:00 am – 6:00 pm

Wednesday Exhibits Open: 10:00 am – 6:00 pm

#### **Registration Hours**

#### Location: Level 1 Lobby

| Friday    | 1:00 pm – 4:00 pm  |

|-----------|--------------------|

| Saturday  | 12:00 pm – 5:00 pm |

| Sunday    | 7:00 am – 7:00 pm  |

| Monday    | 7:00 am – 7:00 pm  |

| Tuesday   | 8:00 am – 6:00 pm  |

| Wednesday | 8:00 am – 4:00 pm  |

| Thursday  | 8:00 am – 11:00 am |

|           |                    |

#### **Online Proceedings**

To view the proceedings, please visit – www.dac.com/proceedings60

#### Stay Connected

Enjoy complimentary WiFi at DAC:

Network Name: DAC2023 Password: 60DAC2023

## First Aid Room

Moscone West First Aid Office is located on the 1st Floor near the Howard Street entrance (behind registration).

Phone: 415.974.4159

REPORT ALL MEDICAL EMERGENCIES IMMEDIATELY

To report a medical emergency, call 511 on a white House Phone, or on a call phone dial 415.974.4021.

## DAC Mobile App

You can download the 60th Design Automation Conference app in the following ways:

- Search your device's App Store for "DAC Conferences"

- Go to the following link: <u>www.core-apps.com/dl/60dac</u>

Once the DAC Conferences application has downloaded,

- Choose 60th Design Automation Conference.

- Select to download the event app.

Once you are in the app don't forget to set up your profile by going to the Publish My Profile icon. If you click the box to publish your profile your name (and picture if you upload one) will show in the Attendee icon. From there you can make "Friendships" with other attendees which will allow you to send messages, and set up private appointments.

For technical assistance please contact <a href="mailto:support@core-apps.com">support@core-apps.com</a>

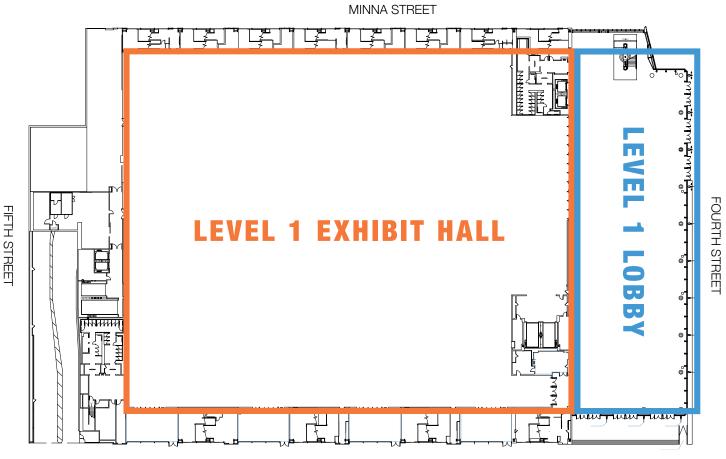

## DAC DIRECTORY MAP: LEVEL 1

SHUTTLE BUS ZONE - HOWARD STREET

## LEVEL 1 LOBBY

Registration

## LEVEL 1 EXHIBIT HALL

🧶 : 👷 : 💽

#### **Exhibits**

Transformative Technology Theater (T-Cube) Design Infrastructure Alley City Bytes & Beverages Community Connection Zone Conference Coffee Break

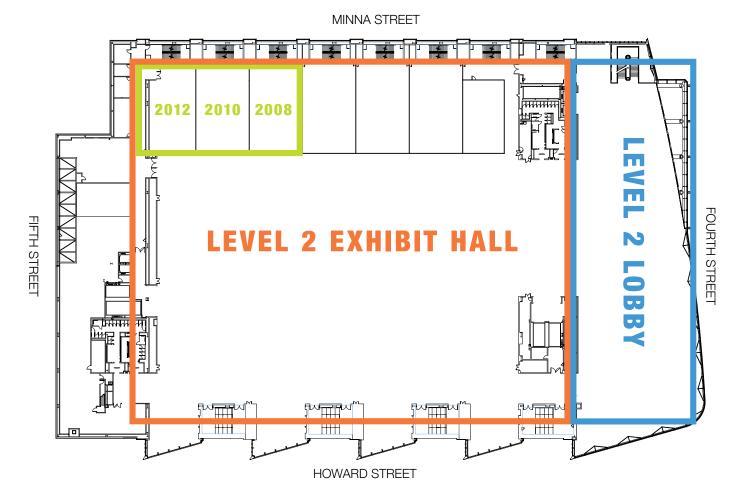

## DAC DIRECTORY MAP: LEVEL 2

## **LEVEL 2 LOBBY**

Networking Receptions Work-in-Progress & Late Breaking Results Posters HACK at DAC Hands-on Training Sessions PhD Forum/University Demo

## LEVEL 2 EXHIBIT HALL Exhibits

R 😧 🔘

DAC Pavilion Engineering Track Posters Press Room RISC-V Zone Theater

## **ROOMS 2008 - 2012**

**Engineering Track Sessions**

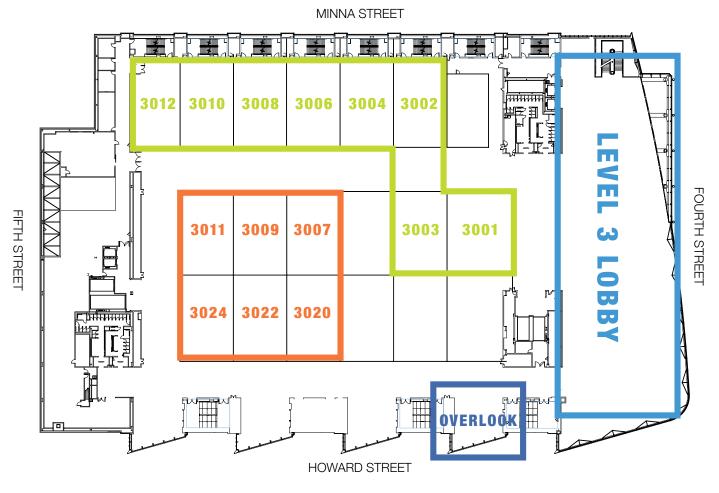

## DAC DIRECTORY MAP: LEVEL 3

## LEVEL 3 LOBBY

Welcome Reception Speaker Breakfast Career Development Day

## ROOMS 3007, 3009, 3011 3020-3024

• • <del>0</del>

Keynote

## **ROOMS 3001 - 3012**

Research Track Sessions Birds of a Feather

## **OVERLOOK**

Speaker Ready Room

# What will you Discover?

Circuit Cellar is the premier media resource for professional engineers, providing critical information on embedded and electronics technology.

circuitcellar.com

## **DAC NETWORKING OPPORTUNITIES**

### **Networking Receptions**

#### Sunday, July 9th

Welcome Reception 6:00 pm – 7:00 pm | Level 3 Lobby

#### Monday, July 10th

Engineering Track Poster Session 5:00 pm – 6:00 pm | Exhibit Hall Level 2

Women in Tech Reception 6:00 pm – 7:30 pm | Level 2 Lobby

PhD Forum and University Demo 7:00 pm – 9:00 pm | Level 2 Lobby

#### Tuesday, July 11

Engineering Track Poster Session 5:00 pm – 6:00 pm | Exhibit Hall Level 2

Work-in-Progress Poster Session 6:00 pm – 7:00 pm | Level 2 Lobby

DAC 60 Celebration Party 6:00 pm – 9:00 pm | Level 2 Lobby

#### Wednesday, July 12

Engineering Track Poster Session and Networking Reception & Awards 5:00 pm – 6:00 pm | Exhibit Hall Level 2

**KEYSIGHT**

Work-in-Progress/Late Breaking Results Poster Session 6:00 pm – 7:00 pm | Level 2 Lobby

#### TUESDAY, JULY 11 . 6:00 PM - 9:00 PM . SECOND FLOOR LOBBY

#### FOOD, DRINKING, MUSIC, GAMES!

Connect with old friends and new as we celebrate 60 years of innovation at the biggest party DAC's ever thrown!

#### SPONSORED BY

**EE**Times embedded

11

## **VISIONARY PRESENTATIONS**

#### **JOSEPH SAWICKI**

EXECUTIVE VICE PRESIDENT, INTEGRATED CIRCUITS, ELECTRONIC DESIGN AUTOMATION, SIEMENS EDA

# Systems 2030 – What's Needed to Succeed in the Next Decade of Design without Resorting to Human Cloning

Monday, July 10 | 9:00 am - 9:15 am

With the accelerating pace of semiconductor complexity, and the increasing software and semiconductor content in systems, traditional EDA levels of productivity increases are insufficient. As electronic system expand to literally hold our lives in their virtual hands, good-enough no longer is. What is needed are solutions across the ecosystem that provide orders of magnitude improvements to productivity, allow new engineers to become experts in very short periods of time, facilitate cross domain collaboration and optimization, and minimize the design space that needs to be explored to ensure systems operate correctly.

In this talk we will explore the past, present and future of complex semiconductor systems design.

**ABOUT:** Joseph Sawicki is a leading expert in IC nanometer design and manufacturing challenges. Formerly responsible for Mentor's industry-leading design-to-silicon products, including the Calibre physical verification and DFM platform and Mentor's Tessent design-for-test product line, Sawicki now oversees all business units in the Siemens EDA IC segment. Sawicki joined Mentor Graphics in 1990 and has held previous positions in applications engineering, sales, marketing, and management. He holds a BSEE from the University of Rochester, an MBA from Northeastern University's High Technology Program, and has completed the Harvard Business School Advanced Management Program.

## PRITH BANERJEE

CHIEF TECHNOLOGY OFFICER, ANSYS

## Driving Engineering Simulation and Design with AI/ML

#### Tuesday, July 11 | 9:00 am - 9:15 am

Traditionally, engineered products were designed with mechanical and electrical CAD tools, simulated and validated for correctness with CAE tools, prototypes were fabricated and tested, and products were then manufactured at scale in factories. This process required long product cycles often spanning years to build a new product. Today, virtually unlimited computing and storage available from the cloud is available for generative design to explore 10,000 design choices in near real-time, verify these products accurately through simulation (eliminating the need to build physical prototypes) and manufacture the products using additive manufacturing and factory automation. In the past, simulation tools were used to model specific, solitary physics such as mechanical structures, fluid dynamics, or electromagnetic interactions by solving second order partial differential equations using numerical methods. Today, simulation tools solve multi-physics problems (fluid-structure-electromagnetics interactions) at scale using the most complex solvers. We will explore the use of AI, Machine Learning and Deep Learning to accelerate these engineering simulations. We have identified four broad use cases of AI/ML applied to simulation: (1) Automatic parameter selection of simulation solvers to improve workflows and designer productivity (2) Augmenting simulation with AI/ML to accelerate simulation by factors of 100X (3) The use of AI/ML based generative design techniques to explore 10,000 designs automatically (4) Business intelligence to help improve engineering workflows. My talk will address three broad categories of AI/ML applied to simulation. (1) Top-down methods where we apply an AI/ML framework to a black box solver to train the ML models to improve run time (2) Bottom-up methods where we deeply embed the AI/ML methods inside the physics of our solvers. (3) Reduced order models where the order of the solutions is reduced using AI/ML methods. We will illustrate each of these approaches on existing, commerical tools. As an example of a bottom-up approach, we will describe an ML-based Partial Differential Equation solver and apply it to accelerate Fluid Dynamics problems and will report our results on our Fluent CFD software. As an example of a top-down method, we will report on an ML framework to improve the productivity of any ML developer working in simulation. As an example of a reduced order model we will report on a hybrid digital twin tool called the Twin Builder. We will report on an end-to-end chip packaging solution using a combination of data-driven and physics-informed neural networks, as integrated within Ansys Redhawk/IcePak/Mechanical solutions for Conjugate Heat Transfer. We will describe approaches to support fast design exploration/optimization using ML frameworks. We will describe ML-enabled assistance in various steps of simulation workflows such as initial meshing, smart sub-modeling, user experience and automatic selection of parameters. We will report on automatically setting the best parameters in Fluent/Live AMG solver.

## **VISIONARY PRESENTATIONS** continued

**ABOUT:** Prith Banerjee is the Chief Technology Officer of Ansys where he is responsible for leading the evolution of Ansys' Technology strategy and champion the company's next phase of innovation and growth Formerly, he was Executive Vice President, Chief Technology Officer of Schneider Electric. Previously, Prith was Managing Director of Global Technology Research and Development at Accenture. Formerly, he was Chief Technology Officer and Executive Vice President of ABB. Earlier, he was Senior Vice President of Research at HP and Director of HP Labs. Formerly, Prith was Dean of the College of Engineering at the University of Illinois at Chicago. Formerly, he was the Walter P. Murphy Professor and Chairman of Electrical and Computer Engineering at Northwestern University. Prior to that, Prith was Professor of Electrical and Computer Engineering at the University of Illinois at College of Chairman and Chief Scientist of BINACHIP Inc., a developer of products in electronic design automation, which was acquired by Xilinx Inc. in 2006. During 2005-2011, he was Founder, Chairman and Chief Scientist of BINACHIP Inc., a developer of products in electronic design automation. FastCompany listed Prith in their 100 top business leaders in 2009. He is a Fellow of the AAAS, ACM and IEEE, and a recipient of the 1996 ASEE Terman Award, the 2001 Taylor Booth Award from IEEE, and the 1987 NSF Presidential Young Investigator Award. Prith earned a B.Tech. in electronics engineering from the Indian Institute of Technology,

#### LIP-BU TAN

CHAIRMAN OF WALDEN INTERNATIONAL AND FORMER CEO/EXECUTIVE CHAIRMAN OF CADENCE DESIGN SYSTEMS

## Advancing Precision Medicine through Generative Al-driven Drug Development

#### Wednesday, July 12 | 9:00 am - 9:15 am

Traditionally, engineered products were designed with mechanical and electrical CAD tools, simulated and validated for correctness with CAE tools, prototypes were fabricated and tested, and products were then manufactured at scale in factories. This process required long product cycles often spanning years to build a new product. Today, virtually unlimited computing and storage available from the cloud is available for generative design to explore 10,000 design choices in near real-time, verify these products accurately through simulation (eliminating the need to build physical prototypes) and manufacture the products using additive manufacturing and factory automation. In the past, simulation tools were used to model specific, solitary physics such as mechanical structures, fluid dynamics, or electromagnetic interactions by solving second order partial differential equations using numerical methods. Today, simulation tools solve multi-physics problems (fluid-structure-electromagnetics interactions) at scale using the most complex solvers. We will explore the use of AI, Machine Learning and Deep Learning to accelerate these engineering simulations. We have identified four broad use cases of AI/ML applied to simulation: (1) Automatic parameter selection of simulation solvers to improve workflows and designer productivity (2) Augmenting simulation with AI/ML to accelerate simulation by factors of 100X (3) The use of AI/ML based generative design techniques to explore 10,000 designs automatically (4) Business intelligence to help improve engineering workflows. My talk will address three broad categories of AI/ML applied to simulation. (1) Top-down methods where we apply an AI/ML framework to a black box solver to train the ML models to improve run time (2) Bottom-up methods where we deeply embed the Al/ML methods inside the physics of our solvers. (3) Reduced order models where the order(?) of the solutions is reduced using Al/ML methods. We will illustrate each of these approaches on existing, commerical tools. As an example of a bottom-up approach, we will describe an ML-based Partial Differential Equation solver and apply it to accelerate Fluid Dynamics problems and will report our results on our Fluent CFD software. As an example of a top-down method, we will report on an ML framework to improve the productivity of any ML developer working in simulation. As an example of a reduced order model we will report on a hybrid digital twin tool called the Twin Builder. We will report on an end-to-end chip packaging solution using a combination of data-driven and physics-informed neural networks, as integrated within Ansys Redhawk/IcePak/Mechanical solutions for Conjugate Heat Transfer. We will describe approaches to support fast design exploration/optimization using ML frameworks. We will describe ML-enabled assistance in various steps of simulation workflows such as initial meshing, smart sub-modeling, user experience and automatic selection of parameters. We will report on automatically setting the best parameters in Fluent/Live AMG solver.

**ABOUT:** Lip-Bu Tan served as Executive Chair of the Board of Directors of Cadence since December 2021 and was a member of the Cadence Board of Directors since February 2004. He served as CEO of the company from 2009 to 2021 and as President from 2009 to 2017. He also serves as chairman of Walden International, the venture capital firm he founded in 1987, and is a founding managing partner of Walden Catalyst Ventures. Prior to joining Cadence, Mr. Tan was Vice President at Chappell & Co. and held management positions at EDS Nuclear and ECHO Energy. Mr. Tan is a member of The Business Council and serves on the boards of directors of Intel Corporation, Schneider Electric SE, Credo Technology Group Holding Ltd., and Green Hills Software. He also serves on the Board of Trustees and the School of Engineering Dean's Council at Carnegie Mellon University and on the University of California, Berkeley's Engineering Advisory Board. Mr. Tan received the Semiconductor Industry Association (SIA)'s 2022 Robert N. Noyce Award and the Global Semiconductor Alliance (GSA)'s 2016 Morris Chang Exemplary Leadership Award. Mr. Tan received a BS from Nanyang University in Singapore, an MS in nuclear engineering from the Massachusetts Institute of Technology, and an MBA from the University of San Francisco.

## VISIONARY PRESENTATIONS continued

#### **CECILIA METRA**

PROFESSOR AND THE DEPUTY PRESIDENT OF THE SCHOOL OF ENGINEERING, UNIVERSITY OF BOLOGNA

# AI Hardware Reliability and Safety Challenges to Enable the Future Metaverse

Thursday, July 13 | 9:00 am - 9:15 am

The Metaverse can be described as a new layer bridging the gap between the digital world and the real one. Today, we are assisting to the development of a significant variety of tools enabling a very accurate digital emulation of the real world (e.g., for product design), or an augmented reality experience (e.g., for education purposes), or the creation of a coupled digital-twin of a real entity (e.g., for product manufacturing and maintenance), etc. The Future Metaverse should include, interconnect and enhance all these already existing capabilities into a unified universe, consisting of interoperable digital and real worlds, with inclusive accessibility to all. Artificial Intelligence (AI) will play a fundamental role in enabling all of this, by providing human interaction with the metaverse (e.g., through speech and gesture recognition, object detection in images/videos, tactile sensing, etc.) and allowing a personalized experience in the metaverse (e.g., based on individual preferences, possible disabilities, etc.). Since AI will guide our integration in the future metaverse, reliability and safety of its implementing hardware with respect to faults and aging conditions possibly occurring during its operation in the field should be guaranteed. Safety and reliability challenges of the AI hardware to enable the future metaverse will be addressed.

**ABOUT:** Cecilia Metra is a Professor and the Deputy President of the School of Engineering at the University of Bologna, Italy, where she has worked since 1991, and from which she received the Laurea Degree in Electronic Engineering and the PhD in electronic engineering and computer science. In 2002, she was visiting faculty consultant for Intel Corporation. She is part of the Italian National Research Center on High Performance Computing, Big Data and Quantum Computing, and of the Italian Research Project on Security and Rights In the CyberSpace. She is 2022-2023 IEEE Director, Division V, and she was the 2019 President of the IEEE Computer Society. She is Co-Chair of the 'IEEE Metaverse'' Project of the IEEE Future Directions, and a member of several IEEE Computer Society and the IEEE Conferences and the IEEE Award Committees. She was a member of the Board of Governors of the IEEE Computer Society and the IEEE CEDA. She was Editor-in-Chief of the IEEE Transactions on Emerging Topics in Computing, and Associate Editor-in-Chief of the IEEE Transactions on Computers. She contributed to numerous IEEE international conferences/symposia/workshops as General/Program Chair, Technical Program Committee member, and Keynote/Invited Speaker.

## **KEYNOTE PRESENTATIONS**

#### ALBERTO L. SANGIOVANNI-VINCENTELLI

EDGAR L. AND HAROLD H. BUTTNER CHAIR OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCES AT THE UNIVERSITY OF CALIFORNIA AT BERKELEY

## Corsi e Ricorsi: Here We Go Again

Monday, July 10 | 9:15 am – 10:00 am

In 2003, I argued that semiconductor and system design, and design automation, have evolved by way of a repeating pattern of intuitive approaches, great insights and rigorous, if conservative, methodologies that I called "Corsi e Ricorsi", using the principles of Giambattista Vico, history philosopher of the XVI Century. Over the course of six decades, this phenomenon fueled an evolution in technologies and computational software that gradually freed silicon and system designers from the shackles of choice, empowering them to overcome 18 orders of magnitude of design complexity to date, never failing to bring the possibility horizon closer.

I will present the evolution of EDA as an effective and powerful early example of Artificial Intelligence, in its broadest sense as "the theory and development of computer systems able to perform tasks that normally require human intelligence", separate the hype from reality, comment on the present frenzy around machine learning applied to EDA, and reassure our community that design automation engineering is, more than ever, one of the world's most natural intelligence rich professions. Finally, I will discuss the challenges posed to EDA by the development of 3D integrated circuits and put them in the context of the evolution of packaging methods over the past 40 years.

**ABOUT:** Alberto Sangiovanni Vincentelli is the Edgar L. and Harold H. Buttner Chair of Electrical Engineering and Computer Sciences at the University of California at Berkeley. In 1980-1981, he was a Visiting Scientist at the Mathematical Sciences Department of the IBM T.J. Watson Research Center. In 1987, he was Visiting Professor at MIT. He is an author of over 800 papers, 17 books and 2 patents in the area of design tools and methodologies, large scale systems, embedded systems, hybrid systems and innovation. He was a co-founder of Cadence and Synopsys, the two leading companies in the area of Electronic Design Automation and the founder and Scientific Director of the PARADES Research Center in Rome.

#### **HEIKE RIEL**

IBM FELLOW, DEPARTMENT HEAD SCIENCE & TECHNOLOGY, IBM

## **Quantum Computing Roadmap**

Tuesday, July 11 | 9:15 am - 10:00 am

Despite the continued advances of digital computing including accelerators for artificial intelligence, there are still many important and relevant mathematical problems that are intractable for classical computers. Quantum Computers are a radically different approach and open a new trajectory to evolve computation and enable solving difficult and complex problems. In the past years significant progress has been made toward understanding the scope of quantum computing, pushing its hardware and software technology, developing applications, and advancing error mitigation/correction protocols. An entire new computing system is built from the bottom up. Advancing the state-of-the-art as quickly as possible requires pursuing in parallel improvements in three key metrics – scale, quality, and speed of quantum systems, as well as simultaneously providing advanced capabilities to exploit the performance and make them easy to use. Integrating new technologies such as advanced packaging, high-density control signal delivery, developing advanced qubit control electronics have already enabled scaling of superconducting quantum processors to 433-qubits. Combined with increases in quality and speed this has driven significant improvements in the performance of quantum computers. Moreover, the computational capabilities of today's quantum hardware can be extended by tight integration of quantum and classical resources using techniques like circuit knitting to accelerate the path towards quantum advantage. Developing approaches to connect individual quantum processors in various ways with classical as well as quantum communication links enables a modular approach to further scale quantum systems.

**ABOUT:** Heike Riel is IBM Fellow, Head of Science & Technology and Lead of IBM Research Quantum Europe at IBM Research. She is responsible for leading the research agenda of the Science & Technology department aiming to create scientific and technological breakthroughs in Quantum Computing, Physics of Artificial Intelligence, Nanoscience and Nanotechnology, Precision Diagnostics and Smart System Integration. She is a distinguished expert in nanotechnology and nanosciences and focuses her research on advancing the frontiers of information technology through the physical sciences. She contributed to advancements in the science and technology of nanoscale electronics, in particular the exploration and development of semiconducting nanowires and nanostructures for applications in future electronic and optoelectronic devices, in molecular electronics for future nanoscale switches and memory applications, and organic light-emitting diodes for display applications. Her current research interests include new materials and device concepts for future nanoelectronics for applications in quantum computing and neuromorphic computing. She also serves as the Deputy Director of the new Swiss National Competence Center for Research on Silicon Spin Qubits.

## **KEYNOTE PRESENTATIONS** continued

#### WALDEN RHINES

PRESIDENT AND CEO, CORNAMI, INC.

## Taking AI to the Next Level

Wednesday, July 12 | 9:15 am - 10:00 am

With forty years of involvement in product development of AI-related products, Dr. Rhines brings perspective to the emerging capabilities that will take AI to the next level of commercial reality. One of the most important enablers is the ability to protect data privacy and ownership while making the data available for intelligent queries. Rhines will address these and other issues that will drive the next wave in the AI revolution.

**ABOUT:** WALDEN C. (Wally) RHINES is President and CEO of Cornami, Inc., a fabless semiconductor and software company focused on fully homomorphic encryption. He was previously CEO of Mentor Graphics for 25 years and Chairman of the Board for 17 years. During his tenure at Mentor, revenue nearly quadrupled and market value of the company increased 10X. Prior to joining Mentor Graphics, Dr. Rhines was Executive Vice President, Semiconductor Group, responsible for TI's worldwide semiconductor business. Dr. Rhines has served on the boards of Cirrus Logic, QORVO, TriQuint Semiconductor, Global Logic, PTK Corp., Silvaco, Pallidus and as Chairman of the Electronic Design Automation Consortium (five two-year terms). He is a Lifetime Fellow of the IEEE. Dr. Rhines holds a Bachelor of Science degree in engineering from the University of Michigan, a Master of Science and PhD in materials science and engineering from Stanford University, an MBA from Southern Methodist University and Honorary Doctor of Technology degrees from the University of Florida and Nottingham Trent University. In 2021, the Global Semiconductor Alliance honored Dr. Rhines, with its prestigious Dr. Morris Chang Exemplary Leadership Award.

#### **MARK HOROWITZ**

YAHOO! FOUNDERS PROFESSOR, STANFORD UNIVERSITY

## Life Post Moore's Law: The New CAD Frontier

Thursday, July 13 | 9:15 am - 10:00 am

For over 50 years, information technology has relied upon Moore's Law: providing, for the same cost, 2x the number of logic transistors that were possible a few years prior. For much of that time, the smaller devices also provided dramatic energy and performance improvement through Dennard Scaling, but that scaling ended over a decade ago. While technology scaling continues, per transistor cost is no longer scaling in the advanced nodes. In this post Moore's Law reality, further price/performance improvement follows only from improving the efficiency of applications using innovative hardware and software techniques. Unfortunately, this need for innovative system solutions runs smack into the enormous complexity of designing and debugging contemporary VLSI based hardware/software platforms; a task so large it has caused the industry to consolidate, moving it away from innovation. To overcome this challenge, we need to develop a new set of CAD tools to enable small groups of application experts to selectively extend the performance of those successful platforms. Like the ASIC revolution in the 1980s, the goal of these tools is to enable a new set of designers, then board level logic designers, now application experts, to leverage the power of customized silicon solutions. Like then, these tools won't initially be useful for current chip designers, but over time will underly all designs. In the 1980s to provide access to logic designers, the key technologies were logic synthesis, simulation, and placement/routing of their designs to gate arrays and std cells. Today, the key is to realize you are creating an "app" for an existing platform, and not creating the system solution from scratch (which is both too expensive and error prone), and to leverage the fact that modern "chips" are made of many chiplets. The new set of tools must provide a design window familiar to application developers, with similar descriptive, performance tuning, and debug capabilities. These new tools will be tied to highly capable platforms that are used as the foundation, like the appStore model for mobile phones. This talk will try to convince you this might be possible, and where innovative tools are needed.

**ABOUT:** Mark Horowitz is the Yahoo! Founders Professor at Stanford University and was chair of the Electrical Engineering Department from 2008 to 2012. He received his BS and MS in Electrical Engineering from MIT in 1978, and his PhD from Stanford in 1984. Dr. Horowitz has received many awards for his work and has broad research interests. He has worked on many processor designs, from early RISC chips and in 1990 he took leave from Stanford to help start Rambus Inc, a company designing high-bandwidth memory interface technology. His work at both Rambus and Stanford drove high-speed link designs for many decades. In the 2000s he started a collaboration with Marc Levoy in computational photography which led to light-field photography and microscopy. His current research includes updating both analog and digital design methods, agile hardware design, and applying engineering to biology. He remains interested in learning new things, and building interdisciplinary teams.

## **SKYTALK PRESENTATIONS**

#### **DR. DEV SHENOY**

PRINCIPAL DIRECTOR FOR MICROELECTRONICS, DEPARTMENT OF DEFENSE

## Microelectronics Security: A Growing National Imperative Monday, July 10 | 1:00 pm – 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

Monday, July 10 | 1:00 pm – 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

The microelectronics industry continues to play a fundamental role in our nation's economic and national security, and technological standing. The recent CHIPS Act and ongoing Department of Defense initiatives such as the Rapid Assured Microelectronics Prototypes (RAMP) program, underscore the government's commitment to accelerating the nation's rapid pace of microelectronics innovation and enable U.S. development of the very best in circuit design, manufacturing, and packaging. But how are we ensuring security across the microelectronics supply chain?

Dr. Devanand Shenoy will provide insights into how a number of DoD and commercial initiatives and investments are strengthening our microelectronics security posture across the development and deployment of leading-edge microelectronics technologies. Learn more about how these programs present opportunities for the Design Automation Conference (DAC) community to participate in the strengthening of our microelectronics cybersecurity readiness.

**ABOUT:** Dr. Dev Shenoy joined the Office of the Under Secretary of Defense for Research and Engineering, OUSD(R&E), as the Principal Director for Microelectronics in July 2021. In this role, Dr. Shenoy is responsible for leading the Department of Defense's research and engineering efforts in Microelectronics. Prior to joining OUSD(R&E), Dr. Shenoy served as the Director of Microelectronics Innovation and as Director of Advanced Technologies at the University of Southern California's Information Sciences Institute. Prior to joining USC/ISI, Dr. Shenoy served as Chief Engineer in the Advanced Manufacturing Office at the Department of Energy (DOE) HQ. In that role, he co-authored DOE's 2015 QTR (Quadrennial Technology Review) that served as a blueprint for DOE's energy technology investments. Among other initiatives, Dr. Shenoy proposed and led a "Big Idea" for U.S. national security and economic competitiveness within the Office of EERE (Energy Efficiency and Renewable Energy) on "Beyond Moore Computing" with participation from eight DOE National Labs. Prior to joining DOE, Dr. Shenoy served as a Senior Advisor at the Manufacturing and Industrial Base Policy (MIBP) Office within the Office of the Secretary of Defense (OSD) as a detailee from the Army Night Vision and Sensors Directorate (NVESD) at Fort Belvoir. In that role, he co-led a Telecom initiative with the White House Office of Science and Technology Policy (OSTP) to explore U.S. opportunities in Optical networks.

## **DR. PAUL CUNNINGHAM**

SENIOR VICE PRESIDENT AND GENERAL MANAGER, CADENCE DESIGN SYSTEMS

## **Entering a New Era with EDA 2.0 and AI-Driven Electronic** System Design

Tuesday, July 11 | 1:00 pm - 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

At Cadence, we see a great opportunity for our industry to enter a new era of EDA 2.0, defined by Al-driven platforms that optimize horizontally across multiple runs of many tools throughout an entire system design program. Learn how EDA 2.0 is bringing all design and verification data together under a unified data platform—RTL, layouts, constraints, waveforms, coverage, reports, log files, state graphs, Al models, and metadata with our new Cadence Joint Enterprise Data and Al (JedAl) Platform.

**ABOUT:** Dr. Paul Cunningham has served as Senior Vice President and General Manager of the System Verification Group (SVG) since March 2021, running the division since 2018. His responsibilities include logic simulation, emulation, prototyping, formal verification, Verification IP, and functional debug. Prior to this role, Cunningham was responsible for Cadence's frontend digital design tools including logic synthesis and design-for-test. Dr. Cunningham joined Cadence in 2011 via the acquisition of Azuro, a startup developing concurrent physical optimization and useful skew clock tree synthesis technologies, where he was a co-founder and CEO. Dr. Cunningham holds a MS and a PhD in Computer Science from the University of Cambridge in the UK.

## **SKYTALK PRESENTATIONS** continued

#### **JEAN-PHILIPPE FRICKER**

FOUNDER AND CHIEF SYSTEMS ARCHITECT, CEREBRAS SYSTEMS

# The Cerebras CS-2: Designing an AI Accelerator Around the World's Largest 2.6 Trillion Transistor Chip

Wednesday, July 12 | 1:00 pm - 1:45 pm | DAC Pavilion, Level 2 Exhibit Hall

Today's exponential growth of neural networks is creating a demand for compute infrastructure that can't keep up with the traditional performance improvements gained through enhancements of semiconductors technology nodes. A co-designed approach is needed to keep up with the demand. We explore how increasing chip dimensions and resulting power and cooling densities are some of the enabling vectors of such co-design.

**ABOUT:** Jean-Philippe (J.P.) is Chief System Architect at Cerebras Systems. Before co-founding Cerebras, J.P. was Senior Hardware Architect at rack-scale flash array startup DSSD (acquired by EMC). Prior to DSSD, J.P. was Lead System Architect at SeaMicro where he designed three generations of fabric-based computer systems. Earlier in his career, J.P. was Director of Hardware Engineering at Alcatel-Lucent and Director of Hardware Engineering at Riverstone Networks. He holds an MS in Electrical Engineering from École Polytechnique Fédérale de Lausanne, Switzerland, and has authored 24 patents.

## **TECHTALK PRESENTATIONS**

#### MOHAMED KASSEM

CTO AND CO-FOUNDER, EFABLESS.COM

## Cloud But Not for Compute – A New Paradigm for Open IC Design

Monday, July 10 | 10:30 am – 11:15 am | Transformative Technology Theater, Level 1 Exhibit Hall

The advantages of cloud extend far beyond compute. Cloud enables secure collaboration at scale, and this is especially key for democratizing chip design. Cloud is the ideal platform for enabling open source reference designs in hardware, provide access to open-source/commercial tool suites, PDKs and everything else needed for end to end chip design. In this talk, you will hear about examples of entire communities leveraging an open platform for chip design, the rapidly evolving world of commercial chips based on open-source reference designs and inspirational success stories. The place where hardware and software developers, chip experts, students and researchers design, share, collaborate, fabricate and commercialize their own chips is here and NOW.

**ABOUT:** Mohamed Kassem is the CTO and Co-Founder of efabless.com, the first semiconductor company applying open community innovation to all aspects of product development. Prior to launching efabless in 2014, Mohamed held several technical and global leadership positions within Texas Instruments' Wireless Business Unit.

Mohamed joined TI in 2000 at the beginning of the digital telephony revolution fueled by the unprecedented integration of major phone functions on a single SoC. He led the first development of 45nm, 28nm analog & mixed-signal IP functions for wireless applications processors.

Mohamed holds a Masters degree in Electrical Engineering from the University of Waterloo, Ontario, Canada and A Bachelors degree in Communications & Electronics from Ain Shams University, Cairo, Egypt.

### **EDITH BEIGNÉ**

RESEARCH DIRECTOR OF AR/VR SILICON, META REALITY LABS

## **Building the Metaverse: Augmented Reality Applications and Integrated Circuits Challenges**

#### Monday, July 10 | 11:30 am - 12:30 pm | DAC Pavilion, Level 2 Exhibit Hall

Augmented reality is a set of technologies that will fundamentally change the way we interact with our environment. It represents a merging of the physical and the digital worlds into a rich, context aware and accessible user interface delivered through a socially acceptable form factor such as eyeglasses. One of the biggest challenges in realizing a comprehensive AR experience are the performance and form factor requiring new custom silicon. Innovations are mandatory to manage power consumption constraints and ensure both adequate battery life and a physically comfortable thermal envelope. This presentation reviews Augmented Reality and Virtual Reality applications and Silicon challenges.

**ABOUT:** Edith Beigné is the Research Director of AR/VR Silicon at Meta Reality Labs where she leads research projects driving the future of AR devices. Her main research interests are low power digital and mixed-signal circuits and design with emerging technologies. Over the past 20 years, she has been focusing her research on low power and adaptive circuit techniques, exploiting new design techniques and advanced technology nodes for different applications ranging from high performance multi-processors to ultra-low power SoC, and, more recently, AR/VR applications. She is the Executive vice chair of ISSCC 2024, was the technical chair of ISSCC 2022 and part of ISSCC TPC since 2014, part of VLSI symposium TPC between 2015 and 2020. Distinguished Lecturer for the SSCS in 2016/2017, Women-in-Circuits Committee chair and JSSC Associate Editor since 2018. She visited Stanford University in 2018 to research on emerging technologies and new architectures.

## **TECHTALK PRESENTATIONS** continued

#### **ROBERT WILLE**

CHIEF SCIENTIFIC OFFICER, SOFTWARE COMPETENCE CENTER

## **Design Automation for Quantum Computing**

Monday, July 10 | 3:00 pm - 3:45 pm | DAC Pavilion, Level 2 Exhibit Hall

Quantum computers have the potential to solve certain tasks that would take millennia to complete even with the fastest (conventional) supercomputer. Numerous quantum computing applications with a near-term perspective (e.g., for finance, chemistry, machine learning, optimization) and with a long-term perspective (i.e., cryptography, database search) are currently investigated.

The Design Automation Community needs to be ready for this! In fact, due to the radically different computational primitives, seemingly simple tasks in the design of corresponding computers and algorithms get substantially harder for quantum computing compared to conventional circuits and systems. This affects how we currently conduct design automation for quantum computing — or how we do not. In fact, established programming languages, synthesizers, design tools, test, or verification schemes do not work for quantum computers anymore. In many aspects, considering the design for quantum computers, we are back at square one. And this may lead to a situation where we may have quantum computers but no proper (automatic) methods that aid us in using their potential!

In this talk, we discuss how design automation can help and how we can get design automation experts excited for this emerging technology. To this end, we report from our long-standing expertise in this domain and our experiences on bridging the quantum computing and the EDA community. We illustrate that quantum computing is no "rocket science" and, using proper models and abstractions, design automation can make a huge difference. This is showcased by several methods and software tools which have been developed in the past years with design automation in mind. Finally, the integration of these methods, tools, and mindsets into entire ecosystems (covering the entire flow from applications to eventual realization) is presented.

**ABOUT:** Robert Wille is Full and Distinguished Professor at the Technical University of Munich, Germany, and Chief Scientific Officer at the Software Competence Center Hagenberg GmbH, Austria (a technology transfer company with more than 100 employees). For more than 15 years, he is working on topics in the domain of quantum computing and successfully established design automation concepts in this domain. The impact of his work is reflected by numerous awards such as Best Paper Awards, e.g., at TCAD and ICCAD, a DAC Under-40 Innovator Award, a Google Research Award, etc., collaborations with industrial partners in this domain, as well as his involvement in prestigious projects and initiatives, e.g., within the scheme of an ERC Consolidator Grant or the comprehensive quantum computing initiative of the Munich Quantum Valley.

## MAJID AHADI DOLATSARA

SOFTWARE R&D ENGINEER, KEYSIGHT TECHNOLOGIES

## **Revolutionizing EDA: The Power of AI, ML, and NLP**

Tuesday, July 11 | 10:30 am – 11:15 am | Transformative Technology Theater, Level 1 Exhibit Hall

The integration of AI, ML, and NLP techniques in EDA has the potential to significantly improve the efficiency, innovation, and quality of electronic systems. Customers in the semiconductor and EDA industries can benefit from reduced design time, increased reliability, and enhanced performance. This talk will draw upon use cases and research that have shown the integration of AI, ML, and NLP techniques in EDA has led to significant improvements in design accuracy. For example, ML algorithms have been used to optimize routing in complex circuits, while NLP techniques have been used to extract relevant design information from textual specifications. The talk will cover the use of unsupervised, supervised, and reinforcement learning techniques and NLP techniques in EDA tools and workflows.

**ABOUT:** Majid Ahadi Dolatsara received the B.Sc. degree in electrical engineering from K. N. Toosi University of Technology, Tehran, Iran, in 2013, the M.Sc. degree in electrical engineering from Colorado State University, Fort Collins, CO, USA, in 2016, and the Ph.D. degree in electrical and computer engineering from Georgia Institute of Technology, Atlanta, GA, USA, in 2021. He has won the Richard B. Schulz best paper award in transactions on electromagnetic compatibility in 2022.

He is currently employed by Keysight Technologies, Calabasas, CA, USA, as a research and development software engineer, working on electronic design automation software. His research interests include development of numerical and machine learning algorithms for high performance simulation in the area of signal and power integrity.

## **TECHTALK PRESENTATIONS** continued

#### **EZEKIEL 'ZEKE' WHEELER**

YOUNG INNOVATOR, HAM RADIO OPERATOR (KJ7NLL)

## **DIY Orbital Tracking System for Space Communication: A Project to Contact the International Space Station**

Tuesday, July 11 | 11:30 am - 12:30 pm | DAC Pavilion, Level 2 Exhibit Hall

Zeke Wheeler was 8 years-old when he asked his dad how he could call the astronauts on the International Space Station (ISS). This casual question resulted in a three-year epic STEM-learning adventure to contact the ISS, which included obtaining an FCC license to operate a radio, creating a satellite tracker using Legos, and researching, designing and building original circuit boards and antennas with his dad using Cadence Microwave Office. There have been trials as well as triumphs in this ongoing project of fortitude and resilience.

**ABOUT:** Zeke Wheeler is twelve years-old and demonstrated an early interest in engineering. In April he received the Best Presentation Award in the Multiphysics In-Design Analysis Track at CadenceLIVE 2023. Since 2020 he has been working to contact the International Space Station, using circuit boards and antennas designed in Microwave Office, and a satellite tracker made from Legos. He looks forward to sharing his project with the DAC community.

## ERIK BERG

MICROSOFT

## What ChatGPT and Generative AI means for Semiconductor Design and Development

Wednesday, July 12 | 11:30 am - 12:30 pm | DAC Pavilion, Level 2 Exhibit Hall

ChatGPT has generated a lot of excitement and speculation lately. People are asking how generative AI will affect us all. Questions around generative AI's potential and limitations are top of mind.

This talk will touch on how AI/ML is helping in the semiconductor industry, and what generative AI can do for the chip design process. How it is likely to affect how we build chips, and what it could mean for semiconductor productivity.

ABOUT: Erik Berg is a Principal Engineer at Microsoft and an innovative leader in the field of SoC verification.

With a career that has been guided by the ambition to maximize the impact of everyone on his team, Erik brings a unique perspective to his work. He is driven by the challenge of scaling verification teams and reducing risk through methodology, tooling, and automation initiatives. As part of Erik's passion for pushing the boundaries of hardware development, he leads Microsoft's Steering Group for the application of machine learning and artificial intelligence in this domain.

One of Erik's notable contributions to the field is the invention of the Debug Decision Tree (DDT) tool. Recognizing the critical importance of debug efficiency, he developed DDT to enhance debug knowledge sharing and automation and collaborated with Synopsys to launch DDT to the market in 2023.

Before joining Microsoft, Erik spent 19 years at Intel, holding verification roles covering IP, SOC, formal, power, and performance. His extensive experience across different domains has provided him with a comprehensive understanding of the complexities involved in creating cutting-edge hardware solutions.

Beyond his professional achievements, Erik holds a PhD from the University of Michigan, specializing in nanofabrication and single electron transistors. His academic background reflects his commitment to staying at the forefront of technological advancements.

## **IN MEMORIAM**

#### Philip Raymond Moorby 1953 – 2022

Philip Raymond Moorby passed away on 15 September at the age of 69 in Rockport.

Phil was born in Birmingham UK on 25 April 1953, fourth child of Ken and Clarice Moorby. He received a degree in mathematics from the University of Southampton, UK followed by a master's degree in computer science in 1974 at Manchester University, UK.

In 1984 Phil joined a start-up in the US and moved to Massachusetts. Over the following years he developed and refined the Verilog simulator which became the gold standard for designing the transistor devices we use every day, and which pushed the limits of engineering, chemistry, and physics. Phil won many awards for his work. In 2016 he received a Fellow Award from the Computer History Museum joining Silicon Valley's most influential technologists.

Phil met his wife, Mary in 2013 and moved to Rockport to join her. He subsequently devoted his time to photography, woodworking, gardening and traveling worldwide with Mary.

Phil leaves behind his wife Mary, his daughter Jill, his stepchildren Brooke, Claire, and Brett whom he loved as his own, as well as his two sisters Jean and Kay, his brother Jack, and various grandchildren nieces and nephews.

### Andres Takach 1964 – 2022

Andres was a research scientist at Mentor Graphics (now Siemens EDA) Catapult High-Level Synthesis group. He was also very active in the High-Level Synthesis community contributing in conferences,

TPCs and reviewing papers. He was the chair of the OSCI standards committee for the SystemC Synthesizable Subset.

#### Richard Goering 1951 – 2023

Richard James Goering, was a technology journalist, who covered IC design and electronic design automation (EDA) starting in 1985. He wrote

extensively about the EDA software technology that's essential for the design of all semiconductors and electronic systems today. In addition to in-depth stories about IC design technology, he wrote about business trends, legal issues, standards efforts, mergers and acquisitions, and the colorful people behind the design of electronic systems and ICs. Richard was best known for serving as EE Times' EDA editor for 17 years, where he wrote hundreds of articles for both the print and on-line editions of the electronics industry's premier weekly newspaper.

## DAC AWARDS AND SCHOLARSHIPS

#### 2023 DAC UNDER-40 INNOVATORS AWARD

**Jianli Chen**, Shanghai LEDA Technology Co., Ltd., Fudan University

Pierre-Emmanuel Gaillardon, University of Utah

Sriram Rajamanohar, Keysight

Yiyu Shi, University of Notre Dame

#### 2023 MARIE R. PISTILLI WOMEN IN ENGINEERING ACHIEVEMENT AWARD

X. Sharon Hu, University of Notre Dame

P.O. PISTILLI UNDERGRADUATE SCHOLARSHIP FOR ADVANCEMENT IN COMPUTER SCIENCE AND ELECTRICAL ENGINEERING

Shane Williams, Princeton University

#### ACM/SIGDA

#### **ACM FELLOWS**

David Atienza, Swiss Federal Institute of TechnologyJörg Henkel, Karlsruhe Institute of TechnologyFarinaz Koushanfar, UC San Diego

#### **2023 ACM TODAES BEST PAPER AWARD**

Atefeh Sohrabizadeh, Cody (Hao) Yu, Min Gao, Jason Cong, UCLA

## ACM TODAES ROOKIE AUTHOR OF THE YEAR (RAY) AWARD

Yue Tang, University of Pittsburgh

#### BEST PAPER AWARD FOR ACM TRANSACTIONS ON RECONFIGURABLE TECHNOLOGY AND SYSTEMS (TRETS)

Niansong Zhang, Xiang Chen, Nachiket Kapre, University of Waterloo

#### ACM SIGDA DISTNGUISHED SERVICE AWARD

Tulika Mitra, National University of Singapore

Patrick Groeneveld, Cerebras Systems

#### ACM SIGDA OUTSTANDING NEW FACULTY AWARD

Tsung-Wei Huang, University of Utah

ACM SIGDA OUTSTANDING PH.D. DISSERTATION AWARD Zhiyao Xie

Advisors: Yiran Chen and Hai Li, Duke University

SIGDA PIONEERING ACHIEVEMENT AWARD Ron Rohrer, Southern Methodist University

#### SIGDA MERITORIOUS SERVICE AWARD

Robert Wille, Technical University of Munich

Lei Jiang, Indiana University Bloomington

Hui-Ru Jiang, National Taiwan University

Jeyavijayan (JV) Rajendran, Texas A&M University

#### IEEE/CEDA

## 2023 PHIL KAUFMAN AWARD FOR DISTINGUISHED CONTRIBUTIONS TO ELECTRONIC SYSTEMS DESIGN

For overall impact on Electronics industry through contributions to scan design for testability, related test automation.

• • •

Giovanni De Micheli, EPFL, Lausanne, Switzerland

#### **IEEE CEDA OUTSTANDING SERVICE AWARD**

For outstanding service to the EDA community as DAC General Chair in 2023.

Robert Oshana, NXP Semiconductors

#### **IEEE FELLOWS**

Sung Kyu Lim, Georgia Institute of Technology

Sherief Reda, Brown University

Zhiru Zhang, Cornell University

Norman Chang, ANSYS, Inc

Ryan Kastner, University of California-San Diego

#### IEEE/ACM A RICHARD NEWTON TECHNICAL IMPACT AWARD IN ELECTRONIC DESIGN AUTOMATION

Moshe Vardi, Pierre Wolper, Université de Liège

#### IEEE DONALD O. PEDERSON SOLID-STATE CIRCUITS AWARD

Ingrid Verbauwhede, KI Leuven

#### IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS (TCAD) DONALD O. PEDERSON BEST PAPER AWARD

DNN+NeuroSim V2.0: An End-to-End Benchmarking Framework for Compute-in-Memory Accelerators for On-Chip Training

Xiaochen Peng, Shanshi Huang, Hongwu Jiang, Anni Lu, Shimeng Yu

#### **IEEE ANDREW S. GROVE AWARD**

H.-S. Philip Wong, Stanford University

## DAC PAVILION SCHEDULE - BOOTH #2259

#### Monday, July 10

#### 10:15 am - 11:15 am

## PANEL: THE BEST OF BOTH WORLDS – BRIDGING THE GAP BETWEEN EDA, SYSTEM AND MANUFACTURING

Moderator: Jay Vleeschhouwer, Griffin Securities

Panelists: John Lee, Ansys; Tom Beckley, Cadence Design Systems; Brian Thompson, PTC; Tony Hemmelgarn, Siemens Digital Industries Software; Stephane Sireau, Dassault Systemes

#### 11:30 am - 12:30 pm

TECHTALK: BUILDING THE METAVERSE: AUGMENTED REALITY APPLICATIONS AND INTEGRATED CIRCUITS CHALLENGES

Speaker: Edith Beigne, Meta

#### 1:00 pm – 1:45 pm

SKYTALK: MICROELECTRONICS SECURITY: A GROWING NATIONAL IMPERATIVE

Speaker: Dr. Devanand Shenoy, U.S. Department of Defense

#### 2:00 pm – 2:45 pm

PANEL: FAAS – HYPED UP NEW ACRONYM OR A WAY TO LEVEL THE SIMULATION PLAYING FIELD? THE OPPORTUNITIES AND CHALLENGES OF FAAS (FUNCTION AS A SERVICE) FOR ACCELERATING SIMULATION AND ANALYSIS.

Moderator: Ben Jordan, JordanDSP

Panelists: Rajath Narasimha, Keysight; Ryan Magruder, Rescale; Yi Cao, Meta Reality Labs; Kenneth Hill, Eviden

#### 3:00 pm – 3:45 pm

TECHTALK: DESIGN AUTOMATION FOR QUANTUM COMPUTING

Speaker: Robert Wille, Software Competence Center

5:00 pm – 6:00 pm GLADIATOR ARENA POSTER BATTLE

#### Tuesday, July 11

#### 10:15 am – 11:15 am ANALYST REVIEW: A VIEW FROM WALL STREET: THE STATE OF EDA

Speaker: Jay Vleeschhouwer, Griffin Securities

#### 11:30 am - 12:30 pm

#### TECHTALK: DIY ORBITAL TRACKING SYSTEM FOR SPACE COMMUNICATION: A PROJECT TO CONTACT THE INTERNATIONAL SPACE STATION

Speaker: Zeke Wheeler, HAM Radio Operator (KJ7NLL)

#### 1:00 pm – 1:45 pm

#### SKYTALK: ENTERING A NEW ERA WITH EDA 2.0 AND AI-DRIVEN ELECTRONIC SYSTEM DESIGN

Speaker: Paul Cunningham, System Verification Group

#### 2:00 pm – 2:45 pm

## PANEL: DESIGN CONSIDERATIONS AND TRADEOFFS FOR 2.5D CHIPLET SOLUTIONS

Moderator: Ed Sperling, Semiconductor Engineering Panelists: Saif Alam, Movellus; Craig Bishop, Deca Technologies; Mark Kuemerle, Marvell; Tony Mastroianni, Siemens EDA

#### 3:00 pm – 3:45 pm

## PANEL: ASK ME ANYTHING WITH JOE COSTELLO AND WALLY RHINES

Moderator: Brian Fuller, Arm Ltd.

Panelists: Joe Costello, Metrics, Kwikbit, Arrikto, Acromove; Wally Rhines, Cornami, Inc.

5:00 pm – 6:00 pm

**GLADIATOR ARENA POSTER BATTLE**

#### Wednesday, July 12

#### 10:15 am - 11:15 am

## ANALYST REVIEW: THE AI HARDWARE SHOW LIVE: SILICON OR SURVIVAL

Speakers: Ian Cutress, More Than Moore; Sally Ward-Foxton, EE-Times

#### 11:30 am - 12:30 pm

TECHTALK: WHAT CHATGPT AND GENERATIVE AI MEANS FOR SEMICONDUCTOR DESIGN AND DEVELOPMENT Speaker: Erik Berg, Microsoft

#### 1:00 pm – 1:45 pm

SKYTALK: THE CEREBRAS CS-2: DESIGNING AN AI ACCELERATOR AROUND THE WORLD'S LARGEST 2.6 TRILLION TRANSISTOR CHIP

Speaker: Jean-Philippe Fricker, Cerebras

#### 2:00 pm – 2:45 pm

#### PANEL: IS SYSTEMS ENGINEERING THE SOLUTION TO THE LIMITS OF DENNARD SCALING AND MOORE'S LAW?

Moderator: Alix Paultre, Endeavor B2B Panelists: Mark Malinoski, Siemens EDA; Larry Williams, Ansys; Brett Hillhouse, IBM; Pooria Yaghini, SpaceX

#### 3:00 pm – 3:45 pm

## PANEL: THE INDUSTRY 4.0 REVOLUTION OF SEMICONDUCTOR DESIGN

Moderator: Brian Bailey, Semiconductor Engineering Panelists: Vijay Narayanan, proteanTecs; Mujtaba Hamid, Microsoft; KT Moore, Cadence Design Systems, Inc.; Mohit Gupta, Aphawave Semi

#### 5:00 pm – 6:00 pm

GLADIATOR ARENA POSTER BATTLE AND ENGINEERING TRACK PRESENTATION AWARDS

#### Sunday, July 9, 2023

#### **2ND CAD FOR HARDWARE SECURITY** WORKSHOP (CAD4SEC 2023)

Time: 8:00 AM - 5:00 PM Event Type: Workshop Topic Area(s): Security Room: 3008, 3rd Floor

Organizer(s): Farimah Farahmandi, Mark Tehranipoor, University of Florida, Gainesville, FL

Security vulnerabilities in hardware designs may turn out to be catastrophic as it is almost impossible to patch them once the hardware design has been manufactured. The emerging and ever-increasing security vulnerabilities in modern/complex hardware designs have been studied in recent years, e.g., side-channel leakage, information leakage, access control violations, and malicious functionality. These attacks can virtually circumvent the security mechanisms built at pre-silicon and put the chips/systems at risk. Ensuring the security of hardware designs is challenging due to their huge complexity, aggressive time-to-markets, limited security-oriented knowledge of designers, high-recurring cost of maintaining large teams/devices, the difficulty of establishing security metrics, etc. In such a circumstance, it is difficult to manually analyze the design implementation in different levels of abstraction to identify potential vulnerabilities. Moreover, it is costly for a design house to keep many security experts. Therefore, the semiconductor industry and system integrators started to look for a set of metrics, reusable security solutions, and automatic computer-aided design (CAD) tools to aid analysis, identifying, root-causing, and mitigating SoC security problems.

The source of security vulnerabilities in hardware designs is manifold: (i) lack of in-depth security knowledge; (ii) design transformation (in IC supply chain or revisioning); (iii) Ever-increasing threat surfaces; (iv) unintentional aggressive optimization by CAD tools. In such circumstances, all hardware design teams must have automatic CAD solutions to be able to analyze the security of the hardware designs thoroughly, at all levels of abstraction, and against all existing threats (e.g., fault injection, side-channel, and hardware Trojan attacks). CAD tools must evaluate the security of the design in the pre-silicon stage and suggest possible countermeasures while it is possible to modify the design and address the potential vulnerabilities.

In consideration of the above challenges and possible solutions and continuation of the 1st (inauguration) CAD4Sec workshop successfully held last year at DAC'59 with more than 80 attendees, we sketch out the extension of this community-wide event by inviting the experts from the industry, academia, and government to expand the knowledge, to represent the need for, and to share the recent progress on the development of automatic security CAD solutions. Additionally, the 2nd CAD4Sec workshop will extend the size and the involvement of practical demonstrations on the recent CAD for security tools by both industries/ academia. There will be a panel discussion consisting of experts in the field to talk about the roadmap for CAD for security development. In continuation to the 1st CAD4Sec workshop, the 2nd CAD4Sec workshop will contain several technical talks on the scope of metrics and CAD as the followina:

- CAD for Electromagnetic Radiation Assessment

- . CAD for Security Property Generation

- CAD for Security-oriented Equivalency Checking

- CAD for Malicious Functionality •

- CAD for Security Monitoring and Validation

- CAD for Security Verification of Advanced Packaging

- CAD for Secure Heterogeneous Integration Assessment

- CAD for Physical Probing Assessment •

- CAD for (Anti-)Reverse Engineering Assessment •

#### **4TH ROAD4NN WORKSHOP: RESEARCH OPEN** AUTOMATIC DESIGN FOR NEURAL NETWORKS

Time: 8:00 AM – 5:00 PM Event Type: Workshop Topic Area(s): AI Room: 3003, 3rd Floor

Organizer(s): Zhenman Fang, Simon Fraser University, Vancouver, Canada; Yanzhi Wang, Northeastern University, Boston, MA; Linghao Song, University of California, Los Angeles, CA

In the past decade, machine learning, especially neural network based deep learning, has achieved an amazing success. Various neural networks, such as CNNs, RNNs, LSTMs, Transformers, Vision Transformers, GNNs, and SNNs, have been deployed for various industrial applications like image classification, speech recognition, and automated control. On one hand, there is a very fast algorithm evolvement of neural network models, and almost every week there is a new model from a major academic and/or industry institute. On the other hand, all major industry giants have been developing and/or deploying specialized hardware platforms to accelerate the performance and energy-efficiency of neural networks across the cloud and edge devices. This includes Nvidia GPU, Intel Nervana/Habana/Loihi ASICs, Xilinx FPGAs, Google TPUs, Microsoft Brainwave, Amazon Inferentia, to name just a few. However, there is a significant gap between the fast algorithm evolvement and staggering hardware development, hence calling for broader participation in software-hardware co-design from both academia and industry.

In this workshop, we focus on the research open automatic design for neural networks, a holistic open source approach to general-purpose computer systems broadly inspired by neural networks. More specifically, we discuss full stack open source infrastructure support to develop and deploy novel neural networks, including novel algorithms and applications, hardware architectures and emerging devices, as well as programming, system, and tool support. We plan to bring together academic and industry experts to share their experience, discuss challenges they face as well as potential focus areas for the community. Below is the planned workshop content.

- CAD for Power/Timing Side Channel Assessment •

- CAD for Timing Side Channel Assessment

- CAD for Fault Injection Assessment

| Research<br>Sessions | Special<br>Session | Panel | Tutorial | Workshop;<br>Hands-on Labs | Transformative<br>Technologies | DAC Pavilion Panel;<br>Analyst Review | TechTalk<br>SKYTalk | Keynotes a<br>Visionary T |

|----------------------|--------------------|-------|----------|----------------------------|--------------------------------|---------------------------------------|---------------------|---------------------------|

|                      |                    |       |          |                            | Theater                        |                                       |                     |                           |

Engineering Track

25

#### Sunday, July 9, 2023

#### IN-MEMORY ARCHITECTURES AND COMPUTING APPLICATIONS WORKSHOP (IMACAW) – 2ND EDITION

Time: 8:00 AM – 5:00 PM Event Type: Workshop Topic Area(s): Design Room: 3004, 3rd Floor

**Organizer(s):** Nima TaheriNejad, Heidelberg University, Heidelberg, Germany; Alberto Bosio, Lyon Institute of Nanotechnology, Lyon, France; Deliang Fan, Arizona State University, Tempe, AZ

Today's computer architectures and device technologies used to manufacture them are facing major challenges, rendering them incapable of delivering the performances required by complex applications such as Big-Data processing and Artificial Intelligence (AI). The iMACAW workshop aims at providing a forum to discuss In-Memory-Computing (as an alternative architecture) and its potential applications. To this end, we take a cross-layer and cross-technology approach covering Stateof-the-Art (SoA) works that use SRAM, DRAM, FLASH, RRAM, PCM, MRAM, or FeFET as their memory technology. The workshop also aims at reinforcing the In-Memory-Computing (IMC) community and at offering a holistic vision of this emerging computing paradigm to the design automation communities.

This workshop will provide an opportunity for the audience to listen to invited speakers who are pioneers of the field, learn from them, ask questions, and interact with them. Open submission contributors also get the opportunity to share their knowledge, present their most-recent work, and their work in progress with the community, interact with other experts in the field, and receive feedback.

#### SSH-SOC: SECURITY AND SAFETY IN HETEROGENEOUS OPEN SYSTEM-ON-CHIP PLATFORMS

Time: 8:00 AM – 5:00 PM Event Type: Workshop Topic Area(s): Security Room: 3010, 3rd Floor

**Organizer(s):** Francesco Restuccia, University of California, San Diego, San Diego, CA; Biruk Seyoum, Columbia University, New York, NY; Davide Rossi, University of Bologna, Bologna, Italy; Luca Benini, ETH Zürich, Switzerland

The diminishing returns of technology scaling on performance have paved the way for innovation in computer architecture towards heterogeneous, domain-specific architectures.

Modern systems increasingly comprise domain-specific accelerators as well as specialized system components (buses, network-on-chip, peripherals, sensors, etc..) to efficiently handle the complex and computationally demanding workloads.

Panel

A popular approach to reduce the SoC design complexity involves a hierarchical strategy of differentiating the system design effort for the components of the heterogeneous architecture. This includes: (i) expensive in-house RTL development for the most critical modules, (ii) leveraging the most recent high-level synthesis (HLS) tools, and/or (iii) outsourcing highly-specialized third-party intellectual property (IP) modules to reduce cost and development time.

Despite its benefits, a diversified design methodology exacerbates the system integration challenge. Furthermore, several recent works have demonstrated how non-careful system integration can lead to dangerous conditions capable of affecting the security, safety, and performance of the system. This can derive from the combination of multiple aspects involving development bugs, lack of specifications, superficial verifications of the behavior of the IP components at the system level, and scarcity of mechanisms supporting the safe and secure system execution.

Such challenges require novel approaches in the design and verification process, in particular when dealing with the strict safety and security requirements of mission-critical systems. The research community can have a disruptive role in facing these challenges – the availability of the full codebase of multiple mature open hardware architectures and reconfigurable platforms represents an unprecedented opportunity for the development, testing, and native integration of novel mechanisms, tools, and analysis supporting security, safety, and performance efficiency for the development of the next-generation of systems.

This workshop welcomes work-in-progress contributions and novel directions to tackle the challenges and profit from the opportunities provided by open hardware designs and architectures for the development of next-generation heterogeneous SoCs. The topics for the workshop include, but are not limited to:

- Security verification for hardware designs and system architectures

- Architectural aspects of secure system integration

- Secure system integration of third-party hardware components

- · Automated firmware generation supporting secure system execution

- · Security aspects of reconfigurable designs

- · Time-predictable system execution in open-hardware designs

- Performance analysis, timing analysis, and worst-case analysis supporting time-predictable system execution and/or communications in open-hardware designs

- Automated firmware generation supporting time-predictable execution

- Fault tolerance and execution in harsh conditions leveraging openhardware designs

- System architectures and methodologies supporting energy efficient/ performant system execution in open-hardware designs

- Hardware/software co-design, co-integration and co-verification of open-source processors, accelerators, and components

- Open architectures for reconfigurable platforms and open CAD tools

- Tools and analysis for open FPGAs and reconfigurable platforms

Research Sessions Special Session Tutorial

Workshop; Transformative Hands-on Labs Technologies Theater

Transformative DAC Pavilion Panel; Technologies Analyst Review

l; TechTalk SKYTalk Keynotes and Visionary Talks Engineering Track

26

Sunday, July 9, 2023

#### THE SIXTH INTERNATIONAL WORKSHOP ON DESIGN AUTOMATION FOR CYBER-PHYSICAL SYSTEMS (DACPS)

Time: 8:00 AM – 5:00 PM Event Type: Workshop Topic Area(s): Embedded Systems and Software Room: 3002, 3rd Floor

**Organizer(s):** Xun Jiao, Villanova University, Villanova, PA; Chao Huang, University of Liverpool, United Kingdom