# CprE 281: Digital Logic

#### **Instructor: Alexander Stoytchev**

http://www.ece.iastate.edu/~alexs/classes/

# **Logic Gates**

CprE 281: Digital Logic Iowa State University, Ames, IA Copyright © Alexander Stoytchev

# **Administrative Stuff**

- HW1 is out. It is due on Monday Aug 24 @ 4pm.

- Submit it as a PDF upload on Canvas before the start of the lecture.

- You can write the solutions on paper and then scan the pages to make \*\*one\*\* PDF file.

- No late homeworks will be accepted.

- Please write clearly on the first page:

- your name

- student ID

- Iab section number

### CprE 281: Digital Logic

Fall 2020, 4:25 - 5:15 p.m. (Mondays, Wednesdays, and Fridays) Course delivery is WWW (synchronous) Instructor: <u>Alexander Stoytchev</u>

- Syllabus

- Class Schedule (Tentative)

- Lecture Notes (also in PDF)

- <u>Labs</u>

- Recitations

- Extra Readings

- Verilog Stuff

- <u>Verilog Reference</u>

- <u>i281 CPU</u>

• <u>Homework 1</u> (Due on Monday Aug 24 @ 4pm)

# Labs Next Week

- Please download and read the lab assignment for next week before you go to your lab section.

- https://www.ece.iastate.edu/~alexs/classes/2020\_Fall\_281/labs/Instructions/

- https://www.ece.iastate.edu/~alexs/classes/2020\_Fall\_281/labs/Lab\_01/

- You must and do the prelab before you go to the lab.

- The TAs will check your prelab answers at the beginning of the recitation. If you don't have it done you'll lose 20% of the lab grade for that lab.

### CprE 281: Digital Logic

Fall 2020, 4:25 - 5:15 p.m. (Mondays, Wednesdays, and Fridays) Course delivery is WWW (synchronous) Instructor: <u>Alexander Stoytchev</u>

- <u>Syllabus</u>

- Class Schedule (Tentative)

- Lecture Notes (also in PDF)

- <u>Labs</u>

- Recitations

- Extra Readings

- Verilog Stuff

- <u>Verilog Reference</u>

- <u>i281 CPU</u>

- Homework 1 (Due on Monday Aug 24 @ 4pm)

| $\leftarrow$ $\rightarrow$ C $\textcircled{0}$ | https://www.ece.iastate.edu/~ale | exs/classes/2020_Fall_281/labs/ | 150%     |

|------------------------------------------------|----------------------------------|---------------------------------|----------|

| Index of /                                     |                                  | ses/2020_Fall_2                 | 281/labs |

| Parent Director                                | <u>y</u>                         | -                               |          |

| Instructions/                                  | 21-Aug-2020 15:21                | -                               |          |

| Lab_01/                                        | 21-Aug-2020 15:22                | -                               |          |

| Lab_02/                                        | 18-Aug-2020 16:48                | -                               |          |

| Lab_03/                                        | 18-Aug-2020 16:51                | -                               |          |

| Lab_04/                                        | 18-Aug-2020 16:53                | -                               |          |

| Lab_05/                                        | 18-Aug-2020 16:56                | -                               |          |

| <u>Lab_06/</u>                                 | 18-Aug-2020 16:58                | -                               |          |

| Lab_07/                                        | 18-Aug-2020 16:59                | -                               |          |

| Lab_08/                                        | 18-Aug-2020 17:02                | -                               |          |

| <u>Lab_09/</u>                                 | 18-Aug-2020 17:05                | -                               |          |

| <u>Lab_10/</u>                                 | 18-Aug-2020 17:06                | -                               |          |

| Lab_11/                                        | 18-Aug-2020 17:08                | -                               |          |

| Lab_12/                                        | 18-Aug-2020 17:20                | -                               |          |

| Mini_Project/                                  | 18-Aug-2020 17:10                | -                               |          |

☑ ▲ https://www.ece.iastate.edu/~alexs/classes/2020\_Fall\_281/labs/Instructions/

150% .... 🖸 🏠 🔍 Search

### Index of /~alexs/classes/2020\_Fall\_281/labs/Instructions

| Name                           | Last modified     | Size Description |

|--------------------------------|-------------------|------------------|

| Parent Directory               |                   | -                |

| PrE_281_Lab_Online_Access.docx | 18-Aug-2020 16:35 | 15K              |

| CprE_281_Lab_Online_Access.pdf | 18-Aug-2020 16:35 | 17K              |

| ModelSIM_Guide.docx            | 20-Aug-2020 11:29 | 2.6M             |

| ModelSIM_Guide.pdf             | 20-Aug-2020 11:30 | 1.5M             |

|                                |                   |                  |

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

| $\leftarrow$ $\rightarrow$ C $\textcircled{o}$ | https://www.ece.iastate.edu/~a | lexs/classes/2020_Fall_281/I | abs/   | 150%      |

|------------------------------------------------|--------------------------------|------------------------------|--------|-----------|

| Index of /                                     | ~alexs/clas                    | ses/2020_                    | _Fall_ | _281/labs |

| Name                                           | Last modified                  | Size Description             |        |           |

| Parent Directory                               | Y                              | -                            |        |           |

| Instructions/                                  | 21-Aug-2020 15:21              | -                            |        |           |

| Lab_01/                                        | 21-Aug-2020 15:22              | ] -                          |        |           |

| Lab_02/                                        | 18-Aug-2020 16:48              | -                            |        |           |

| Lab_03/                                        | 18-Aug-2020 16:51              | -                            |        |           |

| Lab_04/                                        | 18-Aug-2020 16:53              | -                            |        |           |

| Lab_05/                                        | 18-Aug-2020 16:56              | -                            |        |           |

| <u>Lab_06/</u>                                 | 18-Aug-2020 16:58              | -                            |        |           |

| <u>Lab_07/</u>                                 | 18-Aug-2020 16:59              | -                            |        |           |

| <u>Lab_08/</u>                                 | 18-Aug-2020 17:02              | -                            |        |           |

| <u>Lab_09/</u>                                 | 18-Aug-2020 17:05              | -                            |        |           |

| <u>Lab_10/</u>                                 | 18-Aug-2020 17:06              | -                            |        |           |

| <u>Lab_11/</u>                                 | 18-Aug-2020 17:08              | -                            |        |           |

| <u>Lab_12/</u>                                 | 18-Aug-2020 17:20              | -                            |        |           |

| Mini_Project/                                  | 18-Aug-2020 17:10              | -                            |        |           |

O

150% ••• 🔝

#### Index of /~alexs/classes/2020\_Fall\_281/labs/Lab\_01 Name Last modified Size Description Parent Directory CPRE281 LAB01(Answer Sheet).docx 18-Aug-2020 16:48 26K ? CPRE281 LAB01.docx 18-Aug-2020 16:40 28K F CPRE281 LAB01.pdf 18-Aug-2020 16:40 121K Lab 1 CPR E 281 .zip 19-May-2020 08:41 5.9M ModelSIM\_Guide.pdf 20-Aug-2020 11:30 1.5M

Apache/2.2.15 (Red Hat) Server at www.ece.iastate.edu Port 80

| E                            | E 281 LA<br>cal and comp<br>ngineering<br>state univers | UTER                    | Lab 1 An    | swer Sheet   |                  |

|------------------------------|---------------------------------------------------------|-------------------------|-------------|--------------|------------------|

| Name and Date:               | Student ID:                                             | L                       |             | Lab Section: |                  |

| PRELAB:                      |                                                         | able below for a        | n AND gate: | 7            |                  |

| A                            | в                                                       | C                       | and Bate.   | Т            | his is the prela |

| 0                            | 0                                                       |                         |             | ^            |                  |

|                              | 1                                                       |                         |             |              | for lab #1       |

| 1                            | 0                                                       |                         |             |              |                  |

| 1                            | 1                                                       |                         |             |              |                  |

|                              |                                                         | ble for <i>lab1step</i> | 1:          |              |                  |

| LAB:<br>2.0 Fill in t        | the Truth Tal                                           |                         |             |              |                  |

|                              | the Truth Tal<br>B                                      | c                       |             |              |                  |

| 2.0 Fill in t<br>A<br>0      | <b>B</b><br>0                                           | c                       |             |              |                  |

| 2.0 Fill in t<br>A<br>0      | <b>B</b><br>0                                           | c                       |             |              |                  |

| 2.0 Fill in t<br>A<br>0<br>0 | B<br>0<br>1<br>0                                        | c                       |             |              |                  |

Logic Expression: \_\_\_\_\_

Cpr E 281 LAB1 ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY

#### Lab 1 Answer Sheet

#### 4.0 Fill in the Truth Table for lab1step2:

| w | x | Y | z |

|---|---|---|---|

| 0 | 0 | 0 |   |

| 0 | 0 | 1 |   |

| 0 | 1 | 0 |   |

| 0 | 1 | 1 |   |

| 1 | 0 | 0 |   |

| 1 | 0 | 1 |   |

| 1 | 1 | 0 |   |

| 1 | 1 | 1 |   |

Logic Expression:

#### 4.0 Fill in the Truth Table for lab1step3:

| А | В | с | F |

|---|---|---|---|

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

Logic Expression: \_\_\_\_\_

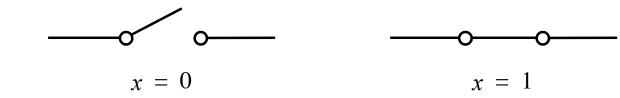

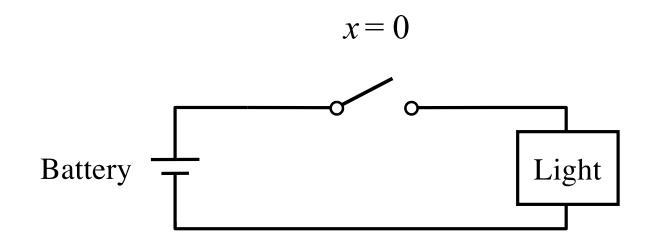

## **A Binary Switch**

(a) Two states of a switch

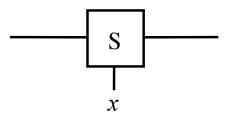

(b) Symbol for a switch

[Figure 2.1 from the textbook]

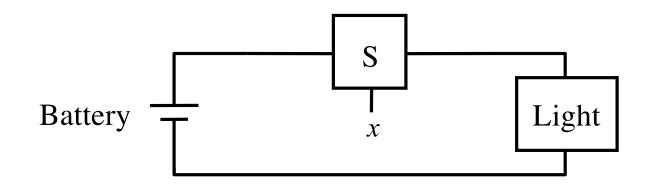

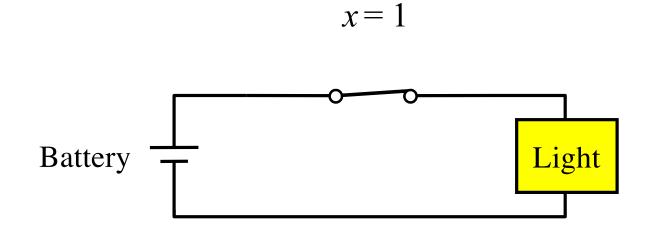

(a) Simple connection to a battery

[Figure 2.2a from the textbook]

(b) Using a ground connection as the return path

[Figure 2.2b from the textbook]

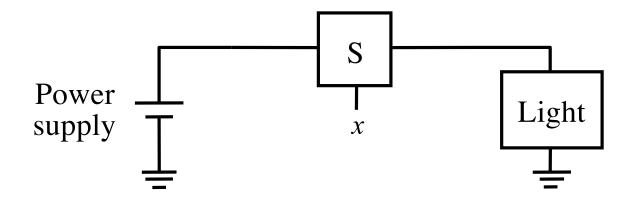

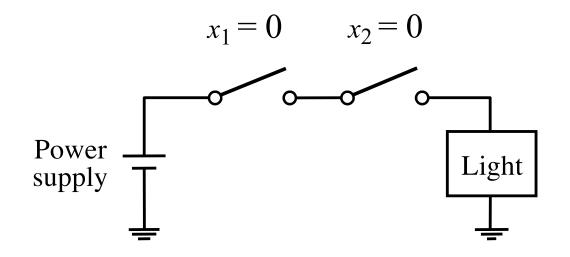

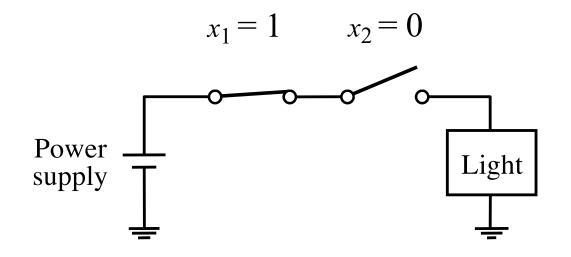

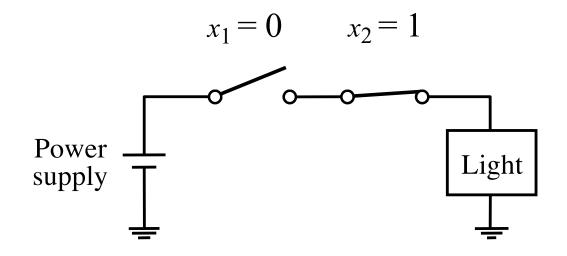

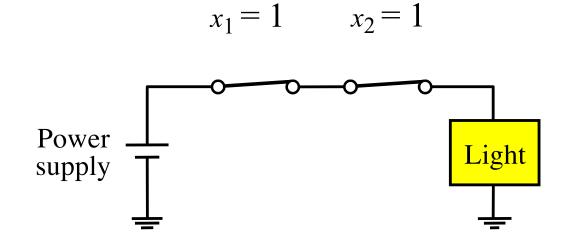

[Figure 2.3a from the textbook]

[Figure 2.3b from the textbook]

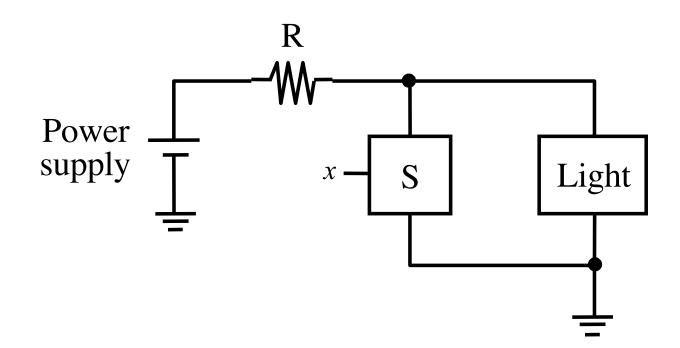

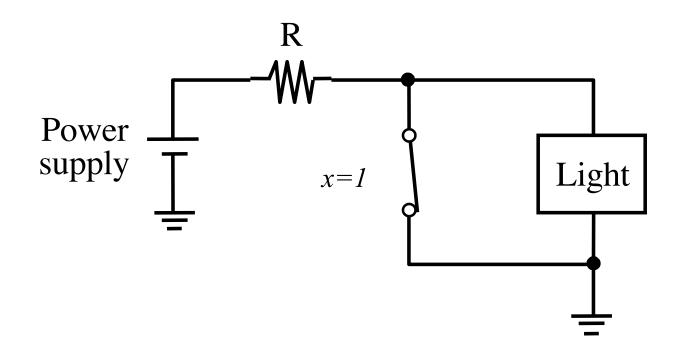

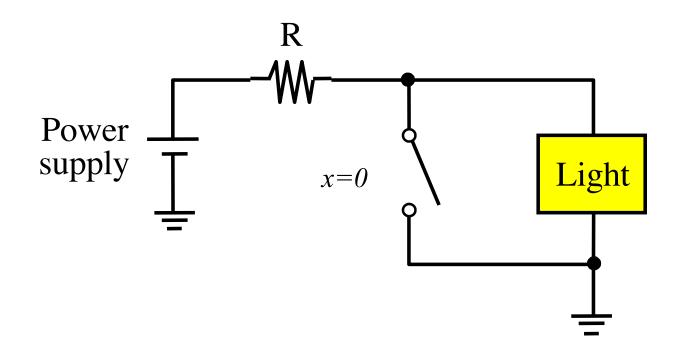

# **An Inverting Circuit**

[ Figure 2.5 from the textbook ]

## **An Inverting Circuit**

## **An Inverting Circuit**

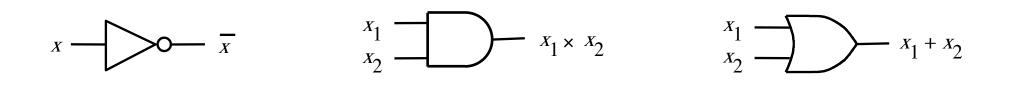

## **The Three Basic Logic Gates**

NOT gate

AND gate

OR gate

[Figure 2.8 from the textbook]

### **Truth Table for NOT**

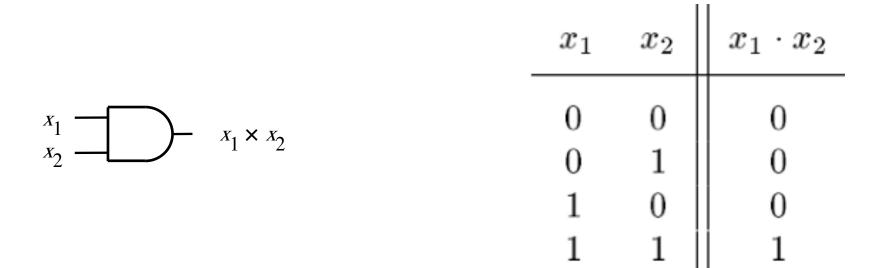

### **Truth Table for AND**

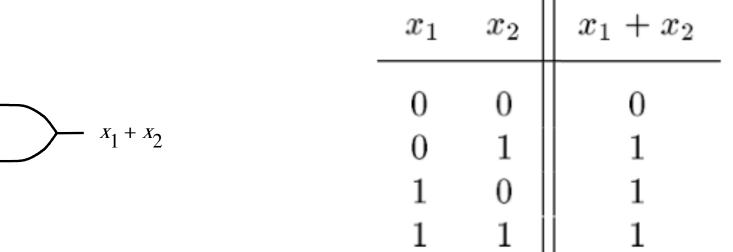

### **Truth Table for OR**

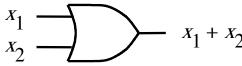

# Truth Tables for AND and OR

| $x_1$ | $x_2$ | $x_1  x_2$ | $x_1 + x_2$ |

|-------|-------|------------|-------------|

| 0     | 0     | 0          | 0           |

| 0     | 1     | 0          | 1           |

| 1     | 0     | 0          | 1           |

| 1     | 1     | 1          | 1           |

AND OR

[ Figure 2.6b from the textbook ]

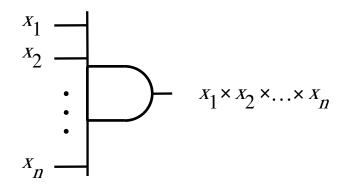

#### Logic Gates with n Inputs

AND gate

OR gate

## Truth Table for 3-input AND and OR

| $x_1$ | $x_2$ | $x_3$ | $x_1$ $x_2$ $x_3$ | $x_1 + x_2 + x_3$ |

|-------|-------|-------|-------------------|-------------------|

| 0     | 0     | 0     | 0                 | 0                 |

| 0     | 0     | 1     | 0                 | 1                 |

| 0     | 1     | 0     | 0                 | 1                 |

| 0     | 1     | 1     | 0                 | 1                 |

| 1     | 0     | 0     | 0                 | 1                 |

| 1     | 0     | 1     | 0                 | 1                 |

| 1     | 1     | 0     | 0                 | 1                 |

| 1     | 1     | 1     | 1                 | 1                 |

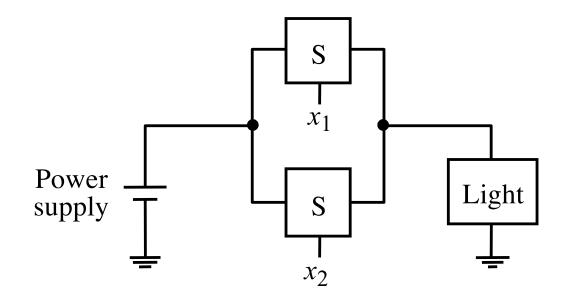

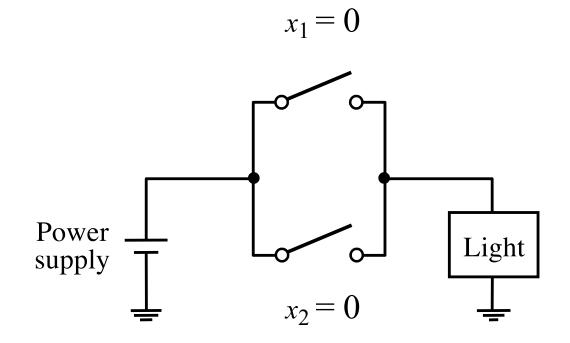

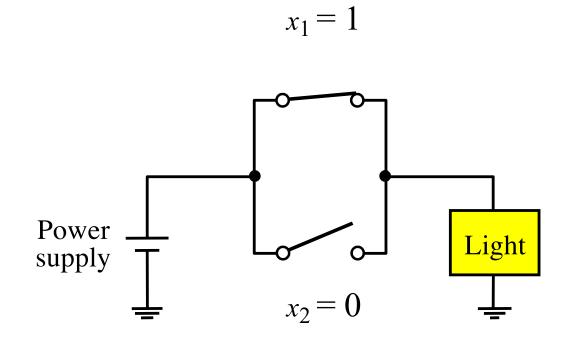

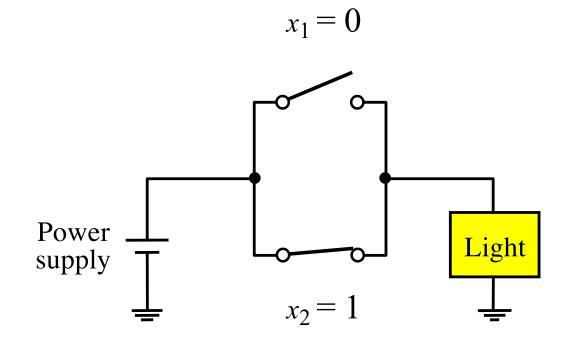

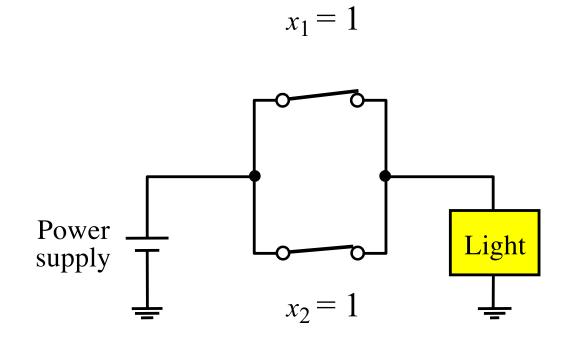

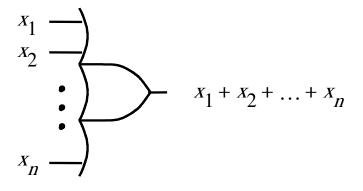

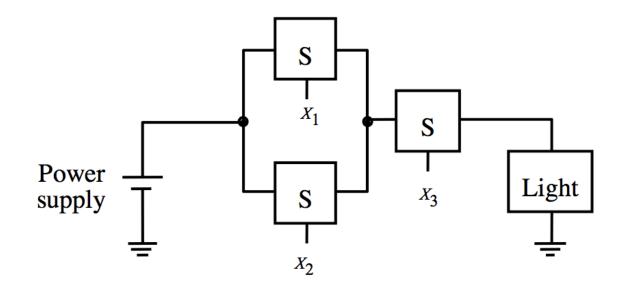

# A series-parallel connection of the switches

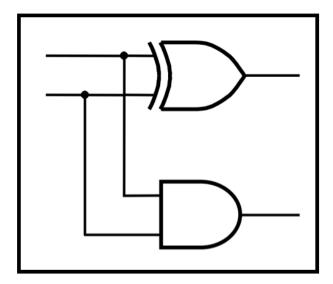

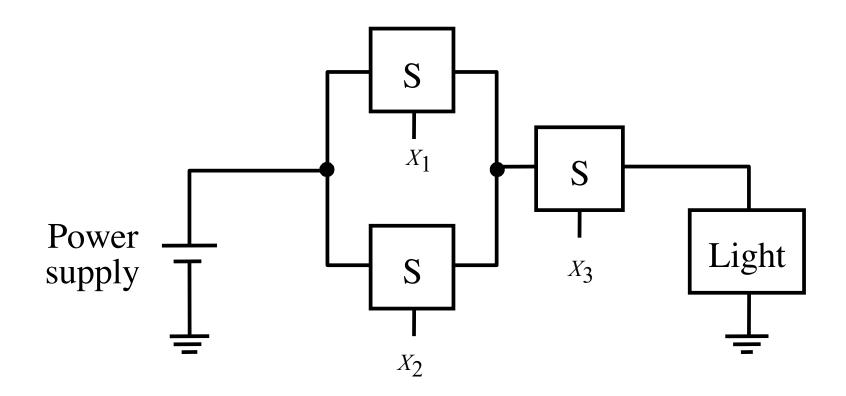

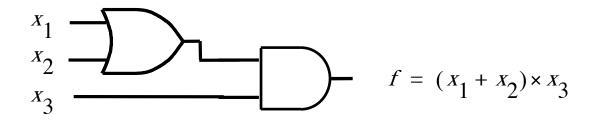

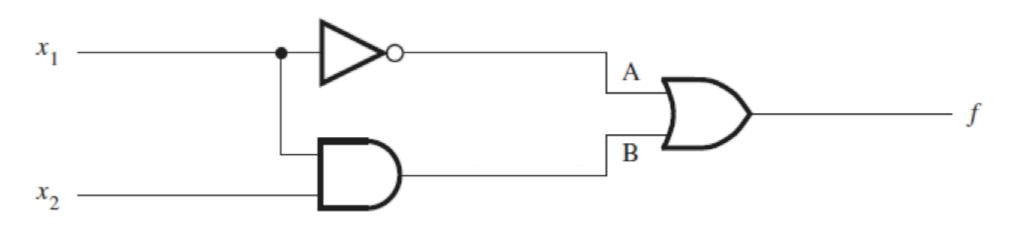

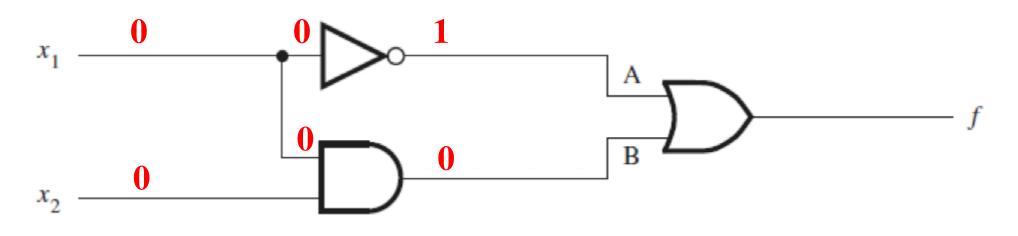

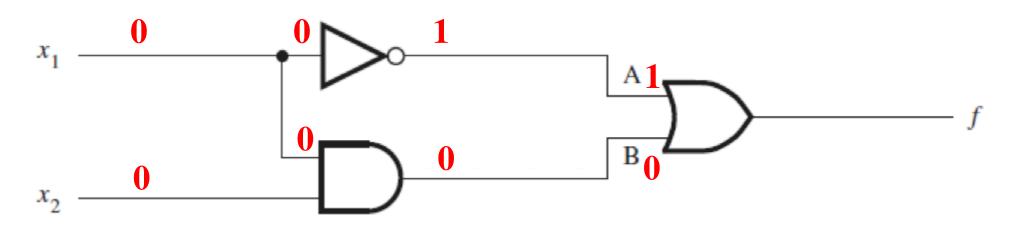

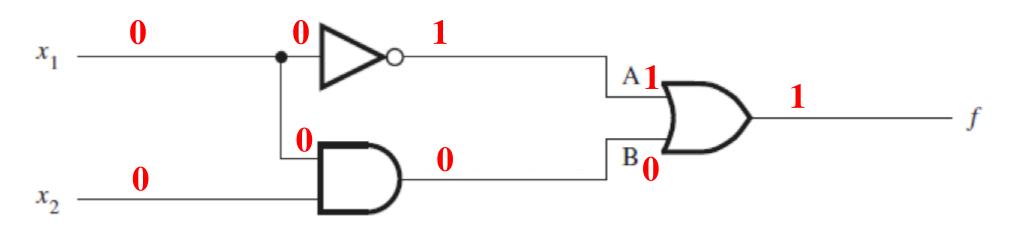

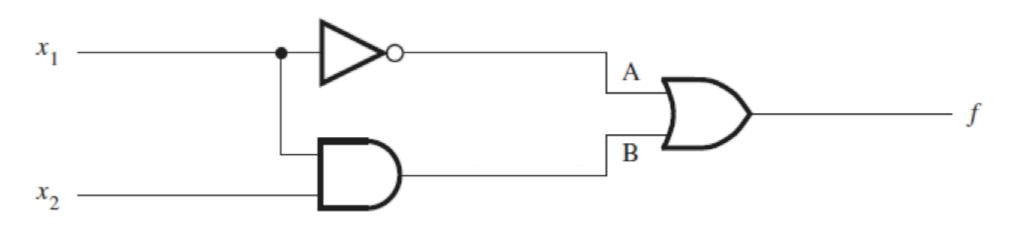

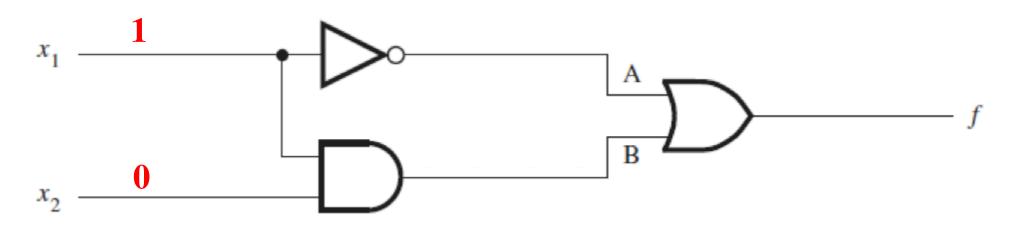

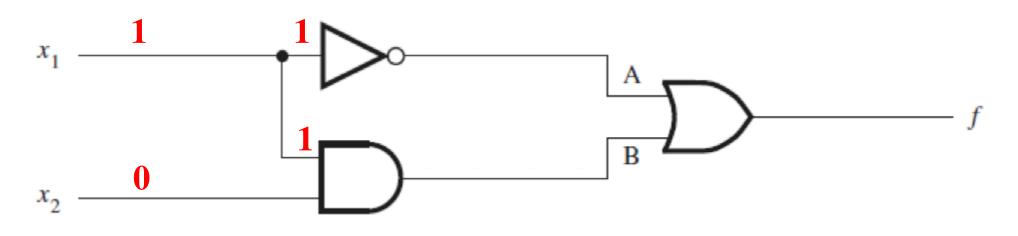

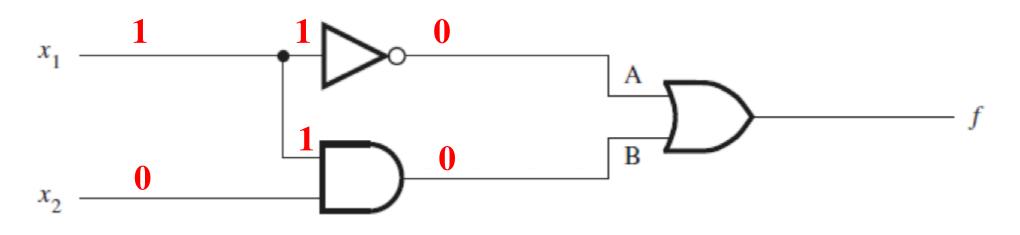

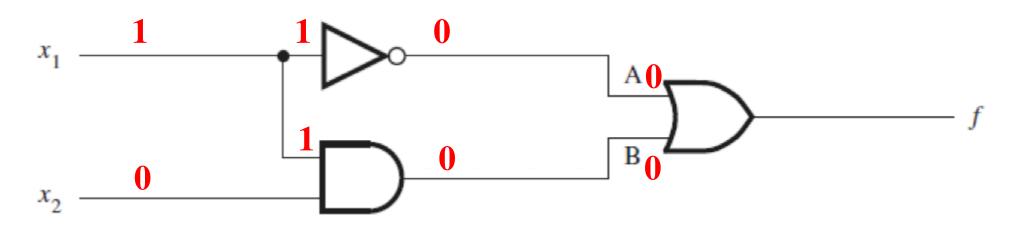

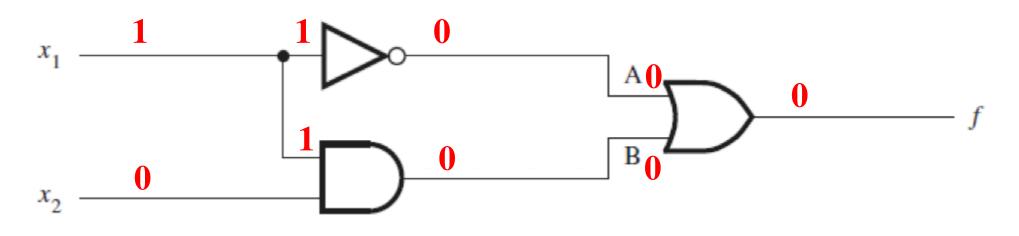

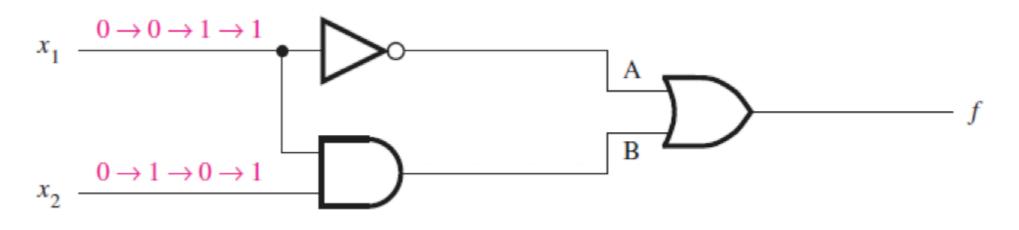

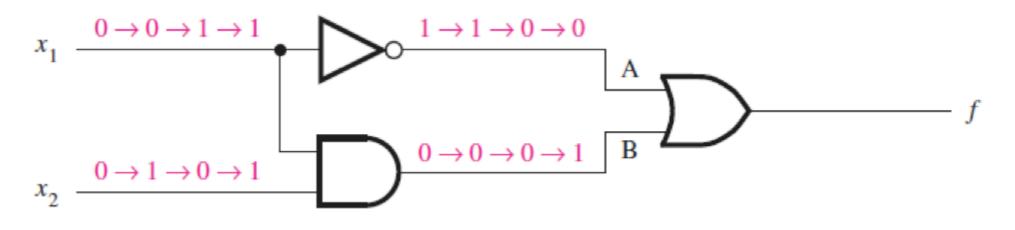

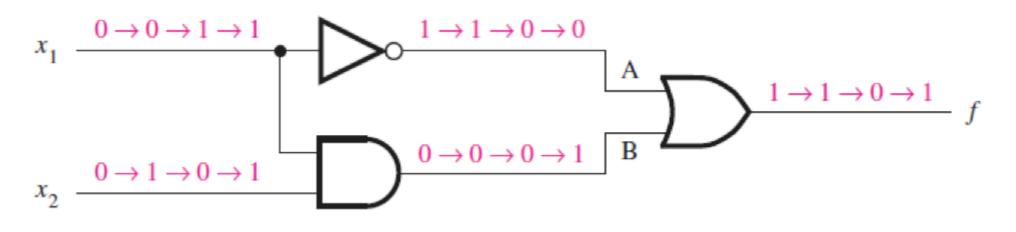

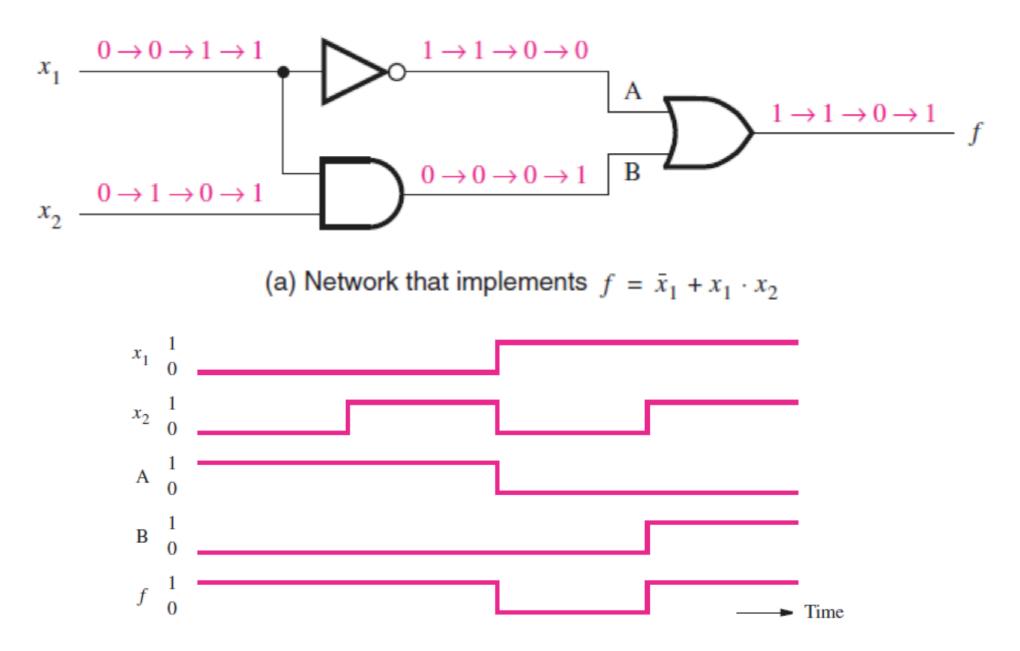

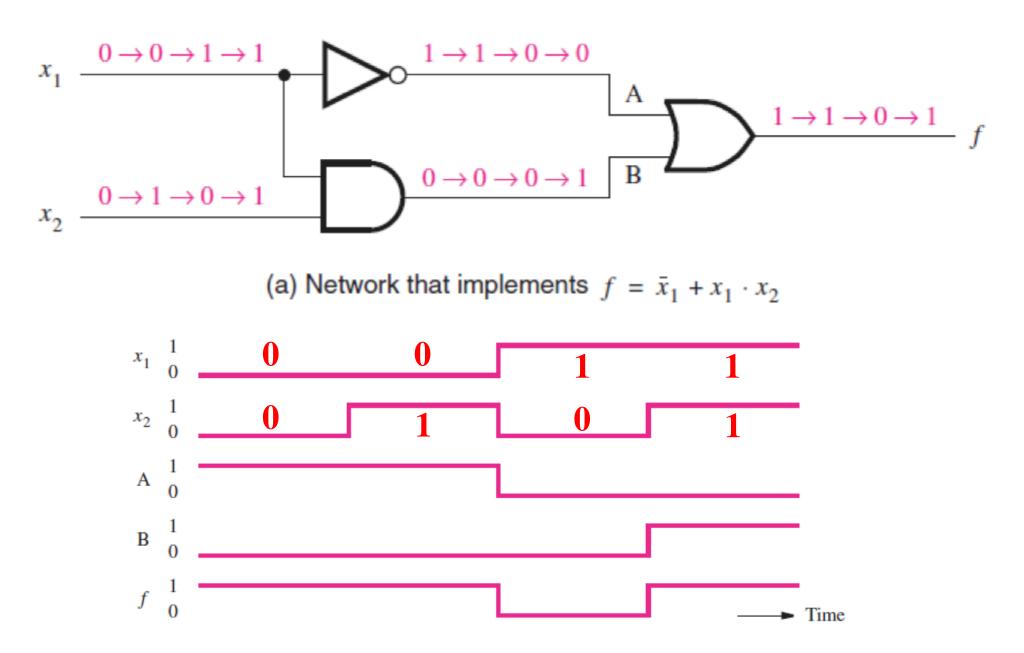

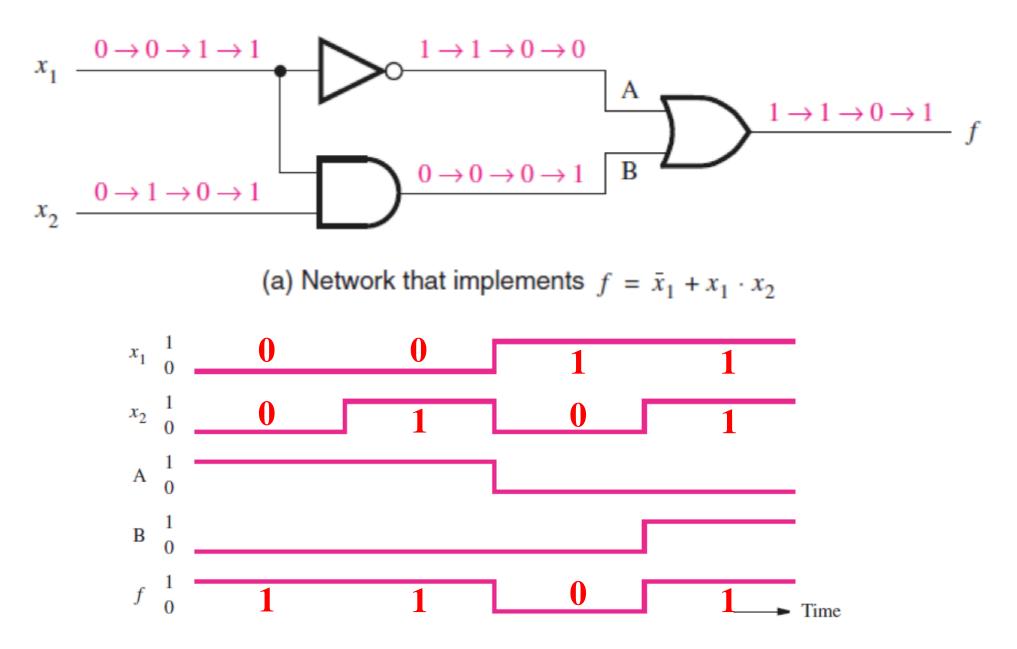

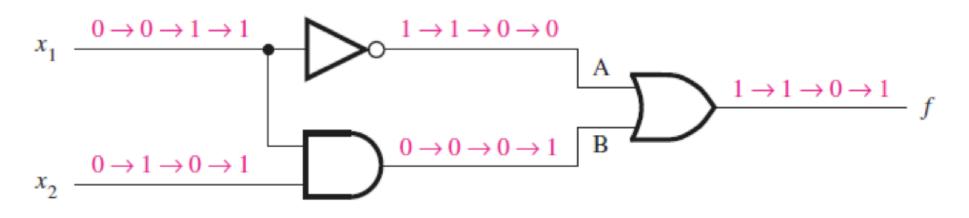

# Example of a Logic Circuit Implemented with Logic Gates

# Example of a Logic Circuit Implemented with Logic Gates

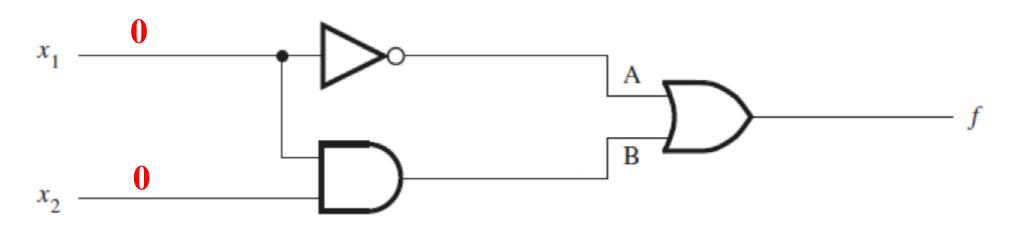

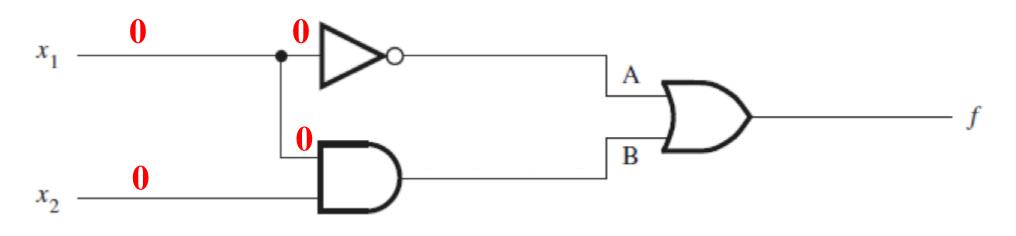

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

<sup>[</sup>Figure 2.10 from the textbook]

<sup>[</sup>Figure 2.10 from the textbook]

<sup>[</sup>Figure 2.10 from the textbook]

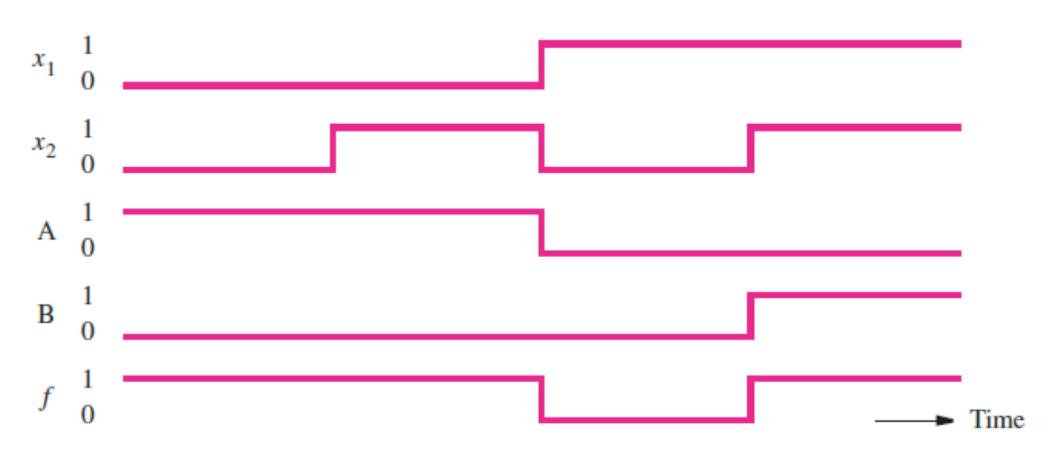

# **Timing Diagram**

## **Truth Table for this Logic Circuit**

| $x_1$ | <i>x</i> <sub>2</sub> | $f(x_1,x_2)$ | Α | В |

|-------|-----------------------|--------------|---|---|

| 0     | 0                     | 1            | 1 | 0 |

| 0     | 1                     | 1            | 1 | 0 |

| 1     | 0                     | 0            | 0 | 0 |

| 1     | 1                     | 1            | 0 | 1 |

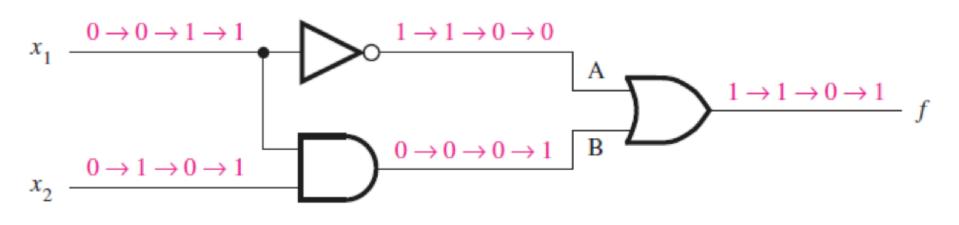

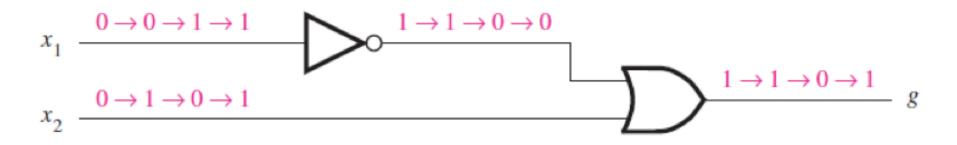

# **Functionally Equivalent Circuits**

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

# **Functionally Equivalent Circuits**

(a) Network that implements  $f = \bar{x}_1 + x_1 \cdot x_2$

(d) Network that implements  $g = \bar{x}_1 + x_2$

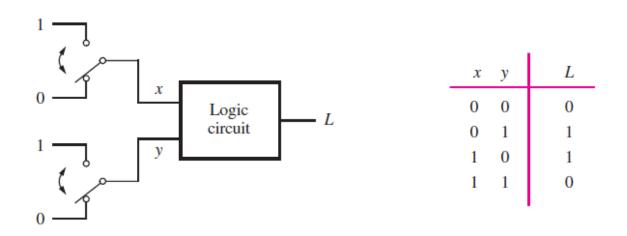

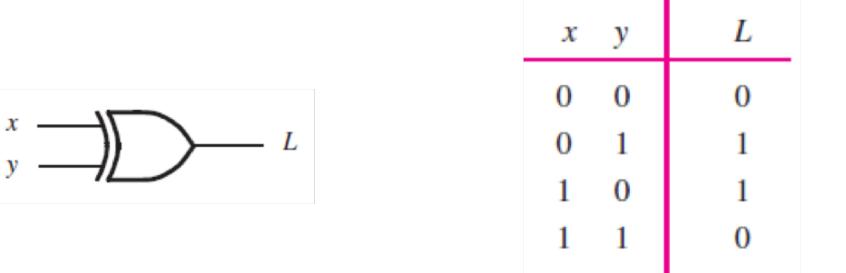

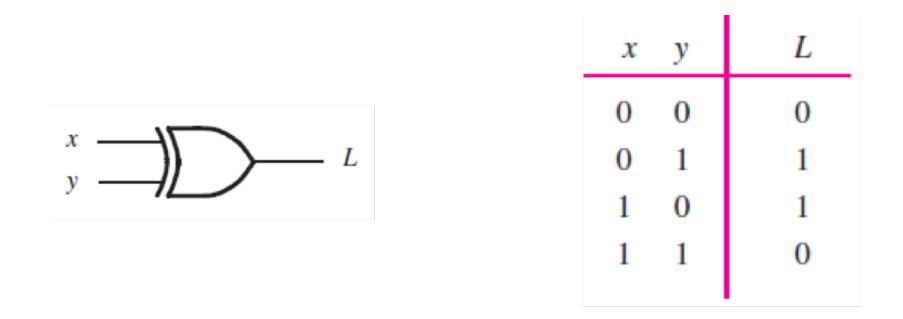

#### The XOR Logic Gate

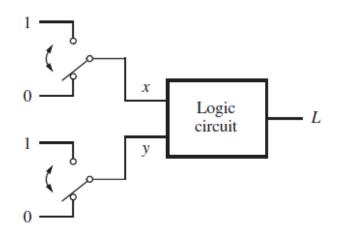

(a) Two switches that control a light

(b) Truth table

#### The XOR Logic Gate

| x | у | L |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

|   |   |   |

(a) Two switches that control a light

(b) Truth table

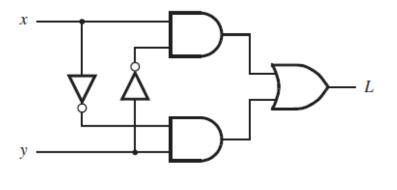

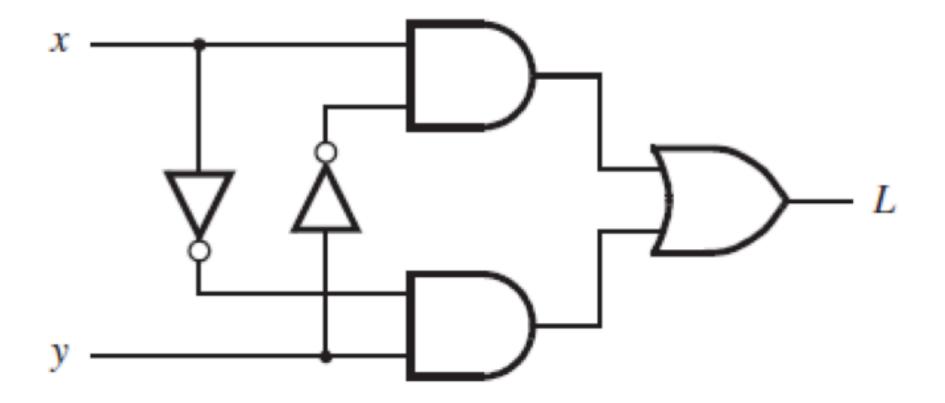

(c) Logic network

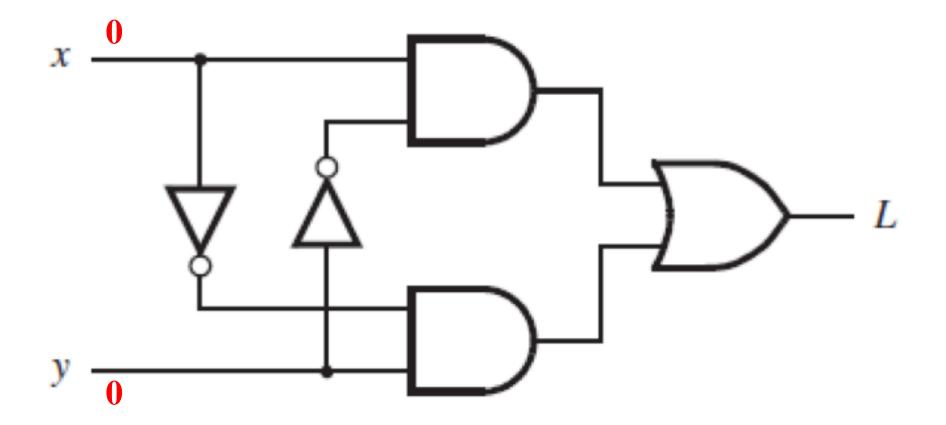

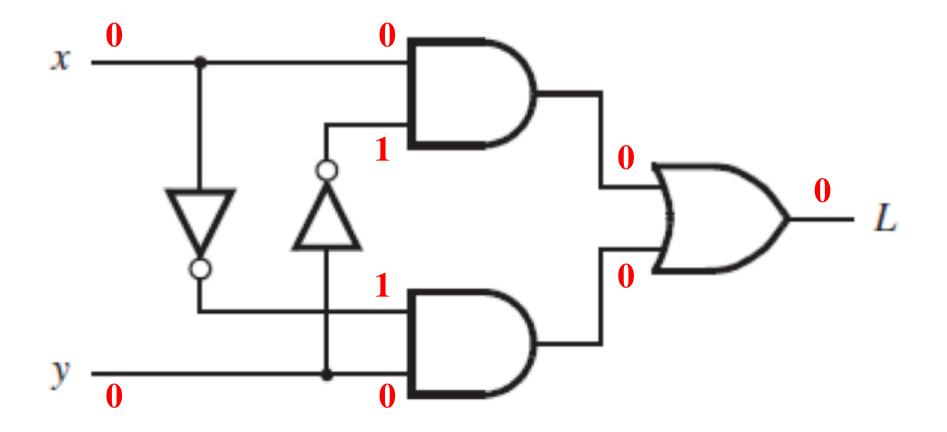

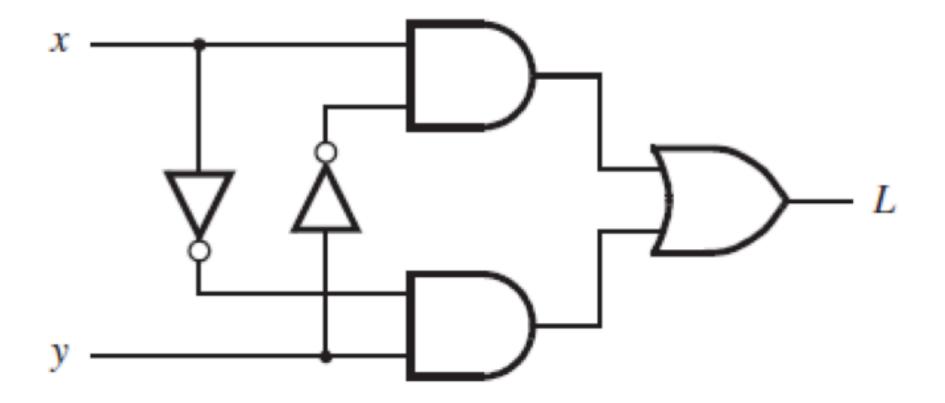

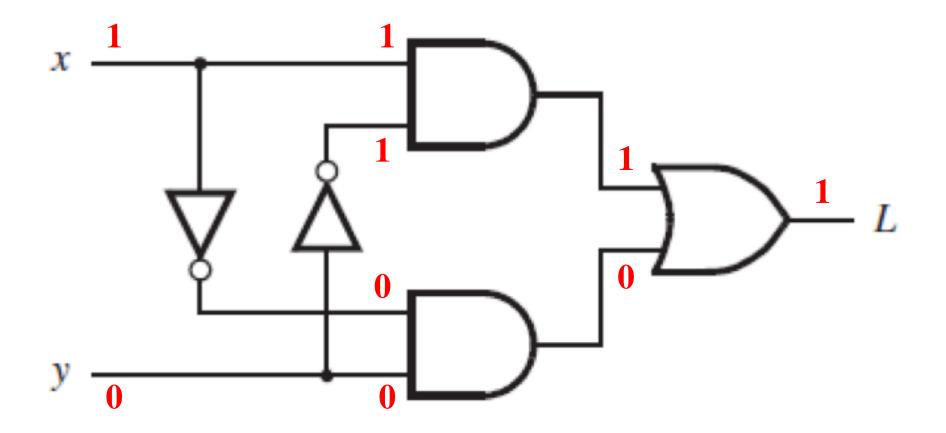

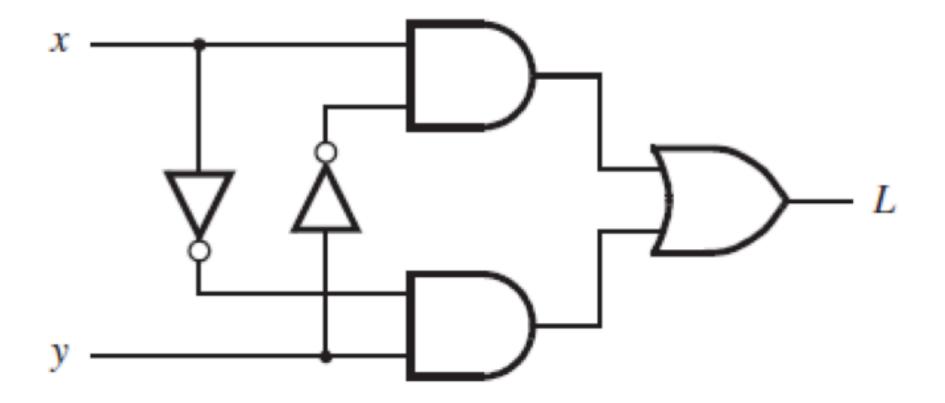

### **XOR Analysis**

# **XOR Analysis**

[ Figure 2.11c from the textbook ]

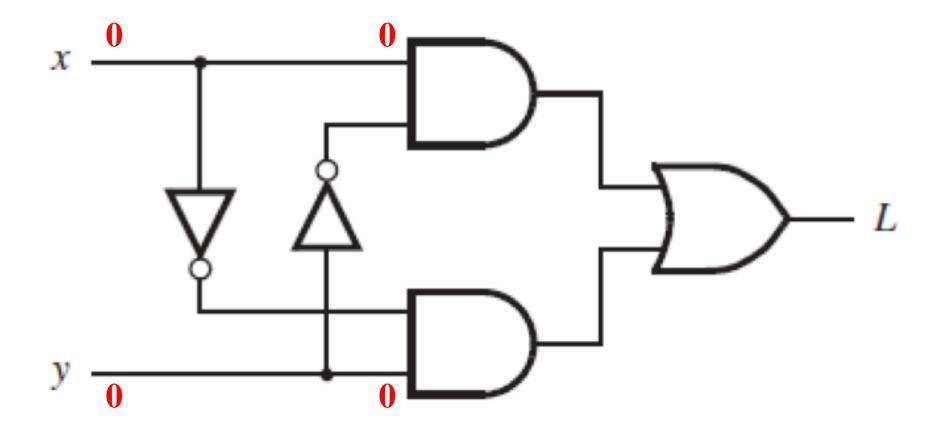

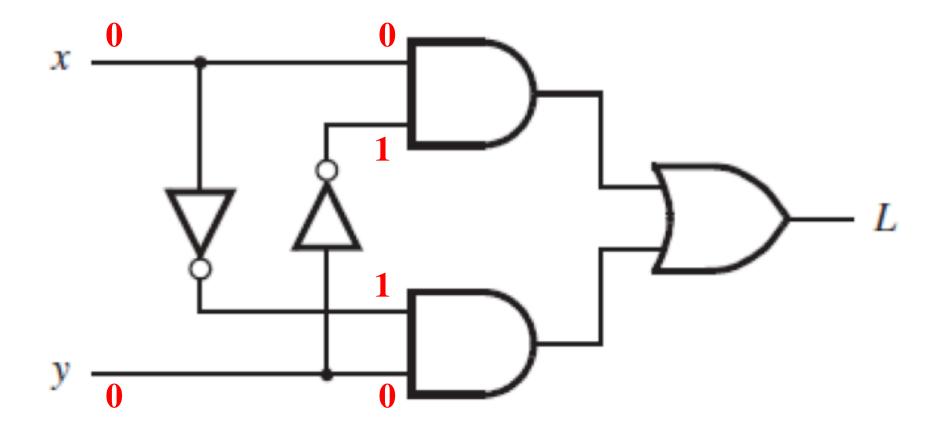

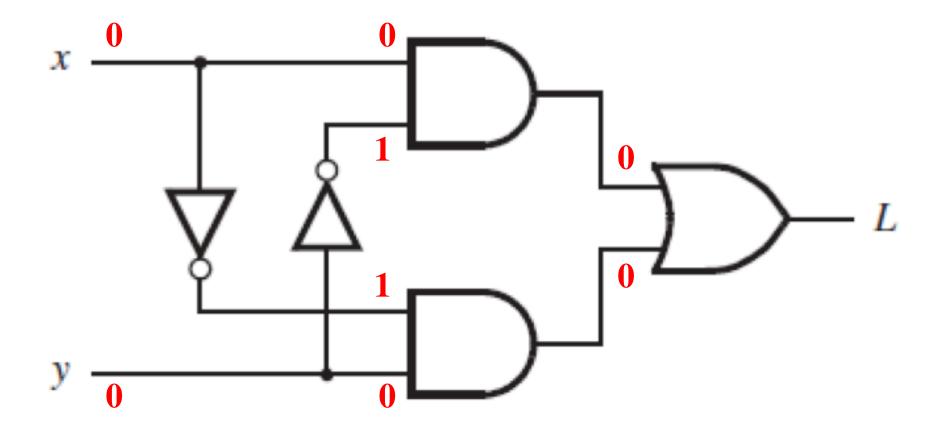

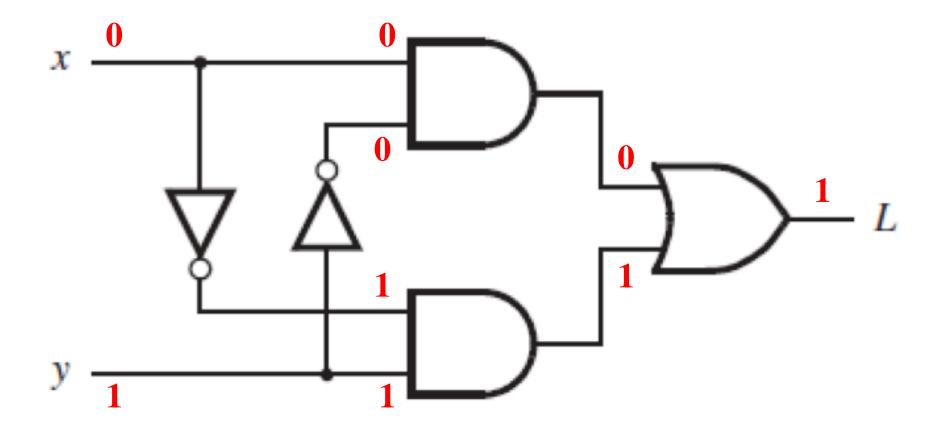

# XOR Analysis (x=0, y=1)

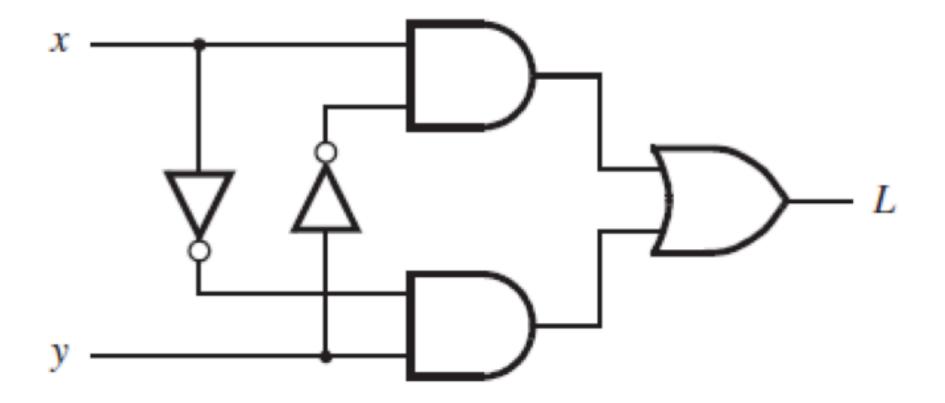

# **XOR Analysis**

[ Figure 2.11c from the textbook ]

# XOR Analysis (x=1, y=0)

# **XOR Analysis**

[ Figure 2.11c from the textbook ]

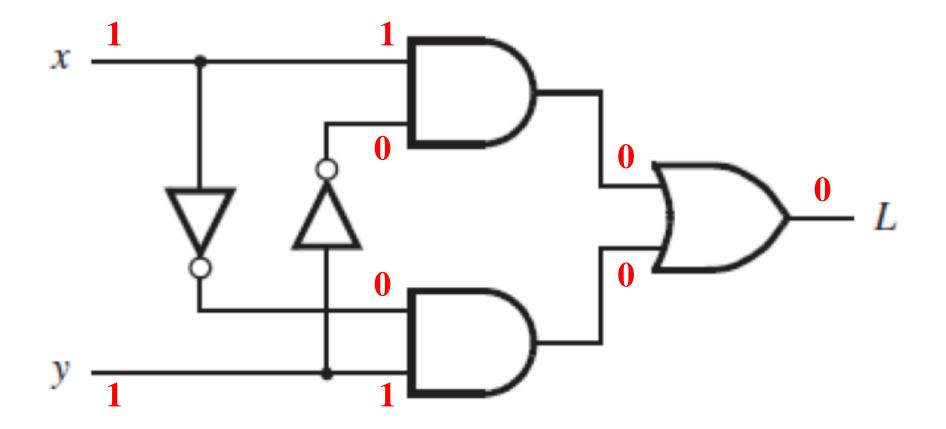

XOR Analysis (x=1, y=1)

# **Truth Table for XOR**

# **Truth Table for XOR**

#### The output is 1 only if both inputs are different.

[Figure 2.12 from the textbook]

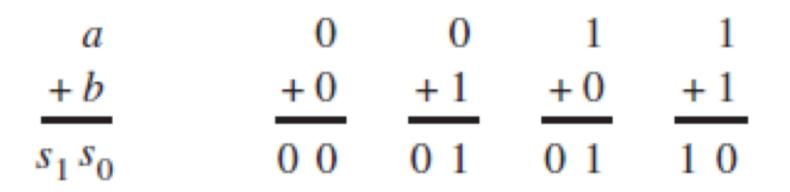

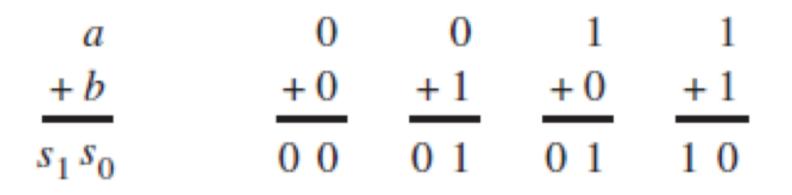

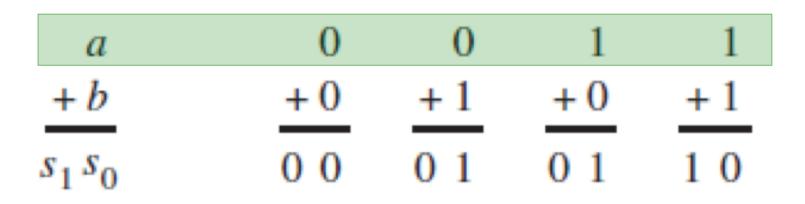

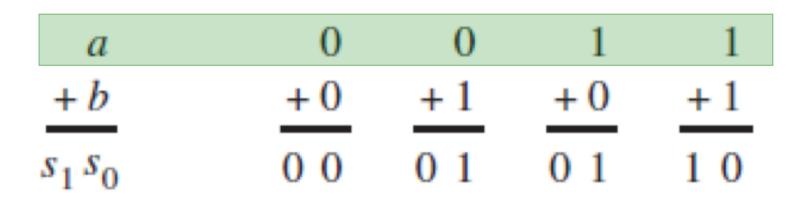

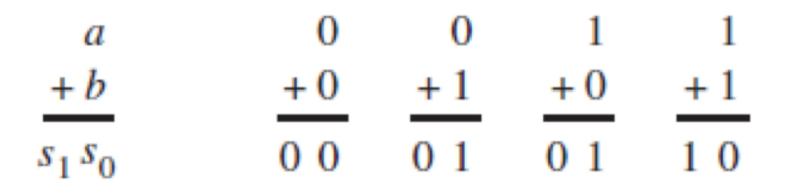

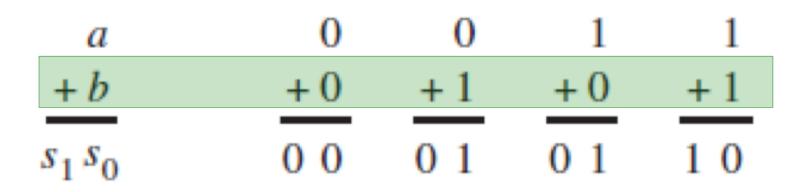

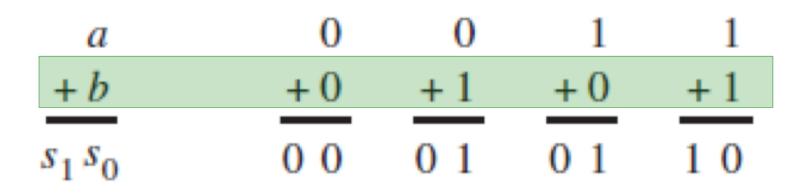

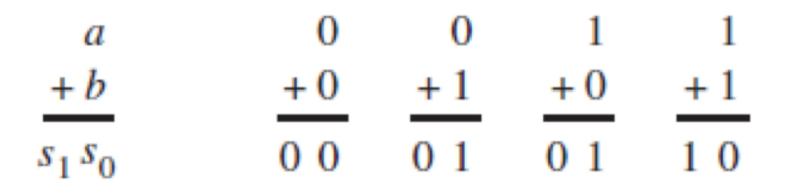

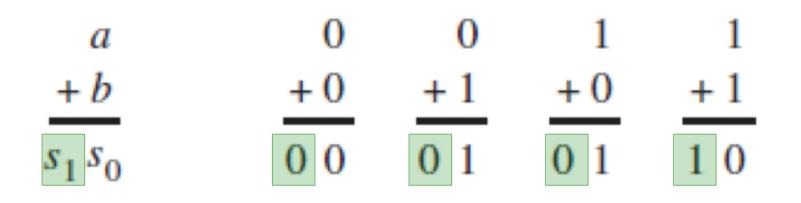

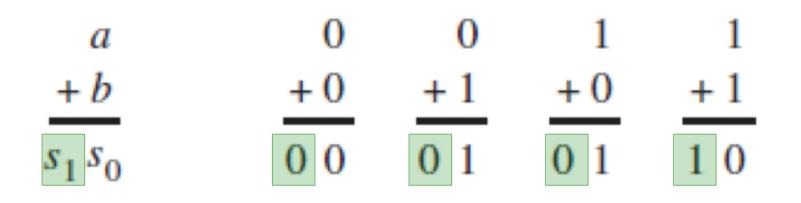

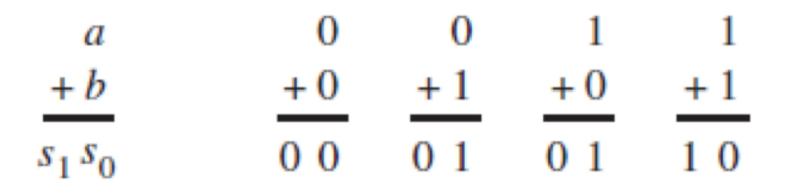

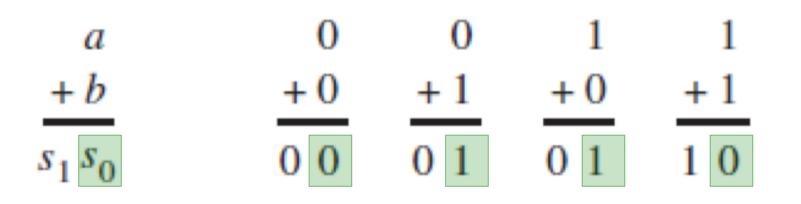

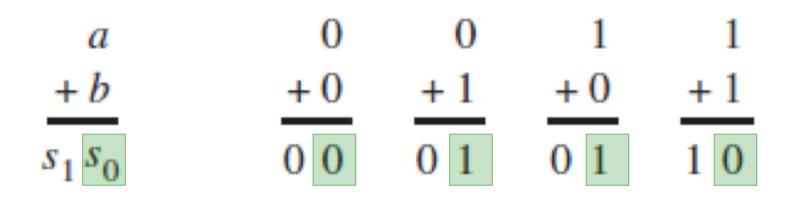

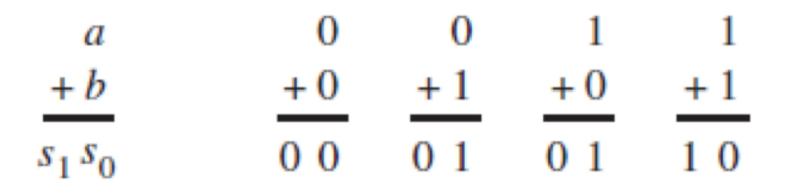

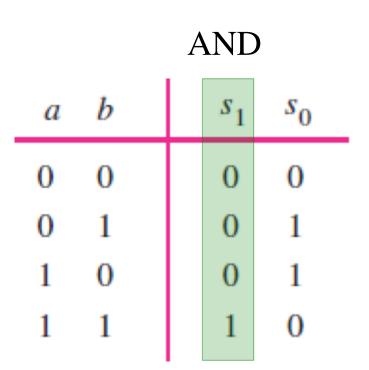

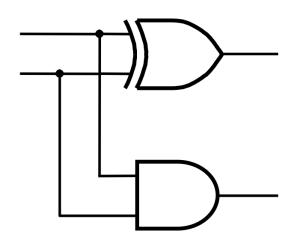

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

[Figure 2.12 from the textbook]

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> <i>s</i> <sub>0</sub> |

|---|---|---------------------------------------------|

| 0 | 0 | 0 0                                         |

| 0 | 1 | 0 1                                         |

| 1 | 0 | 0 1                                         |

| 1 | 1 | 1 0                                         |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b |  | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|--|-----------------------|-----------------------|

| 0 | 0 |  | 0                     | 0                     |

| 0 | 1 |  | 0                     | 1                     |

| 1 | 0 |  | 0                     | 1                     |

| 1 | 1 |  | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |  |

|---|---|-----------------------|-----------------------|--|

| 0 | 0 | 0                     | 0                     |  |

| 0 | 1 | 0                     | 1                     |  |

| 1 | 0 | 0                     | 1                     |  |

| 1 | 1 | 1                     | 0                     |  |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

|   | ? |  |                       |                       |

|---|---|--|-----------------------|-----------------------|

| а | b |  | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

| 0 | 0 |  | 0                     | 0                     |

| 0 | 1 |  | 0                     | 1                     |

| 1 | 0 |  | 0                     | 1                     |

| 1 | 1 |  | 1                     | 0                     |

.

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| ? |  |

|---|--|

|   |  |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |  |

|---|---|-----------------------|-----------------------|--|

| 0 | 0 | 0                     | 0                     |  |

| 0 | 1 | 0                     | 1                     |  |

| 1 | 0 | 0                     | 1                     |  |

| 1 | 1 | 1                     | 0                     |  |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |  |

|---|---|-----------------------|-----------------------|--|

| 0 | 0 | 0                     | 0                     |  |

| 0 | 1 | 0                     | 1                     |  |

| 1 | 0 | 0                     | 1                     |  |

| 1 | 1 | 1                     | 0                     |  |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

| а | b | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> |

|---|---|-----------------------|-----------------------|

| 0 | 0 | 0                     | 0                     |

| 0 | 1 | 0                     | 1                     |

| 1 | 0 | 0                     | 1                     |

| 1 | 1 | 1                     | 0                     |

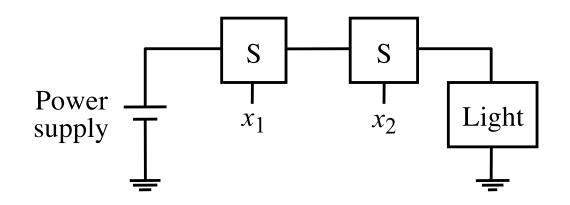

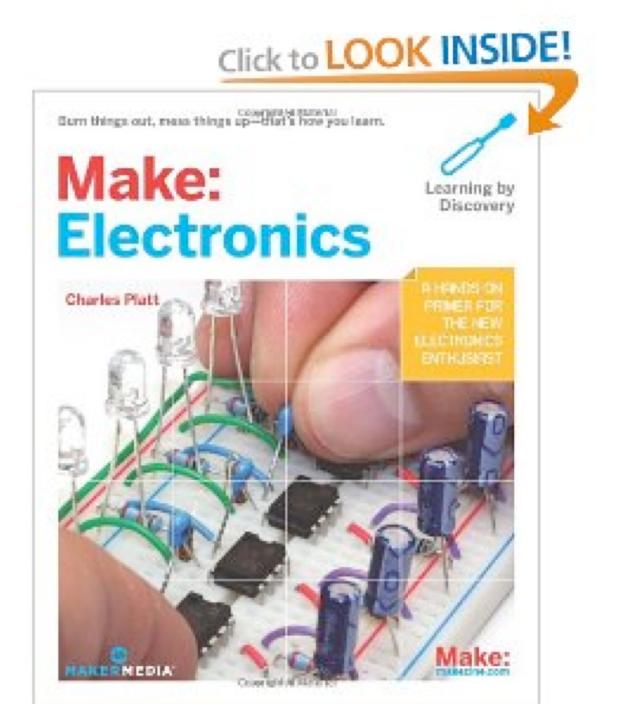

#### The following examples came from this book

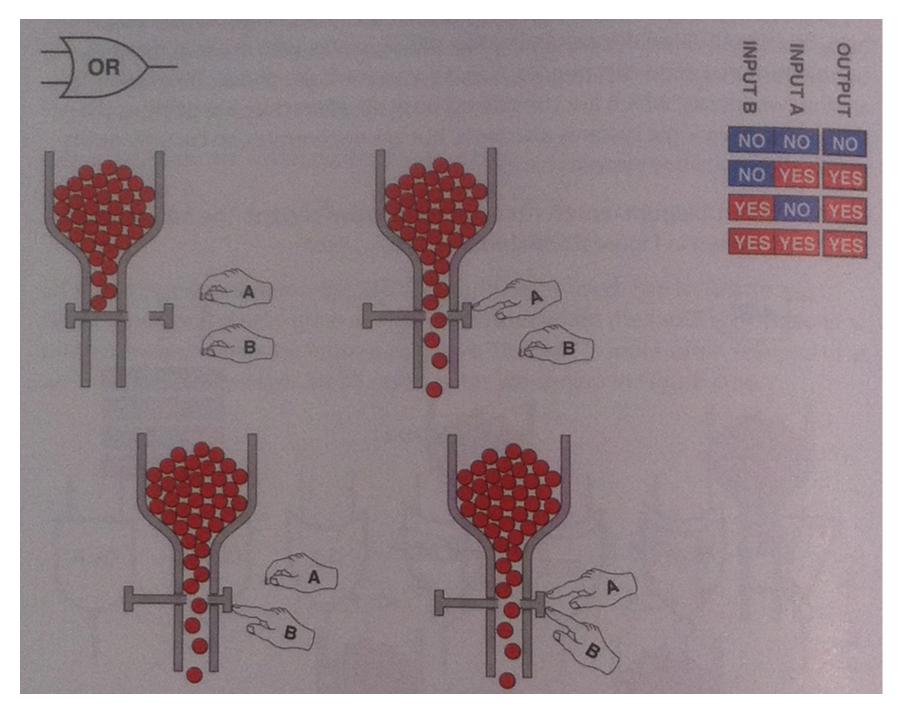

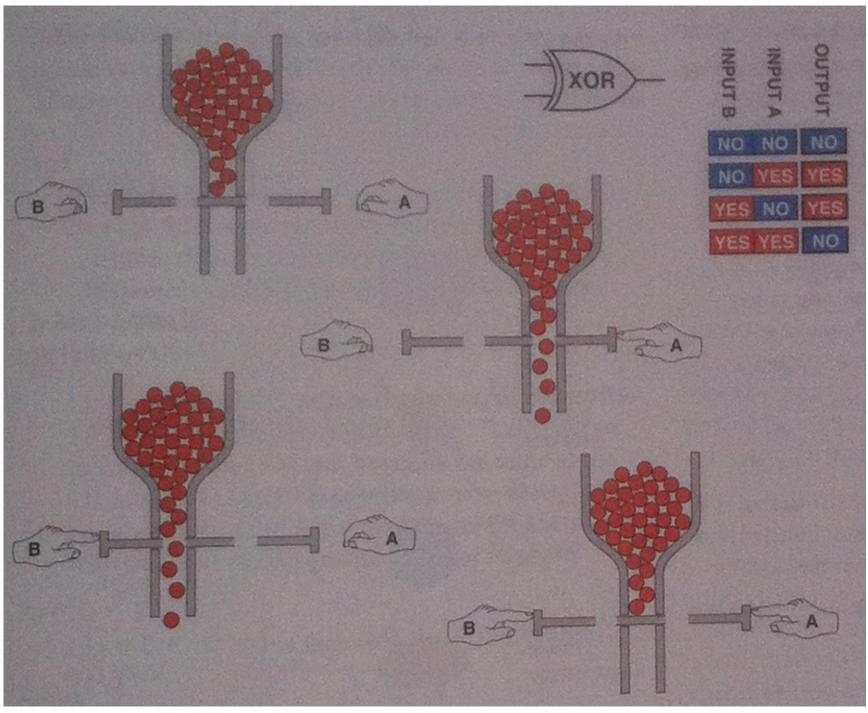

[ Platt 2009 ]

[ Platt 2009 ]

[ Platt 2009 ]

#### **Questions?**

# THE END