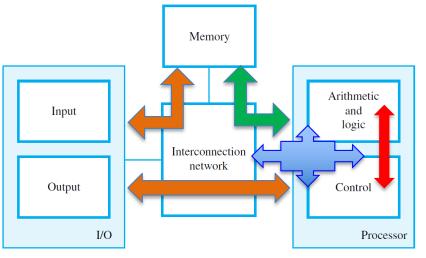

- Instructions categories:

- Data transfer: memory to/from processor

- Input/output transfer: I/O to/from processor/memory

- Arithmetic and logic operations

- Program sequencing and control

- ARM: 57 instructions (PM31-34)

- Thumb: 36 instructions (TI5-2/3)

# **ARM Thumb Instructions (TH3-4)**

| ADC | Add with Carry         | LDMIA | Load multiple                  | NEG   | Negate              |

|-----|------------------------|-------|--------------------------------|-------|---------------------|

| ADD | Add                    | LDR   | Load word                      | ORR   | OR                  |

| AND | AND                    | LDRB  | Load byte                      | POP   | Pop registers       |

| ASR | Arithmetic Shift Right | LDRH  | Load halfword                  | PUSH  | Push registers      |

| В   | Unconditional branch   | LSL   | Logical Shift Left             | ROR   | Rotate Right        |

| Bxx | Conditional branch     | LDSB  | Load sign-extended             | SBC   | Subtract with Carry |

| BIC | Bit Clear              |       | byte                           | STMIA | Store Multiple      |

| BL  | Branch and Link        | LDSH  | Load sign-extended<br>halfword | STR   | Store word          |

| BX  | Branch and Exchange    | LSR   | Logical Shift Right            | STRB  | Store byte          |

| CMN | Compare Negative       | MOV   | Move register                  | STRH  | Store halfword      |

| CMP | Compare                | MUL   | Multiply                       | SWI   | Software Interrupt  |

| EOR | EOR                    | MVN   | Move Negative register         | SUB   | Subtract            |

|     |                        |       |                                | TST   | Test bits           |

Kin Fun Ll, University of Victoria

ECE 255 Introduction to Computer Architecture

Instruction Set Architecture 34

- Two operations to access (read or write) memory

- Load : register ← memory

- − <u>Store</u>: memory ← register

- Source: no change

- Destination: overwritten

- ALU ← operands (<u>only from registers; register size</u>?)

- A characteristic of the Reduced Instruction Set Computer (RISC)

- Storing data operand in registers: advantages ?

# **Thumb Memory Access Instructions**

| multiple registers 🗲 multiple data |                         |       |                               |        |                    |                                               |

|------------------------------------|-------------------------|-------|-------------------------------|--------|--------------------|-----------------------------------------------|

| ADC                                | Add with Carry          | LDMIA | Load multiple                 | Cor    | cept: Stack        | Implementation:<br>Negate<br>Memory           |

| ADD                                | Add 4 bytes             | LDR   | Load word                     |        | ORR                | OR                                            |

| AND                                | AND 2 bytes             | LDRB  | Load byte                     |        | POP                | Pop registers                                 |

| ASR                                | Arithmetic Shift Right  | LDRH  | Load halfword                 |        | PUSH               | Push registers                                |

| В                                  | Unconditional branch    | LSL   | Logical Shift Left            |        | ROR                | Rotate Right                                  |

| Bxx                                | Conditional branch      | LDSB  | Load sign-extende             | ed     | SBC                | Subtract with Carry                           |

| BIC                                | Bit Clear               |       | byte                          |        | STMIA              | Store Multiple                                |

| BL                                 | Branch and Link         | LDSH  | Load sign-extende<br>halfword | ed     | STR                | Store word                                    |

| BX                                 | Branch and Exchange     | LSR   | Logical Shift Righ            | t      | STRB               | Store byte                                    |

| CMN                                | Compare Negative        | MOV   | Move register                 |        | STRH               | Store halfword                                |

| CMP                                | Compare                 | MUL   | Multiply                      |        | SWI                | Software Interrupt                            |

| EOR                                | EOR                     | MVN   | Move Negative re              | gister | SUB                | Subtract                                      |

|                                    | <b>metic operations</b> |       | ECE 255                       |        | TST<br>Ri ← #imm o | Test bits<br>r Ri ← Rj<br>Set Architecture 36 |

Introduction to Computer Architecture

#### **<u>Thumb</u>** Data Processing Instructions Logic in Green Arithmetic in Red **Bit Operation in Blue** ADC NEG Add with Carry Negate **LDMIA** Load multiple ORR ADD Add OR LDR Load word AND POP Pop registers AND I DBB Load byte PUSH Push registers ASR Arithmetic Shift Right I DRH Load halfword ROR Rotate Right Unconditional branch LSL В Logical Shift Left SBC Subtract with Carry Bxx Conditional branch I DSB Load sign-extended byte STMIA Store Multiple BIC Bit Clear LDSH Load sign-extended STR BL Branch and Link Store word halfword STRB Store byte BX Branch and Exchange LSR Logical Shift Right Store halfword CMN STRH Compare Negative MOV Move register SWI Software Interrupt CMP Compare MUL Multiply SUB Subtract EOR EOR MVN Move Negative register

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

Instruction Set Architecture 37

Test bits

TST

#### Thumb Branch/Control Instructions (TH3-4)

| ADC | Add with Carry         | LDMIA | Load multiple                  | NEG   | Negate              |

|-----|------------------------|-------|--------------------------------|-------|---------------------|

| ADD | Add                    | LDR   | Load word                      | ORR   | OR                  |

| AND | AND                    | LDRB  | Load byte                      | POP   | Pop registers       |

| ASR | Arithmetic Shift Right | LDRH  | Load halfword                  | PUSH  | Push registers      |

| В   | Unconditional branch   | LSL   | Logical Shift Left             | ROR   | Rotate Right        |

| Bxx | Conditional branch     | LDSB  | Load sign-extended             | SBC   | Subtract with Carry |

| BIC | Bit Clear              |       | byte                           | STMIA | Store Multiple      |

| BL  | Branch and Link        | LDSH  | Load sign-extended<br>halfword | STR   | Store word          |

| BX  | Branch and Exchange    | LSR   | Logical Shift Right            | STRB  | Store byte          |

| CMN | Compare Negative       | MOV   | Move register                  | STRH  | Store halfword      |

| CMP | Compare                | MUL   | Multiply                       | SWI   | Software Interrupt  |

| EOR | EOR                    | MVN   | Move Negative register         | SUB   | Subtract            |

|     |                        |       |                                | TST   | Test bits           |

Kin Fun LI, University of Victoria

ECE 255 Introduction to Computer Architecture

Instruction Set Architecture 38

# **2.3.5 Instruction Execution**

#### Instruction cycle:

Fetch (decode) and Execute

### Straight-line sequencing:

- Instructions executed in sequential order

- PC incremented by 2/4/8 bytes

#### or 16/32/64-bit word

# **2.3.5 Instruction Sequencing**

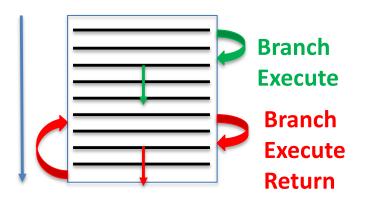

### Change of control flow:

- Change Program Counter

- Two Types:

- Branch or Interrupt

Internal and Expected

**External and Unpredictable**

#### Conditional branch:

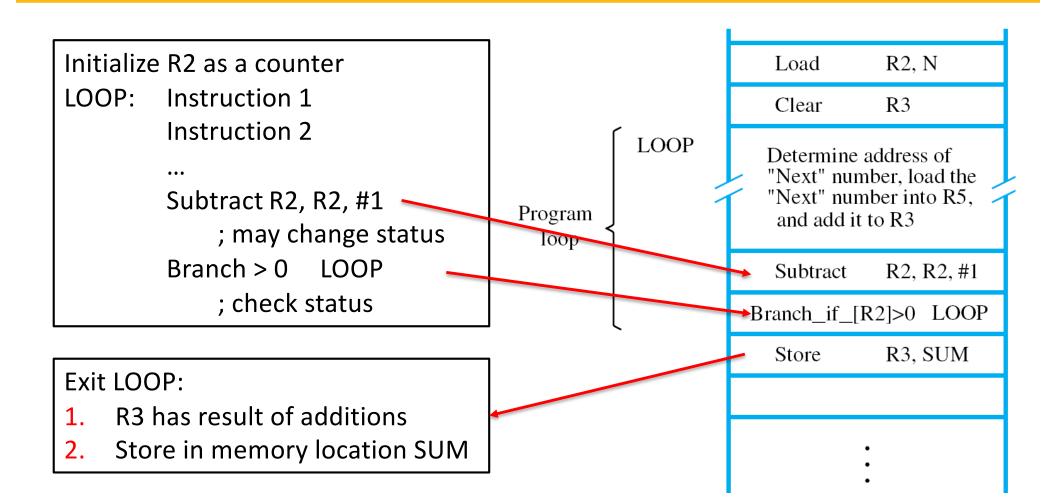

Initialize R2 as a counter; e.g., DO 50 times

- LOOP: Instruction 1 Instruction 2

- SubtractR2, R2, #1 ; change statusBranch > 0 LOOP; check status

- Branch target: LOOP if R2 > 0

. . .

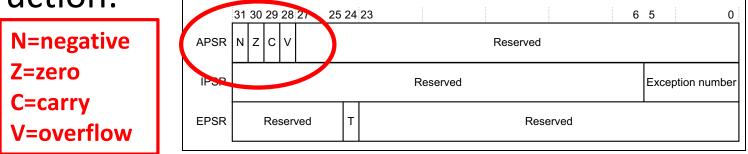

- Condition code in a status register (NZCV in APSR)

- previous operation results for subsequent conditional use

# ARM Conditional Execution (PM39)

The processor carries out the branch based on the condition code (CC) set by another

- Branch CC placement:

- Immediately after the instruction that set the condition code, OR

- After any number of in-between instructions that must not update the condition code

# **Branch Placement**

#### Initialize R2 as a counter

- LOOP1: Instruction 1

- **Instruction 2**

Subtract Branch > 0 LOOP

R2, R2, #1 ; may change status ; check status

#### LOOP2: Instruction 1 Subtract R2, R2, #1 ; may change status ; don't touch Z bit Instruction x ; don't touch Z bit Branch > 0 LOOP

; check status

# **Thumb Conditional Branch**

| Cond | THUMB assembler | ARM equivalent | Action                                                                                    |

|------|-----------------|----------------|-------------------------------------------------------------------------------------------|

| 0000 | BEQ label       | BEQ label      | Branch if Z set (equal)                                                                   |

| 0001 | BNE label       | BNE label      | Branch if Z clear (not equal)                                                             |

| 0010 | BCS label       | BCS label      | Branch if C set (unsigned higher or same)                                                 |

| 0011 | BCC label       | BCC label      | Branch if C clear (unsigned lower)                                                        |

| 0100 | BMI label       | BMI label      | Branch if N set (negative)                                                                |

| 0101 | BPL label       | BPL label      | Branch if N clear (positive or zero)                                                      |

| 0110 | BVS label       | BVS label      | Branch if V set (overflow)                                                                |

| 0111 | BVC label       | BVC label      | Branch if V clear (no overflow)                                                           |

| 1000 | BHI label       | BHI label      | Branch if C set and Z clear<br>(unsigned higher)                                          |

| 1001 | BLS label       | BLS label      | Branch if C clear or Z set<br>(unsigned lower or same)                                    |

| 1010 | BGE label       | BGE label      | Branch if N set and V set, or N<br>clear and V clear (greater or<br>equal)                |

| 1011 | BLT label       | BLT label      | Branch if N set and V clear, or N clear and V set (less than)                             |

| 1100 | BGT label       | BGT label      | Branch if Z clear, and either N set<br>and V set or N clear and V clear<br>(greater than) |

| 1101 | BLE label       | BLE label      | Branch if Z set, or N set and V clear, or N clear and V set (less than or equal)          |

N=negative Z=zero C=carry V=overflow

Kin Fun LI, University of Victoria

Introduction to Computer Architecture

Instruction Set Architecture 44