## Conference Program and Exhibitor Listings

## Welcome to the electronic packaging's premier conference!

The 62nd Electronic Components and Technology Conference

# May 29 - June 1, 2012

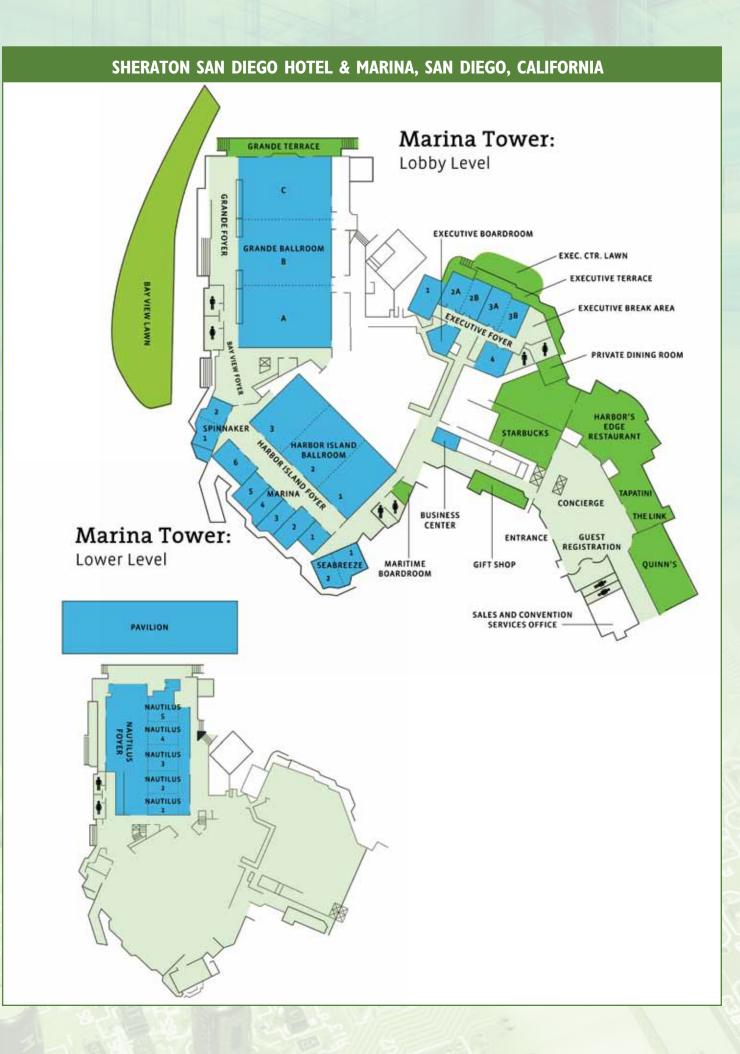

Sheraton San Diego Hotel & Marina San Diego, California, USA

Sponsored by:

Supported by:

For more information, visit: www.ectc.net

## Welcome from the Mayor of San Diego

April 4, 2012

Greetings,

Thank you for choosing San Diego for the 62<sup>nd</sup> Electronic Components and Technology Conference. San Diegans are tremendously proud of their city, a city known worldwide for its warm hospitality and sunny disposition. I'm certain, you, too, will be impressed with all San Diego has to offer.

Best known for its near-perfect climate, natural beauty and fun-filled outdoor recreational activities, San Diego is consistently rated among the nation's top convention destinations and is a perfect match for the 62<sup>nd</sup> Electronic Components and Technology Conference.

San Diego is characterized by a relaxed and friendly spirit that represents the best of the Southern California lifestyle. The pulse of the city is creative, entrepreneurial and energetic.

Once you've experienced what millions of visitors love about our community, you are destined to fall in love with San Diego. With miles of breathtaking sandy beaches, beautiful parks, renowned family attractions, sophisticated and eclectic dining, rich arts and culture and a dynamic nightlife, San Diego's many charms are impossible to resist.

On behalf of the City of San Diego, I welcome you to America's Finest City!

Sincerely,

JERRY SANDERS Mayor

## WELCOME FROM ECTC GENERAL AND PROGRAM CHAIRS

The Executive and Program Committees of the Electronic Components and Technology Conference (ECTC) welcome you to our 62nd conference at the San Diego Sheraton Marina and Resort, San Diego, Calif. This premier international conference is sponsored by the IEEE Components, Packaging and Manufacturing Technology Society (CPMT).

The ECTC Program Committee represents a wide range of disciplines and expertise from the electronics industry around the world. We have selected more than 300 high-quality papers to be presented at the conference in 36 oral sessions, four interactive presentation session and one student posters session. The 36 sessions run through the daytime and cover peer-reviewed papers on 3D/TSV, sensors and MEMS, embedded devices, LEDs, co-design, RF packaging, microfluidics, and inkjet, in addition to conventional packaging topics such as advanced packaging technologies, all types and levels of interconnections, materials, assembly manufacturing, system packaging, optoelectronics, reliability, electronic components and simulation. The program committee strives to address new trends as well as ongoing technological issues. Four Interactive Presentation sessions feature technical peer-reviewed presentations presented in a format that enhances and encourages interaction. One student poster session focuses on research conducted in the academia presented by the budding scientists. Authors from companies, research institutes, and universities in nearly 20 countries will present at the ECTC, making it a truly diverse and global conference.

In addition to the technical sessions that are held during the day, four panel sessions focusing on crucial topics presented by industry experts enhance the technical program. In the special session titled "Next Generation Packaging and Integration: The Transformed Role of the Packaging Foundry," session chair Raj Pendse will gather a panel of experts to present and discuss the increased level of integration in the changing landscape and what subcontracted assembly companies are doing to address customer demand. This panel is intended to serve as an excellent roadmap review for the industry where significant portion relies on subcontracted assembly.

The Panel Discussion on Tuesday evening at 7:30 pm, chaired by Rolf Aschenbrenner and Ricky Lee and titled "Power Electronics: A Booming Market," will focus on power electronics from a packaging perspective. The Plenary Session on Wednesday 7:00 pm, chaired by Christopher Bower and titled "Photonics: Expanding Markets and Emerging Technologies," will unveil the less-known world of photonics research and discuss how it can help improve the semiconductor revenues. Thursday evening starts with the Gala Reception at 6:30 pm and is followed by the CPMT Seminar at 8:00 pm, which is titled "Advanced Coreless Package Substrate and Material Technologies" and chaired by Kishio Yokouchi and Venky Sundaram.

The Professional Development Courses (PDC), organized by the PDC Committee chaired by Kitty Pearsall, will be taught on Tuesday (8:00 am-5:30 pm). World-class experts in their fields offer 16 courses on different topics. Participants can catch up on new technology developments and broaden their technical knowledge base. The technical program and professional development courses are supplemented by the Technology Corner Exhibits where leading companies primarily in the electronics components, materials, and packaging fields exhibit their latest technologies and products. The exhibitors invite you to their reception on Wednesday at 5:30 pm. Along with our receptions and coffee breaks every day, luncheons are another great opportunity to network and discuss technical and business matters. It is our pleasure to announce that Greg Bartlett, the CTO of GLOBALFOUNDRIES will be the invited keynote speaker at the ECTC Luncheon on Wednesday.

The International Electronics Manufacturing Initiative (iNEMI) will host the North American Workshop to solicit input for the 2013 iNEMI roadmap on Tuesday (8:00 am- 6:00 pm).

There is always more than we can explain at the ECTC. Whether you are a manager, engineer, executive or a student, we invite you to experience the exiting developments in electronic components and technology. We would like to take this opportunity to thank our sponsors, exhibitors, authors and speakers, instructors, session chairs, committee members; and arrangement, finance, publication, and publicity chairs, as well as all the volunteers for their support and hard work. We also thank all conference attendees in advance for making the 62nd ECTC a great success. We hope you will like the program and enjoy the conference, and appreciate your feedback.

David McCann General Chair GLOBALFOUNDRIES

Senol Pekin Program Chair Intel Corporation

## WELCOME FROM ECTC SPONSORING ORGANIZATION

This is 2012! There have been many predictions about 2012, including the most devastating one. No matter which version of predictions you believe in, there is one thing for sure: the 62nd Electronic Components and Technology Conference in San Diego will continue the glory from the previous series of ECTC conferences and achieve a big success!

The core of ECTC is its technical

program, which typically consists of 36 oral sessions in three full days. Together with two half-day interactive sessions and one student posters session, the whole technical program accommodates approximately 350 papers from authors/ presenters all over the world in academia and industry. These papers were selected from a pool of more than 700 abstract submissions, which were reviewed by technical sub-committees that consist of about 150 dedicated experts worldwide in electronic packaging and manufacturing. Such a rigorous procedure ensures the outstanding quality of ECTC technical proceedings. The other three pillars of ECTC are professional development courses, panels, and industrial exhibition. Every year these events attract big crowds for participation. With the conference location in southern California, the 62nd ECTC will undoubtedly maintain its momentum in these three areas.

Starting in 2011, the IEEE Components, Packaging & Manufacturing Technology (CPMT) Society has become the sole sponsor to ECTC. This enables an effective and consistent operation of the conference. Being the president of the sponsoring organization, I would like to extend the warm welcome from IEEE CPMT to all attendees of the 62nd ECTC. I also would like to take this opportunity to thank numerous volunteers who contributed to the success of the 62nd ECTC. There will be a luncheon hosted by IEEE CPMT on Thursday, May 31. Please join us as we extend our hospitality and appreciation.

See you then! Ricky Lee President, IEEE CPMT Society

## **CONFERENCE POLICIES AND GUIDELINES**

### **Badges**

Conference attendees MUST wear the official conference badge to be admitted to all training courses, sessions, meals, Technology Corner Exhibits and all conference sponsored social functions.

### **Medical Services**

For emergency medical services, locate any hotel phone, whether in your room or elsewhere in the hotel, and follow its directions for emergencies. Hotel "house" phones have been placed throughout the hotel and conference area for your convenience. If no phone can be located, please locate the nearest hotel staff or ECTC staff for assistance with your emergency. The closest available hotel staff person may be at the front desk.

### **Personal Property**

The hotel's safety deposit box is available for storing your valuables, particularly cash and jewelry. If there is a mini-safe in your room, you should consider using it.

### **Smoking Policy**

The hotel does not allow smoking on it premise. Smoking is also NOT permitted at any ECTC activities including, but not limited to, functions, events, sessions, or seminars as well. Thank you for your consideration and cooperation.

# **Corning® Semiconductor Glass Wafers**

Enabling Next-Generation Glass Solutions For Advanced Packaging

# CORNING

www.corning.com/semiglass

## TABLE OF CONTENTS

| Conference Policies & Guidelines                                                                 | 4 | Session 18: Innovative Test Methods                              | 15    |

|--------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------|-------|

| ECTC Luncheon Speaker                                                                            |   | Session 19: Thru Via Technologies                                |       |

| iNEMI 2013 Roadmap Workshop                                                                      |   | Session 20: Co-Design for the 3D Ecosystem                       |       |

| Registration                                                                                     |   | Session 21: Flip Chip Technologies                               |       |

| PDC Instructors and Proctors Breakfast                                                           |   | Session 22: Precision Components, Sensors and RF Packaging       |       |

| Session Chairs & Speakers Breakfast                                                              |   |                                                                  |       |

| Speaker Prep Room                                                                                |   | Session 23: Assembly Challenges of Area Array Packages           |       |

| Companion Hospitality Room                                                                       |   | Session 24: Inkjet Technology and Embedded Devices               |       |

| Miscellaneous Information                                                                        |   | Session 25: 3D Integration                                       | 18    |

| Luncheons                                                                                        |   | Session 26: Advanced Wirebonding                                 | 18    |

| ECTC Panel Discussion                                                                            |   | Session 27: Bonding Materials and Processes                      |       |

| ECTC Plenary Session                                                                             |   | Session 28: New Trends in Mechanical Modeling and Characterizati |       |

| CPMT Seminar                                                                                     | 7 | Session 29: Novel Approaches in Wafer Level Manufacturing        |       |

| Special Session: Next Generation Packaging and Integration -                                     | _ | Session 30: Interconnect Reliability                             |       |

| the Transformed Role of the Packaging Foundry                                                    |   |                                                                  |       |

| Professional Development Courses                                                                 |   | Session 31: Applications with 3D Technologies                    |       |

| Session Chairs & Speaker Reception                                                               |   | Session 32: Advanced Substrate and Wafer Level Packaging         |       |

| 62nd ECTC Gala Reception                                                                         |   | Session 33: Substrates and Thermal Interface Materials           | 20    |

| Technology Corner Reception                                                                      |   | Session 34: 3D Systems and Emerging PackagesThermal and Therma   | 0-    |

| ECTC Student Reception                                                                           |   | Mechanical Studies                                               |       |

| Continuing Education Units                                                                       |   | Session 35: Optical Interconnects                                |       |

| 2011 ECTC Paper Awards                                                                           |   | Session 36: Integrated Microfluidics                             |       |

| Committee Meetings                                                                               |   | Session 37: Interactive Presentations I (9:00 a.m 11:00 a.m.)    |       |

| Session 1: 3D Interconnect: Bonding and Assembly                                                 |   |                                                                  |       |

| Session 2: Next Generation Packaging Reliability<br>Session 3: MEMS Integration and Processing   |   | Session 38: Interactive Presentations 2 (2:00 p.m 4:00 p.m)      |       |

|                                                                                                  |   | Session 39: Interactive Presentations 3 (9:00 a.m 11:00 a.m.)    |       |

| Session 4: Signal and Power Analysis<br>Session 5: LEDs and Emerging Optoelectronics Integration |   | Session 40: Interactive Presentations 4 (2:00 p.m 4:00 p.m.)     |       |

| Session 6: Novel Interconnections                                                                |   | Session 41: Student Posters (8:30 a.m 10:30 a.m.)                |       |

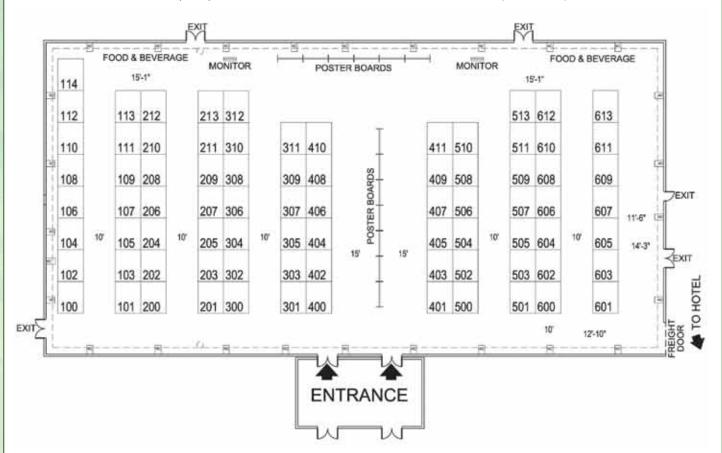

| Session 7: Interposer Technology                                                                 |   | Technology Corner Booth Layout                                   |       |

| Session 8: 3D Reliability                                                                        |   | Technology Corner Exhibits                                       |       |

| Session 9: Sensors and MEMS                                                                      |   | ECTC Executive Committee                                         |       |

| Session 10: Conductive and Non-Conductive Adhesives                                              |   | ECTC Program Committee                                           |       |

| Session 11: Advanced Flip Chip and Underfill Assembly                                            |   |                                                                  |       |

| Session 12: Solder and Material Characterization                                                 |   | 63rd ECTC Call for Papers                                        |       |

| Session 13: 3D TSV Manufacturing                                                                 |   | 63rd ECTC Dates and Location                                     |       |

| Session 14: Flip Chip Interconnect and Electromigration                                          |   | Conference Sponsors                                              | 40-41 |

| Session 15: Innovative Processes and Techniques                                                  |   | Media Sponsors                                                   | 41    |

| Session 16: 3D Electrical Analysis                                                               |   | Hotel Layout                                                     |       |

| Session 17: Lead Free Solders                                                                    |   | Conference at a Glance                                           |       |

|                                                                                                  |   |                                                                  |       |

Conference organizers reserve the right to cancel or change this program without prior notice.

## ECTC Luncheon Keynote Speaker Wednesday, May 30, 2012 • Noon

Grande Ballroom

## Bridging the Gap between the Silicon and Packaging Worlds

## **Presenter: Gregg Bartlett** Chief Technology Officer at GLOBALFOUNDRIES

Gregg Bartlett is Chief Technology Officer at GLOBALFOUNDRIES, where he is responsible for the company's technology strategy, advanced node development, technology partnerships, and alliances. Gregg joined

GLOBALFOUNDRIES in 2009 after a 25-year career in technical and management positions at Freescale Semiconductor and its predecessor, Motorola's Semiconductor Products Sector.

Immediately prior to joining GLOBALFOUNDRIES, Gregg served as Vice President of Design Technology at Freescale, where he was responsible for design methodology and the creation of design IP and collateral for advanced solutions across high-performance networking, automotive, wireless and analog product markets.

He is a member of the board of directors of the Semiconductor Research Corporation, as well as various consortium governance committees. Gregg received his bachelor's degree in chemical engineering from Kansas State University.

## 2012 iNEMI Roadmap -**North American** Workshop

## Tuesday, May 29, 2012

Since 1994, iNEMI (the International Electronics Manufacturing Initiative) has been developing a biennial technology roadmap spanning a 10-year horizon. In 2004, iNEMI expanded the initiative to proactively include global input. This year ECTC is hosting one of the several regional meetings intended to solicit input for the 2013 iNEMI Roadmap. Open to all conference attendees.

## **REGISTRATION, RECEPTIONS AND GENERAL INFORMATION**

## Registration

ECTC registration will be open at the ECTC Registration Desk in the Bayview Foyer, Marina Tower of the Sheraton San Diego Hotel & Marina.

Monday, May 28, 2012 – 3:00 p.m. - 5:00 p.m. (PD Courses & Conference)

Tuesday, May 29, 2012 – 6:45 a.m. - 8:15 a.m. (AM PD Courses & Special Session Only)

Tuesday, May 29, 2012 – 11:00 a.m. - 1:15 p.m. (PM PD Courses Only)

Tuesday, May 29, 2012 – 1:15 p.m. - 5:00 p.m. (Conference)

Wednesday, May 30, 2012 - 6:45 a.m. - 4:00 p.m.

Thursday, May 31, 2012 - 7:30 a.m. - 4:00 p.m.

Friday, June 1, 2012 – 7:30 a.m. - 12:00 p.m.

The above schedule for Tuesday will be vigorously enforced to prevent students from being late for their courses.

## **Door Registration Fees**

Door Registration with Proceedings on USB drive

| Joint ITHERM & ECTC                 | \$1,000 |

|-------------------------------------|---------|

| IEEE Member Full Registration       | \$725   |

| IEEE Member Speaker / Session Chair | \$625   |

| IEEE Member One Day                 | \$475   |

| IEEE Member Speaker One Day         | \$350   |

| Non-Member Full Registration        | \$870   |

| Non-Member Speaker / Session Chair  | \$625   |

| Non-Member One Day                  | \$475   |

| Non-Member Speaker One Day          | \$350   |

| Student                             | \$250   |

| Student Speaker                     | \$250   |

| Exhibits Only                       | \$20    |

|                                     |         |

Tuesday Professional Development Courses

| IEEE Members and Non-Members                  |        |

|-----------------------------------------------|--------|

| Tuesday AM or PM Course with luncheon         | \$475  |

| Tuesday All-Day Courses with luncheon         | \$675  |

| Tuesday Student All-Day Courses with luncheon | .\$125 |

| Extra Luncheon Tickets for each day           | \$50   |

| Extra Proceedings with Registration           |        |

## **Professional Development Course Instructors Breakfast**

PDC Instructors and Proctors are required to attend a briefing breakfast.

7:00 a.m. Tuesday – PDC Instructors and Proctor Briefing (Room Location: Executive Center 4)

## **Session Chairs and Speakers Breakfast**

Session Chairs and speakers are requested to attend a complimentary continental breakfast on the morning of their sessions/presentations. At this time, presentations will be transferred to the conference PC, which is loaded with Windows XP and MS Office 2003.

7:00 a.m. Wednesday thru Friday (Room Location: Grande Ballroom B)

### Speaker Prep Room

Speakers should prepare and review their digital presentations as follows: 7:00 a.m. – 5:00 p.m., Tuesday – Friday (Room Location: Marina 3)

(It is extremely important to assure that your presentation, presentation software and computer work flawlessly with the digital projector provided.)

## **Companion Hospitality Room**

| 8:00 a.m 4:00 p.m. | Wednesday - Thursday                   |  |

|--------------------|----------------------------------------|--|

|                    | (Room Location: 411 & 415 / 4th floor) |  |

| 8:00 a.m Noon      | Friday                                 |  |

|                    | (Room Location: 411 & 415 /4th floor)  |  |

## **MISCELLANEOUS INFORMATION**

### Hotel Concierge

The Hotel Concierge, located in the hotel lobby, can direct you to any show or restaurant, or give suggestions for that special night out. The Concierge can help to make your visit to San Diego a memorable one!

### **Message Center**

Please use the hotel switchboard or the ECTC Registration Desk located at the Bayview Foyer to leave and pickup messages. The hotel number is +1-619-291-2900.

### **Press Room**

Press interviews will be scheduled on an as-requested basis. Check at the ECTC Registration Desk (Bayview Foyer) to schedule an interview while onsite. You may also coordinate an interview with conference leadership or presenting technical experts by contacting Eric Perfecto at perfecto@us.ibm.com or +1-845-894-4400.

## LUNCHEONS

#### Tuesday, May 29, 2012 Noon (Grande Ballroom A)

The Electronic Components and Technology Conference will sponsor a luncheon for all Professional Development Courses attendees, instructors, proctors and PDC committee members.

## Wednesday, May 30, 2012 Noon (Grande Ballroom A - C)

The Electronic Components and Technology Conference and the Lucheon Sponsor ASE will sponsor a luncheon for conference attendees. Best and Outstanding Papers will be awarded. The guest speaker will be Gregg Bartlett of GLOBALFOUNDRIES.

### Thursday, May 31, 2012 Noon (Grande Ballroom A - C)

The IEEE Components, Packaging and Manufacturing Technology Society will sponsor a luncheon for conference attendees. The CPMT awards will be presented.

### Friday, June 1, 2012 Noon (Grande Ballroom B - C)

The ECTC Program Chair will sponsor a luncheon for conference attendees.

There will be a raffle for attendees.

## SPECIAL SESSION, PLENARY SESSION, PANEL SESSION AND CPMT SESSION

SPECIAL SESSION Tuesday, May 29, 2012 • 10:00 AM – Noon Nautilus I

Next Generation Packaging and Integration the Transformed Role of the Packaging Foundry

Chair: Raj Pendse, STATS ChipPAC, Inc.

Speakers: Robert Darveaux, Amkor Technology Bill Chen, Advanced Semiconductor Engineering (ASE) Mike Ma, Siliconware Precision Industries (SPIL) Steve Anderson, STATS ChipPAC, Inc. Dan Tracy, SEMI ECTC PLENARY SESSION Wednesday, May 30, 2012 • 7:00 - 9:00 p.m. Harbor Island I & II

## **Photonics: Expanding Markets & Emerging Technologies**

Chair: Christopher Bower, Semprius Inc.

Speakers: Ashok Krishnamoorthy, Oracle Jeff Perkins, Yole Development Sheng Liu, Huazhong University of Science and Technology Alexander Fang, Aurrion Timo Aalto, VTT Technical Research Centre of Finland Frank Libsch, IBM Corporation

## ECTC PANEL SESSION

Tuesday, May 29, 2012 • 7:30 - 9:30 p.m. Harbor Island I & II

**Power Electronics - A Booming Market**

Co-chair: Rolf Aschenbrenner, Fraunhofer IZM Co-chair: Ricky Lee, Hong Kong University of Science and Technology

Speakers: Dan Kinzer, Fairchild Semiconductor Corp. Klaus-Dieter Lang, Fraunhofer IZM Lionel Cadix, Yole Development Ljubisa Stevanovic, GE Global Research Bernd Roemer, Infineon Technologies AG

## **CPMT SEMINAR**

Thursday, May 31, 2012 • 8:00 PM - 10:00 PM Harbor Island I & II

Advanced Coreless Package Substrate & Material Technologies

Co-chair: Kishio Yokouchi, Fujitsu Interconnect Technologies Ltd. Co-chair: Venky Sundaram, Georgia Institute of Technology

> Speakers: Yuji Nishitani, Sony Corp. Tanaka Kuniyuki, Shinko Electric Industries Co., Ltd. Takeshi Eriguchi, Asahi Glass Co., Ltd. Masateru Koide, Fujitsu Advanced Technologies Ltd.

These sessions/seminars are open to all conference attendees.

## PROFESSIONAL DEVELOPMENT COURSES TUESDAY, MAY 29, 2012

| Morning Courses 8:00 a.m. – Noon                                                                                                                                                                      | Afternoon Courses 1:15 – 5:15 p.m.                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Seabreeze<br>I. Lead-Free Solder Joint Reliability – Material<br>Consideration<br>Course Leader: Ning-Cheng Lee – Indium<br>Corporation                                                               | Seabreeze<br>9. Package Failure Analysis – Failure Analysis<br>and Analytical Tools<br>Course Leaders: Rajen Dias and Deepak Goyal –<br>Intel Corporation                                                      |

| Harbor Island I<br>2. Multi-Physics Modeling in IC Packaging and<br>Microsystems<br>Course Leader: Xuejun Fan – Lamar University                                                                      | Harbor Island I<br>10. Near Junction Remediation of On-Chip<br>Hot Spots<br>Course Leaders: Avram Bar-Cohen – University<br>of Maryland; Karl J. L. Geisler – General Dynamics<br>Advanced Information Systems |

| Marina 2<br>3. Wafer Level Chip Scale Packaging<br>(WL-CSP)<br>Course Leader: Luu Nguyen –Texas Instruments, Inc.                                                                                     | Marina 2<br>11. Technology Advances in 3D-TSV Integration<br>and Packaging of Micro-Nano-Systems<br>Course Leader: James J.Q. Lu – Rensselaer<br>Polytechnic Institute                                         |

| Marina 4<br>4. 3D Integration: Alternative to Continued<br>Scaling<br>Course Leader: Philip Garrou – Microelectronic<br>Consultants of NC                                                             | Marina 4<br>12. 3D IC Packaging & Integration, and 3D Si<br>Integration<br>Course Leader: John Lau – Industrial Technology<br>Research Institute                                                               |

| Harbor Island II<br>5. Polymers/Nano-Composites-Electronic &<br>Photonic Packaging: Recent Advances<br>Course Leaders: C.P. Wong – Georgia Institute of<br>Technology; Daniel Lu – Henkel Corporation | Harbor Island II<br>13. Polymers in Electronic Packaging<br>Course Leader: Jeffrey Gotro – InnoCentrix, LLC                                                                                                    |

| Harbor Island III<br>6. Analog and Power Electronics Packaging<br>Course Leader: Yong Liu – Fairchild Semiconductor<br>Corporation                                                                    | Harbor Island III<br>14. Flip Chip Technology<br>Course Leader: Eric Perfecto – IBM Corporation                                                                                                                |

| Marina 6<br>7. Fundamental Concepts of Reliability &<br>Mechanics in Electronic Packaging<br>Course Leaders: Shubhada Sahasrabudhe and<br>Sandeep Sane – Intel Corporation                            | Marina 6<br>15. Design for Package Reliability<br>Course Leaders: Darvin Edwards and Yaoyu Pang –<br>Texas Instruments, Inc.                                                                                   |

| Spinnaker<br>8. Methods for Efficient High-Frequency<br>Modeling and Optimization of<br>Interconnections in Electronic Packaging<br>Course Leaders: Ivan Ndip and Michael Toepper –<br>Fraunhofer IZM | Spinnaker<br>16. IC Package Design Signal & Power<br>Integrity & EMC<br>Course Leader: Sam Karikalan – Broadcom<br>Corporation                                                                                 |

REFRESHMENT BREAKS - 10:00 - 10:20 a.m. & 3:00 - 3:20 p.m. HARBOR ISLAND FOYER

### **ECTC STUDENT RECEPTION**

Tuesday, May 29, 2012 5:00 - 6:00 p.m. Executive Center Break Area Host: Eric Perfecto – IBM Corporation

Students, have you ever wondered how the ECTC technical committees review and select papers? Or just what subjects, content and paper organization make a standout ECTC paper? Then please come to the ECTC Student Reception. You'll have a chance to enjoy some good food and meet with representatives of each technical subcommittee. Don't miss this chance for an inside view of technical subcommittee operations. Sponsored by the IBM Corporation.

## **GENERAL CHAIR'S SPEAKERS RECEPTION**

Tuesday, May 29, 2012 6:00 - 7:00 p.m. Grande Ballroom A

Invited session chairs and speakers are requested to attend a reception in Grande Ballroom A.

## **TECHNOLOGY CORNER RECEPTION**

Wednesday, May 30, 2012 5:30 - 6:30 p.m.

An Exhibitor Sponsored Reception will be held in the Pavilion, located in the white tented area just outside the Bayview Foyer. All attendees and guests are invited.

## 62ND ECTC GALA RECEPTION Thursday, May 31, 2012 6:30 p.m.

All badged attendees and guests are invited to attend a reception outside on the Bayview Lawn area. The rain backup will be Grande Ballroom B - C.

## **CONTINUING EDUCATION UNITS**

The IEEE Components, Packaging and Manufacturing Technology Society (CPMT) has been authorized to offer Continuing Education Units (CEUs) by the International Association for Continuing Education and Training (IACET) for all Professional Development Courses that will be presented at the 62nd ECTC. CEUs are recognized by employers for continuing professional development as a formal measure of participation and attendance in "non-credit" self-study courses, tutorials, symposia and workshops. IEEE CPMT CEUs can be applied towards the "IEEE CPMT Professional Development Certificate." Complete details, including voluntary enrollment forms, will be available at the conference. All costs associated with ECTC Professional Development Courses CEUs will be underwritten by the conference, i.e. there are no additional costs for Professional Development Courses attendees to obtain CEU credit.

## **2011 ECTC PAPER AWARDS**

## Best of Conference Papers - 2011

The Electronic Components and Technology Conference is proud to announce the "Best of Conference" papers selected from the 61st ECTC proceedings. The authors of the Best Session Paper share a check for US \$2,500 and the authors of the Best Poster Paper share a check for US \$1,500. The winning authors also receive a personalized plaque commemorating their achievement.

## **Best Session Paper**

(Session 32, paper 4) Characterization and Failure Analysis of TSV Interconnects: From Non-Destructive Defect Localization to Material Analysis with Nanometer Resolution

Michael Krause, Frank Altmann, Christian Schmidt, and Matthias Petzold – Fraunhofer IWM; D. Malta and D.Temple – RTI International

## **Best Poster Paper**

(Session 39, paper 9) Conformal Atomic Layer Deposition (ALD) of Alumina on High Surface-Area Porous Copper Electrodes to Achieve Ultra-High Capacitance Density on Silicon Interposers

Hongtao Kanika Sethi, Himani Sharma, P. Markondeya Raj, Venky Sundaram, and Rao Tummala – Georgia Institute of Technology

## Outstanding Papers - 2011

The winning authors for Conference Outstanding Session and Poster Papers receive a personalized plaque commemorating their achievement and will share a check for US \$1,000.

## **Outstanding Session Paper**

(Session 7, paper 4) Advanced Reliability Study of TSV Interposers and Interconnects for the 28nm Technology FPGA

Bahareh Banijamali, Suresh Ramalingam, Kumar Nagarajan, and Raghu Chaware – Xilinx, Inc.

## **Outstanding Poster Paper**

(Session 38, paper 14) Maximum Channel Density in Multimode Optical Waveguides for Parallel Interconnections

Takaaki Ishigure, Ryota Ishiguro, Hisashi Uno, and Hsiang-Han Hsu – Keio University

## Intel Best Student Paper - 2011

The winning student receives a personalized plaque and a check for \$2,500. The following paper was selected based on the Intel Best Student Paper competition conducted at the 61st ECTC:

(Session 16, Paper 3) Aging Aware Constitutive Models for SnAgCu Solder Alloys

S. Chavali,Y. Singh, P. Kumar, G. Subbarayan, I. Dutta and D. R. Edwards – Purdue University

## **COMMITTEE MEETINGS • ASSOCIATED COMMITTEE MEMBERS ONLY**

### Tuesday, May 29, 2012

9:00 a.m. – 5:00 p.m. iNEMI Meeting Nautilus 3

9:00 a.m. – 5:30 p.m. ITRS Assemblies & Packaging Technology Committee *Executive Center I*

5:00 p.m. – 7:00 p.m. CPMT Region 8 Advisory Committee Meeting Room 514, 5th floor

> 9:00 p.m. – 10:30 p.m. ECTC OPTO Committee Marina 6

## Wednesday, May 30, 2012

7:00 a.m. – 8:00 a.m. CPMT Materials TC Meeting Room 514, 5th floor

7:00 a.m. – 8:00 a.m. CPMT High-Density Board Packaging TC

Meeting Room 511, 5th floor

4:30 p.m. – 5:30 p.m. CPMT Technical Committee Chairs Meeting Room 518, 5th floor

6:00 p.m. – 7:00 p.m. Program Subcommittee Chairs & Assistant Chairs Reception General Chair's Suite (by invitation only)

## Thursday, May 31, 2012

**6:45 a.m. – 7:45 a.m.** CPMT Transactions Editors / AEs *Marina* 2

7:00 a.m. – 8:00 a.m. CPMT Education TC Meeting Room 514, 5th floor

5:30 p.m. – 6:30 p.m. ECTC 2013 Program Committee Meeting Harbor Island III

8:00 p.m. 62nd ECTC Governing/Executive Committee Reception General Chair's Suite (by invitation only)

## Friday, June 1, 2012

7:00 a.m. – 8:00 a.m. CPMT RF & Wireless TC Marina 2

**7:00 a.m. – 8:00 a.m.** CPMT Nano Packaging TC Meeting Room 514, 5th floor

**1:30 p.m. – 4:30 p.m.** ECTC Executive Committee *Executive Center 3B*

## Program Sessions: Wednesday, May 30, 8:00 a.m. - 11:40 a.m.

| Program Sessions: Wednesday, May 50, 6:00 a.m 11:40 a.m.                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Session 1: 3D Interconnect:<br>Bonding and Assembly                                                                                                                                                                                                                                                                                                                                            | Session 2: Next Generation Packaging<br>Reliability                                                                                                                                                                                                                                               | Session 3: MEMS Integration and<br>Processing                                                                                                                                                                                                                               |  |  |

| Committee:<br>Interconnections                                                                                                                                                                                                                                                                                                                                                                 | Committee:<br>Applied Reliability                                                                                                                                                                                                                                                                 | Committees: Emerging Technologies /<br>Electronic Components & RF                                                                                                                                                                                                           |  |  |

| Harbor Island II                                                                                                                                                                                                                                                                                                                                                                               | Harbor Island I                                                                                                                                                                                                                                                                                   | Harbor Island III                                                                                                                                                                                                                                                           |  |  |

| Session Co-Chairs:<br>Changqing Liu – Loughborough University<br>James Lu – Rensselaer Polytechnic Institute                                                                                                                                                                                                                                                                                   | Session Co-Chairs:<br>Sridhar Canumalla – Microsoft Corporation<br>Jeffrey Suhling – Auburn University                                                                                                                                                                                            | Session Co-Chairs:<br>John Cunningham – Oracle<br>P. Markondeya Raj – Georgia Institute of Technology                                                                                                                                                                       |  |  |

| <ol> <li>8:00 a.m. – Structural Design, Process, and<br/>Reliability of a Wafer-Level 3D Integration<br/>Scheme with Cu TSVs based on Micro-Bump/<br/>Adhesive Hybrid Wafer Bonding<br/>C.T. Ko, Z.C. Hsiao, P.S. Chen, J.H. Huang, H.C. Fu, Y.J.<br/>Huang, C.W. Chiang, C.K. Lee, H.H. Chang, W.L. Tsai,<br/>and Y.H. Chen – ITRI;Y.J. Chang – National Chiao Tung<br/>University</li> </ol> | <ol> <li>8:00 a.m. – Board Level Solder Joint Assembly<br/>and Reliability for Ultra Thin BGA Packages<br/>Mohammad M. Hossain, Srinivasa R.Aravamudhan,<br/>Marilyn Nowakowski, Xiaoqing Ma, Satyajit S. Walwadkar,<br/>Vijay Kulkarni, and Sriram Muthukumar – Intel<br/>Corporation</li> </ol> | <ol> <li>8:00 a.m. – Electronic Packaging of Sensors<br/>for Lower Limb Prosthetics         <ul> <li>Kelly Lee and Nancy Stoffel – College of Nanoscale<br/>Science and Engineering; Kevin Fite – Clarkson<br/>University</li> </ul> </li> </ol>                            |  |  |

| <ol> <li>8:25 a.m. – Evaluation of 3D Interconnect<br/>Routing and Stacking Strategy to Optimize<br/>High Speed Signal Transmission for Memory<br/>on Logic<br/>J. Roullard, S. Capraro, T. Lacrevaz, C. Bermond, G.<br/>Houzet, and B. Flechet – Université de Savoie; A.<br/>Farcy – STMicroelectronics; J. Charbonnier, C. Fuchs, C.<br/>Ferrandon, and P. Leduc – CEA-LETI</li> </ol>      | <ol> <li>8:25 a.m. – Safe Working Process Strain Limits<br/>for Large Area Array Packages: Observations<br/>from Spherical Bend Testing<br/>John McMahon, Brian Gray, and Brian P. Standing –<br/>Celestica</li> </ol>                                                                            | <ol> <li>8:25 a.m. – Cost Effective Thin Film Packaging<br/>for Wide Area MEMS         J.L. Pornin, D. Saint-Patrice, C. Gillot, E. Lagoutte, M. Pellat,<br/>and S. Fanget – CEA-LETI     </li> </ol>                                                                       |  |  |

| 3. 8:50 a.m. – Study of Low Temperature and<br>High Heat-Resistant Fluxless Bonding via<br>Nanoscale Thin Film Control toward Wafer-<br>Level Multiple Chip Stacking for 3D LSI<br>Eiji Morinaga, Yuichi Oka, Hiroaki Nishimori, Haruhiko<br>Miyagawa, Ryohei Satoh, Yoshiharu Iwata, and Ryota<br>Kanezaki – Osaka University                                                                 | <ol> <li>8:50 a.m. – Board Level Drop Test Modeling<br/>Masazumi Amagai and Jang Seungmin – Texas<br/>Instruments, Inc.</li> </ol>                                                                                                                                                                | <ol> <li>8:50 a.m. – Low Temperature Sealing Process<br/>for Vacuum MEMS Encapsulation</li> <li>D. Saint-Patrice, J.L. Pornin, B. Savornin, G. Rodriguez, S.<br/>Danthon, and S. Fanget – CEA-LETI</li> </ol>                                                               |  |  |

| Refr                                                                                                                                                                                                                                                                                                                                                                                           | eshment Break: 9:15 a.m. – 10:00 a.m. (Pavil                                                                                                                                                                                                                                                      | ion)                                                                                                                                                                                                                                                                        |  |  |

| <ol> <li>10:00 a.m. – High Density Metal-Metal<br/>Interconnect Bonding with Pre-Applied<br/>Fluxing Underfill<br/>Christopher Gregory, Matthew Lueck, Alan Huffman,<br/>John M. Lannon, Jr., and Dorota S. Temple – RTI<br/>International</li> </ol>                                                                                                                                          | <ol> <li>10:00 a.m. – Methods for Reliability<br/>Assessment of MEMS Devices – Case Studies<br/>of a MEMS Microphone and a 3-Axis MEMS<br/>Gyroscope<br/>J. Hokka, J. Raami, H. Hyvönen, M. Broas, J. Makkonen, J. Li,<br/>T. Mattila, and M. Paulasto-Kröckel – Aalto University</li> </ol>      | <ol> <li>10:00 a.m. – On-Chip THz 3D Antennas<br/>Paolo Nenzi, Francesco Tripaldi, Volha Varlamava, Fabrizio<br/>Palma, and Marco Balucani – University of Rome</li> </ol>                                                                                                  |  |  |

| <ol> <li>10:25 a.m. – Characterization of a Novel<br/>Fluxless Surface Preparation Process for Die<br/>Interconnect Bonding<br/>Eric F. Schulte, Keith A. Cooper, and Matthew Phillips –<br/>SET North America; Subhash L. Shinde – Sandia National<br/>Laboratory</li> </ol>                                                                                                                  | <ol> <li>10:25 a.m. – Stress Evolution in an<br/>Encapsulated MEMS Package Due to<br/>Viscoelasticity of Packaging Materials<br/>Seungbae Park, Dapeng Liu, Yeonsung Kim, and Hohyung<br/>Lee – SUNY Binghamton; Sam Zhang – Analog Devices,<br/>Inc.</li> </ol>                                  | <ol> <li>10:25 a.m. – A CMOS Embedded RF-MEMS<br/>Tunable Capacitor for Multi-Band/Multi-<br/>Mode Smartphones</li> <li>Y. Kurui, H. Yamazaki, Y. Shimooka, T. Saito, E. Ogawa, T.<br/>Ogawa, T. Ikehashi, Y. Sugizaki, and H. Shibata – Toshiba<br/>Corporation</li> </ol> |  |  |

| <ol> <li>10:50 a.m. – Development of Anhydride-<br/>Based NCFs for Cu/Sn-Ag Eutectic Bonding<br/>and Process Optimization for Fine Pitch TSV<br/>Chip Stacking<br/>Ji-Won Shin, Yong-Won Choi, Young Soon Kim, and<br/>Kyung-Wook Paik – KAIST; Un Byung Kang, Young<br/>Kun Jee, and Ji Hwan Hwang – Samsung Electronics<br/>Company, Ltd.</li> </ol>                                         | <ol> <li>10:50 a.m. – Reliability Analyses on a TSV<br/>Structure for CMOS Image Sensor<br/>Ben-Je Lwo and Chung-Yen Ni – National Defense<br/>University</li> </ol>                                                                                                                              | <ol> <li>10:50 a.m. – High Power Laminate MEMS RF<br/>Switch<br/>Sung Jun Kim, Yang Zhang, Minfeng Wang, Mark Bachman,<br/>and G.P. Li – University of California, Irvine</li> </ol>                                                                                        |  |  |

| <ol> <li>11:15 a.m. – "Dual-Purpose" Remateable<br/>Conductive Ball-in-Pit Interconnects for Chip<br/>Powering and Passive Alignment in Proximity<br/>Communication Enabled Multi-Chip<br/>Packages<br/>Hiren D. Thacker, Ivan Shubin, Ying Luo, Kannan Raj,<br/>James G. Mitchell, Ashok V. Krishnamoorthy, and John E.<br/>Cunningham – Oracle</li> </ol>                                    | <ol> <li>11:15 a.m. – Dynamic Bending Test Analysis<br/>of Inkjet-Printed Conductors on Flexible<br/>Substrates<br/>Eerik Halonen,Aki Halme, Tapio Karinsalo, Pekka Iso-<br/>Ketola, Matti Mäntysalo, and Riku Mäkinen – Tampere<br/>University of Technology</li> </ol>                          | <ol> <li>11:15 a.m. – A Novel Electrostatic Radio<br/>Frequency Micro Electromechanical Systems<br/>(RF MEMS) with Prognostics Function<br/>Yunhan Huang, Michael Osterman, and Michael Pecht –<br/>University of Maryland</li> </ol>                                       |  |  |

## Program Sessions: Wednesday, May 30, 8:00 a.m. - 11:40 a.m.

| Program Sessions: Wednesday, May 50, 6:00 a.m 11:40 a.m. |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Se                                                       | ssion 4: Signal and Power Analysis                                                                                                                                                                                                                                                                                | Session 5: LEDs and Emerging<br>Optoelectronics Integration                                                                                                                                                                                                                                                                                                                                                                                             | Session 6: Novel Interconnections                                                                                                                                                                                                                                                                                                                           |

|                                                          | ommittee:<br>odeling & Simulation                                                                                                                                                                                                                                                                                 | Committee:<br>Optoelectronics                                                                                                                                                                                                                                                                                                                                                                                                                           | Committee:<br>Interconnections                                                                                                                                                                                                                                                                                                                              |

| Na                                                       | utilus I                                                                                                                                                                                                                                                                                                          | Nautilus 3                                                                                                                                                                                                                                                                                                                                                                                                                                              | Nautilus 5                                                                                                                                                                                                                                                                                                                                                  |

| He                                                       | ssion Co-Chairs:<br>nning Braunisch – Intel Corporation<br>chael Lamson – Consultant                                                                                                                                                                                                                              | Session Co-Chairs:<br>Alex Rosiewicz – EM4<br>Hiren Thacker – Oracle Labs, Oracle                                                                                                                                                                                                                                                                                                                                                                       | Session Co-Chairs:<br>James E. Morris – Portland State University<br>Tom Gregorich – MediaTek                                                                                                                                                                                                                                                               |

| Ι.                                                       | <b>8:00 a.m.</b> – The Design of Higher-Order<br>Reference Voltage Generation Circuits for<br>Single-Ended Memory Interfaces<br>Wendem T. Beyene – Rambus, Inc.                                                                                                                                                   | <ol> <li>8:00 a.m. – High Power LED Subassemblies<br/>for Automotive Front Light Application<br/>G. Elger, B. Spinger, R. Peters, N. Benter, H.Willwohl,<br/>S. Honma, U. Bohnenkamp, A. Stolarski, M. Sikkens, A.<br/>Emmerich, and H. Gijsbers – Philips Technology GmbH;<br/>N. Lesch – Philips Lumileds</li> </ol>                                                                                                                                  | <ol> <li>8:00 a.m. – Metal-Coated Mono-Sized<br/>Polymer Core Particles for Fine Pitch Flip-<br/>Chip Interconnects</li> <li>Mark W. Sugden, Changqing Liu, David Hutt, and David<br/>Whalley – Loughborough University; Helge Kristiansen<br/>– Conpart A.S.</li> </ol>                                                                                    |

| 2.                                                       | 8:25 a.m. – Efficient and Accurate Modeling<br>of Effective Medium for Interconnects in<br>Lossy Shielded Layered Medium using Fast<br>Convergent Series<br>Sidharath Jain and Jiming Song – Iowa State University;<br>Telesphor Kamgaing and Yidnekachew Mekonnen – Intel<br>Corporation                         | <ol> <li>8:25 a.m. – Application Specific LED<br/>Packaging for Automotive Forward-Lighting<br/>Application and Design of Whole Lamp<br/>Module<br/>Fei Chen, Zhangming Mao, Xing Fu, Cao Li, Mengxiong<br/>Zhao, and Sheng Liu – Huazhong University of Science<br/>and Technology; Kai Wang – Guangdong Real Faith<br/>Optoelectronics, Inc.</li> </ol>                                                                                               | <ol> <li>8:25 a.m. – THz Ribbon Waveguides using<br/>Polymer-Ceramic Nanocomposites<br/>Xianbo Yang and Premjeet Chahal – Michigan State<br/>University</li> </ol>                                                                                                                                                                                          |

| 3.                                                       | 8:50 a.m. – System-Level SoC Near-Field<br>(NF) Emissions: Simulation to Measurement<br>Correlation<br>Rajen Murugan, Souvik Mukherjee, Minhong Mi, Lionel<br>Pauc, and Claudio Girardi – Texas Instruments, Inc.;<br>Dipanjan Gope, Daniel de Araujo, Swagato Chakraborty,<br>and Vikram Jandhyala – Nimbic Inc. | <ol> <li>8:50 a.m. – Index Matched Fluidic Packaging<br/>of High Power UV LED Clusters on Aluminum<br/>Substrates for Improved Optical Output<br/>Power<br/>Marc Schneider, Benjamin Leyrer, Christian Herbold,<br/>Stefan Maikowske, and Jürgen Brandner – Karlsruhe<br/>Institute of Technology</li> </ol>                                                                                                                                            | <ol> <li>8:50 a.m. – Thermocompression Bonding of<br/>Ag-MWCNTs Nanocomposite Films as an<br/>Alternative Die-Attach Solution for High-<br/>Temperature Packaging of SiC Devices<br/>Vanessa Smet, Mamun Jamal, Alan Mathewson, and Kafil<br/>M. Razeeb – Tyndall National Institute</li> </ol>                                                             |

|                                                          | Refr                                                                                                                                                                                                                                                                                                              | eshment Break: 9:15 a.m. – 10:00 a.m. (Pavili                                                                                                                                                                                                                                                                                                                                                                                                           | on)                                                                                                                                                                                                                                                                                                                                                         |

| 4.                                                       | <b>10:00 a.m. – Statistical Analysis of Inter-<br/>Symbol-Interference and Crosstalk for<br/>Coding Buses</b><br>Yu Chang, Dan Oh, and Ralf Schmitt – Rambus, Inc.                                                                                                                                                | <ol> <li>10:00 a.m. – Advanced Thin Glass Based<br/>Photonic PCB Integration<br/>Henning Schröder and Lars Brusberg – Fraunhofer IZM;<br/>Norbert Arndt-Staufenbiel and Klaus-Dieter Lang –TU<br/>Berlin; Karim Richlowski and Christian Ranzinger –<br/>Contag GmbH</li> </ol>                                                                                                                                                                         | <ol> <li>10:00 a.m. – Novel Interconnect<br/>Methodologies for Ultra-Thin Chips on Foils<br/>A. Sridhar; H. Fledderus, R.H.L. Kusters, and J. van den<br/>Brand – TNO/Holst Centre; M. Cauwe – IMEC</li> </ol>                                                                                                                                              |

| 5.                                                       | <b>10:25 a.m. – Simulation Challenges in</b><br><b>Designing High Speed Serial Links</b><br>Arun Reddy Chada – Missouri University of Science and<br>Technology; Bhyrav Mutnury, Douglas Wallace, Douglas<br>Winterberg, and Minchuan Wang – Dell Inc.;Antonio<br>Ciccomancini Scogna – CST of America, Inc.      | <ol> <li>10:25 a.m. – A Laminate Cantilever<br/>Waveguide Optical Switch<br/>Jonas Tsai, Arthur Yang Zhang, G.P. Li, and Mark Bachman<br/>– University of California, Irvine</li> </ol>                                                                                                                                                                                                                                                                 | <ol> <li>10:25 a.m. – Gold Passivated Mechanically<br/>Flexible Interconnects (MFIs) with High<br/>Elastic Deformation<br/>Chaoqi Zhang, Hyung Suk Yang, and Muhannad S. Bakir –<br/>Georgia Institute of Technology</li> </ol>                                                                                                                             |

| 6.                                                       | 10:50 a.m. – A New Approach to Deriving<br>Packaging System Statistical Eye Diagram<br>Based on Parallel Non-Linear Transient<br>Simulations using Multiple Short Signal Bit<br>Patterns<br>Zhaoqing Chen, Wiren Dale Becker, and George Katopis<br>– IBM Corporation                                             | <ol> <li>10:50 a.m. – Pick and Align–High Precision<br/>Active Alignment of Optical Components<br/>Michael Leers, Matthias Winzen, Erik Liermann, Heinrich<br/>Faidel, Thomas Westphalen, Joern Miesner, Joerg<br/>Luttmann, and Dieter Hoffmann – Fraunhofer Institute<br/>for Laser Technology ILT</li> </ol>                                                                                                                                         | <ol> <li>10:50 a.m. – Microsolder/Adhesive Hybrid<br/>Joints for High-Density, High-Power,<br/>High-Reliability, and Reworkable Module<br/>Interconnection in Mobile Phones<br/>Kiwon Lee and Kyung-Wook Paik – KAIST; Ilkka J.<br/>Saarinen and Lasse Pykari – Nokia Corporation</li> </ol>                                                                |

| 7.                                                       | <ul> <li>11:15 a.m. – Optimizing the Timing Center<br/>for High-Speed Parallel Buses</li> <li>Dan Oh, Arun Vaidyanath, Chris Madden, and Yohan</li> <li>Frans – Rambus, Inc.; Woopoung Kim – Qualcomm, Inc.</li> </ul>                                                                                            | <ol> <li>11:15 a.m. – Fabrication of Low Cost Wafer-<br/>Level Micro-Lens Arrays with Spacers using<br/>Glass Molds by Combining a Chemical Foaming<br/>Process (CFP) and a Hot Forming Process (HFP)<br/>Shunjin Qin, Jintang Shang, Tingting Wang, Wenlin Kuai,<br/>and Wenlong Wei – Southeast University; Li Zhang and<br/>Chiming Lai – Jiangyin Changdian Advanced Packaging<br/>Co. Ltd.; Siyuan Lv – Nanjing Foreign Language School</li> </ol> | <ol> <li>11:15 a.m. – Hybrid Au-Underfill Resin<br/>Bonding with Lock-and-Key Structure<br/>Masatsugu Nimura, Jun Mizuno, and Shuichi Shoji<br/>– Waseda University; Akitsu Shigetou – National<br/>Institute for Materials Science; Katsuyuki Sakuma – IBM<br/>Corporation; Hiroshi Ogino and Tomoyuki Enomoto –<br/>Nissan Chemical Industries</li> </ol> |

## Program Sessions: Wednesday, May 30, 1:30 p.m. - 5:10 p.m.

| Program Sessio                                                                                                                                                                                                                                                                                                                                                                                                     | ons: weanesday, May 30, 1:30                                                                                                                                                                                                                                                           | p.m 5:10 p.m.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 7: Interposer Technology                                                                                                                                                                                                                                                                                                                                                                                   | Session 8: 3D Reliability                                                                                                                                                                                                                                                              | Session 9: Sensors and MEMS                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Committee:<br>Advanced Packaging                                                                                                                                                                                                                                                                                                                                                                                   | Committees: Applied Reliability /<br>Interconnections                                                                                                                                                                                                                                  | Committee:<br>Advanced Packaging                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Harbor Island II                                                                                                                                                                                                                                                                                                                                                                                                   | Harbor Island I                                                                                                                                                                                                                                                                        | Harbor Island III                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Session Co-Chairs:<br>Christopher Bower – Semprius, Inc.<br>John Knickerbocker – IBM Corporation                                                                                                                                                                                                                                                                                                                   | Session Co-Chairs:<br>Vikas Gupta – Texas Instruments, Inc.<br>Wei-Chung Lo – ITRI                                                                                                                                                                                                     | Session Co-Chairs:<br>Ricky Lee – Hong Kong Univ. of Science & Technology<br>James Zhang – Micron Technology, Inc.                                                                                                                                                                                                                                                                                                                                    |

| <ol> <li>1:30 p.m. – Integrating Through-Silicon Vias<br/>with Solder Free, Compliant Interconnects for<br/>Novel, Large Area Interposers<br/>Ivan Shubin, Alex Chow, Hiren D. Thacker, Kannan Raj,<br/>Ashok V. Krishnamoorthy, James G. Mitchell, and John<br/>E. Cunningham – Oracle; Eugene M. Chow and Dirk<br/>DeBruyker – Palo Alto Research Center (PARC); Koji<br/>Fujimoto – DNP America, LLC</li> </ol> | <ol> <li>1:30 p.m. – High-Frequency Measurements of<br/>TSV Failures<br/>Joohee Kim, Daniel Jung, Jonghyun Cho, Jun So Pak, and<br/>Joungho Kim – KAIST; Jong Min Yook and Jun Chul Kim<br/>– Korea Electronics Technology Institute</li> </ol>                                        | <ol> <li>1:30 p.m. – Assembly and Packaging<br/>Technologies for High Temperature SiC-<br/>Sensors<br/>Roderich Zeiser, Phillipp Wagner, and Jürgen Wilde –<br/>University of Freiburg</li> </ol>                                                                                                                                                                                                                                                     |

| <ol> <li>I:55 p.m. – Process Integration and Testing<br/>of TSV Si Interposers for 3D Integration<br/>Applications<br/>J. Lannon Jr., A. Hilton, A. Huffman, M. Lueck, E.Vick, S.<br/>Goodwin, G. Cunningham, D. Malta, C. Gregory, and D.<br/>Temple – RTI International</li> </ol>                                                                                                                               | <ol> <li>1:55 p.m. – Electrical Characterization<br/>Method to Study Barrier Integrity in 3D<br/>Through-Silicon Vias<br/>Y.L. Li, D. Velenis, T. Kauerauf, M. Stucchi, Y. Civale, A.<br/>Redolfi, and K. Croes – IMEC</li> </ol>                                                      | <ol> <li>1:55 p.m. – Drop Impact Reliability of MEMS<br/>Inertial Sensors with Membrane Suspensions<br/>for Mobile Phones<br/>Jong Woon Kim, Heung Woo Park, Min Kyu Choi,<br/>Won Kyu Jeung, and Jung Won Lee – Samsung Electro-<br/>Mechanics Company, Limited</li> </ol>                                                                                                                                                                           |

| <ol> <li>2:20 p.m. – High Density and Low-Cost<br/>Silicon Interposer using Thin-film and Organ<br/>Lamination Processes<br/>Jong-Min Yook, Jun Chul Kim, Se-Hoon Park, Jong-In<br/>Ryu, and Jong Chul Park – Korea Electronics Technolog<br/>Institute</li> </ol>                                                                                                                                                 | Fine Pitch Solder Micro-Bumps<br>Bahareh Banijamali, Suresh Ramalingam, Henley Liu, and                                                                                                                                                                                                | 3. 2:20 p.m. – Chip on Board Development for<br>a Novel MEMS Accelerometer for Seismic<br>Imaging<br>Zhuqing Zhang, Jennifer Wu, Sheldon Bernard, and<br>Robert G.Walmsley – Hewlett Packard Company                                                                                                                                                                                                                                                  |

| F                                                                                                                                                                                                                                                                                                                                                                                                                  | efreshment Break: 2:45 p.m 3:30 p.m. (Pavili                                                                                                                                                                                                                                           | ion)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ol> <li>3:30 p.m. – Assembly and Reliability<br/>Challenges in 3D Integration of 28nm FPGA<br/>Die on a Large High Density 65nm Passive<br/>Interposer<br/>Raghunandan Chaware, Kumar Nagarajan, and Suresh<br/>Ramalingam – Xilinx, Inc.</li> </ol>                                                                                                                                                              | <ol> <li>3:30 p.m. – Chip Package Interaction in<br/>Micro Bump and TSV Structure<br/>Ha-Young You, Yuchul Hwang, Jun-Woo Pyun, Young-<br/>Gyun Ryu, and Hyoung-Sub Kim – Samsung Electronics<br/>Co., Ltd.</li> </ol>                                                                 | <ol> <li>3:30 p.m. – Failsafe Wafer-Level Packaging of<br/>a Piezoelectric MEMS Actuator</li> <li>M.A. Matin, K. Ozaki, D.Akai, K. Sawada, and M. Ishida –<br/>Toyohashi University of Technology</li> </ol>                                                                                                                                                                                                                                          |