# Digital power controller with PMBus

# **About this document**

#### Scope and purpose

This document explains the hardware features and serves as the user guide for the EVAL\_600W\_FBFB\_XDPP evaluation board, designed by Infineon Technologies. The XDPP1100-Q024 digital controller belongs to Infineon's XDP™ digital controller family. It is optimized to provide high performance and design flexibility for controlling DC-DC power converters. This controller helps designers to achieve high efficiency, system control, and cost-saving goals for applications such as telecom, servers, and data centers. EVAL\_600W\_FBFB\_XDPP offers an easy-to-use test platform for stand-alone evaluation of the 24-pin XDPP1100 controller's performance. To introduce and explore the various features of XDPP1100-Q024, this document explains how to use XDPP1100-Q024 to control an isolated hard-switching full-bridge DC-DC power converter.

#### Intended audience

Power supply design engineers, system engineers, embedded power designers

# **Table of contents**

| 1     | General description                                                                           | 3  |

|-------|-----------------------------------------------------------------------------------------------|----|

| 1.1   | Specifications                                                                                | 3  |

| 1.1   | Block diagram                                                                                 | 4  |

| 1.2   | Power-board overview                                                                          | 4  |

| 1.2.1 | Non-dissipative snubber                                                                       | 5  |

| 1.2.2 | Auxiliary power supply                                                                        | 5  |

| 1.3   | Daughterboard overview                                                                        | 5  |

| 1.3.1 | Jumper settings                                                                               | 6  |

| 2     | Evaluation board setup                                                                        | 7  |

| 2.1   | Hardware required                                                                             | 7  |

| 2.2   | Board setup                                                                                   | 7  |

| 3     | Getting started                                                                               | 9  |

| 3.1   | Software GUI                                                                                  | 9  |

| 3.1.1 | System requirements                                                                           | 9  |

| 3.1.2 | Install GUI                                                                                   | 9  |

| 3.2   | Initiate the connection and communication to the XDPP1100 digital controller through the GUI. | 9  |

| 3.3   | Powering up the converter                                                                     | 13 |

| 3.3.1 | Measured efficiency                                                                           | 14 |

| 3.3.2 | Output voltage ripple                                                                         | 15 |

| 4     | Design configuration and evaluate XDPP1100                                                    | 16 |

| 4.1   | Device Topology (PWM mapping and topology selection)                                          | 16 |

| 4.1.1 | Topology tab                                                                                  | 16 |

| 4.1.2 | DeadTime tab                                                                                  | 17 |

| 4.2   | System settings (flexible startup and shutdown)                                               | 19 |

| 4.2.1 | Startup and shutdown tab                                                                      |    |

|       |                                                                                               |    |

# Digital power controller with PMBus

# **General description**

| 4.2.2       | Flexible startup                                                                              | 22 |

|-------------|-----------------------------------------------------------------------------------------------|----|

| 4.3         | PID – bode plot (Kp, Ki, Kd gain tuning and loop stability (gain margin and phase margin))    | 22 |

| 4.3.1       | Bode plot tab                                                                                 | 22 |

| 4.3.2       | Load model tab                                                                                | 23 |

| 4.4         | Faults and protection (fault responses and limits)                                            | 25 |

| 4.4.1       | Protections tab                                                                               | 26 |

| 4.4.2       | Fault Configuration tab                                                                       | 28 |

| 4.4.3       | Common Faults tab                                                                             | 29 |

| 4.4.4       | Pmbus Command protections tab                                                                 | 30 |

| 4.4.5       | Overcurrent and short-circuit protection experimental results                                 | 31 |

| 4.5         | Basic configuration (V <sub>IN</sub> telemetry, I <sub>OUT</sub> , I <sub>IN</sub> telemetry) |    |

| 4.5.1       | Output current sense tab                                                                      |    |

| 4.5.1.1     | Temperature sense                                                                             | 33 |

| 4.5.2       | Input current sense tab                                                                       | 34 |

| 4.5.3       | Vin Telemetry tab                                                                             | 35 |

| 4.5.3.1     | Setting tlm0_vin_src_sel to VRS1 (VRSEN, vrs_init prior to startup)                           | 36 |

| 4.5.3.2     | Setting tlm0_vin_src_sel to TS ADC V <sub>IN</sub> (PRISEN)                                   |    |

| 4.5.4       | PWM/ramp tab                                                                                  |    |

| 4.5.5       | Telemetry tab                                                                                 |    |

| 4.6         | Advanced features (droop, burst, fast transients, feed-forward, flux balancing)               |    |

| 4.6.1       | Feed-forward tab                                                                              |    |

| 4.6.2       | Flux balancing tab                                                                            |    |

| 4.6.3       | Burst mode tab                                                                                |    |

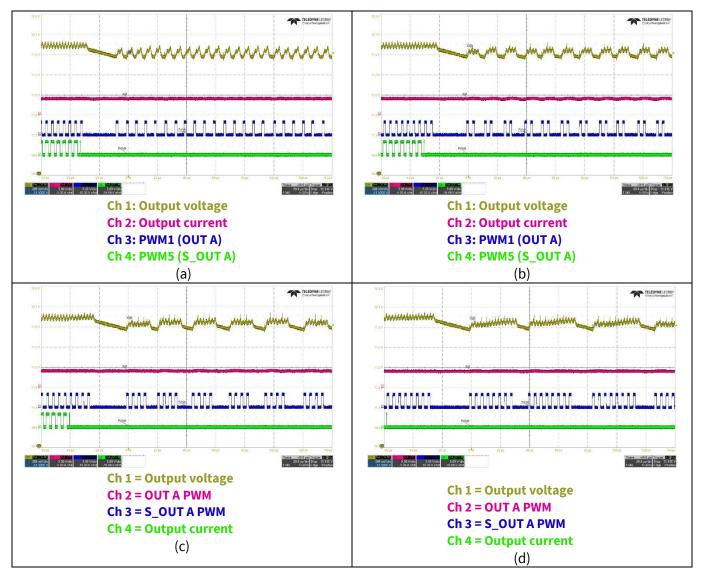

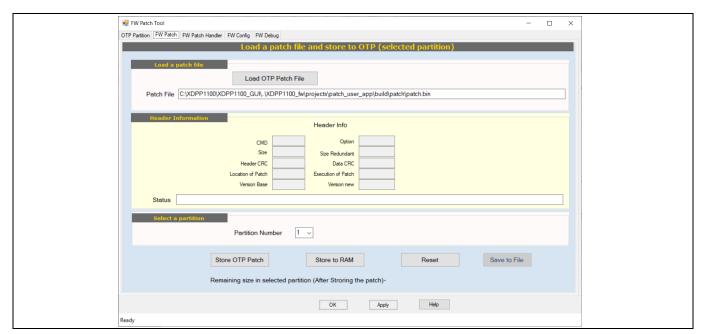

| 4.7         | FW patch (FW patching, configuration and FW debug)                                            |    |

| 4.7.1       | OTP Partition tab                                                                             |    |

| 4.7.2       | FW patch tab                                                                                  |    |

| 4.7.2.1     | Load PMBus spreadsheet                                                                        |    |

| 4.7.3       | FW Patch Handler tab                                                                          |    |

| 4.8         | Store user configuration to OTP                                                               |    |

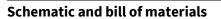

|             | hematic and bill of materials                                                                 |    |

| 5 5c<br>5.1 | Schematic                                                                                     |    |

| 5.2         | Bill of materials                                                                             |    |

|             |                                                                                               |    |

|             | omenclature                                                                                   |    |

| Referen     | ces                                                                                           | 57 |

| Revision    | history                                                                                       | 58 |

# **Digital power controller with PMBus**

# 1 General description

The evaluation board features the XDPP1100-Q024 digital power controller, which is the smallest in the class available on the market. It drives Infineon's state-of-the-art MOSFETs (OptiMOS™ 5 100 V and OptiMOS™ 6 40 V) using Infineon's dual-channel gate drivers (EiceDRIVER™ 2EDL8024G and EiceDRIVER™ 2EDL8124G) in a full-bridge isolated dc-dc power supply topology.

The EVAL\_600W\_FBFB\_XDPP evaluation kit contains the following boards which are orderable separately:

- 1. Isolated full-bridge DC-DC converter power-board, EVAL\_600W\_FBFB\_XDPP

- 2. XDPP1100-Q024 daughterboard, EVAL\_XDPP1100\_Q024\_DB

- 3. USB to I<sup>2</sup>C dongle, USB007A1

- 4. Graphical user interface (the GUI can be downloaded from the Infineon website <a href="https://softwaretools.infineon.com/tools/com.ifx.tb.tool.xdpp1100configuratortool">https://softwaretools.infineon.com/tools/com.ifx.tb.tool.xdpp1100configuratortool</a>)

# 1.1 Specifications

Table 1 Specifications

|                                                                                                           | Min.  | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------|-------|------|------|------|

| Input voltage range                                                                                       | 36    |      | 75   | V    |

| V <sub>IN</sub> turn-on threshold                                                                         | 35    |      |      | V    |

| V <sub>IN</sub> turn-off threshold                                                                        | 30    |      |      | V    |

| Maximum input current (100 percent load, 42 V <sub>IN</sub> )                                             |       |      | 16   | А    |

| Output voltage (at V <sub>IN</sub> = 42 V to 72 V)                                                        |       | 12   |      | V    |

| Output current (natural convection)                                                                       |       |      | 20   | А    |

| Output current (400 LFM)                                                                                  |       |      | 50   | А    |

| Output voltage regulation ( $V_{IN}$ = 42 V to 72 V, Load 0 to 50 A, Tc = -40°C to 85°C)                  |       | ±120 |      | mV   |

| Output voltage ripple (peak to peak at full load) With 990 µF output capacitor                            |       |      | 300  | mV   |

| Load transient (48 $V_{IN}$ , 990 $\mu F$ and 132 $\mu F$ , 1 A/ $\mu s$ ) 50 percent to 100 percent load |       | ±300 |      | mV   |

| Load-transient settling time                                                                              |       | 100  |      | μs   |

| Switching frequency                                                                                       |       | 250  |      | kHz  |

| Efficiency at 48 V, 20 A                                                                                  |       | 95.3 |      | %    |

| Operating temperature (ambient)                                                                           | -40   |      | 80   | °C   |

| Isolation voltage                                                                                         |       | 1500 |      | V    |

| Monitoring accuracy – READ_VIN                                                                            | -0.75 |      | 0.75 | V    |

| Monitoring accuracy – READ_VOUT                                                                           | -10   |      | 10   | mV   |

| Monitoring accuracy – READ_IOUT at 5A to 50A                                                              | -1.5  |      | 1.5  | А    |

| Monitoring accuracy – READ_TEMPERATURE                                                                    | -5    |      | 5    | °C   |

# Digital power controller with PMBus

# 1.1 Block diagram

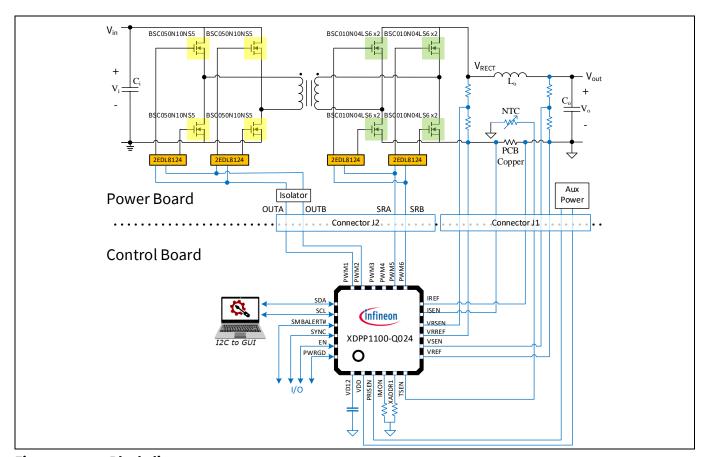

The block diagram of the evaluation kit is shown in **Figure 1**.

Figure 1 Block diagram

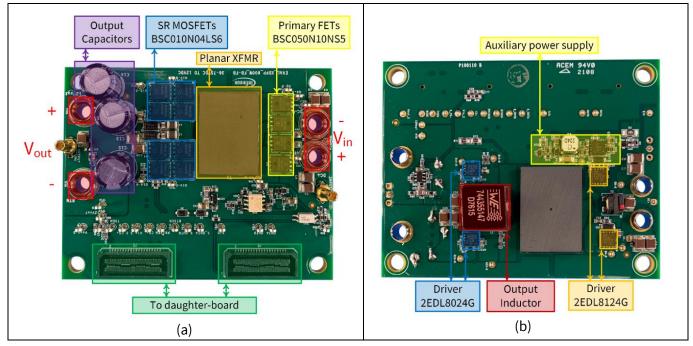

#### 1.2 Power-board overview

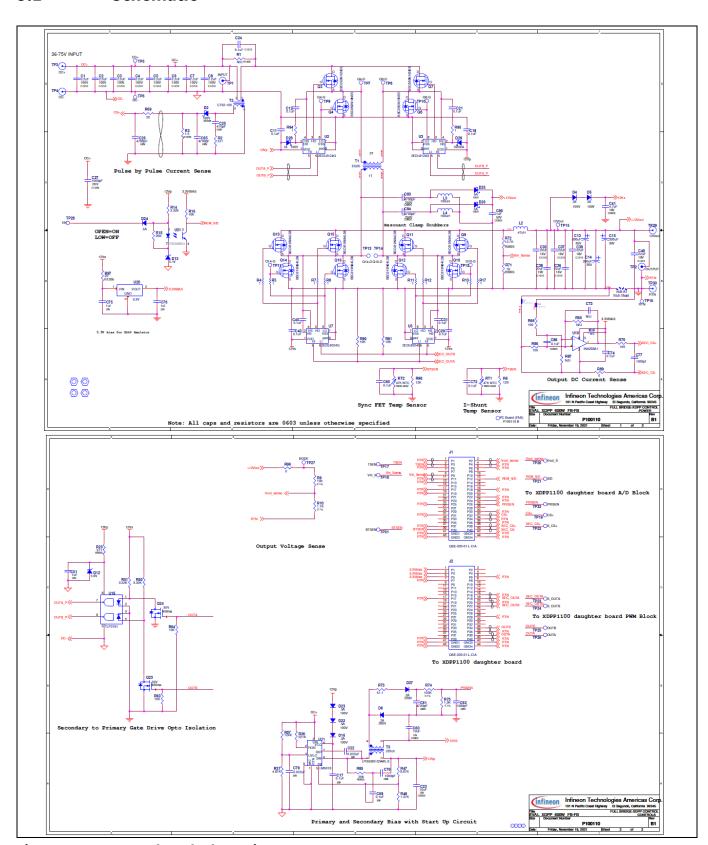

The power stage is a hard-switching full-bridge to full-bridge (FB-FB) DC-DC converter (**Figure 2**). It will be connected to the XDPP1100 digital controller daughterboard through two board-to-board rectangular connectors. Voltage mode control (VMC) is implemented for output voltage regulation to convert the input voltage range of 42 V – 75 V DC to output voltage of 12 V DC. While a fan is not included in the evaluation kit, a minimum of 400 LFM air flow is required to cool down the power stage. The recommended fan part number is 04028DA-12R-AU-F0.

The power board consists of a full-bridge converter with full-bridge synchronous rectification (SR), isolated through a planar transformer, a non-dissipative snubber, and an auxiliary power supply.

The planar transformer provides isolation between the input and the output with 3:1 turns ratio. It allows versatile polarity configurations and grounding connections for the input and output terminals. Below  $V_{IN}$  = 42 V the converter will lose 12 V regulation, and the output voltage will drop to around 10.8 V at  $V_{IN}$  = 36 V. However, it can still provide the full load current.

The output current is sensed using a small PCB copper shunt, saving power loss and cost of the precision sense resistor.

The main Infineon components used in the 600 W FB-FB evaluation board are:

XDPP1100 XDP™ IDC digital controller

# Digital power controller with PMBus

# infineon

# **General description**

- OptiMOS™ 5 100 V\_BSC050N10NS5, 100 V 5 mΩ, SuperS08 power transistor

- OptiMOS™ 6 40 V\_BSC010N04LS6, 40 V 1 mΩ, SuperS08 power transistor

- EiceDRIVER™ 2EDL8024G Infineon's isolated dual-channel junction-isolated gate driver

- EiceDRIVER™ 2EDL8124G Infineon's isolated dual-channel junction-isolated gate driver

Figure 2 Power board - a) top view, b) bottom view

# 1.2.1 Non-dissipative snubber

An Infineon-designed non-dissipative capacitor-diode-inductor (CDL) snubber circuit is used to improve the performance of the SR stage. This CDL resonant clamp snubber circuit recycles the reverse recovery current of the SR FETs' body diodes into the output capacitors. It improves the system efficiency, reduces the high frequency ringing across the secondary SR FETs, and makes it possible to have lower voltage switches in the SR stage.

# 1.2.2 Auxiliary power supply

An onboard auxiliary power supply circuit on the power board (**Figure 2b**) provides 10 VDC for primary gate drivers, isolated 10 V for the secondary gate drive circuits, and 3.3 V DC to supply XDPP1100 on the daughterboard. The approximate minimum input voltage for the auxiliary power supply operation is 30 V DC.

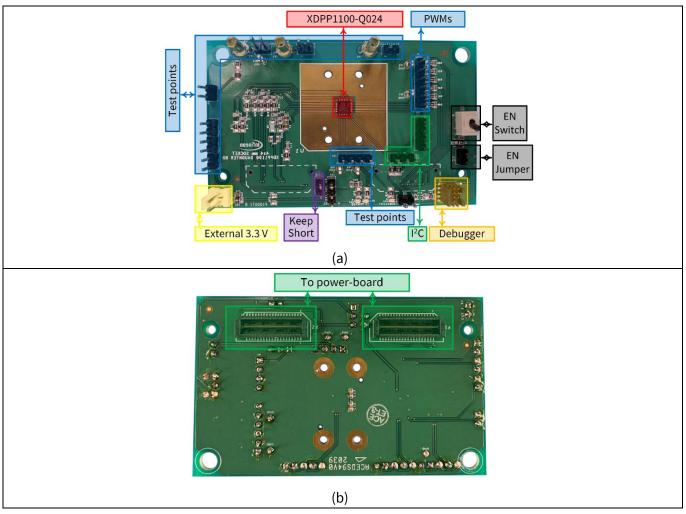

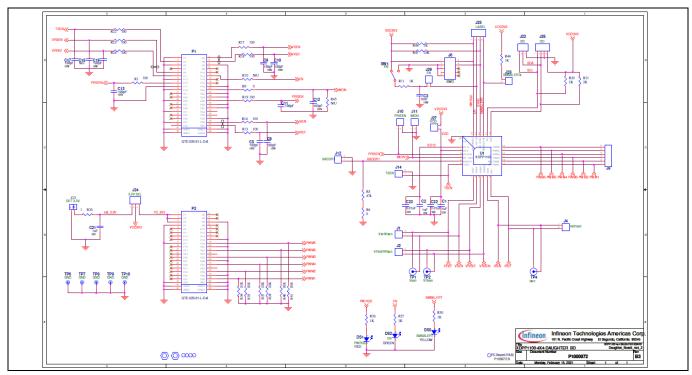

# 1.3 Daughterboard overview

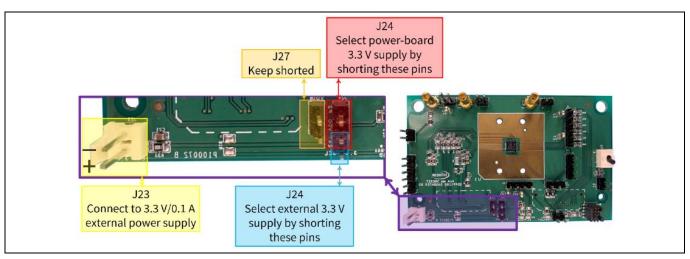

The control stage of this evaluation kit is on the EVAL\_XDPP1100\_Q024\_DB daughterboard (**Figure 3**). It includes the XDPP1100-Q024 digital controller, analog filters for processing feedback signals from the power board, PWM outputs, digital inputs and outputs, I<sup>2</sup>C connector, firmware (FW) debugger port for Lauterbach, and LED indicators. It can be supplied using an external 3.3 V DC source or from the power-board depending on the header J24 configuration (**Figure 3a**). The board-to-board rectangular header connectors are located on the bottom side of the EVAL\_XDPP1100\_Q024\_DB daughterboard to connect to the power converter board (**Figure 3b**).

# Digital power controller with PMBus

# **General description**

Figure 3 Daughterboard - a) top view, b) bottom view

# 1.3.1 Jumper settings

Table 2

Daughterboard jumper settings

| Jumper | Description           | Functionality                                                                                                                              |

|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| J23    | External 3.3 V        | External 3.3 V (0.1 A) supply should be connected to the daughterboard at J23 if external 3.3 V is selected by J24.                        |

| J24    | 3.3 V supply selector | <ul><li>Select external 3.3 V supply by shorting pins 1 and 2.</li><li>Select power board 3.3 V supply by shorting pins 2 and 3.</li></ul> |

| J27    | 3.3 V jumper          | Connect or disconnect 3.3 V supply to VDD of the IC. By default, this pin should be shorted.                                               |

| J29    | EN jumper             | Control the EN pin of XDPP1100 by an onboard toggle switch (SW1) if J29 is shorted.                                                        |

# Digital power controller with PMBus

# 2 Evaluation board setup

# 2.1 Hardware required

- Power supply (36 V DC to 75 V DC, 16 A)

- Electronic load (600 W at 12 V DC)

- Precision shunt resistors for input and output current measurement (optional)

- Digital multimeters

- Oscilloscope (500MHz or higher bandwidth)

- Fan (suggested: 04028DA-12R-AUF) (optional at low loading)

- Infineon USB to I<sup>2</sup>C dongle (USB007A1 or USB007B)

- Microsoft Windows 10 (32 or 64-bit)

# 2.2 Board setup

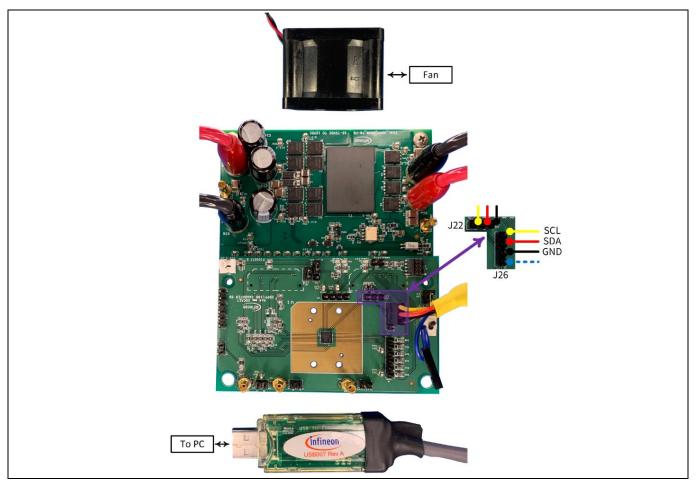

**Figure 4** shows the XDPP1100 evaluation kit set up while the XDPP1100 daughterboard is mounted on top of the power converter board.

The board-to-board connectors provide the plug-in mechanism between the power board and the daughterboard. For connecting these two boards, align the daughterboard connectors with the power board connectors and then push it down to make sure the contact is good.

The I<sup>2</sup>C dongle has the following color code: SCL – yellow, SDA – red, GND – black.

- For a non-isolated dongle (USB007A1), the blue wire can be used to control the EN pin of XDPP1100 through the GUI. In this case, it has to be connected to pin 2 of J29. If this wire is left floating, the EN pin cannot be controlled through the GUI.

- For an isolated dongle (USB007B), the blue wire has to be connected to 3.3 V to supply power to the dongle. In this case, the EN control could be done by the onboard switch SW1 (jumper J29 should be shorted).

The dongle can be connected to either J22 (no pin for blue wire) or J26 (has pin for blue wire), as shown in **Figure 4**.

# **Evaluation board setup**

Figure 4 **Evaluation test set-up**

Note:

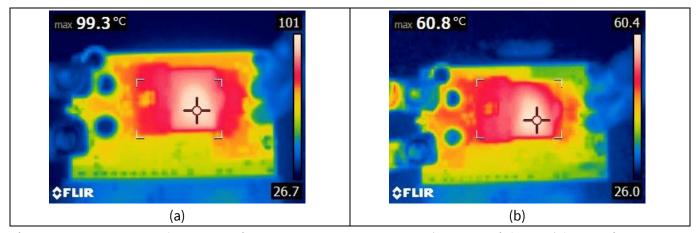

If the power board operates at room temperature with natural airflow, the maximum load current must be limited to 25 A (Figure 5).

Figure 5 Thermal performance with  $V_{IN}$  = 48 V and  $I_{OUT}$  = 25 A - a) natural airflow, b) fan cooling

# Digital power controller with PMBus

**Getting started**

# 3 Getting started

# 3.1 Software GUI

Infineon provides a complimentary GUI software tool. It provides a high-level environment for users to conveniently access advanced features of the XDPP1100 digital controller without dealing with low-level programming. Online configuring, controlling and monitoring of the evaluation kit are provided through the GUI, which enhances the overall design workflow of the system. Below are the key features:

- 1) Step-by-step design tools to configure and optimize the XDPP1100's performance for a wide variety of DC-DC topologies

- 2) Fault status monitoring

- 3) Online telemetry reporting of  $V_{OUT}$ ,  $I_{OUT}$ ,  $V_{IN}$ ,  $P_{IN}$ , and temperature

- 4) Save and load design files

- 5) Allows storing of PMBus configuration and I<sup>2</sup>C registers into RAM or one-time programmable memory (OTP)

- 6) Allows storing of FW patch into RAM or OTP for advance customized designs and control algorithm

- 7) Linear11 and Linear16 Q-number format calculator tool

Detailed steps to install the GUI and initiate its communication with the XDPP1100 evaluation board are as follows:

# 3.1.1 System requirements

- 1) Ensure that the PC is connected to the internet

- 2) Infineon's GUI tool requires installation of *Microsoft .Net Framework 4.0* (link to download)

- 3) Security warnings during the installation should be disregarded for complete and correct installation.

#### 3.1.2 Install GUI

Installing the GUI is the first step toward evaluating the XDPP1100. Download the installation package from the Infineon **software toolbox**. **Do not connect** the USB-to-I<sup>2</sup>C dongle before the installation process is complete. When installing, recommend to install the XDPP1100 GUI to the default folder C:\Users\user\_name\Infineon\Tools\XDPP1100-GUI.

Refer to the **XDPP1100 GUI installation guide** for any additional information about GUI installation or troubleshooting issues related to dongle connection.

# 3.2 Initiate the connection and communication to the XDPP1100 digital controller through the GUI

After successful installation of the GUI, USB driver, and available updates, the step-by-step procedure to connect the XDPP1100-Q024 daughterboard to the GUI for system initialization is as follows:

- 1) Set up the evaluation kit as shown in Figure 4.

- 2) For the power board, connect a DC power supply to the input terminals (TP 3 and TP 4), which is capable of supplying 36 V DC to 75 V DC and 16 A.

V 1.0

# Digital power controller with PMBus

# **Getting started**

Note:

Connect the necessary digital multimeters and probes to monitor desired voltages, current signals, and waveforms **before** turning on the power supply. As a reminder, the primary and secondary sides of the power converter are isolated. Make sure to consult the circuit schematic at the end of this document and use differential probes accordingly to comply with the isolation to prevent damage to equipment and the evaluation kit! For the power board, connect an electronic load at the output terminals (TP 29 and TP 30).

Note:

The 3.3 V VDD supply for the daughterboard is provided from an on-board auxiliary power supply in the power board. The auxiliary power supply provides 3.3 V DC bias voltage when the input voltage (TP 3 and TP 4 on the power board) is above 30 V. Alternatively, external 3.3 V DC can supply the daughterboard. In this case, the jumper placement on the J24 header has to be altered following **Figure 6**. The external bias provides flexibility, and allows the user to communicate and configure the XDPP1100 without connecting the power board to the power supply.

Figure 6 Daughterboard 3.3 V jumpers

- 3) Plug the USB dongle into the PC and the J26 header of the daughterboard (Figure 4).

- 4) If XDPP1100 is configured to operate only with the EN pin, ensure that EN switch (SW1) is in the off position (EN LED is off) for safe operation before pre-configuration. This is to avoid turning on the unit unintentionally while writing FW configuration into the memory of the digital controller.

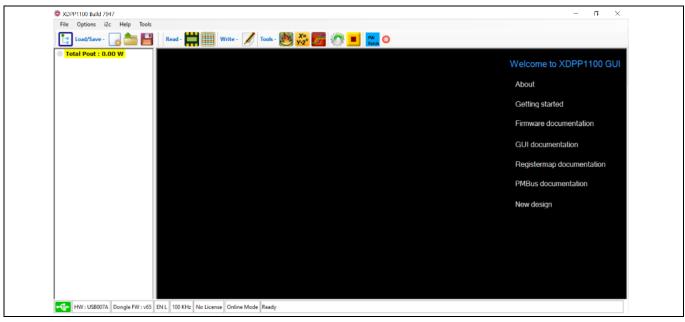

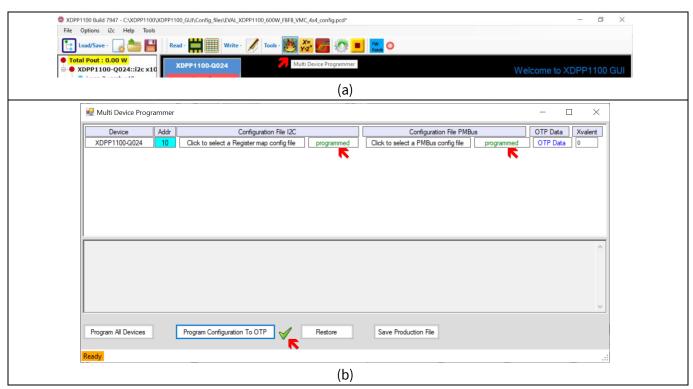

- 5) Run the **XDPP1100GUI.exe**. The GUI starting window is shown in **Figure 7**.

# Digital power controller with PMBus

# **Getting started**

Figure 7 The XDPP1100 GUI starting window

Note:

The green USB icon at the bottom left corner of the starting window indicates that its driver is installed and updated successfully. Also, the USB hardware (HW) model and dongle FW version will be shown on the information bar at the bottom of the starting window in this case. On the other hand, the red USB icon indicates that the GUI does not recognize the dongle. A troubleshooting guide for failure in recognizing the dongle is provided in XDP\_GUI\_installation\_guide (link to download).

6) Use the auto-populate shortcut button to scan the device connected through the I<sup>2</sup>C bus. If the XDPP1100 is properly biased (following step 2), the GUI will first identify the device part number and its address offset and will add the device to the design.

Note:

If the XDPP1100-Q024 is pre-programmed, the GUI will read a stored program on the digital controller and restore it into the GUI. This allows users to check the configuration stored in the non-volatile memory (NVM) of the XDPP1100. The XDPP1100 has OTP NVM, with 64 kB available space for FW patch and configuration. And, if the XDPP1100 is not pre-programmed (blank IC), the registers and PMBus command have the default values, most of which are zero.

Figure 8 Auto populate

- 7) If the XDPP1100 is not pre-programmed;

- Click File>Open Board Design (Figure 9)

- Navigate to ..\XDPP1100\_GUI\Config\_files\EVAL\_XDP\_600W\_FBFB\_VMC

- Select and open EVAL\_XDPP1100\_600W\_FBFB\_VMC\_4x4.pcd

# Digital power controller with PMBus

#### **Getting started**

Figure 9 Open design file

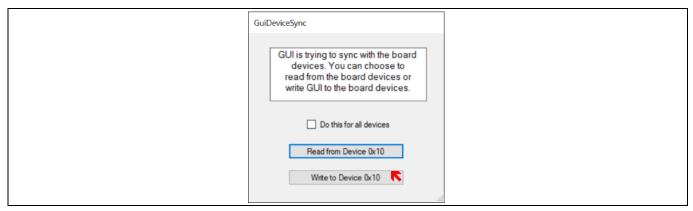

The GUI will show a pop-up window (Figure 10). Click Write to Device 0x10. This will write the program into the RAM of the XDPP1100.

Note:

RAM is a volatile memory and can be used during the design phase to try different configuration settings without wasting the non-volatile OTP space. If the configuration is stored in the RAM, the configuration would be lost when the XDPP1100 is powered off. Thus, repeating steps 8 and 9 is necessary when cycling the 3.3 V VDD and restarting the MCU. Non-volatile OTP can be used to store the finalized design settings into the IC. Please refer to Section 4.8 for storing the program in OTP.

Figure 10 Write to device operation

9) For continuous monitoring of the system parameters, which are V<sub>IN</sub>, V<sub>OUT</sub>, I<sub>IN</sub>, I<sub>OUT</sub>, temperature, and P<sub>IN</sub>, Click Options>Enable Telemetry Update (Figure 11). The check symbol next to each feature from the Options dropdown menu indicates that the item is enabled. Undocking the telemetry window can also be activated by enabling **Show Floating Status** (Figure 12) from the list.

Figure 11 **GUI options**

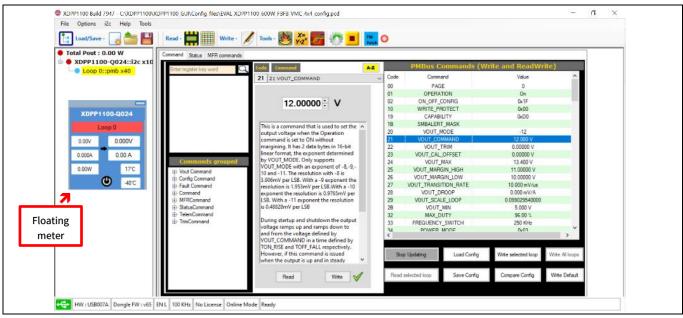

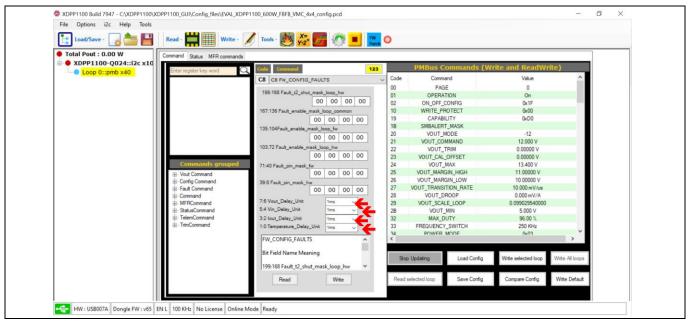

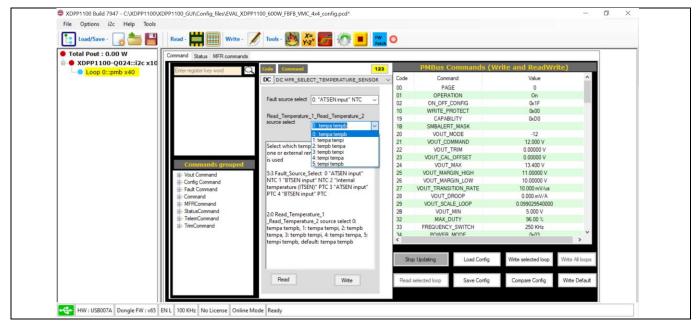

Figure 12 shows the GUI after establishing communication and ensuring the configuration file is programmed to the device. To verify establishment of communication between the digital controller and the device (Figure **12**):

- Click the **Loop0::pmbus x40** below the device part number (**XDPP1100-Q024::i2c x10**) (highlighted in yellow). It opens the PMBus configuration page of **Loop0**.

# Digital power controller with PMBus

# **Getting started**

- In PMBus Commands (Write and Read) window, select VOUT\_COMMAND (Code 21)

- Click **Read**. The green check indicates that reading from the device was successful.

- The **VOUT\_COMMAND** should be 12 V. It shows the correct Config file is programmed into the IC.

Figure 12 GUI with connected XDPP1100-Q024 and the loaded design file

The **Help** icon is located in the GUI top menu bar and provides comprehensive documentation on the wide capability of the GUI covering a number of integrated tools. These embedded tools provide an environment for fast and optimum system control design without involving in HW level programming while maintaining deep accessibility to different features of the digital controller. For more information, please refer to **Help** icon.

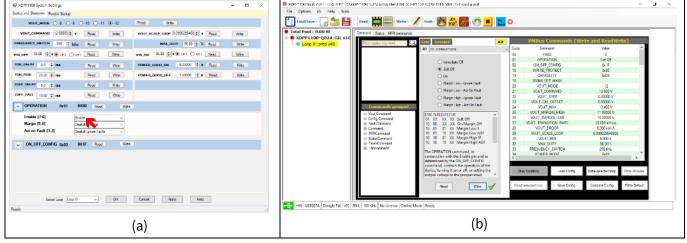

# 3.3 Powering up the converter

After successfully initiating the connection and establishing the communication between the GUI and the daughterboard (**Section 3.2**), the procedure to turn on the power converter is as follows:

Note: Make sure all steps from **Section 3.2** are complete before moving on to the following steps!

- 1) Place a fan with a minimum of 400 LFM airflow next to the power board while airflow blows over the top and the bottom of the power board where the FETs are populated. For example, supplying the recommended fan (04028DA-12R-AU-F0) with 7.5 V DC and placing it at a distance of 1 to 2 cm to the bottom side of the power board will meet the cooling criteria (**Figure 4**).

- 2) Set the electronic load to 5 A.

- 3) Enable the daughterboard using the **EN** switch (SW1) on the daughterboard.

- 4) To turn on the converter from the GUI:

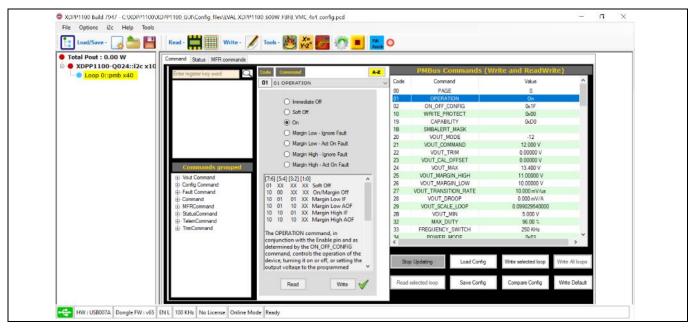

- Click the Loop0::pmbus x40 (highlighted in yellow in Figure 12). In the Command tab, the PMBus configuration page of Loop0 will be listed.

- In PMBus Commands window, select OPERATION (Code 01)

- Select On and Click Write (green check shows writing the PMBus command was successful) (Figure 13)

# Digital power controller with PMBus

# **Getting started**

Figure 13 **PMBus OPERATION command**

At this point, the evaluation board should be on, and supplying the connected 5 A electronic load with 12 V DC output voltage.

The status of the power board is provided by the PWRGD (DS1) red LED on the daughterboard. This LED indicates that the output voltage of Loop0 is between the predefined thresholds. For the first 3.3 V power-up, this LED is on as it is pulled up to 3.3 V. Once the converter is enabled, the status of this LED will be determined by the output voltage level, and the polarity of the POWER\_GOOD PMBus commands. While the default logic is active low, it can be modified to active high. To do so:

- Click the **Loop0::pmbus x40** below the device part number (**XDPP1100-Q024::i2c x10**) (highlighted in yellow in Figure 12). This opens the PMBus configuration page of Loop0.

- In the **PMBus Commands** window, select **FW\_CONFIG\_PMBUS** (Code C9).

- Set GPIO polarity to 2 and Click on Write.

Now, the current configuration file is programmed to active high.

If prefer to keep the POWER\_GOOD signal low during the device initialization, one option is to remove the pullup resistor at the PWRGD pin on the control board and set pwrgd\_ppen =1. This enables the CMOS output of the PWRGD pin. It won't be pulled up by the external circuit and drive the logic by internal push-pull circuit.

In the PMBus Commands window, Power Good ON (Code 5E) and Power Good OFF (Code 5F) PMBus commands set the Power\_Good thresholds. For example, with the current configuration;

- PWRGD (DS1) red LED is on if the output voltage is higher than Power Good ON.

- PWRGD (DS1) red LED is off if the output voltage is lower than **Power\_Good\_OFF**.

#### 3.3.1 **Measured efficiency**

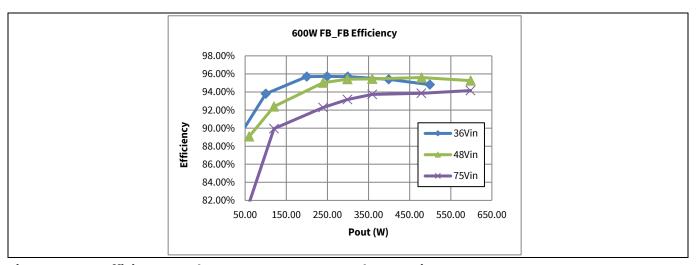

The power board efficiencies for  $V_{IN}$  = 36 V, 48 V, and 72 V in no-load and full-load operation conditions are shown in Figure 14. The efficiency results at  $V_{IN}$  = 36 V are taken with  $V_{OUT}$  set to 10 V as the power board cannot regulate due to the 3:1 turns ratio of the isolated transformer.

# Digital power controller with PMBus

# **Getting started**

Figure 14 Efficiency results at 36 V DC, 48 V DC, and 75 V DC input

# 3.3.2 Output voltage ripple

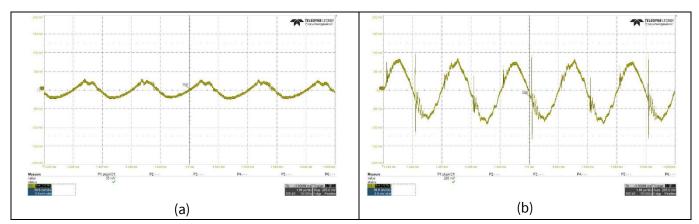

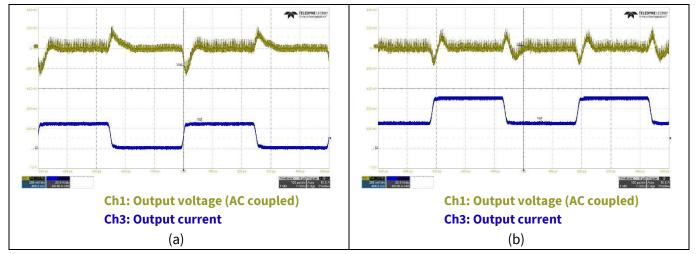

Output voltage ripple waveforms of the power board with minimum  $V_{pk-pk} = 50$  mV (at  $V_{IN} = 48$  V,  $I_{OUT} = 0$  A) and maximum  $V_{pk-pk} = 150$  mV (at  $V_{IN} = 72$  V,  $I_{OUT} = 50$  A) are shown in **Figure 15**.

Figure 15 Output voltage ripple (AC coupled mode) - a)  $V_{IN} = 48 \text{ V}$ ,  $I_{OUT} = 0 \text{ A}$ , b)  $V_{IN} = 72 \text{ V}$ ,  $I_{OUT} = 50 \text{ A}$

#### Digital power controller with PMBus

**Design configuration and evaluate XDPP1100**

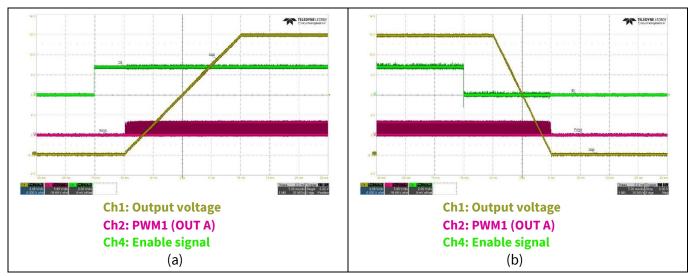

# 4 Design configuration and evaluate XDPP1100

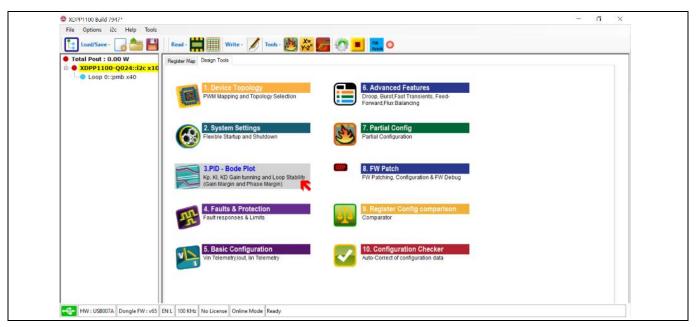

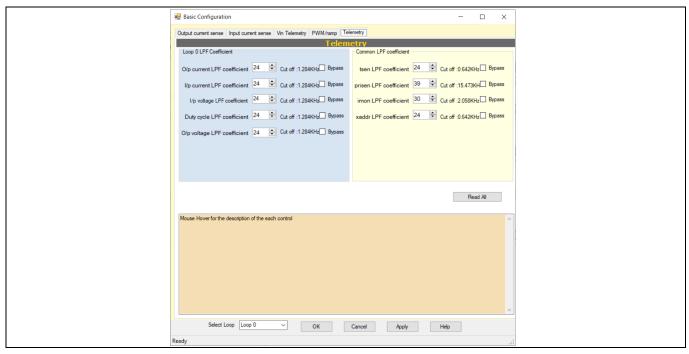

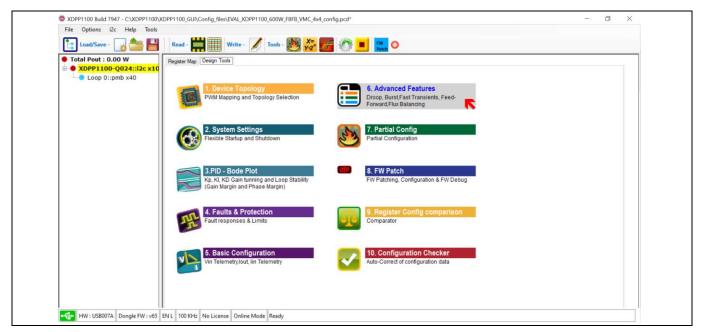

This section presents different design tools integrated with the GUI to configure the XDPP1100 digital controller to meet system requirements. The following sections are a part of the **Design Tools** window of the XDPP1100\_GUI (**Figure 16**). These sections are designed as an introduction to familiarize users with and guide them to evaluate extensive programming options and design tool features provided for the XDPP1100 family of digital controllers. More detailed and comprehensive guidelines are provided in the documents available in the **Help** dropdown menu of the GUI.

Figure 16 GUI Design Tools feature and Device Topology (PWM mapping and topology)

# 4.1 Device Topology (PWM mapping and topology selection)

Using the **Device Topology** tool, users can configure the XDPP1100 based on power board topology, targeted control strategy and PWM deadtimes settings. To access this tool:

- Click the **XDPP1100-Q024::i2c x10** (highlighted in yellow in **Figure 16**).

- Click the **Design Tools** and select **1. Device Topology**

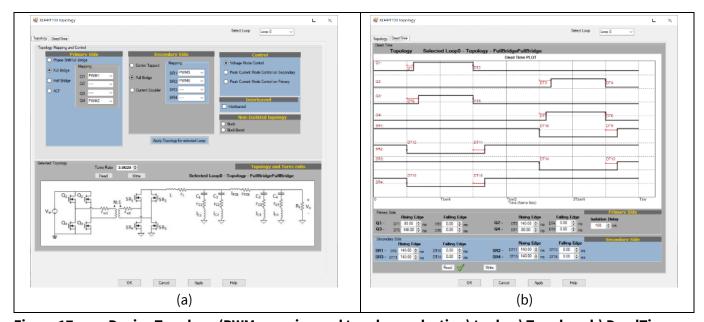

The XDPP1100 Topology window will be opened with Topology and DeadTime tabs (Figure 17).

# 4.1.1 Topology tab

User Guide

Users can select their power board topology and targeted control strategy and assign available PWMs to the switches (**Figure 17**). PWM mapping enhances the compatibility of the XDPP1100 to designed power boards and HW. They are mapped to each power switch using the drop-down list assigned for each PWM in the **Topology** tab.

The evaluation power board is a FB-FB topology. Four PWM signals from the digital controller are expanded for the diagonal switches with onboard HW. As shown in **Figure 17**, two primary switches Q2, Q3, and two secondary SR switches SR3, SR4 are left unmapped, while the other four switches are assigned to available PWM signals.

16 of 59

VMC is selected in this tab (Figure 17) as the control strategy for this evaluation kit.

# Digital power controller with PMBus

**Design configuration and evaluate XDPP1100**

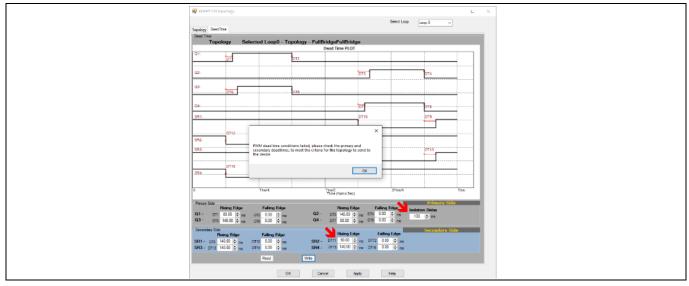

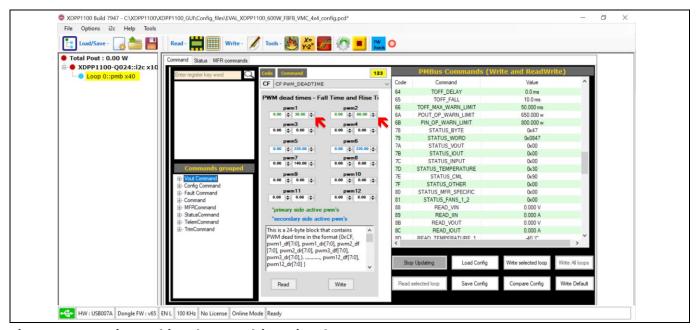

# 4.1.2 DeadTime tab

DPWM dead time settings can be programmed in the **DeadTime** tab (**Figure 17**). In this tab, interactive PWM waveforms associated with each switch provide visual system verification for assigned deadtimes.

Three PWM techniques can be provided by the PWM module of the XDPP1100, which are trailing-edge, leading-edge, and dual-edge PWM modulation. Dual-edge PWM is the default configuration, which is shown in **Figure**17. For more details of different modulation techniques, please refer to **Section 4.5.4**.

All settings in this tab will be applied just after clicking **Write**.

Note: Changes will be stored in RAM and stored into OTP once the program has been finalized.

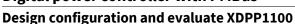

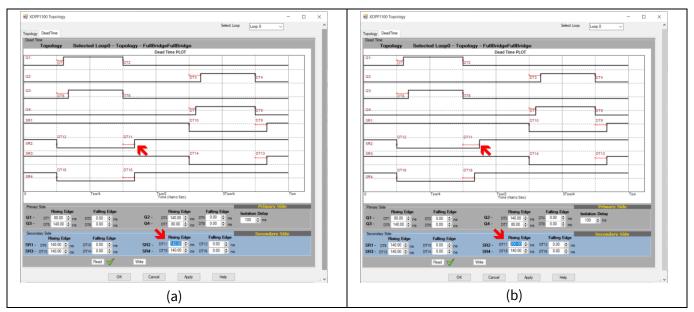

Figure 17 Device Topology (PWM mapping and topology selection) tool - a) Topology b) DeadTime

The deadtime unit in this module is ns. Changing dead time values will change switching waveforms accordingly and depict updated dead times. For example, the effect of increasing SR2 rising edge dead time (**DT11**) from 140 ns to 200 ns is shown in **Figure 18**.

# Digital power controller with PMBus

Figure 18 PWM dead time configuration - a) DT11 = 140 ns, b) DT11 = 200 ns

One of the critical factors for isolated bridge topologies is timing between the primary and the secondary opposite phases to avoid shoot-through. For this timing criteria, HW propagation delays should also be considered. As a safety measure, **Isolation Delay** reminds users to consider propagation delays between the XDPP1100 output and the gate of the primary-side switches during the configuration of the PWM rising edge of the SR switches (**Figure 19**). This is just a reminder to avoid the wrong PWM dead time configuration to avoid shoot-through, and does not have any impact on the actual PWM dead time timings. This setting only provides a warning message if dead time settings violate the **Isolation Delay** criteria. For example, if an **Isolation Delay** is considered 100 ns for the primary PWMs, GUI does not allow users to configure SR rising-edge delay less than 100 ns. GUI prompts a warning message if 100 ns criteria is violated, and does not allow the user to configure these settings (**Figure 19**).

Figure 19 PWM isolation delay

For the evaluation kit programmed by the provided board design file, generated PWM signals by the daughterboard for the power board to supply 10 A load with 12 V DC output voltage are shown in (**Figure 20**).

# **Digital power controller with PMBus**

Design configuration and evaluate XDPP1100

Figure 20 Evaluation kit PWM waveforms for 12 V DC output voltage and 10 A load current

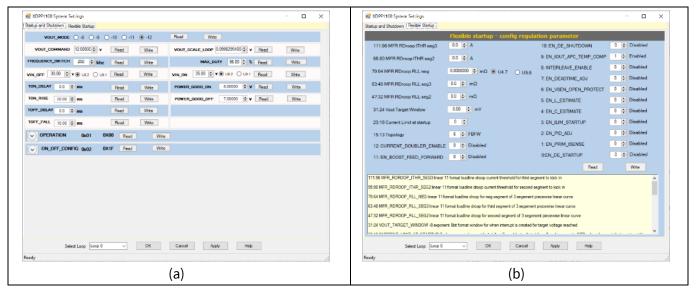

# 4.2 System settings (flexible startup and shutdown)

Users can configure the startup, shutdown, and regulation settings of XDPP1100 using the **System Settings** tool. To access this tool,

- Click the XDPP1100-Q024::i2c x10 (highlighted in yellow in Figure 21).

- Click the **Design Tools** and select **2. System Settings**

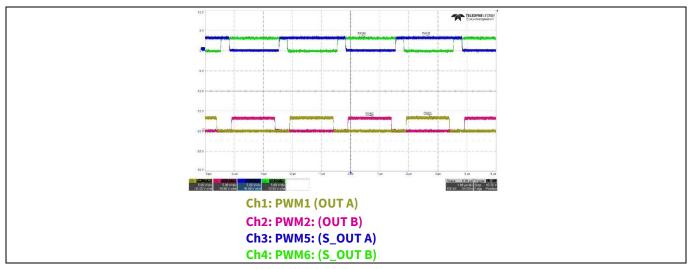

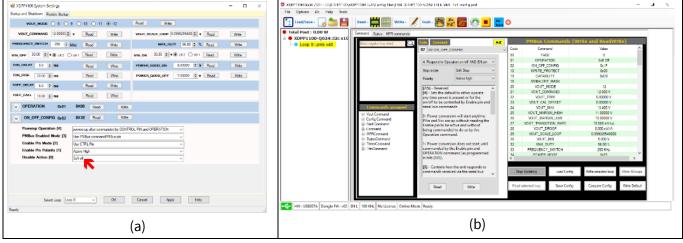

The XDPP1100 System Settings window will be opened with Startup and Shutdown and Flexible Startup tabs (Figure 22).

All settings in these tabs will be applied just after clicking on Write.

Note: Changes will be stored in RAM and must be stored into OTP once the program has been finalized.

Figure 21 System settings (flexible startup and shutdown)

# Digital power controller with PMBus

Figure 22 XDPP1100 System settings - a) startup and shutdown, b) flexible startup

# 4.2.1 Startup and shutdown tab

Various startup and shutdown features of the XDPP1100 such as soft-start time, soft-stop time, turn-on delay, turn-off delay, on/off configuration, and response to enable command can be configured in this tab (**Figure 22**). The PMBus commands in this tab are the standard PMBus commands, and their description can be found in PMBus specification documents.

The description of some PMBus commands in this tab are as follows:

- TON\_RISE command sets the time, in ms, from when the output starts to rise until the voltage has entered the regulation band.

- TOFF\_FALL sets the time, in ms, from the end of the turn-off delay time until the voltage is commanded to zero (Figure 23).

For shutting down the converter over the course of **TOFF\_DELAY**, **Write** the **Soft Off** command in the **OPERATION** PMBus command (**Figure 23**).

Figure 23 Soft stop feature

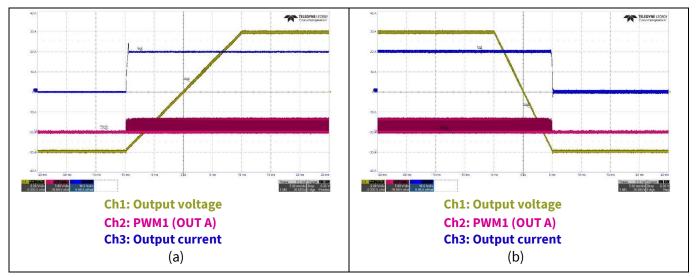

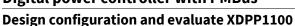

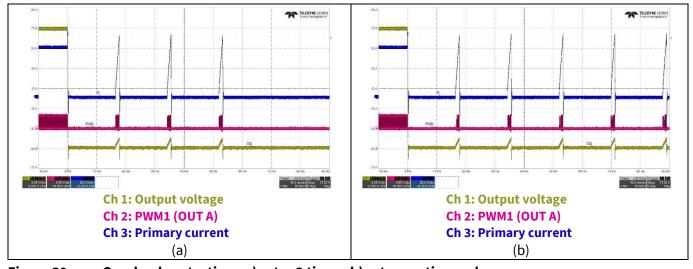

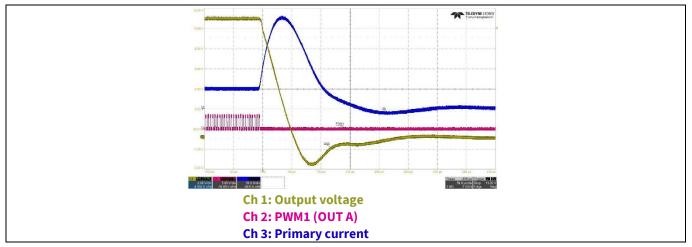

The evaluation kit turn-on response for TON\_RISE = 20 ms and turn-off response for TOFF\_FALL = 10 ms are shown in **Figure 24a** and **Figure 24b**, respectively. The load current is set to 20 A in these experiments.

# **Digital power controller with PMBus**

#### Design configuration and evaluate XDPP1100

Figure 24 Evaluation kit soft start and soft stop waveforms at 20 A load - a) TON\_RISE = 20 ms, b)

TOFF\_FALL = 10 ms

- TON\_DELAY command sets the time, in ms, from when a start condition is received (as programmed by the ON\_OFF\_CONFIG command) until the output voltage starts to rise.

- TOFF\_DELAY command sets the time, in ms, from when a stop condition is received (as programmed by the ON\_OFF\_CONFIG command) until the unit stops transferring energy to the output (Figure 25). Write the Soft Stop option for the Stop mode in the ON\_OFF\_CONFIG PMBus (Code 02) command to take advantage of TOFF\_DELAY for soft shutting down (Figure 25).

The evaluation kit turn-on response for TON\_DELAY = 5 ms, and turn-off response for TOFF\_DELAY = 5 ms are shown in **Figure 26a** and **Figure 26b**, respectively. The load current is set to 20 A in these experiments.

Figure 25 TOFF\_DELAY feature

# Digital power controller with PMBus

Figure 26 Evaluation kit turn-on and -off delays waveforms at 20 A load - a) TON\_DELAY = 5 ms, b) TOFF\_DELAY = 5 ms

#### 4.2.2 Flexible startup

Advance startup features of the XDPP1100, such as multi-segment droop, and some FW features such as current sense (CS) temperature compensation and diode emulation startup can be configured in this tab (Figure 22). The PMBus commands in this tab are the Infineon-specified PMBus commands, and their description can be found in the XDPP1100 application note (link to download)

This evaluation board uses PCB trace as a shunt resistor to measure the output current. To achieve better current measurement accuracy over the wide temperature range, temperature compensation of the output current is enabled. To do so, EN IOUT APC TEMP COMP is set to 1 in Flexible Startup window (Figure 22). Temperature coefficient is set to 0.0039 internally for the copper.

#### 4.3 PID - bode plot (Kp, Ki, Kd gain tuning and loop stability (gain margin and phase margin))

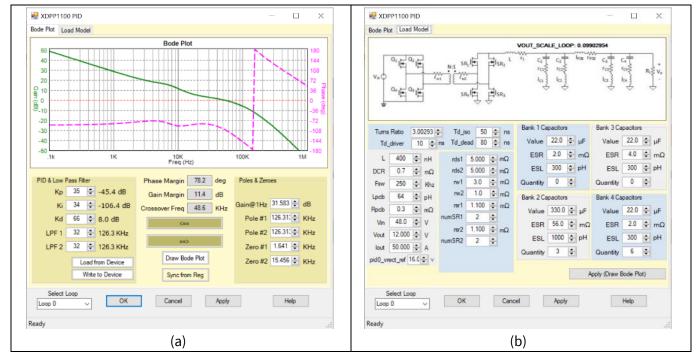

The XDPP1100 is equipped with a Type-III compensator for closed-loop control of power converters. Users can design and configure the PID compensator settings of the control loop(s) of XDPP1100 using this tool. It is also equipped with a simulation tool to predict the bode plot of the system based on power converter topology, load model, and PID parameters. To access this tool:

- Click the XDPP1100-Q024::i2c x10 (highlighted in yellow in Figure 27).

- Click **Design Tools** and select **3. PID Bode Plot.**

The XDPP1100 PID window will be opened with Bode Plot and Load Model tabs (Figure 28).

#### 4.3.1 **Bode plot tab**

This tab provides an interactive closed-loop bode plot considering detailed parameters of the converter and load, parasitic, and compensator values. Users can easily and precisely tune the controller based on desired poles and zeroes locations, phase/gain margins, or PID cut-off frequencies.

#### **Digital power controller with PMBus**

Design configuration and evaluate XDPP1100

# 4.3.2 Load model tab

In this tab, users can enter a detailed model of the converter and load, including parasitic, transformer leakages, switching deadtimes, etc. These values will be used in the **Bode Plot** tab to design and set up desired closed-loop system.

A detailed explanation of this tool and PID compensator is provided in the **XDPP1100 application note** (link to download).

Figure 27 PID - bode plot (K<sub>p</sub>, K<sub>i</sub>, K<sub>d</sub> Gain tuning and loop stability (gain margin and phase margin))

Figure 28 PID - bode plot - a) bode plot, b) load model

Some key parameters of the system listed in the load model tab are explained in Table 3.

# Digital power controller with PMBus

Table 3 Load model parameters

| Parameter     | Meaning                                                                                         | Parameter | Meaning                                        |

|---------------|-------------------------------------------------------------------------------------------------|-----------|------------------------------------------------|

| Turns ratio   | Transformer turns ratio Np:Ns<br>(automatically computed by GUI based<br>on PMBus command 0xCE) | Rds1      | R <sub>DSON</sub> of primary switch 1          |

| Td_iso        | Propagation delay of isolator                                                                   | Rds2      | R <sub>DSON</sub> of primary switch 2          |

| Td_driver     | Propagation delay of primary gate driver                                                        | rw1       | Transformer primary winding DCR                |

| Td_dead       | Primary PWM dead-time Td_rise                                                                   | rw2       | Transformer secondary winding DCR              |

| L             | Output inductor                                                                                 | rsr1      | R <sub>DSON</sub> of secondary SR1 switch      |

| DCR           | Output inductor DCR                                                                             | numSR1    | Number of SR1 switch in parallel               |

| Fsw           | Switching frequency                                                                             | rsr2      | R <sub>DSON</sub> of secondary SR2 switch      |

| Lpcb          | PCB parasitic inductance                                                                        | numSR2    | Number of SR2 switch in parallel               |

| Rpcb          | PCB parasitic resistance                                                                        | ESR       | Output capacitor ESR                           |

|               |                                                                                                 | ESL       | Output capacitor ESL                           |

| pid_vrect_ref | Nominal V <sub>IN</sub> divided by turns ratio                                                  | Quantity  | Output capacitor quantity (number in parallel) |

System parameters of the evaluation kit are set in its Config file as Figure 28b. In this case, the nominal input voltage is  $V_{IN} = 48 \text{ V}$ , and turns ratio is 3. Hence, **pid0\_vrect\_ref** = 48 V / 3 = 16 V.

In the **Bode Plot** tab (Figure 28a), Kp, Ki, and Kd can be tuned to achieve desired gain and phase margin. This tab provides an automatic tool to drive PID gains by first locating poles and zeroes at desired frequencies and then clicking . Also, after adjusting PID parameters, clicking on will show the location of poles and zeroes accordingly. In general, two zeroes (Zero #1 and Zero #2) can be placed at the double-pole of the output LC filter, and Pole #1 can be placed at half of the switching frequency.

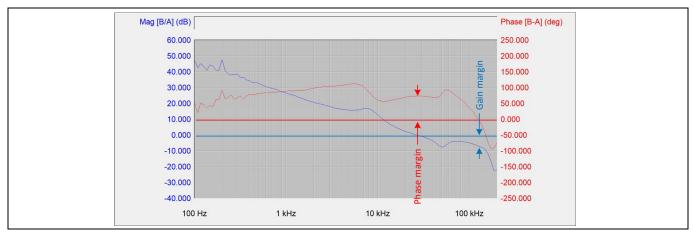

The predicted bode plot and stability of the closed-loop system can be validated experimentally by using a loop analyzer. To connect a loop analyzer to the evaluation kit: 1) replace R96 from  $0 \Omega$  to  $30 \Omega$  on the power board, 2) inject the noise on TP 27 (bode) with respect to TP 15 ( $V_{OUT}$ ) (refer to schematic **Figure 63**), 3) connect the output channel and input channel of the loop analyzer to TP 15 (Vout) and TP 27 (bode), respectively. An example of an experimental bode plot measured using an AP200 loop analyzer is shown in Figure 29.

Experimental bode plot (phase margin = 75°, gain margin = 9 dB, crossover frequency = 28 Figure 29 kHz)

# Digital power controller with PMBus

# Design configuration and evaluate XDPP1100

For the evaluation kit, load-transient responses of the closed-loop system equipped with the tuned compensator are shown in **Figure 30**.

Figure 30 Load-transient response at V<sub>IN</sub> = 48 V - a) load step: 5 percent ↔ 50 percent, b) load step: 50 percent ↔ 100 percent

# 4.4 Faults and protection (fault responses and limits)

Users can configure fault thresholds and set up protection responses of XDPP1100 to various faults (voltage, current, temperature, etc.) in the system using this tool. To access this tool:

- Click on XDPP1100-Q024::i2c x10 (highlighted in yellow in Figure 31).

- Click on **Design Tools** and select **4. Faults and Protection**

The XDPP1100 Fault Protections window will be opened with Protections, Fault Configuration, Common Faults, and Pmbus Command protections tabs (Figure 32).

Figure 31 Faults and protection (fault responses and limits)

# Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

Figure 32 XDPP1100 fault protections window with Protections, Fault Configuration, Common Faults, and Pmbus Command protections tabs

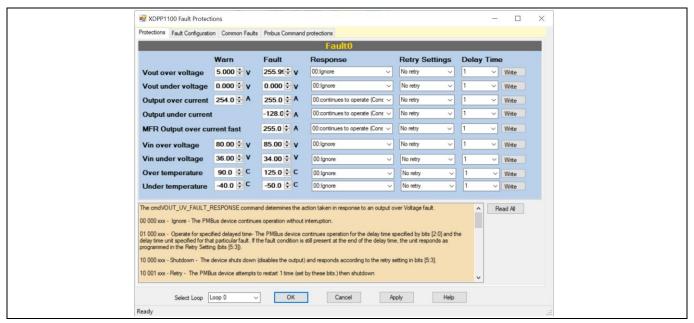

# 4.4.1 Protections tab

This tab configures the warning threshold, fault threshold, fault response behavior, retry settings, and delay time of the fault. All settings in these tabs will be applied just after clicking on **Write**.

Note: Changes will be stored in RAM and stored into OTP once the program has been finalized.

The XDPP1100 uses a warning threshold as a hysteresis mechanism for proper response to system faults. Setting fault and warning threshold to unequal values with correct direction is necessary for proper responses to the faults. For example,  $V_{\text{OUT}}$  overvoltage fault threshold must be higher than the overvoltage warning threshold. On the other hand, the undervoltage fault threshold must be lower than undervoltage warning threshold.

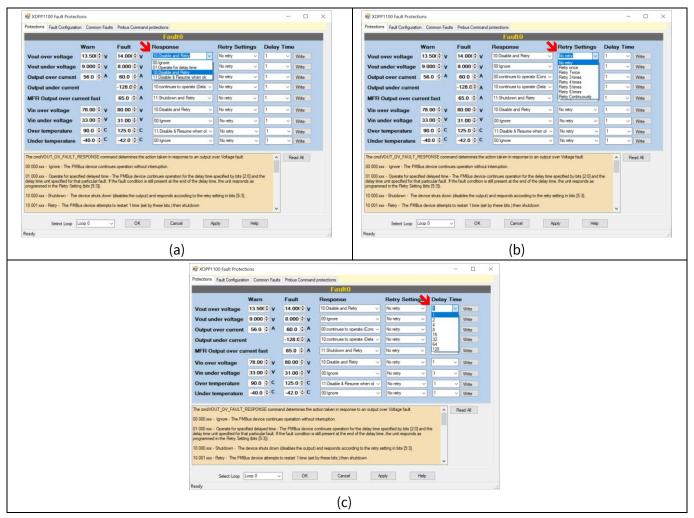

For each of the faults, desired response (**Figure 33a**), the number of the retry after fault response (**Figure 33b**), and the delay time to retry after fault detection (**Figure 33c**) can be set from their dropdown menu.

# **Digital power controller with PMBus**

#### Design configuration and evaluate XDPP1100

Figure 33 Protections tab; a) select response behavior to faults, b) select number of retry after a fault, c) select delay time for retry after response to a fault

Fault **Delay Time** works together with **Fault\_Delay\_Unit** configurable by **FW\_CONFIG\_FAULTS** (Code C8) PMBus command at the PMBus page shown in **Figure 34** (not in this tool). The result defines the fault operation's delay and retries delay between consecutive retries. This delay equals to (**Fault\_Delay\_Time** × **Fault\_Delay\_Unit**). For example, if the **Response** for **Over temperature** is programmed to **01: Operate for delay time**, **Delay Time** is set to **64**, and **Temperature\_Delay\_Unit** is set to **4ms**, the actual delay time is 64 × 4 ms = 256 ms after detecting overtemperature fault. With this setting, XDPP1100 will let the converter operate for 256 ms before shutting it down. The maximum delay time supported by XDPP1100 is 128 × 256 ms = 32.768 sec.

Note: The Delay\_Unit for the input current fault is the same as the Vin\_Delay\_Unit.

# **Digital power controller with PMBus**

#### Design configuration and evaluate XDPP1100

Figure 34 Setting Fault\_Delay\_Unit(s) in FW\_CONFIG\_FAULTS (Code C8) PMBus command

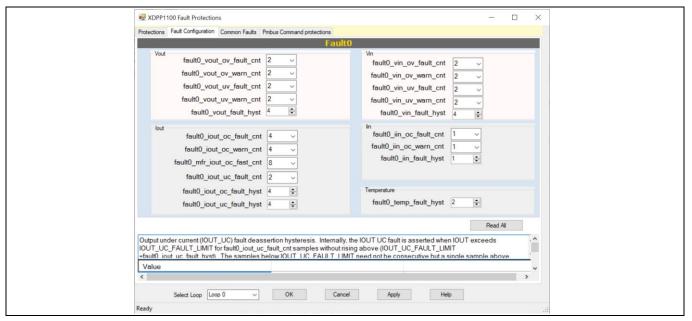

# 4.4.2 Fault Configuration tab

To avoid false fault triggering, XDPP1100 can be programmed to assert a fault/warning after the occurrence of a certain number of consecutive faults (fault count). This feature can be configured in the **Fault Configuration** tab (**Figure 35**).

Note:

Setting a higher fault count reduces sensitivity to a fault and delays proper response. Configuring the correct number is essential to avoid false fault triggering while maintaining an acceptable level of sensitivity to avoid damage to the system.

In this tab, fault hysteresis registers (**fault\_hyst**) set the HW hysteresis for the inputs to the fault comparators, which provides clean data for processing in the FW. It is worth mentioning that this setting is different from the FW hysteresis explained in **Section 4.4.1**. The HW hysteresis should be set higher than ripples of signals to avoid overflowing the processor due to oscillation of the output of the fault comparator.

Note:

Changes in this tab are immediately applied upon making the drop-down selection. Changes will be stored in RAM and stored into OTP once the program has been finalized.

Hovering the cursor over each register name will give a more detailed its description.

# Digital power controller with PMBus

# Design configuration and evaluate XDPP1100

Figure 35 Fault Configuration tab

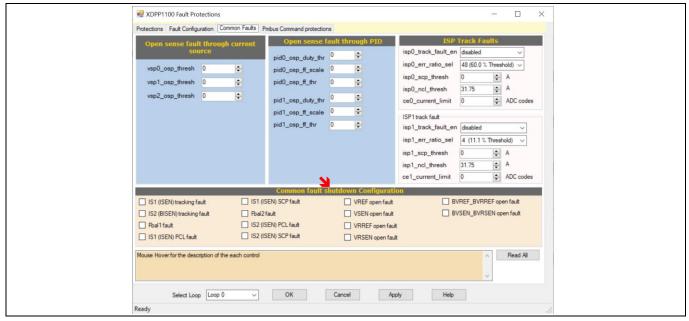

#### 4.4.3 Common Faults tab

The XDPP1100 features a number of unique fault protections such as loop open sense fault, short-circuit protection, positive and negative cycle-by-cycle current limit, and flux balancing fault. These fault protections are grouped as a common faults in the **Common Faults** tab (**Figure 36**). The response to a common fault can be set to either ignore or shutdown. To set the shutdown response of a common fault, check the box of the associated fault in the **Common fault shutdown Configuration** section (**Figure 36**).

Note: Changes in this tab are immediately applied upon making the drop-down selection. Changes will be stored in RAM and must be stored into OTP once the program has been finalized.

Figure 36 Common Faults tab

# Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

The **ispX\_scp\_thresh** defines the short circuit protection (SCP) threshold. It should be set to the highest among all over-current protection (OCP) thresholds because it requires only a single sample (at the 25 MHz ADC sample rate) above the threshold to respond and shut down the system. Setting this threshold to 0 disables the SCP fault detection. To enable SCP shutdown, check the "**IS1** (**ISEN**) **SCP fault**" box in the **Common fault shutdown Configuration** section (**Figure 36**).

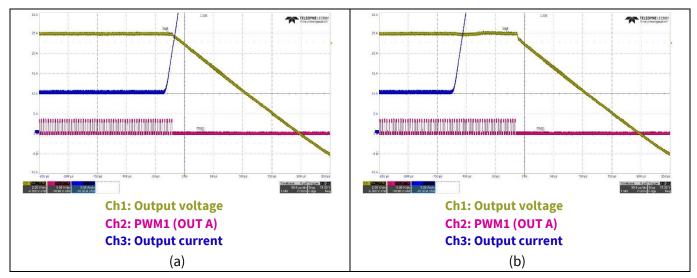

**Figure 37** demonstrates differences between responses to SCP and OC using the evaluation kit. The SCP fault threshold (**ispX\_scp\_thresh**) is set to 22 A. For the OCP settings, the **MFR\_IOUT\_OC\_FAST\_FAULT\_LIMIT** (Code D1) PMBus command is set to 20 A, and the **fault0\_mfr\_iout\_oc\_fast\_cnt** in the **Fault Configuration** (**Figure 35**) tab is set to 8 to have nine counts. The OC\_FAST fault count block has one switching cycle latency; thus, the shutdown happens after 10 switching cycles. Both SCP and OCP fault responses are set to shut down.

Figure 37 Responses to SCP and OCP (at 48 V input, 12 V output)- a) shutdown by SCP, which responded in one switching cycle, b) shutdown by MFR\_IOUT\_OC\_FAST, which responded after 10 switching cycles

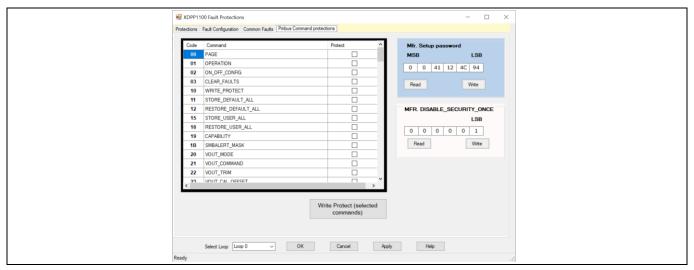

# 4.4.4 Pmbus Command protections tab

In this tab, password protection can be activated and set for the intended PMBus command to protect and prevent unauthorized modification of a selected PMBus command.

The **Pmbus Command protections** tab allows users to:

- Check if the password is set by reading MFR\_DISABLE\_SECURITY\_ONCE.

- Write a new password by writing into Mfr. SETUP password if the MFR\_DISABLE\_SECURITY\_ONCE read 00 00 00 00 00

- Turn off the security by writing the password to MFR\_DISABLE\_SECURITY\_ONCE if the MFR\_DISABLE\_SECURITY\_ONCE read 00 00 00 00 01.

- Select the PMBus that need to be protected.

- Set MFR\_SECURITY\_BIT\_MASK by clicking Write Protect (selected commands) button.

If one command is selected for **Write Protect (selected commands)** and the security is activated, rewriting of this command will be prohibited, and **STATUS\_CML** command reports Invalid/Unsupported data.

Please refer to the **Faults Protection** section of the XDPP1100 application note (**link to download**) for a detailed explanation.

# Digital power controller with PMBus

Design configuration and evaluate XDPP1100

Figure 38 Pmbus Command protections tab

# 4.4.5 Overcurrent and short-circuit protection experimental results

Experimental results of the evaluation kit for the overload protection with different retry settings and the SCP waveforms are presented in **Figure 39** and **Figure 40**, respectively. The parameters used in this test are  $IOUT\_OC\_FAULT\_LIMIT = 60 \text{ A}$ ,  $MFR\_IOUT\_OC\_FAST\_FAULT\_LIMIT = 65 \text{ A}$ ,  $fault0\_iout\_oc\_fault\_cnt = 4$ ,  $fault0\_mfr\_iout\_oc\_fast\_cnt = 8$ , and  $tlm0\_kfp\_iout = 24$ . In all cases, the converter operates during normal operation condition with  $V_{IN} = 48 \text{ V}$ , Vout = 12 V, and  $I_{OUT} = 50 \text{ A}$ .

Figure 39 Overload protection - a) retry 3 times, b) retry continuously

# Digital power controller with PMBus

# Design configuration and evaluate XDPP1100

Figure 40 **Short-circuit protection**

#### 4.5 Basic configuration (V<sub>IN</sub> telemetry, I<sub>OUT</sub>, I<sub>IN</sub> telemetry)

Using this tool, users can program the basic configurations of the PWM ramp and telemetry-related registers of XDPP1100. To access this tool:

- Click on **XDPP1100-Q024::i2c x10** (highlighted in yellow in **Figure 41**).

- Click on **Design Tools** and select **5. Basic Configuration.**

The Basic Configuration window will be opened with Output current sense, Input current sense, Vin **Telemetry**, **PWM/ramp**, and **Telemetry** tabs (**Figure 42**).

Note:

Changes in this tab are immediately applied on making the down selection. All changes are stored into RAM of the IC and must be stored to OTP once the changes are finalized.

Please refer to the Input voltage sensing and feed-forward and Current Sense sections of the XDPP1100 application note (link to download) for a detailed explanation.

Figure 41 Basic Configuration (V<sub>IN</sub> telemetry, I<sub>OUT</sub>, I<sub>IN</sub> telemetry)

#### Digital power controller with PMBus

Design configuration and evaluate XDPP1100

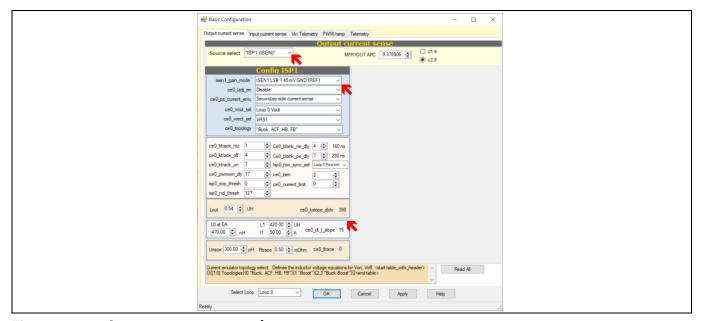

#### 4.5.1 Output current sense tab

In the evaluation kit, the output current is sensed by the current ADC ISEN/IREF. So, the Source select in this tab should be chosen as ISP1 (ISEN) (Figure 42).

PMBus command MFR\_IOUT\_APC (Code EA) configures the output CS gain. MFR\_IOUT\_APC is equal to ISEN\_LSB/(Rsns × Gamp\_Rsns) where ISEN\_LSB is defined by the isen\_gain\_mode (Figure 42), which can be set as 100 µV or 1.45 mV, **Rsns** is the current sense resistor value, and **G**<sub>amp</sub> <sub>Rsns</sub> is the amplification gain after the Rsns.

For this evaluation board, ISEN\_LSB is chosen as 1.45 mV LSB by setting isen\_gain\_mode to ISEN1 LSB 1.45mV GND IREF1 (Figure 42). As an external op-amp is used on the board, the Rsns is the sense resistance multiplied by the op-amp gain. For **Rsns**, the CS shunt is implemented by PCB copper, which has a resistance of  $0.2~\text{m}\Omega$  at room temperature, and  $G_{amp\_Rsns}$  is 20. Hence, MFR\_IOUT\_APC = 1.45 mV /  $(0.2~\text{m}\Omega \times 20)$  = 0.36 A.

Also, the design tool provides a calculation of the slope of the current estimator (ce\_kslope\_didv) based on the output inductor L<sub>OUT</sub> value (Figure 42). Please refer to XDPP1100 application note (link to download) for more information on the current estimator module.

Figure 42 Output current sense tab

For more accurate current telemetry, on board trimming is required to correct the error of gain and offset from board to board. The evaluation board doesn't perform the trimming. User could trim the MFR\_IOUT\_APC and **IOUT\_CAL\_OFFSET** to achieve desired accuracy.

A detailed explanation of the CS registers can be found in Table 16 of XDDP1100 technical reference manual.

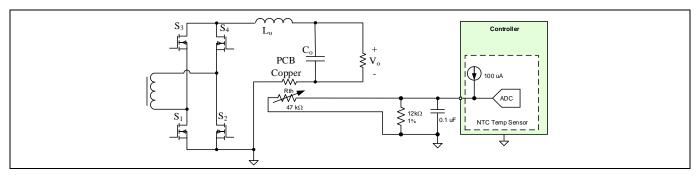

#### 4.5.1.1 **Temperature sense**

XDPP1100-Q024 supports one external and one internal temperature measurement for precise measurements and protection. An optimized look-up table for the external temperature sensor is in the XDPP1100's ROM for recommended 47 kΩ negative temperature coefficients (NTCs) (Murata NCP15WB473F03RC or Panasonic ERT-J0EP473J) in parallel with a 12 k $\Omega$  resistor (Figure 44). Temperature sensors is connected to **TSEN** pin. Also, users can define their customized temperature look-up table for other desired sensors (e.g. VBE temperature sense) by FW patch if another temperature sensing device is preferred.

# Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

The internal temperature sensor is within the XDPP1100 die and measures the controller's junction temperature.

Figure 43 NTC temperature sensing circuit

On the power board of the evaluation kit, the temperature sensors RT1 and RT2 are respectively for the shunt resistance and synchronous FET temperature sensing techniques. As PCB copper trace is used as the current sensor on this board, RT1 temperature is fed back to the processor to compensate for the temperature drift of the current sensor.

Temperature sensors can be configured through the PMBus command MFR\_SELECT\_TEMPERATURE\_SENSOR (Code DC) (Figure 44). Please note that only Read\_Temperature\_1 can be set as the current source's source of temperature drift compensation. Hence, select 1: tempa tempi as the source of temperature reading (Read\_Tempreature\_1\_Read\_Tempreature\_2).

Figure 44 Configure temperature sensors through the PMBus command MFR\_SELECT\_TEMPERATURE\_SENSOR (Code DC)

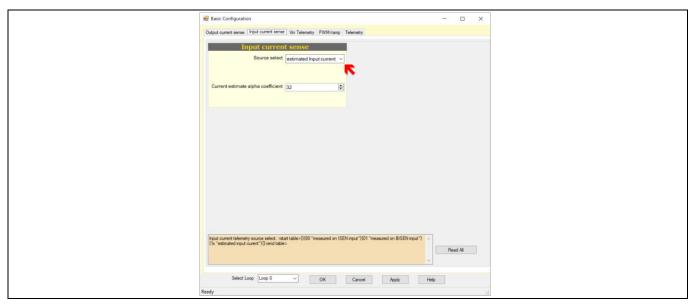

# 4.5.2 Input current sense tab

The XDPP1100-Q024 has one precise CS ADC. In the current configuration of the evaluation kit, this CS ADC is dedicated to measuring the output current. And for the input current, its value is estimated based on the measured  $V_{\text{IN}}$ ,  $V_{\text{OUT}}$ , and  $I_{\text{OUT}}$ . In the **Input current sense** tab, the **estimated Input current** is chosen at the **Source select** as shown in **Figure 45**. The current estimate alpha coefficient defines the relative contributions of  $V_{\text{OUT}} / V_{\text{IN}}$  and duty cycle in the computing the input current estimated value.

# **Digital power controller with PMBus**

# Design configuration and evaluate XDPP1100

Figure 45 Input current sense tab

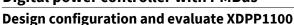

# 4.5.3 Vin Telemetry tab

The XDPP1100 offers a wide selection of sources for the input voltage measurement (**Figure 46**) which are listed and explained in **Table 4**.

Table 4 tlm\_vin\_src\_sel configuration table

| Value | Input voltage source                                                                                                                |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | <b>VRSEN</b> . Secondary V <sub>RECT</sub> sense, <b>vrs_init</b> prior to start-up                                                 |

| 1     | <b>BVSEN_BVRSEN</b> . Secondary V <sub>RECT</sub> sense, <b>vrs_init</b> prior to start-up                                          |

| 2     | <b>Loop 0 V<sub>OUT</sub></b> . Select on loop 1 when loop 1 V <sub>IN</sub> provided by loop 0 V <sub>OUT</sub> (e.g., post-buck). |

| 3     | <b>TS ADC V</b> <sub>IN</sub> . non-pulsed/primary $V_{IN}$ sense via telemetry ADC (PRISEN)                                        |

| 4     | tlm_vin_force. Forced V <sub>IN</sub> via FW (e.g., FW over-ride of HW computation)                                                 |

| 5     | <b>VRSEN</b> . Secondary $V_{RECT}$ sense, <b>0 V</b> prior to start-up. Select on loop 1 when sharing loop 0 $V_{RECT}$ sense      |

| 6     | <b>VRSEN</b> . Non-pulsed/primary V <sub>IN</sub> sense                                                                             |

| 7     | BVSEN_BVRSEN. Non-pulsed/primary V <sub>IN</sub> sense                                                                              |

The evaluation kit has two input voltage sense circuits. Users can select each from the Vin Telemetry tab (**Figure 46**);

- 1. Setting tlm0\_vin\_src\_sel to VRS1 (VRSEN, vrs\_init prior to startup) will configure the XDPP1100 to measure V<sub>IN</sub> from the secondary side of the main transformer through the VRSEN pin. It works when the main power supply is in switching.

- 2. Setting tlm0\_vin\_src\_sel to TS ADC Vin will configure the XDPP1100 to measure V<sub>IN</sub> through the auxiliary power supply via the PRISEN pin. It works as long as the auxiliary power is in the regulation.

Note: In general, selecting **VRSEN** is preferred for higher accuracy, faster feed-forward response, and faster fault protection.

# Digital power controller with PMBus

Figure 46 Vin Telemetry tab

# 4.5.3.1 Setting tlm0\_vin\_src\_sel to VRS1 (VRSEN, vrs\_init prior to startup)

For measuring the input voltage from the rectified voltage ( $V_{RECT}$ ) at the secondary side of the isolated transformer ( $V_{RECT}$ ), **VRS1 (VRSEN, vrs\_init prior to startup)** has to be selected from the **tlm0\_vin\_src\_sel** drop-down list as the input voltage source. In this case, the  $V_{RECT}$  waveform and the associated registers will be shown in the **Vin Telemetry** tab.

A detailed explanation of the VRSEN registers can be found in Table 2 and 61 of the **XDDP1100 technical reference manual**. An initial voltage for VS1 (VRSEN) when operating in VRS mode (**vrs\_voltage\_init**) will be calculated automatically by the design tool based on the following equations:

1. For the FB and the active clamped forward (ACF) topologies:

$$vrs\_voltage\_init = \frac{Vin\_init(V)}{20mV} \times MFR\_VRECT\_SCALE \times MFR\_TRANSFORMER\_SCALE$$

2. For the half-bridge (HB) topology:

User Guide

$$vrs\_voltage\_init = \frac{Vin\_init(V)/2}{20mV} \times MFR\_VRECT\_SCALE \times MFR\_TRANSFORMER\_SCALE$$

For instance, in the FB topology of the evaluation kit with Vin = 48 V, we have:

$$vrs\_voltage\_init = \frac{48V}{20mV} \times 0.073 \times 0.333 = 58$$

# 4.5.3.2 Setting tlm0\_vin\_src\_sel to TS ADC V<sub>IN</sub> (PRISEN)

To measure the input voltage through the auxiliary power supply, **TS ADC Vin** has to be selected from the **tlm0\_vin\_src\_sel** drop-down list as the input voltage source. In this case, related **PRISEN** registers will be shown in the **Vin Telemetry** tab.

A detailed explanation of PRISEN registers can be found in Table 23 of the **XDDP1100 technical reference** manual.

36 of 59

V 1.0

#### Digital power controller with PMBus

Design configuration and evaluate XDPP1100

**vin\_pwl\_slope** and **vin\_trim** are the gain and offset of a linear relationship between the TS ADC code and actual Vin value. Users can also compensate for HW measurement errors by these two registers. For the  $V_{IN}$ , we have:

$$V_{IN} = vin_pwl_slope \times ADC + vin_trim$$

**vin\_pwl\_slope** can be calculated by the following equation:

$$vin\_pwl\_slope = \frac{1.2 \times 2^5}{PRISEN\ SCALE}$$

For example, in the evaluation kit, the resistor divider for PRISEN measurement has the ratio of 1.3 k $\Omega$ / (100 k $\Omega$  + 1.3 k $\Omega$ ) = 0.0128. Hence, **vin\_pwl\_slope** is:

$$vin\_pwl\_slope = \frac{1.2 \times 2^5}{0.0128} = 3000$$

The offset error can be compensated by the **vin\_trim** register.

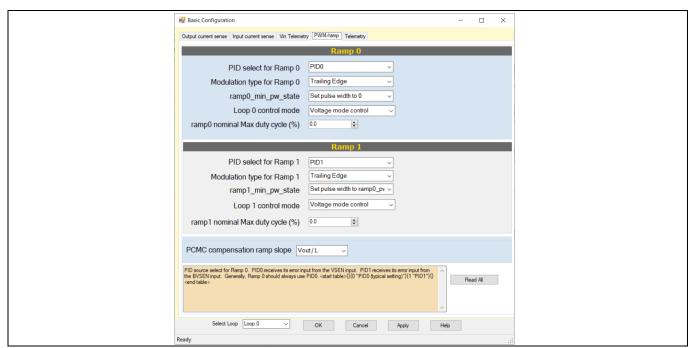

### 4.5.4 PWM/ramp tab

Users can configure PWM flavor, control mode, and maximum duty-cycle scaling for the respective loop through this tab (**Figure 47**).

Figure 47 PWM/ramp tab

A description of the registers in this tab can be found in Table 48 of the XDDP1100 technical reference manual.

### 4.5.5 Telemetry tab

Users can set the low-pass filter (LPF) coefficients of corresponding telemetry in this tab. The LPF coefficients for output current, input current, input voltage, duty-cycle, and output voltage measurements depend on the switching frequency of the power converter. On the other hand, the filter coefficients for temperature, PRISEN, IMON, and address telemetries are independent from the switching frequency.

#### Digital power controller with PMBus

**Design configuration and evaluate XDPP1100**

Figure 48 Telemetry tab

# 4.6 Advanced features (droop, burst, fast transients, feed-forward, flux balancing)

Users can program advanced features of the XDPP1100 such as feed-forward, current balancing, flux balancing, current sharing, sync in/out, droop, fast transient, and burst operation using this tool. To access this tool:

- Click on XDPP1100-Q024::i2c x10 (highlighted in yellow in Figure 49).

- Click on **Design Tools** and select **6. Advanced Features.**

The Advanced Configuration window will be opened with Feed-forward, Current balancing, Flux balancing, Current sharing, Sync In/Out, Droop, Fast Transient, and Burst tabs.

The current balancing, current sharing, sync in/out, droop, and fast transient are not the focus of this evaluation board. Please refer to the XDPP1100 application note (**link to download**) for more information on these advanced features.

#### Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

Figure 49 Advanced features (droop, burst, fast transients, feed-forward, flux balancing)

#### 4.6.1 Feed-forward tab

The XDPP1100 is equipped with a HW-based feed-forward feature to enhance the speed of control loop response compared to the linear feedback system. The XDPP1100 adjusts power-converter duty cycle based on the updated input and output voltage values upon sensing the input voltage transient. **Feed-forward** registers are listed and explained in Table 2 and 34 in the **XDPP1100 technical reference manual**.

Register **pid\_ff\_vrect\_sel** allows the user to select one of four sources for the V<sub>IN</sub> input:

- Select VS1 (VRSEN) Vrect: Senses V<sub>RECT</sub> on VRSEN inputs

- Select VS2 (BVSEN\_BVRSEN) Vrect: Senses V<sub>RECT</sub> on BVRSEN inputs

- Select **Telemetry Sense Vin**: Senses V<sub>IN</sub> on the **PRISEN** input (telemetry sense V<sub>IN</sub>)

- Select pid0\_ff\_vrect\_override: Overrides of sensed V<sub>RECT</sub> through FW

The **pid0\_ff\_vrect\_override** register value defines the feed-forward value to override V<sub>RECT</sub>. It is calculated from PMBus commands as in the follows:

$$pid0\_ff\_vrect\_override = \frac{Vin(V)}{1.25mV} \times MFR\_VRECT\_SCALE \times MFR\_TRANSFORMER\_SCALE$$

For example, in the evaluation kit, we have:

$$pid0\_ff\_vrect\_override = \frac{48V}{1.25mV} \times 0.07227 \times 0.333 = 924$$

In the evaluation kit, the provided configuration sets XDPP1100 to use the rectified voltage at the secondary side of the transformer (**VRSEN**) as the source of input voltage telemetry and feed-forward implementation. The alternative input source is using generic ADC (**PRISEN**). However, as the sample rate of the **VRSEN ADC** is considerably higher than the general-purpose ADC, selecting VRSEN as the source of the feed-forward module leads to the faster loop response.

V 1.0

#### Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

Note:

Changes in this tab are immediately applied on making the drop-down selection. All changes are stored into RAM of the IC and must be stored to OTP once the changes are finalized.

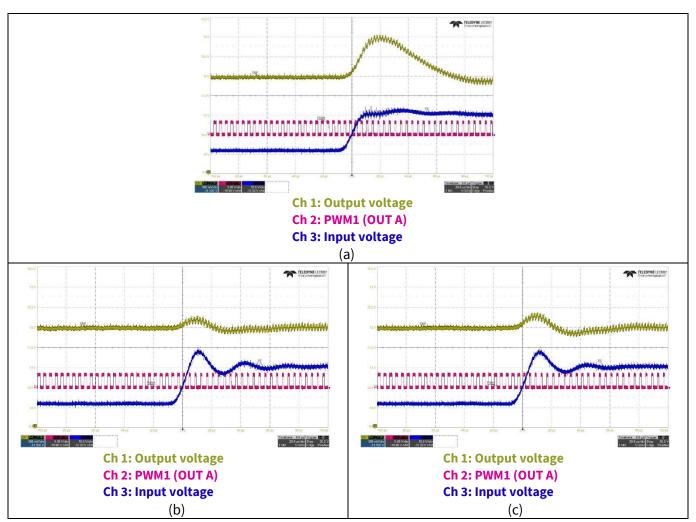

Figure 50 Feed-forward experimental results - a) feed-forward disabled by selecting pid0\_ff\_override\_sel as pid0\_ff\_override and pid0\_ff\_override = 0, b) same cycle enabled, c) same cycle disabled

## 4.6.2 Flux balancing tab

In the FB converters, timing mismatch between the gating signals can cause asymmetrical applied volt-seconds across the transformer winding from one half-cycle to its complementary half cycle. So, applied voltage will not be purely AC anymore. In this case, the excess DC voltage term across the transformer winding causes "flux-walkaway" and leads to saturation of its ferromagnetic core. To avoid this phenomenon, PWM timing must be adjusted dynamically to compensate for practical timing mismatches and prevent the transformer core from being saturated.

The XDPP1100 volt-second balancing module will ensure symmetrical volt-seconds across the transformer winding. In each duty cycle, input voltage and timings using rectified voltage ( $V_{RECT}$ ) and a high-speed edge comparator with 5 ns accuracy will be measured. Then, an error between (volt × second) of each half-cycle will be fed to a PI compensator to adjust the PWM timings and ensure flux balancing. **Flux balancing** is available just for the FB topology in voltage-mode control. This feature will be activated when register

#### Digital power controller with PMBus

Design configuration and evaluate XDPP1100

ramp0\_dutyc\_lock = 1. Flux balancing registers are listed and explained in Table 77 of the XDDP1100

technical reference manual.

For correct measurement of the VRS pulse width and flux balancing, sufficient dead time before the SR rising edge is crucial. If the SR rising edge is too close to the falling edge (i.e., insufficient dead time), the XDPP1100 VRS counter might measure VRS pulse width inaccurately and fail to do the flux balancing.

Note:

Changes in this tab are immediately applied on making the drop-down selection. All changes are stored in RAM of the IC and must be stored to OTP once the changes are finalized.

The XDPP1100 is capable of performing two different volt-second balance methods; flux (volt-seconds balance and time-only balance. For the evaluation kit, each method can be configured as follows:

- 1. To enable flux balancing using time only, set **kp\_fbal** = 4, **ki\_fbal** = 24, **vbal\_mode\_sel** = **flux balance mode** (select for FB primary), **fbal\_time\_only** = Enable and ramp0\_dutyc\_lock = checked.

- 2. To enable flux balancing using volt-second, set **kp\_fbal** = 4, **ki\_fbal** = 24, **vbal\_mode\_sel** = **flux balance mode (select for FB primary), fbal\_time\_only** = **disable** and **ramp0\_dutyc\_lock** = checked.

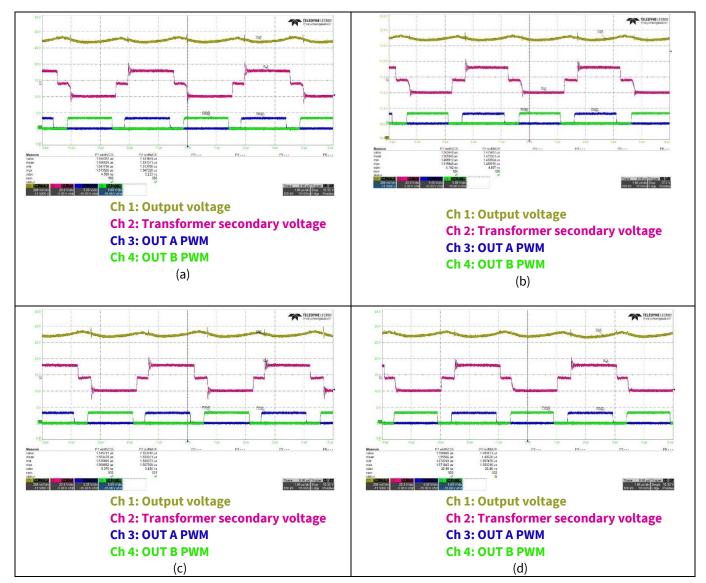

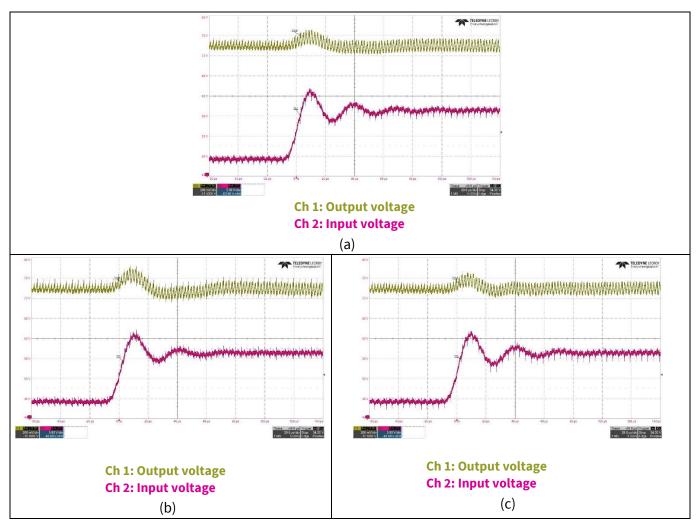

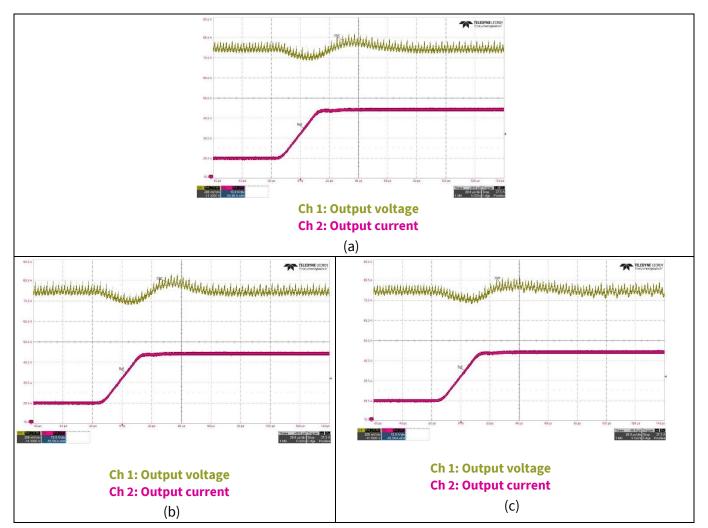

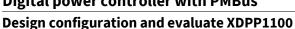

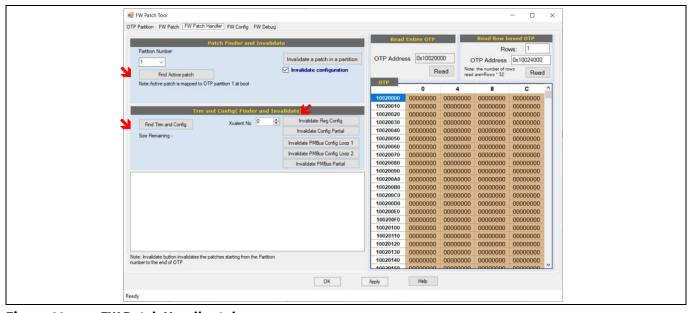

To evaluate the experimental performance of the **Flux balancing** module, 30 ns is added to one side of the primary side gate pulse (**Figure 51**) in order to create imbalanced volt-seconds. These PWM settings can be done using the PMBus command **PWM\_DEADTIME** (Code CF). Steady-state experimental results of the evaluation kit without flux balancing, with flux balancing enabled but operating in discontinuous conduction mode (DCM), with flux balancing enabled and time-only mode, and with enabled flux-balancing and volt-seconds technique, are shown in **Figure 52a to d**, respectively. As shown in **Figure 52b**, XDPP1100 disables flux-balancing under the predefined DCM threshold, because predicting the primary voltage from the transformer secondary winding is not feasible in DCM operation. Similarly, experimental results for the line transient and the load transient are shown in **Figure 53** and **Figure 54**, respectively.

Figure 51 Mismatching the gate driver signals

#### Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

Figure 52 Flux balancing steady-state result - a) ramp0\_dutyc\_lock = unchecked (flux balancing disabled), b) ramp0\_dutyc\_lock = checked and Iout = 10 A (flux balancing is disabled due to DCM), c) ramp0\_dutyc\_lock = checked and fbal\_time\_only = enable (flux balancing is disabled due to DCM), d) ramp0\_dutyc\_lock = checked and fbal\_time\_only = disable (flux balancing enabled with volt × seconds technique)

### Digital power controller with PMBus

Design configuration and evaluate XDPP1100

Figure 53 Flux balancing line transient results - a) ramp0\_dutyc\_lock = unchecked (flux balancing disabled), b) ramp0\_dutyc\_lock = checked and fbal\_time\_only = enable (flux balancing is disabled due to DCM), c) ramp0\_dutyc\_lock = checked and fbal\_time\_only = disable (flux balancing enabled with volt × seconds technique)

#### Digital power controller with PMBus

Design configuration and evaluate XDPP1100

Figure 54 Flux balancing load transient results - a) ramp0\_dutyc\_lock = unchecked (flux balancing disabled), b) ramp0\_dutyc\_lock = checked and fbal\_time\_only = enable (flux balancing is disabled due to DCM), c) ramp0\_dutyc\_lock = checked and fbal\_time\_only = disable (flux balancing enabled with volt × seconds technique)

#### 4.6.3 Burst mode tab

Burst mode is a common technique to reduce switching losses of switched-mode power-converters in the light-load operation condition. This mode of operation can be enabled by setting PMBus command **POWER\_MODE** (Code 34) to 0. By enabling this feature, XDPP1100 enters burst mode and stops switching the power converters (burst-off) when the load current falls below the burst-entry threshold. After that, when the output voltage drops to a target level (burst-on), switching will be resumed. SRs are also off during the burst mode (burst-on). Those target levels define output voltage ripple in this mode of operation. In the burst mode, PID output is frozen to its value right before entering burst mode. Thus, during the burst-on period, the converter works with a constant duty cycle. **Burst mode** registers are listed and explained in **Table 5**.

Table 5 Burst mode registers (loop0, pid 0)

| Register name | Module name | Description                                     |

|---------------|-------------|-------------------------------------------------|

| en_burst0     | pid0        | FW driven, the burst mode is enabled when PMBus |

|               |             | command POWER_MODE = 0                          |

#### Digital power controller with PMBus

#### Design configuration and evaluate XDPP1100

| Register name           | Module name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pid0_burst_mode_ith     | pid0        | Burst mode entry current threshold. When burst mode is enabled (POWER_MODE= 0), the controller will enter burst mode upon the sensed current dropping below pid0_burst_mode_ith.  Note LSB = (Qadc / 2) where Qadc is the value of MFR_IOUT_APC in A                                                                                                                                                                                                 |

| Pid0_burst_mode_err_thr | pid0        | Burst mode error voltage threshold where the error voltage is defined as (target voltage - sense voltage) at VSEN. When the controller is in burst mode (error voltage greater than pid0_burst_mode_err_thr) it will trigger the start of a new burst sequence.  Note: This threshold is always positive, indicating the controller triggers the start of a new burst sequence at or below the target voltage.  LSB = 1.25 mV. Range = 0 to 18.75 mV |