# West Bridge<sup>®</sup> Astoria<sup>™</sup> Technical Reference Manual

Document # 001-70142 Rev. \*A

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

Copyright © 2012-2015 Cypress Semiconductor Corporation. All rights reserved.

Cypress, the Cypress Logo, and West Bridge are registered trademarks and Astoria, MoBL-USB, and ReNumeration are trademarks of Cypress Semiconductor Corporation. Macintosh is a registered trademark of Apple Computer, Inc. Windows is a registered trademark of Microsoft Corporation. SmartMedia is a trademark of Toshiba Corporation. All other product or company names used in this manual may be trademarks, registered trademarks, or servicemarks of their respective owners.

Purchase of I2C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.

The information in this document is subject to change without notice and should not be construed as a commitment by Cypress. While reasonable precautions have been taken, Cypress assumes no responsibility for any errors that may appear in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Cypress. Made in the U.S.A.

#### Disclaimer

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PAR-TICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

The acceptance of this document will be construed as an acceptance of the foregoing conditions.

This manual is the West Bridge Astoria Technical Reference Manual. It gives information for these chips CYWB0216ABS CYWB0220ABS CYWB0224ABS CYWB0226ABS CYWB0320ABX CYWB0321ABX

# Contents

| 1. Contents                             |                                          | 3  |

|-----------------------------------------|------------------------------------------|----|

| 1. Introducing West Bridge <sup>®</sup> | Astoria™                                 | 9  |

| 1.1 Astoria Architectu                  | re                                       |    |

| 1.2 Top Level Block D                   | liagram                                  |    |

| 1.3 Top Level Functio                   | nal Blocks                               | 11 |

| 1.3.1 Processor                         | Interface Port (P-Port)                  |    |

| 1.3.2 USB Port (                        | U-Port)                                  | 12 |

| 1.3.3 Storage Po                        | ort (S-Port)                             | 12 |

|                                         | SD/MMC Port (S-Port)                     |    |

|                                         | CE-ATA (S-Port)                          |    |

| 1.3.3.3 (                               | GPIO[1:0]                                | 17 |

| 5                                       |                                          |    |

| •                                       | 2W                                       |    |

|                                         | dpoints                                  |    |

|                                         | ndpoints                                 |    |

| 1.6 Document History                    |                                          | 20 |

| 2. Endpoint Zero                        |                                          | 21 |

| 2.1 Control Endpoint                    | EP0                                      | 21 |

| 2.2 USB Requests                        |                                          | 23 |

|                                         |                                          |    |

|                                         | е                                        |    |

|                                         | ure                                      |    |

|                                         | ptor                                     |    |

|                                         | Get Descriptor-Device                    |    |

|                                         | Get Descriptor-Device Qualifier          |    |

|                                         | Get Descriptor-Configuration             |    |

|                                         | Get Descriptor-String                    |    |

|                                         | Get Descriptor-Other Speed Configuration |    |

|                                         | ptor                                     |    |

|                                         | Set Configuration                        |    |

|                                         | uration                                  |    |

|                                         | ce                                       | -  |

|                                         | Ce                                       | -  |

|                                         | ie                                       |    |

| Z.Z. TU SYNC FIAN                       |                                          |    |

| 3. Enumeration and ReNume               | ration™                                  | 35 |

| 3.1 | Firmw | are Loading                             | 35 |

|-----|-------|-----------------------------------------|----|

|     |       | Loading the Firmware from the Processor |    |

|     |       | Legacy Boot Mode                        |    |

|    |            | 3.1.3 Debug Boot Mode                                       |    |

|----|------------|-------------------------------------------------------------|----|

|    |            | 3.1.4 Register Configuration                                |    |

|    |            | 3.1.5 The Default USB Device                                |    |

|    |            | 3.1.6 Astoria Vendor Request for Firmware Load              |    |

|    | 3.2        | EEPROM Configuration Byte                                   | 40 |

|    | 3.3        | The RENUM Bit                                               | 41 |

|    | 3.4        | Astoria's Response to Device Requests<br>(RENUM = 0)41      |    |

|    | 3.5        | How the Firmware ReNumerates                                |    |

|    | 3.6        | Multiple ReNumerations™                                     |    |

| 4. | Interrupts |                                                             | 43 |

|    | 4.1        | SFRs                                                        | 43 |

|    | 4.2        | Interrupt Processing                                        |    |

|    |            | 4.2.1 Interrupt Masking                                     |    |

|    |            | 4.2.1.1 Interrupt Priorities                                |    |

|    |            | 4.2.2 Interrupt Sampling                                    |    |

|    |            | 4.2.3 Interrupt Latency                                     |    |

|    | 4.3        | USB-Specific Interrupts                                     |    |

|    |            | 4.3.1 Resume Interrupt                                      |    |

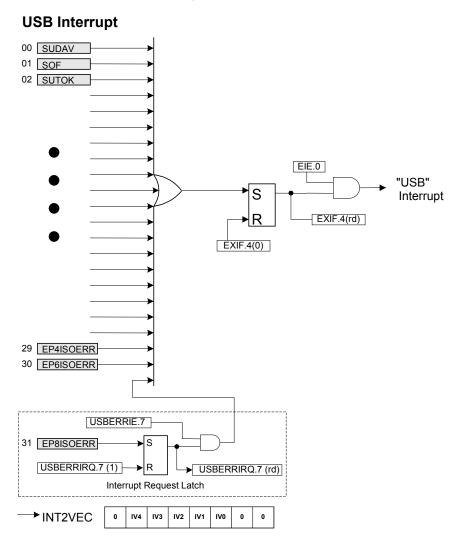

|    |            | 4.3.2 USB Interrupts                                        |    |

|    |            | 4.3.2.1 SUTOK, SUDAV Interrupts                             | 49 |

|    |            | 4.3.2.2 SOF Interrupt                                       | 49 |

|    |            | 4.3.2.3 Suspend Interrupt                                   | 49 |

|    |            | 4.3.2.4 USB RESET Interrupt                                 |    |

|    |            | 4.3.2.5 HISPEED Interrupt                                   |    |

|    |            | 4.3.2.6 EP0ACK Interrupt                                    |    |

|    |            | 4.3.2.7 Endpoint Interrupts                                 |    |

|    |            | 4.3.2.8 In-Bulk-NAK (IBN) Interrupt                         |    |

|    |            | 4.3.2.9 EPxPING Interrupt                                   |    |

|    |            | 4.3.2.10 ERRLIMIT Interrupt<br>4.3.2.11 EPxISOERR Interrupt |    |

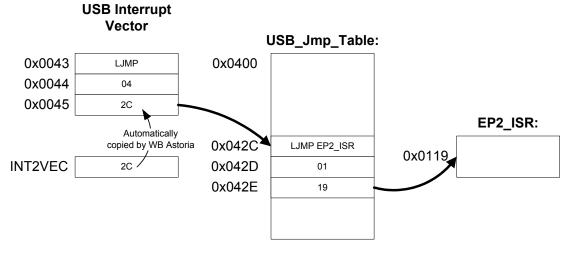

|    | 4.4        | USB-Interrupt Autovectors                                   |    |

|    | 4.4        | 4.4.1 USB Autovector Coding                                 |    |

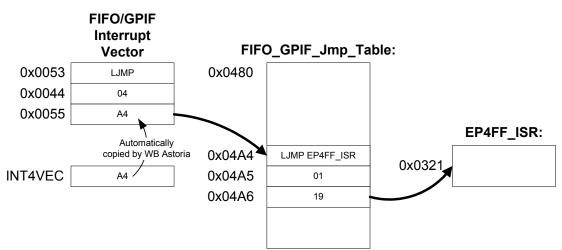

|    | 4.5        | GPIF Interrupt                                              |    |

|    | 4.6        | GPIF Interrupt Autovectors                                  |    |

|    | 4.0        | 4.6.1 GPIF Autovector Coding                                |    |

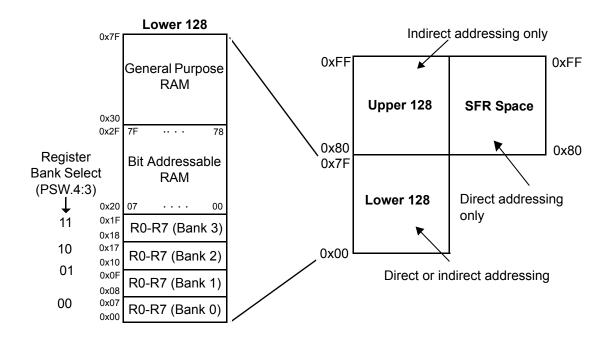

| 5. | Memory     |                                                             | 55 |

|    | 5.1        | Internal Data RAM                                           |    |

|    | 5.1        | 5.1.1 The Lower 128                                         |    |

|    |            | 5.1.2 The Upper 128                                         |    |

|    |            | 5.1.3 Special Function Register Space                       |    |

|    | 5.2        | Astoria Memory Map                                          |    |

| 6. | Power Man  | nagement                                                    | 59 |

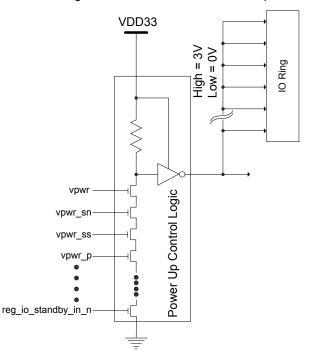

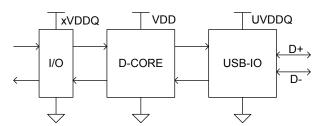

|    | 6.1        | Power Domains                                               |    |

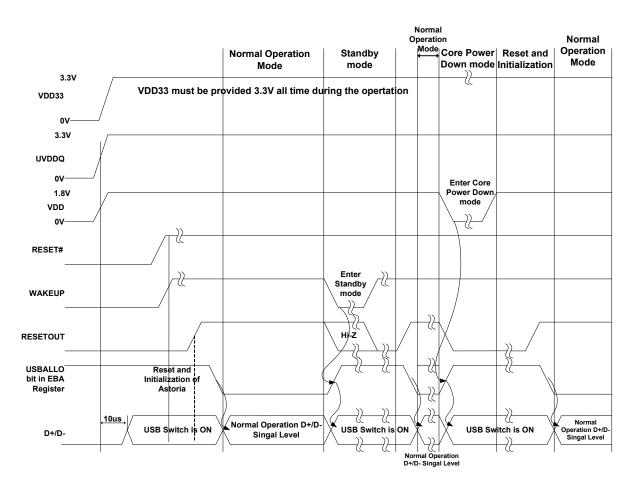

|    | 6.2        | Power Supply Sequence                                       |    |

|    | 6.3        | Power Modes                                                 |    |

|    | 0.0        | 6.3.1 Normal Mode                                           |    |

|    |            | 6.3.2 Standby Mode                                          |    |

|    |            | 6.3.3 Suspend Mode                                          |    |

|    |            |                                                             |    |

7.

8.

9.

## Contonto

|           | C                                                                                             | ontents |

|-----------|-----------------------------------------------------------------------------------------------|---------|

|           | 6.3.3.1 Wakeup                                                                                | 64      |

|           | 6.3.4 Core Power Down                                                                         |         |

| 6.4       |                                                                                               |         |

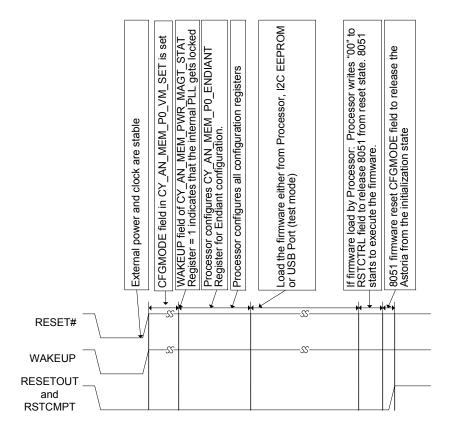

| Resets    |                                                                                               | 67      |

| 7.1       | Hard Reset                                                                                    | 67      |

| 7.2       | Reset by Register (Soft Reset)                                                                | 69      |

| 7.3       | Wakeup Mechanism                                                                              | 71      |

| 7.4       | USB Bus Reset                                                                                 | 71      |

| 7.5       | Astoria Disconnect                                                                            | 71      |

| Access to | Endpoint Buffers                                                                              | 73      |

| 8.1       | Physical And Logical Endpoints                                                                | 73      |

| 8.2       | High Speed and Full Speed Differences                                                         | 74      |

| 8.3       |                                                                                               |         |

| 8.4       | CPU Access to Astoria Endpoint Data                                                           | 76      |

| 8.5       | CPU Control of Astoria Endpoints                                                              | 77      |

|           | 8.5.1 Registers That Control EP0, EP1IN, and EP1OUT                                           | 77      |

|           | 8.5.1.1 EP0CS                                                                                 |         |

|           | 8.5.1.2 EP0BCH and EP0BCL                                                                     |         |

|           | 8.5.1.3 USBIE, USBIRQ                                                                         |         |

|           | 8.5.1.4 EP01STAT                                                                              |         |

|           | 8.5.1.5 EP10UTCS                                                                              |         |

|           | 8.5.1.6 EP10UTBC                                                                              |         |

|           | 8.5.1.7 EP1INCS                                                                               |         |

|           | 8.5.1.8 wEP1INBC                                                                              |         |

|           | 8.5.2 Registers That Control EP2, EP3, EP4, EP5, EP6, EP7, EP8 and EP9                        |         |

|           |                                                                                               |         |

|           | 8.5.2.2 EP2ISOINPKTS, EP4ISOINPKTS, EP6ISOINPKTS, EP8ISOINPKTS                                |         |

|           | 8.5.2.3 EP2CS, EP4CS, EP6CS, EP8CS<br>8.5.2.4 EP2BCH:L, EP4BCH:L, EP6BCH:L, EP8BCH:L          |         |

|           | 8.5.2.4 EP2BCH:L, EP4BCH:L, EP6BCH:L, EP8BCH:L.<br>8.5.3 Registers That Control All Endpoints |         |

|           | 8.5.3 Registers mat control All Endpoints                                                     |         |

|           | 8.5.3.2 EPIE, EPIRQ                                                                           |         |

|           | 8.5.3.3 USBERRIE, USBERRIRQ, ERRCNTLIM, CLRERRCNT                                             |         |

|           | 8.5.3.4 TOGCTL                                                                                |         |

| 8.6       | The Setup Data Pointer                                                                        |         |

| 0.0       | 8.6.1 Transfer Length                                                                         |         |

|           | 8.6.2 Accessible Memory Spaces                                                                |         |

| 8.7       |                                                                                               |         |

| Storage B | lock and TPIC                                                                                 | 85      |

| 9.1       | TPIC Registers                                                                                |         |

| 0.1       | 9.1.1 TPIC P2S SOFT RESET Register                                                            |         |

|           | 9.1.2 TPIC_P2S_CFG Register                                                                   |         |

|           | 9.1.3 TPIC_P2S_EN Register                                                                    |         |

|           | 9.1.4 TPIC_INT0_CLR Register                                                                  |         |

| 9.2       |                                                                                               |         |

|           | 9.2.1 SIB_READ_WAIT_EN Register                                                               |         |

|           | 9.2.2 SIB_NAND_CFG Register                                                                   |         |

|           | 9.2.3 SIB_MODE_CFG Register                                                                   |         |

| 9.3       |                                                                                               |         |

|          |        | 9.3.1 Slave FIFO:                                                            |      |

|----------|--------|------------------------------------------------------------------------------|------|

|          |        | 9.3.2 GPIF                                                                   | . 90 |

|          |        | 9.3.2.1 GPIF initialization                                                  | .90  |

|          | 9.4    | GPIO                                                                         | .92  |

|          | 9.5    | Reset SIB                                                                    | .92  |

|          | 9.6    | Sending Commands to the SD/MMC Card                                          |      |

| 10 Gono  | ral Dr | ogrammable Interface (GPIF)                                                  | 95   |

| IV. Gene |        | •                                                                            |      |

|          | 10.1   | GPIF Signals                                                                 |      |

|          |        | 10.1.1 Data Lines                                                            |      |

|          |        | 10.1.2 GPIF Address Lines                                                    |      |

|          |        | 10.1.3 GPIF Control Out Signals                                              |      |

|          |        | 10.1.4 Ready IN Signals                                                      |      |

|          |        | 10.1.5 Interface Clock (IFCLK)                                               |      |

|          |        | 10.1.6 GPIF Designer                                                         | .96  |

| 11. Copr | ocess  | or Interface Logic                                                           | 97   |

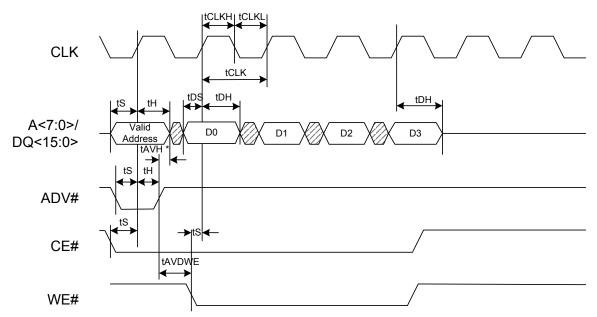

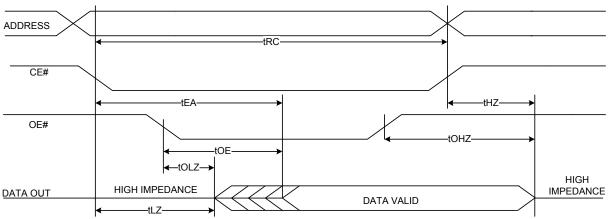

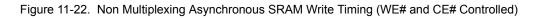

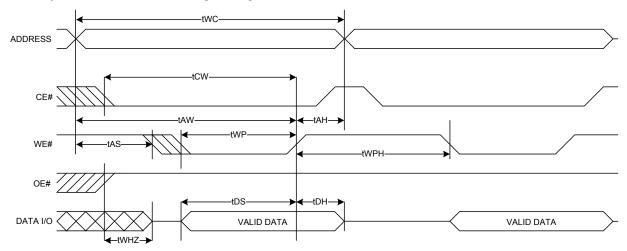

|          | 11.1   | Operational Modes                                                            | .97  |

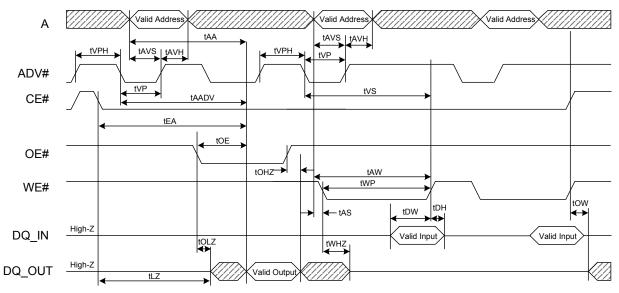

|          |        | 11.1.1 Address and Data Buses Non Multiplexing Asynchronous Pseudo CRAM Mode |      |

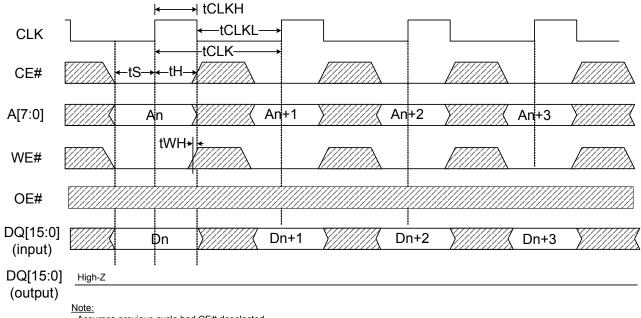

|          |        | 11.1.2 Address and Data Buses Non Multiplexing Synchronous Mode              |      |

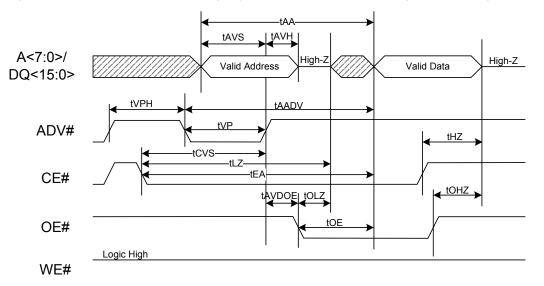

|          |        | 11.1.3 Address and Data Buses Multiplexing Asynchronous Pseudo CRAM Mode     |      |

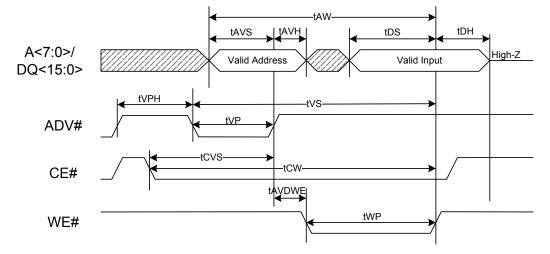

|          |        | 11.1.4 Address and Data Buses Multiplexing Synchronous Pseudo CRAM Mode      |      |

|          |        | 11.1.5 Address and Data Buses Non Multiplexing Asynchronous SRAM Mode        |      |

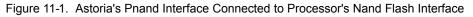

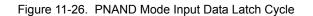

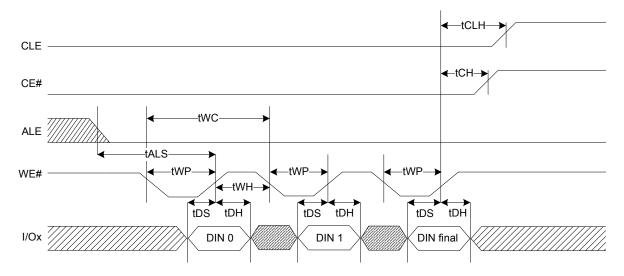

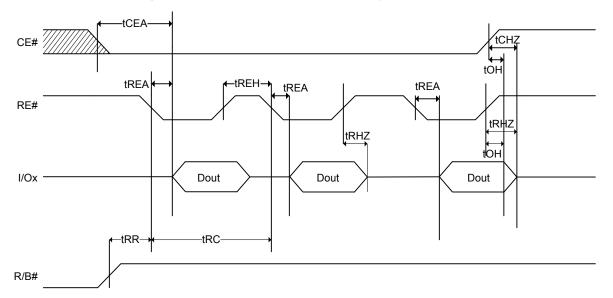

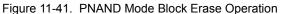

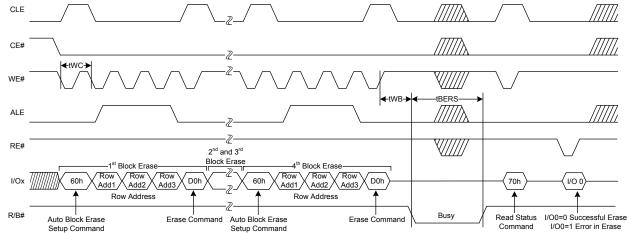

|          |        | 11.1.6 Pseudo NAND (PNAND) Mode                                              |      |

|          |        | 11.1.6.1 Pseudo NAND (PNAND) Configuration Registers Summary                 |      |

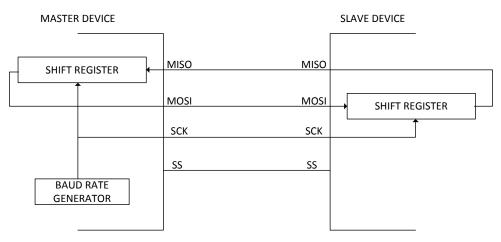

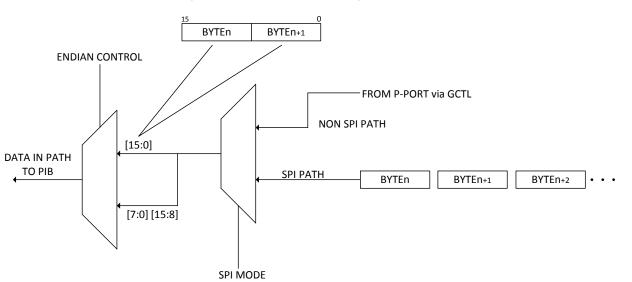

|          |        | 11.1.7 PI2C and PSPI Interface                                               |      |

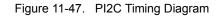

|          |        | 11.1.7.1 PI2C Mode (Available on ADM, PNAND, and PSPI Modes)                 |      |

|          |        | 11.1.7.2 PSPI Mode                                                           |      |

|          |        | 11.1.8 Switching the P-Port from Asynchronous Mode to Synchronous Mode       |      |

|          |        | 11.1.9 Port Interface Configuration Register                                 |      |

|          |        |                                                                              |      |

|          |        | 11.1.10AC Timing Parameters                                                  |      |

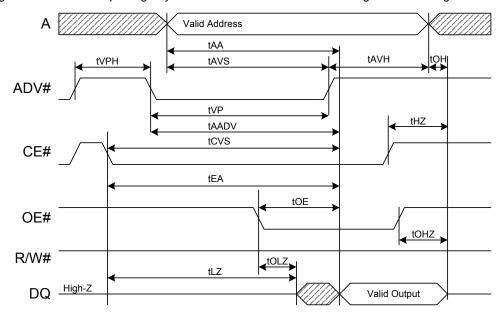

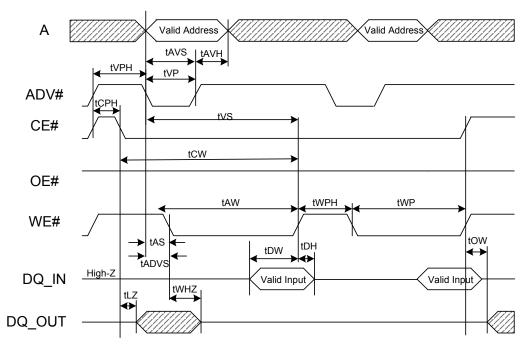

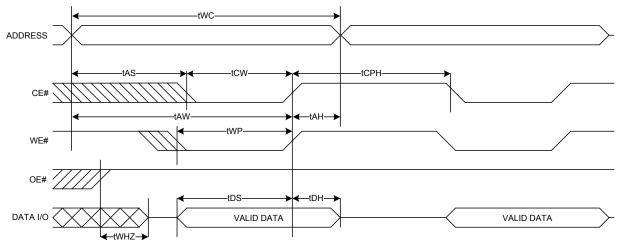

|          |        | 11.1.10.1 Pseudo CRAM Non Multiplexing Asynchronous Mode                     |      |

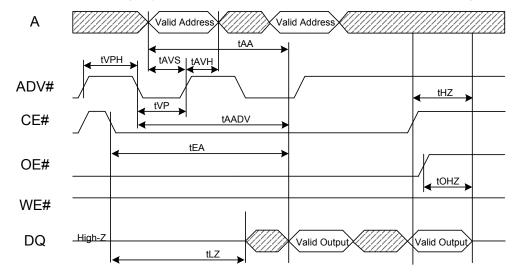

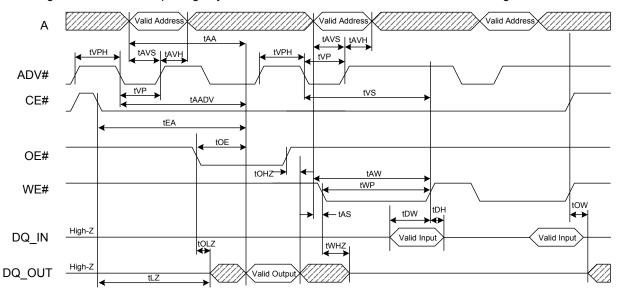

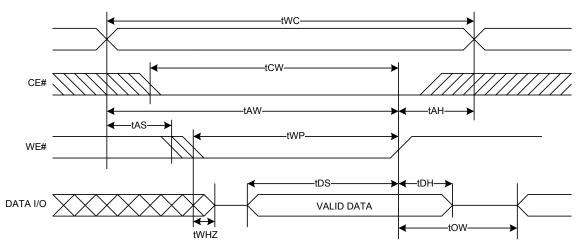

|          |        | 11.1.10.2 Pseudo CRAM Address Data Multiplexing Asynchronous Mode            |      |

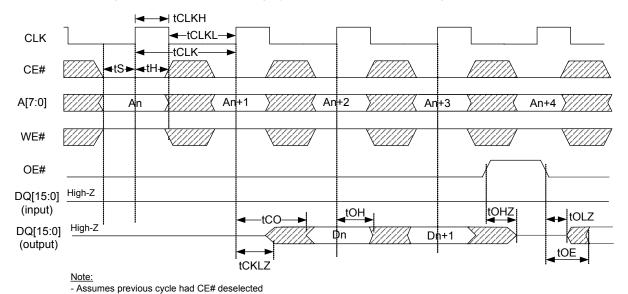

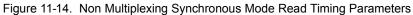

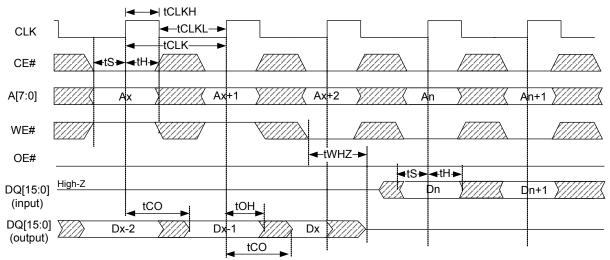

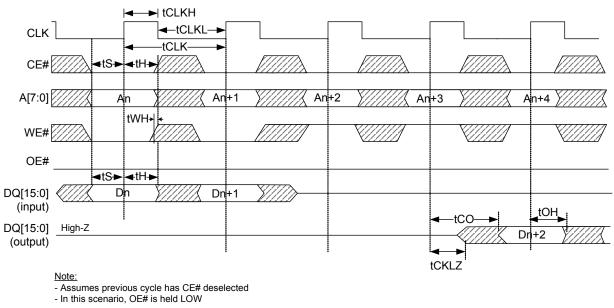

|          |        | 11.1.10.3 Non Multiplexing Synchronous Mode                                  |      |

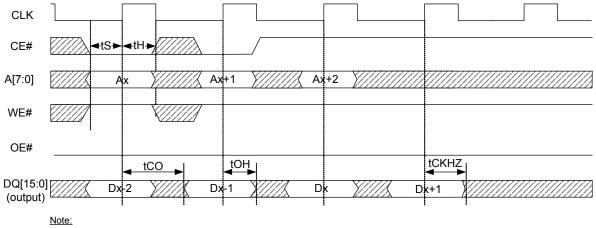

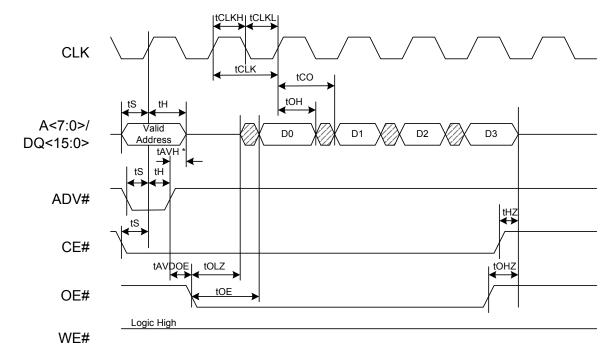

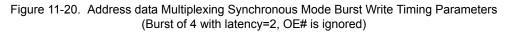

|          |        | 11.1.10.4 Address Data Multiplexing Synchronous Pseudo CRAM Mode1            |      |

|          |        | 11.1.10.5 Non Multiplexing Asynchronous SRAM Mode                            |      |

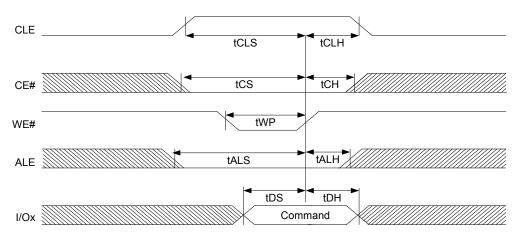

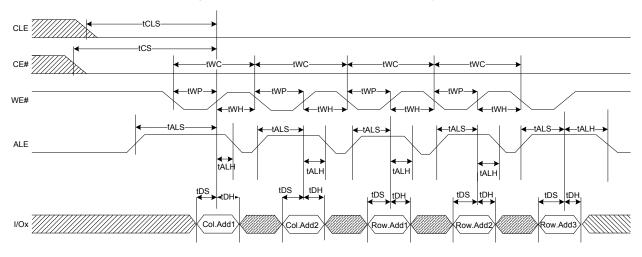

|          |        | 11.1.10.6 Pseudo NAND (PNAND) mode1                                          |      |

|          |        | 11.1.10.7 PSPI and PI2C Interface1                                           |      |

|          |        | 11.1.10.8 Other P-Port Timings1                                              |      |

|          |        | Address Space1                                                               |      |

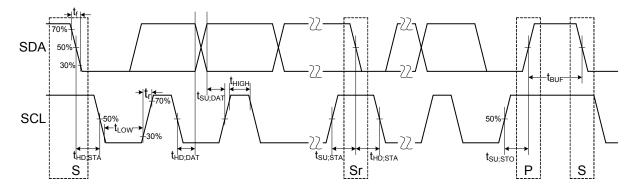

|          | 11.3   | Interrupt1                                                                   |      |

|          |        | 11.3.1 P-Port Interrupt Register1                                            | 144  |

|          |        | 11.3.2 P-Port Interrupt Mask Register1                                       | 145  |

|          | 11.4   | Bootup Initialization1                                                       | 146  |

|          |        | 11.4.1 Wakeup Mechanism1                                                     | 146  |

|          |        | 11.4.2 Configuration Registers1                                              | 146  |

|          | 11.5   | Mailbox Registers1                                                           |      |

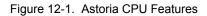

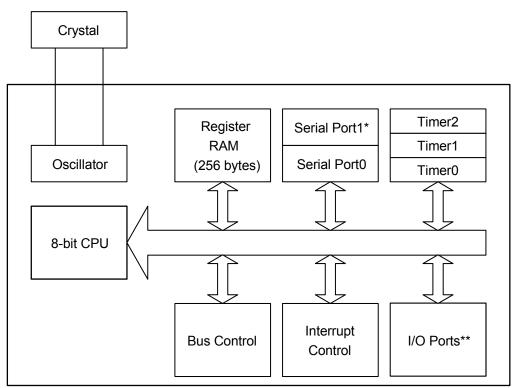

| 12. CPU  | Introd | uction 1                                                                     | 53   |

|          | 12.1   | 8051 Enhancements1                                                           | 154  |

|          |        | Performance Overview                                                         |      |

|          |        | Software Compatibility1                                                      |      |

|          | 12.0   | ootware companying                                                           | 100  |

#### Contents

|           | 12.4     | 803x/805x Feature Comparison      |     |

|-----------|----------|-----------------------------------|-----|

|           | 12.5     |                                   |     |

|           |          | 12.5.1 Serial Ports               |     |

|           |          | 12.5.2 Timer 2                    |     |

|           |          | 12.5.3 Timed Access Protection    |     |

|           |          | 12.5.4 Watchdog Timer             |     |

|           |          | 12.5.5 Power Fail Detection       |     |

|           |          | 12.5.6 Port I/O                   |     |

|           |          | 12.5.7 Interrupts                 |     |

|           | 12.6     | Astoria Register Interface        |     |

|           | 12.7     | Astoria Internal RAM              |     |

|           | 12.8     | I/O Ports                         |     |

|           | 12.9     | Interrupts                        |     |

|           | 12.10    | ) Power Control                   |     |

|           |          | Special Function Registers        |     |

|           |          | 2 External Address/Data Buses     |     |

|           | 12.13    | 3 Reset                           |     |

| 13. Ins   | structio | n Set                             | 161 |

|           | 13 1     | Instruction Timing                | 164 |

|           |          | 13.1.1 Stretch Memory Cycles      |     |

|           |          | 13.1.2 Dual Data Pointers         |     |

|           |          | 13.1.3 Special Function Registers |     |

| 14. Inc   | out/Outp | put                               | 167 |

| <b>-r</b> | -        | I/O Ports                         |     |

|           |          |                                   |     |

|           |          | SFR Registers                     |     |

| 14.2 | SFR Registers                                |     |

|------|----------------------------------------------|-----|

| 14.3 | I/O Port Alternate Functions                 |     |

|      | 14.3.1 Port A Alternate Functions            | 170 |

|      | 14.3.2 Port B and Port D Alternate Functions | 171 |

|      | 14.3.3 Port C Alternate Functions            | 172 |

| 14.4 | I2C Bus Controller                           |     |

|      | 14.4.1 Interfacing to I2C Peripherals        |     |

|      | 14.4.1.1 Multiple Bus Masters                |     |

|      | 14.4.2 Registers                             |     |

|      | 14.4.2.1 I2CS Register                       |     |

|      | 14.4.2.2 I2CDAT Register                     |     |

|      | 14.4.2.3 I2CTL Register                      |     |

|      | 14.4.3 Sending Data                          |     |

|      | 14.4.4 Receiving Data                        |     |

| 14.5 | EEPROM Boot Loader                           |     |

|      |                                              |     |

## 15. Timers and Serial Interface

| 1 | 7 | 9 |

|---|---|---|

| 1 | 1 | 9 |

| 15.1 | Timers                                                  | 179 |

|------|---------------------------------------------------------|-----|

|      | 15.1.1 EZ-USB FX2LP and West Bridge Astoria Differences | 179 |

|      | 15.1.2 Timer and Controller Mode                        | 179 |

| 15.2 | Serial Interface                                        | 180 |

|      | 15.2.1 EZ-USB FX2LP and West Bridge Astoria Differences | 180 |

|      | 15.2.2 Serial Interface Configuration Register and Mode | 181 |

## 16. Register Summary

Contents

# 1. Introducing West Bridge<sup>®</sup> Astoria<sup>™</sup>

The Universal Serial Bus (USB) is widely accepted as the connection method of choice for PC peripherals. USB delivered on its promises of easy attachment, an end to configuration problems, and true plug-and-play operation.

The West Bridge<sup>®</sup> Astoria<sup>™</sup> device is a single-chip USB 2.0 peripheral controller that supports High-Speed USB (HS USB) and mass storage access. The West Bridge<sup>®</sup> Arroyo<sup>™</sup> device is a low-pin-count version of the West Bridge Astoria device.

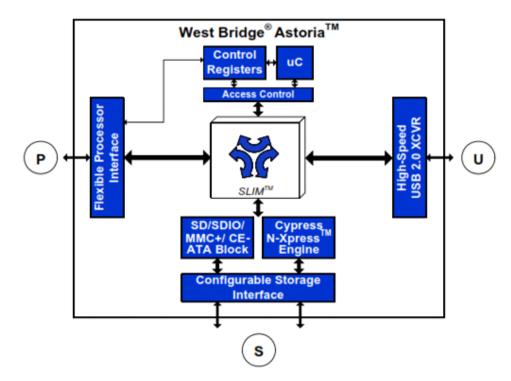

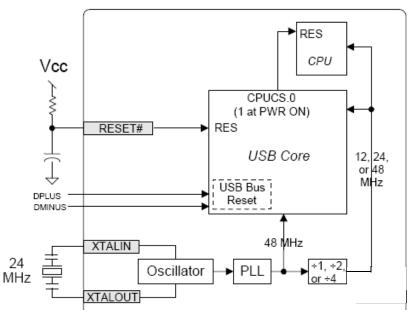

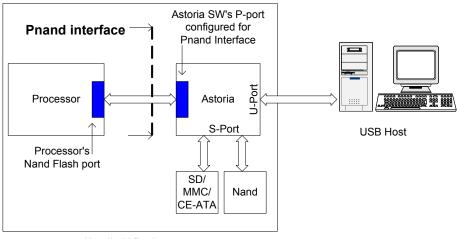

This controller provides access from a processor interface and a High-Speed USB (HS-USB) interface to peripherals such as SD (ver. 1.1 and 2.0), full SDIO, MMC/MMC+, and CE-ATA. It supports arbitration for interleaving accesses between the processor interface, the HS-USB, and the peripherals, so that an external processor and an external USB host can transfer data to each other and to the mass-storage peripherals simultaneously. Figure 1-1 shows a high-level block diagram.

Note From this point, all descriptions of Astoria also apply to Arroyo, unless otherwise specified.

Figure 1-1. West Bridge Astoria High-Level Block Diagram

## 1.1 Astoria Architecture

The Cypress West Bridge Astoria family supports the high bandwidth offered by the USB 2.0 high-speed mode. Astoria packs all of the intelligence required by a USB peripheral interface into a compact integrated circuit.

The Astoria chips offer these features:

- An integrated, high-performance CPU based on the industry-standard 8051 processor

- Automatic handling of most of the USB protocol, which simplifies code and accelerates the USB learning curve

- Processor interface port (P-port) can be configured to Pseudo CRAM processor interface, SRAM interface, Pseudo Serial Peripheral Interface (PSPI) slave interface mode, PNAND interface or Address Data Multiplexed (ADM) interface mode. The PI2C interface is available in the ADM and PSPI interface modes.

- In Pseudo CRAM processor interface mode, the interface can be configured to non-multiplexing or multiplexing address and data buses.

- Storage port (S-port) supports up to two SD, SDIO, MMC, MMC Plus, and CE-ATA. It can also support a peripheral with custom communication protocols.<we should define all of these acronyms>

- It provides interleaved access among P-port processor interface, HS USB interface, and mass storage.

- Available in 100-Pin VFBGA and 81-Pin WLCSP packages.

The controller offers multiple access paths among three different ports: the Processor port (for example, connecting to a handset baseband processor), the HS USB port (connecting to an external USB host), and the mass-storage port (connecting to mass-storage devices). DMA is supported so that data transfers, such as transfers between the HS USB and the processor, and between the processor and mass storage can happen.

Usage models include the USB host accessing mass storage, the USB host exchanging data with the handset processor (used as a modem), and the handset processor accessing mass storage. West Bridge Astoria enables these accesses to happen independently and interleaved, after accounting for the fact that a single resource (such as USB or mass storage) can issue or receive only one data transfer at a time.

When any SD, SDIO, MMC, MMC Plus, and CE-ATA mass storage peripherals are not connected to the storage port, Astoria can connect peripherals with custom communication protocols. You can create the custom communication protocol using internal general programmable interface (GPIF) functionality, connected to storage port. The GPIF serves as an 'internal' master, interfacing directly to the external peripheral FIFOs and generating user-programmed control signals for the interface to external logic. Additionally, the GPIF can be made to wait for external events by sampling external signals on its RDY pins. The GPIF runs much faster than the external peripheral FIFO data rate to give good programmable resolution for the timing signals.

The Astoria's CPU is rich in features. It runs at a clock rate of up to 48 MHz and uses four clocks per instruction cycle instead of the twelve required by a standard 8051.

The Astoria chip family uses an enhanced SIE/USB interface that simplifies Astoria code by implementing much of the USB protocol. In fact, Astoria can function as a full USB device even without firmware. All Astoria family chips operate at 3.3 V. This simplifies the design of bus-powered USB devices, because the 5 V power available at the USB connector can drive a 3.3 V regulator to deliver clean, isolated power to the Astoria chip.

# 1.2 Top Level Block Diagram

## 1.3 Top Level Functional Blocks

The following sections provide an outline of the top level functional blocks in Astoria.

## 1.3.1 Processor Interface Port (P-Port)

This port provides standard asynchronous and synchronous memory interface that can connect to the processors. The processor interface at the P-port can be configured to:

- Pseudo CRAM memory interface mode

- Synchronous nonmultiplexing AD mode (ADV# must pull low in this mode)

- Asynchronous nonmultiplexing AD mode

- Synchronous multiplexing AD mode

- Asynchronous multiplexing AD mode

- Standard SRAM interface. This supports asynchronous nonmultiplexing AD mode (ADV# must pull low in this mode)

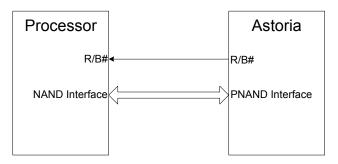

- Pseudo NAND (PNAND) interface mode

- PSPI slave mode. In this mode, Astoria does not support daisy chain connection.

- PI2C interface mode. This interface connects to an external EEPROM that allows Astoria to download the firmware image from the EEPROM. The interface is available in PNAND, multiplexing AD, and PSPI modes.

CYPRESS

Through the P-port interface, the external processor can access the Astoria configuration and status registers, the internal buffers for data to and from the U-port (HS USB port), and the removable media (SD, MMC, and others) also attached at the S-port.

## 1.3.2 USB Port (U-Port)

The USB port controls the interface to the High-Speed USB 2.0 port. In accordance with the USB 2.0 specification, Astoria can also operate in Full-Speed USB mode. This port consists of the USB SIE, transceiver, and USB switch. The USB switch in Astoria supports only Full-Speed USB communication. Arroyo does not provide the USB switch feature. The USB interface can access and be accessed by the P-port and the S-port.

The Astoria USB interface supports programmable CON-TROL/BULK/INTERRUPT/ISOCHRONOUS endpoints.

## 1.3.3 Storage Port (S-Port)

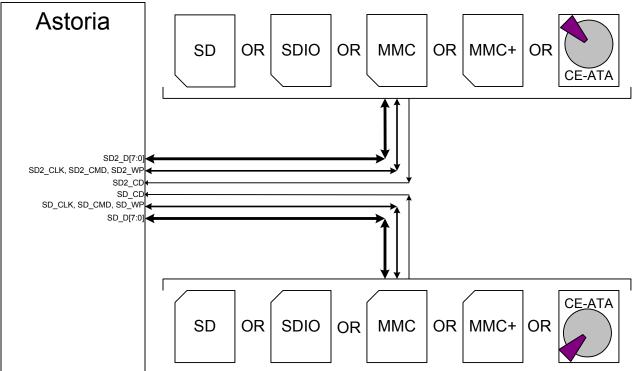

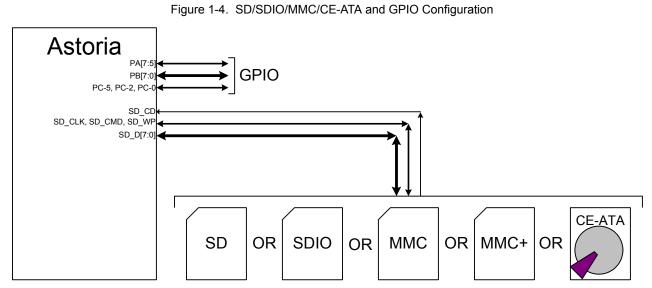

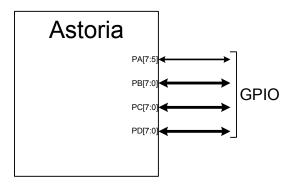

The S-port consist two separate buses: S1 and S2.

These ports can be configured individually as:

- 1. SD/SDIO/MMC/CE-ATA only interface

- 2. SD/SDIO/MMC/CE-ATA and GPIO interface

- 3. GPIO-only interface

- 4. GPIF and SD/SDIO/MMC/CE-ATA interface

- 5. GPIF-only interface

- 6. GPIF and GPIO interface

The standard 8051 ports A to D are mapped for various alternate functions, for S-Port interfaces, in Astoria; Port E is not available in West Bridge Astoria.

Figure 1-3 on page 12 through Figure 1-5 on page 13 illustrates the connections for S-port configurations. Table 1-1 on page 13 summarizes all configurations in the S-port. Table 1-2 on page 13 shows the S-port mapping in all configurations.

The S-port interface includes three different power domains: SSVDDQ, SNVDDQ, and GVDDQ. For the system design, the power domain connection depends on S-port configuration. You must connect the power domains of all interface signals to the same power source (for example, the same voltage level). If the S-port is configured to "GPIF only Configuration," SSVDDQ, SNVDDQ, and GVDDQ must connect to the same voltage level (for example, 3.3 V). In this case, the RESET and WAKEUP pin require a 3.3-V input signal (for example, VIH = 3.3 V).

Note Arroyo has only one storage bus.

Figure 1-5. GPIO-Only Configuration

Table 1-1. S-Port Configurations Summary

| Configuration                         | Description |                                                                      |  |

|---------------------------------------|-------------|----------------------------------------------------------------------|--|

| SD/SDIO/MMC/CE-ATA only interface     | Dual SD     | 2 × SD/SDIO/MMC/CE-ATA                                               |  |

| SD/SDIO/MMC/CE-ATA and GPIO interface | SD + GPIO   | 1 × SD/SDIO/MMC/CE-ATA and 14 × GPIO pins                            |  |

| GPIF-only interface                   | GPIF        | 27 × GPIF pins                                                       |  |

| GPIO-only interface                   | GPIO        | 27 × GPIO pins                                                       |  |

| GPIF and GPIO interface               | GPIF + GPIO | 8 × GPIF_DATA, 2 × GPIF_CTL, 1 × GPIF_RDY and 16 GPIO Pins           |  |

| GPIF and SD interface                 | GPIF + SD   | 8 × GPIF_DATA, 2 × GPIF_CTL, 1 × GPIF_RDY and 1 × SD/SDIO/MMC/CE-ATA |  |

| Table 1-2. S | S-Port Mapping | in All Configurations <sup>[a</sup> | , b] |

|--------------|----------------|-------------------------------------|------|

|--------------|----------------|-------------------------------------|------|

| Configuration   | Default | Dual SD | SD / Port B<br>GPIO | GPIF Only<br>(16-bit data) | GPIO Only | GPIF (8-bit) /<br>Port D GPIO | SD / GPIF |

|-----------------|---------|---------|---------------------|----------------------------|-----------|-------------------------------|-----------|

| NANDCFG         | 0       | 0       | 0                   | 1                          | 0         | 0                             | 0         |

| IFCONFIG[0]     | 1       | 1       | 1                   | 0                          | 0         | 0                             | 1         |

| SIB_NAND_CFG[5] | 0       | 0       | 0                   | 1                          | 1         | 1                             | 0         |

| SIB_NAND_CFG[0] | 0       | 1       | 0                   | 0                          | 0         | 0                             | 0         |

| IFCONFIG2[0]    | 0       | 0       | 1                   | 0                          | 1         | 0                             | 0         |

| IFCONFIG2[1]    | 0       | 0       | 0                   | 0                          | 1         | 1                             | 0         |

| Table 1-2. | S-Port Mapping in                       | All Configurations <sup>[a, b]</sup> | (continued) |

|------------|-----------------------------------------|--------------------------------------|-------------|

|            | • · • · • · • · • · • · • · · · · · · · | , e ega. a.a.ee                      | (           |

| C       | onfigura | tion    | Default     | Dual SD    | SD / Port B<br>GPIO | GPIF Only<br>(16-bit data) | GPIO Only | GPIF (8-bit) /<br>Port D GPIO | SD / GPIF   |

|---------|----------|---------|-------------|------------|---------------------|----------------------------|-----------|-------------------------------|-------------|

|         |          | 0       | NA*         | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 1       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 2       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 3       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         | OUT      | 4       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 5       | GPIO        | -          | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 6       | GPIO        | -          | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 7       | GPIO        | -          | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

| ort A   |          | 0       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 1       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 2       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 3       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         | IN       | 4       | NA          | NA         | NA                  | NA                         | NA        | NA                            | NA          |

|         |          | 5       | GPIO        | -          | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 6       | GPIO        | SD2_CLK    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 7       | GPIO        | SD2_CMD    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         | OUT      |         | GPIF_D[7:0] | SD2_D[7:0] | GPIO                | GPIF_D[7:0]                | GPIO      | GPIF_D[7:0]                   | GPIF_D[7:0] |

| ort B   | IN       |         | GPIF_D[7:0] | SD2_D[7:0] | GPIO                | GPIF_D[7:0]                | GPIO      | GPIF_D[7:0]                   | GPIF_D[7:0] |

|         |          | 0       | GPIO        | SD2_POW    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 1       | -           | -          | -                   | GPIO                       | GPIO      | GPIO                          | -           |

|         |          | 2       | GPIO        | -          | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 3       | -           | -          | -                   | GPIO                       | GPIO      | GPIO                          | -           |

|         | OUT      | 4       | GPIO[0]     | GPIO[0]    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 5       | GPIO[1]     | GPIO[1]    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 6       | SD_POW      | SD_POW     | SD_POW              | GPIO                       | GPIO      | GPIO                          | SD_POW      |

|         |          | 7       | -           | -          | -                   | GPIO                       | GPIO      | GPIO                          | -           |

| ort C   |          | 0       | GPIO        | SD2_POW    | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 1       | SD_WP       | SD_WP      | SD_WP               | GPIO                       | GPIO      | GPIO                          | SD_WP       |

|         |          | 2       | GPIO        | SD2_WP     | GPIO                | GPIO                       | GPIO      | GPIO                          | GPIO        |

|         |          | 3       | SD_CMD      | SD_CMD     | SD_CMD              | GPIO                       | GPIO      | GPIO                          | SD_CMD      |

|         | IN       | 4       | GPIO[0]     | SD_CD      | SD_CD               | GPIO[0]                    | GPIO[0]   | GPIO[0]                       | SD_CD       |

|         |          | 5       | GPIO[1]     | SD2_CD     | GPIO                | GPIO[1]                    | GPIO[1]   | GPIO[1]                       | GPIO[1]     |

|         |          | 6       | SD_POW      | SD_POW     | SD_POW              | GPIO                       | GPIO      | GPIO                          | SD_POW      |

|         |          | 7       | SD_CLK      | SD_CLK     | SD_CLK              | GPIO                       | GPIO      | GPIO                          | SD_CLK      |

|         | OUT      |         | SD_D[7:0]   | SD_D[7:0]  | SD_D[7:0]           | GPIF_D[15:8]               | GPIO      | GPIO                          | SD_D[7:0]   |

| ort D   | IN       |         | SD_D[7:0]   | SD_D[7:0]  | SD_D[7:0]           | GPIF_D[15:8]               | GPIO      | GPIO                          | SD_D[7:0]   |

| PIF_R   | DY[0]    |         | GPIF_RDY    | -          | -                   | GPIF_RDY                   | -         | GPIF_RDY                      | GPIF_RDY    |

|         |          | SET_OUT | RESET_OUT   | RESET_OUT  | RESET_OUT           | GPIF_RDY                   | RESET_OUT | RESET_OUT                     | GPIF_RDY    |

|         |          | 0       | GPIF_CTL    | -          | -                   | GPIF_CTL                   | -         | GPIF_CTL                      | GPIF_CTL    |

| GPIF_CT | TL       | 1       | GPIF_CTL    | -          | -                   | GPIF_CTL                   | -         | GPIF_CTL                      | GPIF_CTL    |

a. IN GPIO highlighted in yellow.b. Unused shaded gray

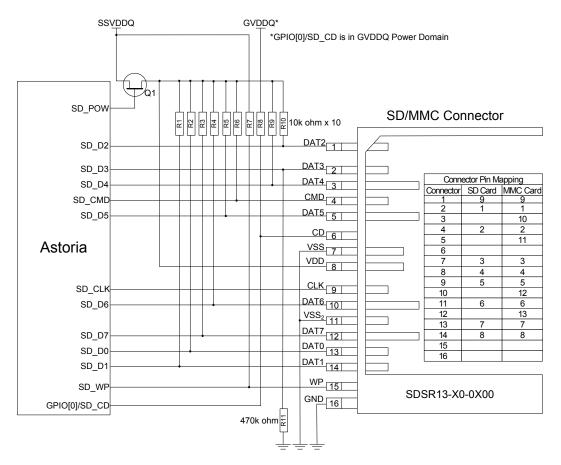

### 1.3.3.1 SD/MMC Port (S-Port)

This interface port supports:

- The Multimedia Card-System Specification, MMCA Technical Committee, Version 4.2.

- CE-ATA CE-ATA Digital Protocol CE-ATA Committee, Version 1.1, September 29, 2005.

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 1.1, October 15, 2004.

- SD Memory Card Specification Part 1, Physical Layer Specification, SD Group, Version 2.00, May 9, 2006

- SD Specification Part E1, SDIO Specification, SD Group, Version 1.10, August 18, 2004

The 8051 firmware sets the configuration of the S-port as either 16-bit GPIF (no SD/MMC device) or 8-bit GPIF and SD/SDIO/MMC. The S-port can be configured to support up to two SD/SDIO/MMC ports. In this configuration, GPIF is not supported at the S-port. West Bridge Astoria provides support for 1-bit and 4-bit SD cards, and 1-bit, 4- bit, and 8bit MMC, MMC+, and CE-ATA (Micro Hard Disk Drive) cards. Each SD/SDIO/MMC port supports one SD, SDIO, and MMC/MMC Plus/CE-ATA card.

Astoria supports SD commands, including the multisector program command that is handled by the API.

#### SD\_CLK Output Clock

During the data transfer, the SD\_CLK clock can be enabled (turned on) or disabled (stopped) at any time by the internal flow-control mechanism. This flow-control mechanism stops the clock when it detects that the buffer (Endpoint) is overflowing by the multiple blocks read from the SD/MMC/ MMC+/CE-ATA card. The internal mechanism must be synchronized to the SD\_CLK clock during its enable and disable switching. This requirement increases the performance of Astoria during the SD read operation. The SD\_CLK clock output frequency, configured as 400 kHz, 20 MHz, 24 MHz, and 48 MHz by 8051, is described:

- 400 kHz: For SD/MMC/MMC+ card initialization

- 20 MHz: For a card with frequency 0 to 20 MHz

- 24 MHz: For a card with frequency 0 to 26 MHz

- 48 MHz: For a card with frequency 0 to 52 MHz

#### Card Insertion and Removal Detection (CD)

Astoria can support the following card insertion and removal detection mechanisms on the S-port:

Use of SD\_D[3]/SD2\_D[3] data for card insertion and removal detection. In this system design, this signal must have a 470-kΩ pull down resistor connected to SD\_D[3]/SD2\_D[3]. In the SD card, internally, it has a 10-kΩ pull-up resistor on the SD\_D[3]/SD2\_D[3]. When the card is inserted or removed from the SD/MMC connector, the voltage level changes at the SD\_D[3]/ SD2\_D[3] pin, which triggers an interrupt to the 8051. This card insertion and removal detection mechanism may not be supported by the older MMC cards.

Use of GPIO[0]/GPIO[1] for card insertion and removal detection. Some SD/MMC connectors facilitate a microswitch for card insertion and removal detection (CD). This microswitch is connected to GPIO[0]/GPIO[1]. When the card is inserted or removed from the SD/MMC connector, it turns the microswitch on and off and causes a voltage level change at GPIO[0]/GPIO[1] that triggers an interrupt to the 8051. The card detects microswitch polarity is assumed to be the same as the write-protect microswitch polarity explained in the following sections. LOW indicates that a card is inserted.

The card insertion and removal detection interrupt on both SD\_D[3]/SD2\_D[3] and GPIO[0]/GPIO[1] can be independently masked (disabled). When the SD bus (SD\_D [7:0]) has no ownership or has been allocated the processor, the SD\_D[3] is tristated, driven by the signal changes external to Astoria. In this case, if SD\_D3 is used for card insertion and removal detection, it must mask the interrupt to avoid unwanted interrupts.

The following four scenarios describe how to handle card an insertion/removal detection interrupt from the 8051 firmware.

- The SD bus has no ownership (the processor and Astoria do not own the SD Bus):

- The SD bus is in tristate at all times

- The card insertion/removal detection interrupt on SD D[3] is disabled (masked).

- THe SD bus initially has no ownership; Astoria then gets ownership:

- □ Astoria gets ownership of the SD Bus.

- □ The 8051 firmware clears the card insertion/removal detection interrupt status (or IRQ flag).

- The 8051 enables (unmasks) the card insertion/ removal detection interrupt.

- The SD bus is owned by the processor, but is being allocated to Astoria:

- The 8051 sends an SD bus request message to the processor.

- When the processor releases the SD bus with a response message, Astoria writes a '1' to the SDIO-AVI field of the External Bus Allocation register to take ownership of the SD bus.

- After Astoria takes ownership of the SD bus, the 8051 firmware clears the card insertion/removal detection interrupt status (or IRQ flag).

- The 8051 enables (unmasks) the card insertion/ removal detection interrupt.

- The SD bus is owned by Astoria, but is allocated to the processor:

- The processor sends an SD Bus request message to Astoria.

- When the SD bus is available to be allocated to the processor, the 8051 disables (masks) the card insertion/removal detection interrupt on SD\_D[3].

- □ The 8051 releases ownership to the processor.

- □ The 8051 sends a message to the processor saying that the bus has been released.

#### Write Protection (WP)

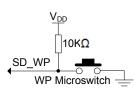

The SD\_WP (SD Write Protection) in the S-port connects to the WP microswitch of the SD/MMC card connector. This signal pin is internally connected to the 8051 GPIO pin for firmware to detect SD card write protection. Figure 1-6 shows the connection of the WP microswitch to the SD\_WP pin.

Figure 1-6. Connecting the WP Microswitch to the SD\_WP Pin

Table 1-3. S-Port Pin Definitions for SD/SDIO/MMC/MMC+

#### SD\_POW

SD\_POW is an output pin that provides an option to control the power for the SD/MMC card or CE-ATA drive. This pin connects to the external power switch control to turn on or off the power for the SD/MMC card or CE-ATA drive. The output signal of this pin is controlled by the 8051 firmware. Figure 1-7 on page 17 shows the this signal's system connectivity.

#### **SD/MMC System Interface Requirement**

In the SD/MMC specification, pull-up and pull-down resistors are required, as shown in Figure 1-7 on page 17. This figure also shows the two different card mechanisms, though only one is required in the system design.

If the system design uses SD\_D[3] for card insertion and removal detection, Q1 must be on at all times and R8 is not required. If the system design uses GPIO[0] for card insertion and removal detection, R11 must be a 10-k $\Omega$  pull-up, instead of a 470-k $\Omega$  pull-down.

| Astoria SDIO Port<br>Pin Name | SD/SDIO/MMC/MMC<br>Plus Card Pin # | SD <sup>[a]</sup>       | SDIO 1-Bit Mode         | SDIO 4-Bit Mode               | MMC/MMC Plus <sup>[b]</sup> | SPI Mode                  |

|-------------------------------|------------------------------------|-------------------------|-------------------------|-------------------------------|-----------------------------|---------------------------|

| SD_D[0]/SD2_D[0]              | 7                                  | D0                      | Data                    | D0                            | D0                          | Data Out                  |

| SD_D[1]/SD2_D[1]              | 8                                  | D1                      | Interrupt               | D1 or Interrupt<br>(optional) | D1                          | N/A                       |

| SD_D[2]/SD2_D[2]              | 9                                  | D2                      | Read wait (optional)    | D2 or Read Wait<br>(optional) | D2                          | N/A                       |

| SD_D[3]/SD2_D[3]              | 1                                  | Card Detect/D3          | N/A                     | D3                            | D3                          | Chip Select<br>(neg true) |

| SD_D[4]/SD2_D[4]              | 10                                 | N/A                     | N/A                     | N/A                           | D4                          | N/A                       |

| SD_D[5]/SD2_D[5]              | 11                                 | N/A                     | N/A                     | N/A                           | D5                          | N/A                       |

| SD_D[6]/SD2_D[6]              | 12                                 | N/A                     | N/A                     | N/A                           | D6                          | N/A                       |

| SD_D[7]/SD2_D[7]              | 13                                 | N/A                     | N/A                     | N/A                           | D7                          | N/A                       |

| SD_CLK/SD2_CLK                | 5                                  | Clock                   | Clock                   | Clock                         | Clock                       | Clock                     |

| SD_CMD/SD2_CMD                | 2                                  | Command /<br>Response   | Command /<br>Response   | Command /<br>Response         | Command /<br>Response       | Data In                   |

| SD_POW/SD2_POW                | Not in SD/SDIO/<br>MMC spec        | Power Switch<br>Control | Power Switch<br>Control | Power Switch<br>Control       | Power Switch<br>Control     | Power Switch<br>Control   |

| SD_WP/SD2_WP                  | Not in SD/SDIO/<br>MMC spec        | Write Protect           | Write Protect           | Write Protect                 | Write Protect               | Write Protect             |

a. Data lines 1, 2 and 3 not used for 1 bit bus width.

b. Number of data lines used depends on bus width selected (1, 4 or 8).

Figure 1-7. SD/MMC System Interface Connection Requirement

#### 1.3.3.2 CE-ATA (S-Port)

CE-ATA is a micro-hard-disk drive interface that is optimized for handheld and embedded applications storage. CE-ATA is layered on top of the MMC electrical interface using a protocol that uses the existing MMC access primitives. The interface electrical and signaling definition is similar to the one defined in the MMC specification.

In the CE-ATA protocol, there are two mechanisms to detect command completion. The first mechanism is interrupt and the second is polling (polling the status register from the device). Astoria uses only the interrupt mechanism for command completion detection.

Astoria also supports the Command Completion Signal Disable (CCSD) protocol.

The detailed Data-In and Data-Out Command Protocol with the Interrupt Enable are described in sections 5.1 (Data-In) and 6.1 (Data-Out) of the *CE-ATA Host Design Guidance*, Revision 1.0, September 29, 2005. Refer to this document for further details of the implementation.

#### 1.3.3.3 GPIO[1:0]

GPIO[1:0] is mapped to 8051 Port C bit 5 and 4 (for example, PC[5:4]). These GPIO pins are multifunction pins. In normal operation mode, these two pins can be configured to UART interface by setting the GPIO\_UART\_EN field of the UART Configuration register to '1'. In UART configuration, GPIO[0] is configured to TxD0 and GPIO[1] is configured to RxD0.

## 1.4 Packages

Astoria is available in 100-pin VFBGA and 81-pin WLCSP packages. Arroyo is available in a 81-pin WLCSP package. See the product datasheet for pin assignment, ball map, and interface option details.

# 1.5 Endpoints Overview

Astoria supports data transfer among its three ports through endpoint (EP) buffering.

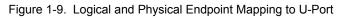

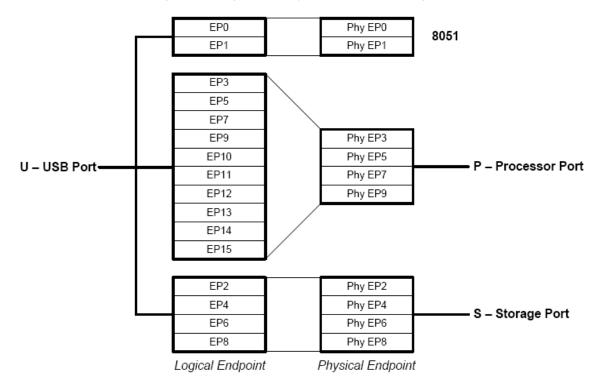

## 1.5.1 Logical Endpoints

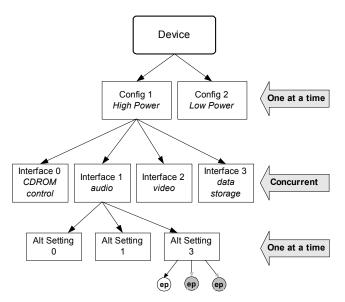

Astoria supports 16 logical endpoints, which can be configured as shown in Figure 1-8 on page 19.

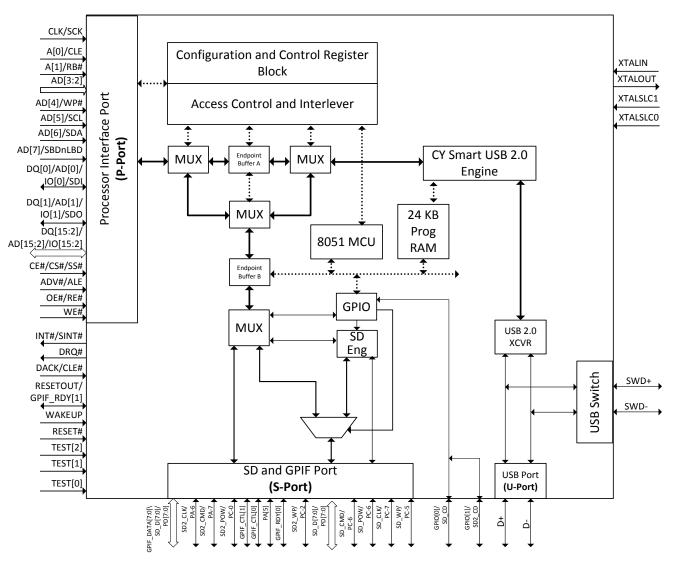

- EP2, EP4, EP6, and EP8 are allocated to the U-port to S-port path (corresponding to Endpoint Buffers B in Figure 1-2 on page 11).

- EP3, EP5, EP7, EP9, EP10, EP11, EP12, EP13, EP14, and EP15 are allocated to the U-port to P-port path (corresponding to Endpoint Buffers A in Figure 1-2 on page 11).

- Endpoints are allocated by the 8051 MCU within Astoria.

- EP0 and EP1 endpoints are accessible only to the 8051 MCU within Astoria.

- In addition to EP0 and EP1, the 8051 MCU within Astoria has access to all of the endpoint buffers (for example, EP2 to EP8).

- Each endpoint can be configured to be "IN" or "OUT"

- Up to 10 logical endpoints can be active at any time for the P-port to U-port path; there are up to 4 logical endpoints combined for the U-port to S-port and the P-port to S-port paths. For example, if Astoria's U-port is not accessing the S-port, the P-port to S-port path can use up to 4 logical endpoints. Endpoint assignment and activation is carried out in firmware. If the USB host tries to access an endpoint that is inactive, it will send a NAK.

- During a DMA transfer request to the processor, the EPnDRQ field in the DRQ Status register, CY\_AN\_MEM\_P0\_DRQ indicates the logical endpoint for which the DMA request was made. Because EP0 and EP1 are not accessible by the processor port, EP0DRQ and EP1DRQ are reserved and are not asserted for DMA request to processor port.

## 1.5.2 Physical Endpoints

Logical endpoints are mapped to physical endpoints. Physical endpoints can be dedicated to a logical endpoint or shared between multiple logical endpoints. Physical endpoints can only map to multiple logical endpoints in the same direction. Logical to physical endpoint mapping is dynamic and can be changed by the 8051 firmware, with the exception of the EP0, EP1, EP2, EP4, EP5, EP6, and EP8 endpoints. EP0, EP1, EP2, EP4, EP5, EP6, and EP8 are always mapped to dedicated physical EP0, EP1, EP2, EP4, EP5, EP6, and EP8 are always mapped to dedicated physical EP0, EP1, EP2, EP4, EP5, EP6, and EP8 endpoints. Also, logical EP for the ISO channel requires dedicated physical EP in the U-port to P-port (USB host to external processor) path. These ISO transfers can only use endpoint numbers 3, 5, 7, and 9.

- There are a total of 11 physical endpoints: 4 physical endpoints (equivalent to 4 KB of buffering total) between the U-port and the P-port, 4 physical endpoints between the U-port and the S-port, and 3 physical endpoints for EP0, EP1IN, and EP1OUT (accessed only by 8051).

- EP0 is the default CONTROL endpoint, a bidirectional endpoint that uses a single 64-byte buffer for both IN and OUT data.

- EP1IN and EP1OUT use separate 64 byte buffers.

- Logical endpoints {EP3, EP5, EP7, EP9, EP10, EP11, EP12, EP13, EP14, EP15} between U and P port can be mapped to the four physical endpoints between the U-port and the P-port.

- When multiple logical endpoints are mapped to a single physical endpoint, the logical endpoints are served in a first-in-first-out basis.

| EP0 IN&OUT 64   64<br>EP1 IN 64   64<br>EP1 OUT 64   64 | 64     64       64     64       64     64       64     64 | 4   64                     | 64<br>64<br>64    | 64<br>64<br>64    | 64<br>64<br>64    | 64<br>64<br>64 | 64<br>64<br>64    | 64<br>64<br>64    | 64<br>64<br>64 |

|---------------------------------------------------------|-----------------------------------------------------------|----------------------------|-------------------|-------------------|-------------------|----------------|-------------------|-------------------|----------------|

| EP2<br>512<br>512<br>512<br>512                         | 512 51                                                    | P2 EP2<br>12 512<br>12 512 | EP2<br>512<br>512 | EP2<br>1024       | EP2<br>1024       | EP2<br>1024    | EP2<br>512<br>512 | EP2<br>1024       | EP2<br>1024    |

| EP4EP4512512512512                                      |                                                           | 12 512<br>12 512           | 512<br>512        | 1024              | 1024              | 1024           | 512<br>EP6<br>512 | 1024              | 1024           |

| EP6<br>512<br>512<br>512<br>512                         | 1024                                                      | P6 EP6<br>12 512<br>12 512 | EP6<br>1024       | EP6<br>512<br>512 | EP6<br>512<br>512 | EP6<br>1024    | 512<br>512        | 1024              | 1024           |

| EP8<br>512<br>512<br>512                                | 1024 5 <sup>-</sup>                                       | P8<br>12 512<br>12 512     | 1024              | EP8<br>512<br>512 | 512<br>512        | 1024           | EP8<br>512<br>512 | EP8<br>512<br>512 | 1024           |

| 1 2                                                     | 3 4                                                       | 1 5                        | 6                 | 7                 | 8                 | 9              | 10                | 11                | 12             |

#### Figure 1-8. Endpoint Configuration

Introducing West Bridge<sup>®</sup> Astoria™

# 1.6 Document History

This section is a chronicle of the West Bridge<sup>®</sup> Astoria<sup>™</sup> Technical Reference Manual.

### Astoria Technical Reference Manual History

| Release Date | Version | Originator | Description of Change |

|--------------|---------|------------|-----------------------|

| 02/24/2012   | **      | DBIR       | New document          |

| 03/16/2015   | *A      | DBIR       | Sunset Review         |

| 03/10/2015   | A       | DBIR       | Updated template      |

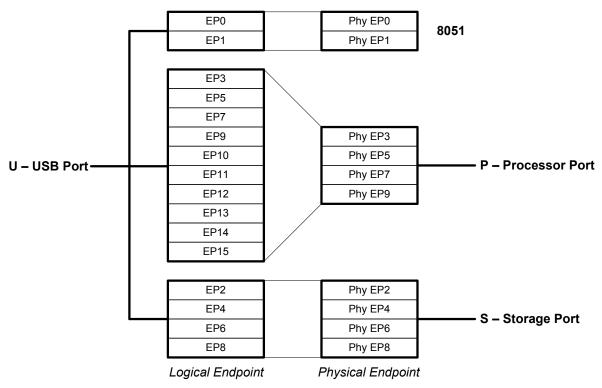

Endpoint zero has particular significance in a USB system. It is a CONTROL endpoint, and every USB device requires one. The USB host uses special SETUP tokens to signal transfers that involve device control; only CONTROL endpoints accept these special tokens.

The USB host sends a suite of standard device requests over endpoint zero. These standard requests are fully defined in Chapter 9 of the USB Specification. This chapter describes how the West Bridge<sup>®</sup> Astoria<sup>™</sup> chip handles endpoint zero requests.

Astoria provides extensive hardware support for handling endpoint-zero operations; this chapter describes those operations and the Astoria resources that simplify the firmware that handles them.

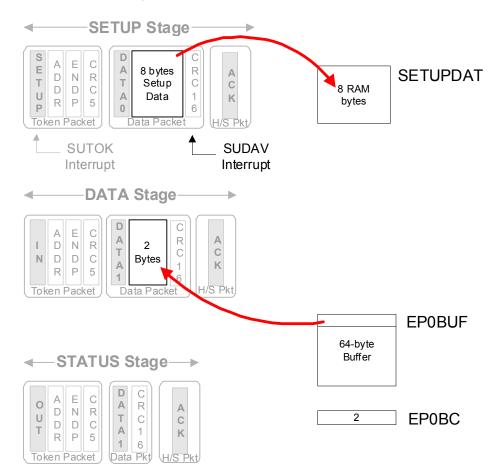

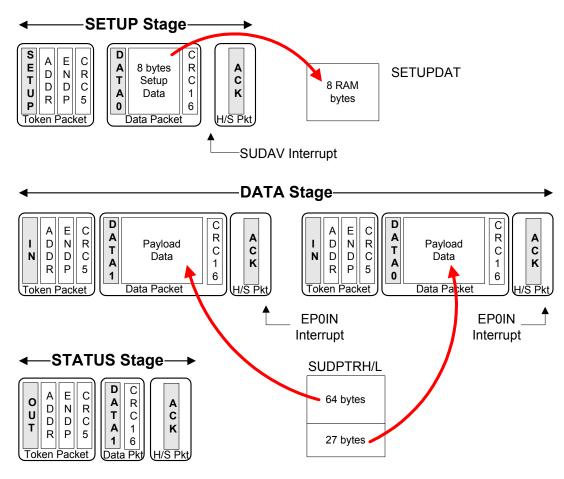

Astoria provides a single 64-byte buffer, EP0BUF, which firmware handles exactly like a bulk endpoint buffer for the data stages of a CONTROL transfer. A second 8-byte buffer called SETUPDAT, which is unique to endpoint zero, holds data that arrives in the SETUP stage of a CONTROL transfer. This relieves the Astoria firmware of the burden of tracking the three CONTROL transfer phases (SETUP, DATA, and STATUS). Astoria also generates separate interrupt requests for the various transfer phases, further simplifying code.

Endpoint zero is always enabled and accessible by the USB host.

## 2.1 Control Endpoint EP0

Endpoint zero accepts a special SETUP packet, which contains an 8-byte data structure that provides host information about the CONTROL transaction. CONTROL transfers include a final STATUS phase, constructed from standard PIDs (IN/OUT, DATA1, and ACK/NAK).

Some CONTROL transactions include all required data in their 8-byte Setup Data packet. Other CONTROL transactions require more OUT data than fits into the eight bytes, or require IN data from the device. These transactions use standard bulk-like transfers to move the data. Note that, in Figure 2-1 on page 22, the DATA stage looks exactly like a bulk transfer. As with BULK endpoints, the endpoint zero byte count registers must be loaded to ACK each data transfer stage of a CONTROL transfer.

The STATUS stage consists of an empty data packet with the opposite direction of the data stage, or an IN if there was no data stage. This empty data packet gives the device a chance to ACK or NAK the whole CONTROL transfer.

The HSNAK bit delays the completion of a CONTROL transfer until the device can respond to a request. For example, if the host issues a Set Interface Request, the Astoria firmware performs housekeeping chores, such as adjusting internal modes and reinitializing endpoints. During this time, the host issues handshake (STATUS stage) packets to which Astoria automatically responds with NAKs, indicating that it is 'busy. When the firmware completes its housekeeping operations, it clears the HSNAK bit (by writing '1' to it), which instructs Astoria to ACK the STATUS stage, ending the transfer. This handshake prevents the host from trying to use an interface before it is fully configured.

To perform an endpoint stall for the DATA or STATUS stage of an endpoint zero transfer (the SETUP stage can never stall), firmware must set both the STALL and HSNAK bits for endpoint zero.

Figure 2-1. A USB Control Transfer (With Data Stage)

Some CONTROL transfers do not have a DATA stage. In those cases, the code that processes the Setup data must check the length field in the Setup data (in the 8-byte buffer at SETUPDAT) and arm endpoint zero for the DATA phase (by loading EP0BCH:L), only if the length field is nonzero.

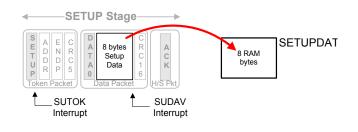

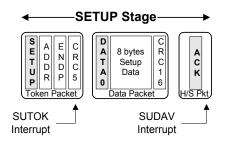

Two interrupts tell the firmware that a SETUP packet has arrived, as shown in Figure 2-2.

Figure 2-2. Two Interrupts Associated with EP0 CONTROL Transfers

Astoria asserts the SUTOK (Setup token) interrupt request when it detects the Setup token at the beginning of a CON-TROL transfer. This interrupt is normally used for debug only.

Astoria asserts the SUDAV (Setup data available) interrupt request when the eight bytes of Setup data have been received error-free and transferred to the SETUPDAT buffer. Astoria automatically takes care of any retries if it finds errors in the Setup data. These two interrupt request bits must be cleared by firmware.

Firmware responds to the SUDAV interrupt request by either directly inspecting the eight bytes at SETUPDAT or transferring them to a local buffer for further processing. Servicing the Setup data is a high priority, because the USB Specification says that CONTROL transfers must always be accepted and never NAKed. It is possible, therefore, that a CONTROL transfer could arrive while the firmware is still servicing a previous one. In this case, firmware must abort the earlier CONTROL transfer service and service the new one. The SUTOK interrupt gives advance warning that a new CON-TROL transfer is about to overwrite the eight SETUPDAT bytes.

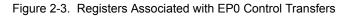

## Registers Associated with Endpoint Zero For handling SETUP transactions

If the firmware stalls endpoint zero (by setting the STALL and HSNAK bits to 1), Astoria automatically clears the stall bit when the next SETUP token arrives.

Like all Astoria interrupt requests, the SUTOK and SUDAV bits can be directly tested and cleared by the firmware (cleared by writing '1') even if their corresponding interrupts are disabled. Figure 2-3 shows the Astoria registers that are associated with CONTROL transactions over EP0.

These registers augment those associated with normal bulk transfers, which are described in the Access to Endpoint Buffers chapter on page 73.

Two bits in the USBIE (USB Interrupt Enable) register enable the SUTOK and SUDAV interrupts. The actual interrupt-request bits are in the USBIRQ (USB Interrupt Requests) register.

Astoria transfers the eight SETUP bytes into eight bytes of RAM at SETUPDAT. A 16-bit pointer, SUDPTRH:L, gives hardware help for handling CONTROL IN transfers, in particular the 'Get Descriptor' requests described later in this chapter.

## 2.2 USB Requests

The Universal Serial Bus Specification Version 2.0, Chapter 9, USB Device Framework defines a set of Standard Device Requests. When the firmware is in control of endpoint zero (RENUM = 1), Astoria handles only one of these requests (Set Address) automatically; the firmware supports all of the others. The firmware acts on device requests by decoding

the eight bytes contained in the SETUP packet and available at SETUPDAT. Table 2-1 defines these eight bytes.

Table 2-1. The Eight Bytes in a USB SETUP Packet

| Byte | Field         | Meaning                                        |

|------|---------------|------------------------------------------------|

| 0    | bmRequestType | Request Type, Direction, and Recipient.        |

| 1    | bRequest      | The actual request (see Table 2-2).            |

| 2    | wValueL       |                                                |

| 3    | wValueH       | 16-bit value, varies according to bRequest.    |

| 4    | wIndexL       |                                                |

| 5    | wIndexH       | 16-bit field, varies according to bRequest.    |

| 6    | wLengthL      | Number of bytes to transfer if there is a data |

| 7    | wLengthH      | phase.                                         |

The Byte column in Table 2-1 shows the byte offset from SETUPDAT. The Field column shows the different bytes in the request, where the 'bm' prefix means bitmap, 'b' means byte [8 bits, 0 to 255], and 'w' means word [16 bits, 0 to 65535].

Table 2-2 shows the values defined for bRequest, and how the firmware responds to each request. The remainder of this chapter describes each of the requests in Table 2-2 in detail.

**Note** Table 2-2 applies when RENUM = 1, meaning that the firmware, rather than the Astoria hardware, handles device requests.

| bRequest          | Name              | Astoria Action                | Firmware Response                        |

|-------------------|-------------------|-------------------------------|------------------------------------------|

| 0x00              | Get Status        | SUDAV Interrupt               | Supply RemWU, SelfPwr or Stall Bits      |

| 0x01              | Clear Feature     | SUDAV Interrupt               | Clear RemWU, SelfPwr or Stall Bits       |

| 0x02              | (Reserved)        | None                          | Stall EP0                                |

| 0x03              | Set Feature       | SUDAV Interrupt               | Set RemWU, SelfPwr or Stall Bits         |

| 0x04              | (Reserved)        | None                          | Stall EP0                                |

| 0x05              | Set Address       | Update FNADDR Register        | None                                     |

| 0x06              | Get Descriptor    | SUDAV Interrupt               | Supply table data over EP0-IN            |

| 0x07              | Set Descriptor    | SUDAV Interrupt               | Application dependent                    |

| 0x08              | Get Configuration | SUDAV Interrupt               | Send current configuration number        |

| 0x09              | Set Configuration | SUDAV Interrupt               | Change current configuration             |

| 0x0A              | Get Interface     | SUDAV Interrupt               | Supply alternate setting number from RAM |

| 0x0B              | Set Interface     | SUDAV Interrupt               | Change alternate setting number          |

| 0x0C              | Sync Frame        | SUDAV Interrupt               | Supply a frame number over EP0-IN        |

| Vendor Requests   |                   |                               |                                          |

| 0xA0 (Firmware Lo | oad)              | Upload / Download on-chip RAM |                                          |

| 0xA1 to 0xAF      |                   | SUDAV Interrupt               | Reserved by Cypress Semiconductor        |

| All except 0xA0   |                   | SUDAV Interrupt               | Application dependent                    |

Table 2-2. How the Firmware Handles USB Device Requests (RENUM = 1)

In the ReNumerated condition (RENUM = 1), Astoria passes all USB requests except Set Address to the firmware using the SUDAV interrupt.

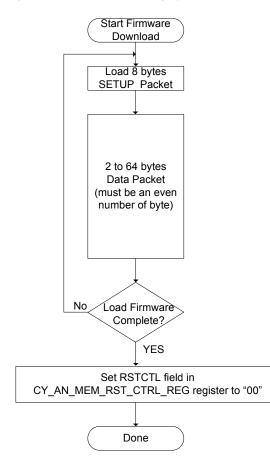

Astoria implements one vendor-specific request: 'Firmware Load,' 0xA0. (The bRequest value of 0xA0 is valid only if byte 0 of the request, bmRequestType, is also 'x10xxxxx,' indicating a vendor-specific request.) The 0xA0 firmware load request may be used even after ReNumeration<sup>™</sup>, but is only valid while the 8051 is held in reset. If your application implements vendor-specific USB requests, and you do not want to use the Firmware Load feature, do not use the bRequest value 0xA0 for your custom requests. The Firmware Load feature is fully described in the Enumeration and ReNumeration<sup>™</sup> chapter on page 35.

To avoid future incompatibilities, vendor requests 0xA0 to 0xAF are reserved by Cypress Semiconductor.

#### 2.2.1 Get Status

The USB Specification defines three USB status requests. A fourth request, to an interface, is declared in the specification as 'reserved'. The four status requests are:

- Remote Wakeup (device request)

- Self-Powered (device request)

- Stall (endpoint request)

- Interface request (reserved)

Astoria automatically asserts the SUDAV interrupt to tell the firmware to decode the SETUP packet and supply the appropriate status information.

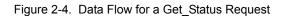

As Figure 2-4 shows, the firmware responds to the SUDAV interrupt by decoding the eight bytes Astoria has copied into RAM at SETUPDAT. The firmware answers a Get Status request (bRequest = 0) by loading two bytes into the EP0BUF buffer and loading the byte count register EP0BCH:L with the value 0x0002. Astoria then transmits these two bytes in response to an IN token. Finally, the firmware clears the HSNAK bit (by writing '1' to it), which instructs Astoria to ACK the status stage of the transfer.

The following tables show the eight SETUP bytes for Get Status Requests.

Table 2-3. Get Status-Device (Remote Wakeup and Self-Powered Bits)

| Byte | Field         | Value | Meaning    | Firmware<br>Response            |

|------|---------------|-------|------------|---------------------------------|

| 0    | bmRequestType | 0x80  | IN, Device |                                 |

| 1    | bRequest      | 0x00  | Get Status | Load two bytes into             |

| 2    | wValueL       | 0x00  |            | EP0BUF:                         |

| 3    | wValueH       | 0x00  |            | Byte 0: bit 0 =<br>Self-Powered |

| 4    | wIndexL       | 0x00  |            | Byte 0: bit 1 =                 |

| 5    | wIndexH       | 0x00  |            | Remote Wakeup                   |

| 6    | wLengthL      | 0x02  | Two bytes  | Byte 1: zero                    |

| 7    | wLengthH      | 0x00  | requested  |                                 |

Get Status-Device queries the state of two bits, Remote Wakeup and Self-Powered. The Remote Wakeup bit shows whether the device is enabled to request remote wakeup (remote wakeup is explained in the Power Management chapter on page 59). The Self-Powered bit shows whether the device is self-powered (as opposed to USB bus-powered).

The firmware returns these two bits by loading two bytes into EP0BUF, then loading a byte count of 0x0002 into EP0BCH:L.

| Byte | Field         | Value | Meaning                            | Firmware<br>Response                |

|------|---------------|-------|------------------------------------|-------------------------------------|

| 0    | bmRequestType | 0x82  | IN, Endpoint                       |                                     |

| 1    | bRequest      | 0x00  | Get Status                         |                                     |

| 2    | wValueL       | 0x00  |                                    |                                     |

| 3    | wValueH       | 0x00  |                                    | Load two bytes into<br>EP0BUF:      |

| 4    | wIndexL       | EP    | 0x00-0x08:                         | Byte 0: bit 0 =                     |

| 5    | wIndexH       | 0x00  | OUT0-OUT8<br>0x80-0x88:<br>IN0-IN8 | Stall Bit for EP(n)<br>Byte 1: zero |

| 6    | wLengthL      | 0x02  | Two bytes                          |                                     |

| 7    | wLengthH      | 0x00  | requested                          |                                     |

Table 2-4. Get Status-Endpoint (Stall Bits)

Each endpoint has a STALL bit in its EPxCS register. If this bit is set, any request to the endpoint returns a STALL hand-

shake rather than ACK or NAK. The Get Status-Endpoint request returns the STALL state for the endpoint shown in byte 4 of the request. Note that bit 7 of the endpoint number EP (byte 4) specifies direction (0 = OUT, 1 = IN).

Endpoint zero is a CONTROL endpoint, which by USB definition is bidirectional. Therefore, it has only one stall bit.

#### About STALL

The USB STALL handshake means that something unexpected has happened. For instance, if the host requests an invalid alternate setting or tries to send data to a non-existent endpoint, the device responds with a STALL handshake over endpoint zero instead of ACK or NAK.

Stalls are defined for all endpoint types except ISOCHRO-NOUS, which does not employ handshakes. Every Astoria bulk endpoint has its own stall bit. The firmware sets the stall condition for an endpoint by setting the stall bit in the endpoint's EPxCS register. The host tells the firmware to set or clear the stall condition for an endpoint using the Set Feature/Stall and Clear Feature/Stall requests.

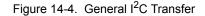

The device can also set the stall condition on its own. For example, in a routine that handles endpoint zero device requests, the firmware stalls EP0 when a request that is not defined or not supported is decoded.