**Application note**

#### **Document information**

| Information | Content                                                                                  |

|-------------|------------------------------------------------------------------------------------------|

| Keywords    | Power supply, clock source, reset, host interface, RF interface, PCB layout, PCB stackup |

| Abstract    | Provides design guidelines for IW416 device.                                             |

Revision history

| Rev | Date     | Description     |

|-----|----------|-----------------|

| v.1 | 20210526 | Initial version |

# 1 Overview

This document provides design guidelines for NXP IW416 device. The IW416 is a highly integrated Wi-Fi<sup>®</sup> 4 (2.4 GHz/5 GHz) and Bluetooth<sup>®</sup> 5.1 single-chip solution.

The IW416 is available in two package options - QFN and WLCSP.

NXP releases reference designs to provide examples on how to design a PCB using the device. We strongly recommend follow these design guidelines closely. Please contact your NXP representative to schedule a design review and discuss design options.

Note: In the following sections, the IW416 may be referred to as "Wireless SoC"

# 2 Power supply

#### 2.1 Power supply overview

Table 1 lists the power supplies.

| Supply | Description              | Typical value  |

|--------|--------------------------|----------------|

| VCORE  | Core power supply        | 1.05 V         |

| AVDD18 | Analog power supply      | 1.8 V          |

| VPA    | Wi-Fi PA power supply    | 2.2 V          |

| VIO    | Digital I/O power supply | 1.8 V or 3.3 V |

| VIO_SD | SDIO power supply        | 1.8 V or 3.3 V |

| VIO RF | RF power supply          | 1.8 V or 3.3 V |

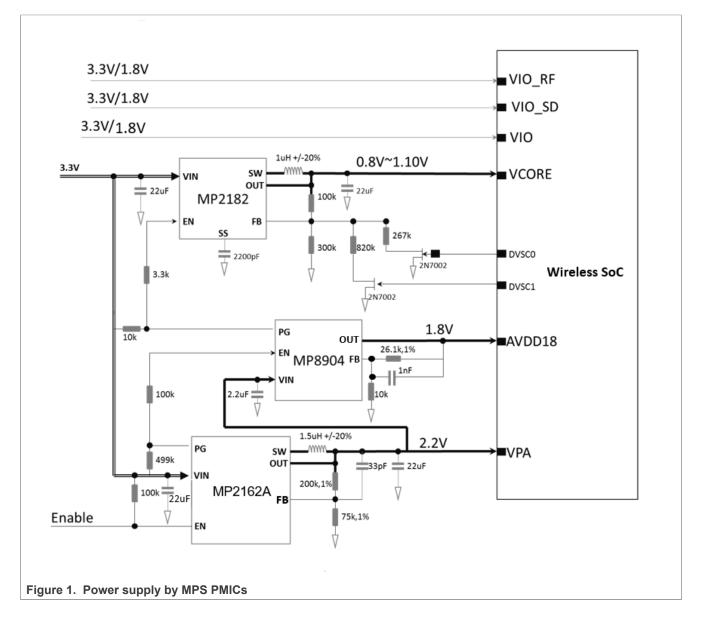

A "2-wire" power management interface is used to lower the core voltage to reduce power consumption in sleep mode. The power management interface uses two control signals, DVSC1 and DVSC0, to dynamically adjust the voltage level from the power management IC (PMIC). Under normal operation, the core voltage level is 1.05 V. In sleep mode, the core voltage is dropped to 0.8 V.

The following sections describe PMIC solutions from MPS, NXP, and Marvell manufacturers:

- MPS: MP2182, MP2162A, MP8904

- Marvell 88PG823

- NXP PM823

## 2.2 Power supply using MPS PMICs

<u>Figure 1</u> shows a simplified block diagram using the MPS MP2182, MP2162A and MP8904. Two control signals, DVSC1 and DVSC0, are used to control the core voltage level. <u>Table 2</u> shows the part numbers.

#### Table 2. MPS PMICs part numbers

| Manufacturer | Part number              |

|--------------|--------------------------|

| MPS          | BUCK: MP2162AGQH-C867-Z  |

| MPS          | BUCK: MP2182GTL-C867-Z   |

| MPS          | BUCK: MP8904DD-C867-LF-Z |

AN13125 Application note

### 2.3 Power supply using NXP PM823 or Marvell 88PG823

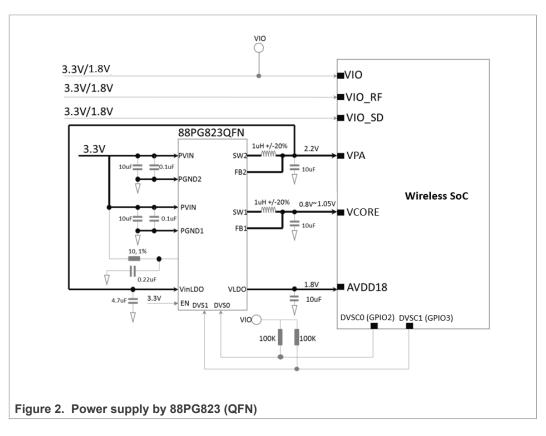

Figure 2 shows a simplified block diagram using the NXP PM823 or Marvell 88PG823 (QFN). Two control signals, DVSC1 and DVSC0, are used to control the core voltage level. Table 3 shows the part numbers.

| Table 3. | Marvell and | NXP PMICs | part numbers  |

|----------|-------------|-----------|---------------|

|          | mai von ana |           | part mannooro |

| Manufacturer | Part number                             |

|--------------|-----------------------------------------|

| Marvell      | QFN package option: 88PG823-xx-NPD2C000 |

| Marvell      | WLCSP package option: 88PG823-xx-CBK2-T |

| NXP          | QFN package option: PM823HN/A0CHP       |

| NXP          | WLCSP package option: PM823UK/A0CZ      |

### 2.4 Power-up sequence requirements

All the power rails must meet correct power-up sequence. Refer to IW416 data sheet.

## 2.5 PCB layout guidelines

Refer to the following PCB layout guidelines for power supply.

- Follow the PMIC schematic/layout exactly. Any deviation must be reviewed with PMIC vendor Applications Engineer.

- Use power planes (layer) and polygons to lower the power impedance.

- Use decoupling capacitors with low ESR

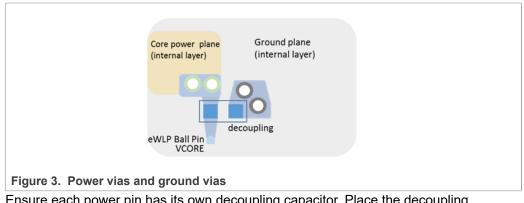

- Place the power vias and ground vias as close as possible to the decoupling capacitors, as shown in Figure 3.

- Ensure each power pin has its own decoupling capacitor. Place the decoupling capacitors as close as possible to the power pin.

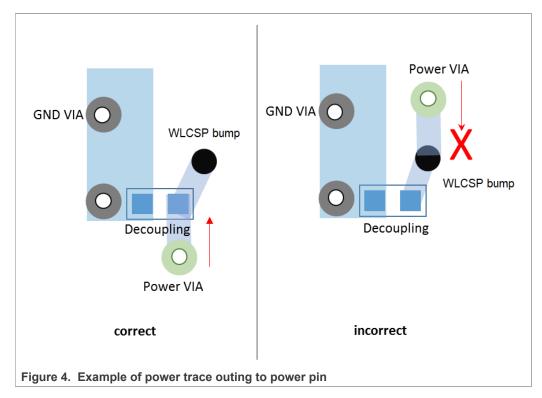

- The power from source to the power pin should go through the decoupling network before connecting to the power pin. As shown in <u>Figure 4</u>

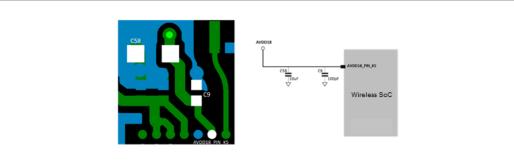

• There is a decoupling capacitor for each power pin and a bulk capacitor for each rail. Place the decoupling capacitor as close as possible to the power pin, then place the bulk capacitor. <u>Figure 5</u> shows an example where C9 is the decoupling capacitor for K5 pin. In this example, place C9 as close as possible to K5 pin, and place C58 close to C9.

Figure 5. Decoupling capacitor and bulk capacitor placements

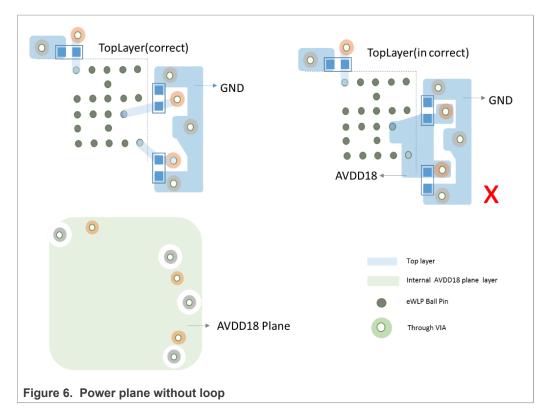

• Do not place any analog power plane (trace) as ring and loop in the layout. Figure 6 shows the correct top layer (left hand side of the figure) and the incorrect top layer (right hand side). In the correct top layer, there is no loop on the AVDD18 net.

### 3 Clock source

Two main clock sources are available: a crystal, and an external oscillator. An optional sleep clock is also available for low power mode.

#### 3.1 Crystal

In a typical application, a 26 MHz or 40 MHz crystal is used as a reference clock source. We recommend to select a crystal with  $\pm 10$  ppm at 25°C and  $\pm 10$  ppm over the operating temperature range. For detailed crystal specifications, refer to IW416 data sheet.

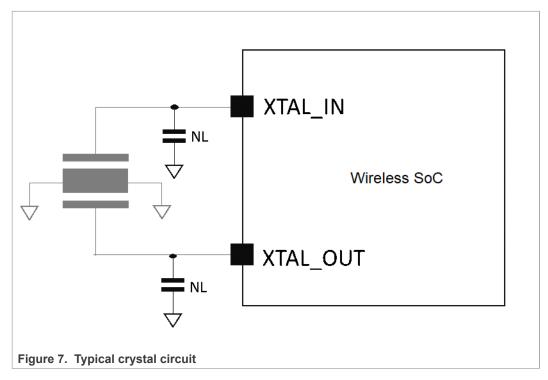

<u>Figure 7</u> shows the crystal connections. The internal capacitor in the Wireless SoC is used to tune the crystal frequency. External loading capacitors are typically not needed.

#### PCB layout guidelines for the crystal

Refer to the following guidelines for the crystal:

- Place the crystal close to the device and keep it as far away as possible from the RF side of the device and high frequency signal traces such as SDIO, PCIe, or USB.

- Keep XTAL\_IN and XTAL\_OUT traces far from any noisy or switching signal, at a distance of at least ten times the substrate height.

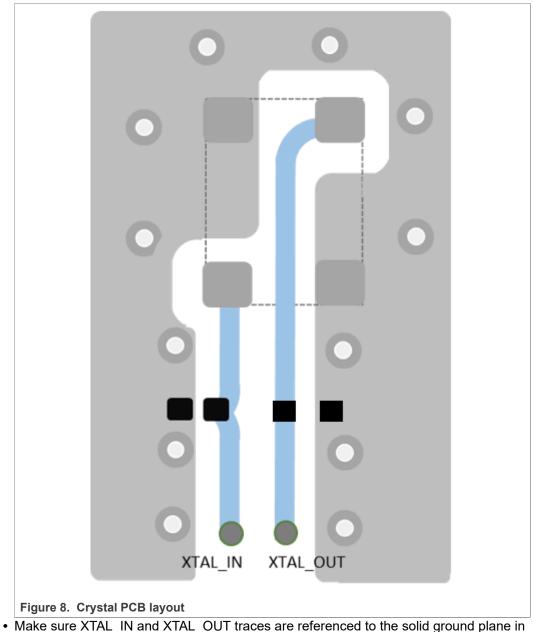

• Keep XTAL\_IN and XTAL\_OUT traces as short as possible, as shown in Figure 8.

- Make sure XTAL\_IN and XTAL\_OOT traces are referenced to the solid ground plane in the second layer.

Place the ground guard with ground stitching vias around the XTAL\_IN and XTAL\_OUT.

- Place the ground guard with ground stitching vias around the XTAL\_IN and XTAL\_OUT traces, as shown in <u>Figure 8</u>.

- To minimize the reference clock signals, cut out all internal metal planes under the crystal and keep the last ground plane as the reference plane.

### 3.2 External oscillator

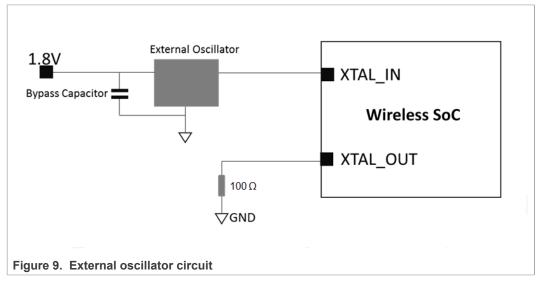

Figure 9 shows the typical application circuit for an external oscillator.

An external 26 MHz external oscillator may be used as reference clock source. If using an external oscillator, make sure its frequency accuracy meets the ±20 ppm IEEE specification over the operating temperature range of the product. Refer to IW416 data sheet for the oscillator requirement specification.

#### PCB layout guidelines for the external oscillator

- Follow the external oscillator vendor's recommendations for the layout.

- Place the oscillator as far as possible from the Wireless SoC RF side.

- Keep the clock trace as short as possible.

- Ground the guard trace with the ground via around the clock trace.

#### 3.3 Sleep clock

An optional external sleep clock may be used to further reduce the power consumption in sleep mode.

Note the following:

- The external sleep clock frequency is 32.768 kHz.

- The external sleep clock usage is optional

- If an external sleep clock is not used, it is recommended to leave the SLP\_CLK\_IN pin floating.

## 4 Reset

#### 4.1 Reset overview

Power on reset (POR) is triggered when the correct power up sequence is followed. Refer to IW416 data sheet for details on power up sequence requirements.

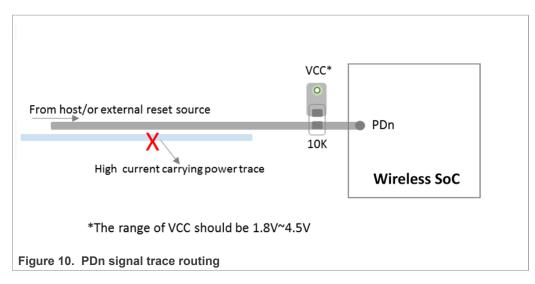

The PDn signal is used to reset the Wireless SoC. On the NXP reference design, the PDn signal is pulled up to VIO to meet the power-up sequence requirements. The PDn pin may be connected to a reset signal from the host CPU. Refer to IW416 data sheet for further details on PDn usage.

#### 4.2 Reset strap configuration

It is critical to set the reset configuration pins correctly at reset to ensure the proper configuration for the Wireless SoC. Refer to IW416 data sheet for details on the configuration pins and host configuration options.

#### 4.3 PCB layout guidelines

- Do not route PDn signal next to a large switching signal or on the edge of the PCB to avoid EMI affecting the reset signal, as shown in <u>Figure 10</u>.

- The pull-up resistor on the external reset signal is placed close to PDn pin.

# 5 Host interface

Table 4 lists the supported host interfaces.

| Table 4. Wi-Fi and Bluetooth host interfaces |           |

|----------------------------------------------|-----------|

| Wi-Fi                                        | Bluetooth |

| SDIO 3.0                                     | UART      |

#### 5.1 SDIO interface

The SDIO interface has the following characteristics:

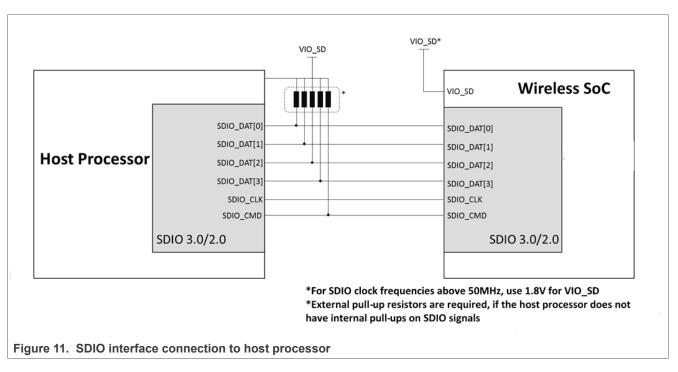

- SDIO v3.0 is backward compatible with SDIO v2.0 HOST. SDIO 3.0 is recommended for maximum throughput.

- For SDIO clock running at 25 MHz (SDR12) and 50 MHz (SDR25), VIO\_SD must be 3.3V.

- For SDIO clock running at > 50 MHz (SDR50 and DDR50), VIO\_SD must be 1.8V.

- SDIO clock (SD\_CLK) supports up to 208 MHz clock speed

- The required pull up for SDIO interface on SD\_CMD, and SD\_D[3:0] signals should be provided by the host. The pull up value is between 10 k $\Omega$  to 100 k $\Omega$  according to SDIO v3.0 specifications.

- Series damping resistors may be needed to help with signal integrity issues. When extending the SDIO signals through ribbon cable, series resistors of 75  $\Omega$  are recommended to reduce the undershoot/overshoot due to long trace run and cable impedance mismatch.

#### Figure 11 shows the SDIO interface connection to the host processor.

#### PCB layout guidelines for SDIO interface

Refer to the following PCB layout guidelines for SDIO interface:

- SDIO signals are routed with 50(±10%) ohm impedance

- · Route the SDIO signals as far away as possible from the RF trace

- Route all SDIO signal lines entirely over a solid ground plane. Avoid splits and voids on an adjacent layer.

- · Keep the same length for all SDIO signal traces and as short as possible.

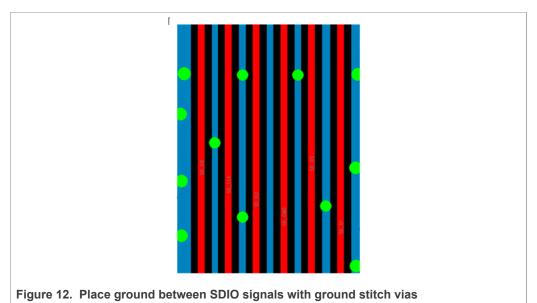

- Place the ground plane along with SDIO signals with stitch vias as shown in Figure 12.

- Avoid routing power supply traces under or above SDIO signal traces. If SDIO signal traces are routed on one of the inner layers, then make sure to shield them by having solid ground above and below SDIO traces.

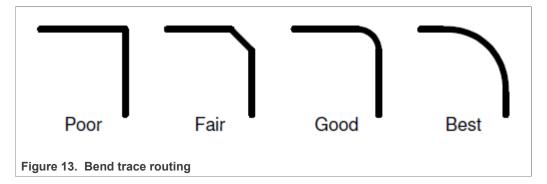

- The bend trace routing should be smooth with a large radius rather than of 90 degree with a sharp edge, as shown in Figure 13.

## 5.2 UART interface

Figure 14 shows a typical application circuit for the UART interface.

|                     |                       |   | Wireless SoC |

|---------------------|-----------------------|---|--------------|

| Host Processor      | UART UART_CTSn        |   | UART_RTSn    |

|                     | UART_RTSn             |   | UART_CTSn    |

|                     | UART_TX               |   | UART_SIN     |

|                     | UART_RX               |   | UART_SOUT    |

|                     |                       |   |              |

|                     |                       |   |              |

|                     |                       |   |              |

| igure 14. UART host | interface connections | 6 |              |

# 6 **RF** interface

The NXP reference designs for the Wireless SoC show the front-end configurations currently supported by NXP. It is recommended to discuss your desired front-end configuration with your NXP representative and have your design reviewed by NXP.

### 6.1 RF front-end for QFN package

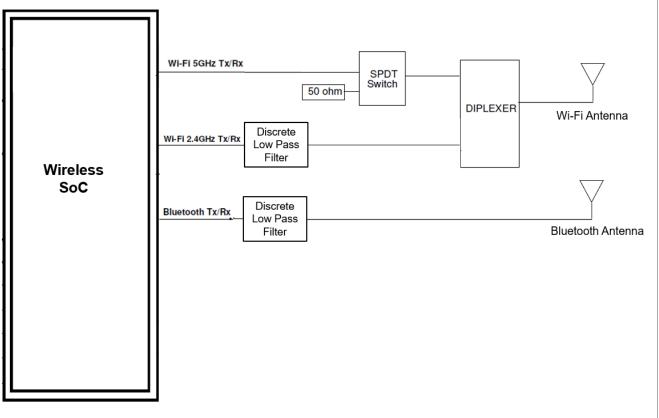

The QFN package can be used in single and dual antenna applications. In a dual antenna application, one antenna is for Wi-Fi and the other antenna is for Bluetooth. In a single antenna application, the antenna is shared between Wi-Fi and Bluetooth.

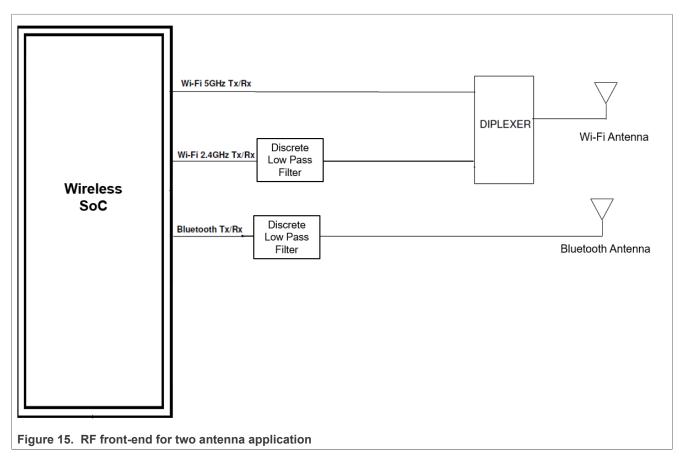

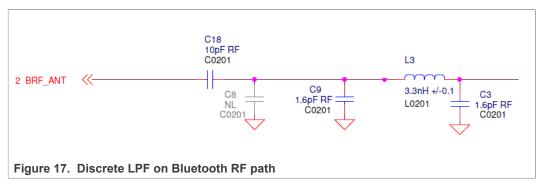

<u>Figure 15</u> shows the typical front-end topology for a two-antenna application. Use discrete low pass filters (LPF) to ensure the rejection of out-of-band emissions. LPF components also act as impedance matching circuits between the wireless SoC pin and the diplexer part on the PCB. For maximum power transfer in RF, the input/output impedance needs to match 50  $\Omega$ .

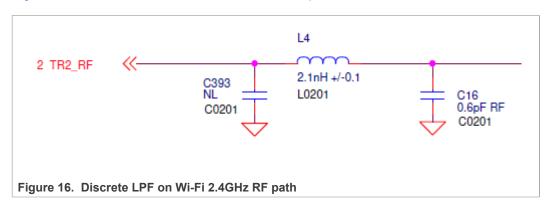

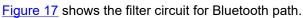

Figure 16 shows the filter circuit for Wi-Fi 2.4 GHz path.

For two antenna applications and where simultaneous 2.4 GHz Wi-Fi and Bluetooth transmission is possible, note the following recommendations:

- To reduce the impact of mutual interference, provide at least 30 dB isolation between the two antennas

- · Keep the antenna gain to a minimum, outside the 2.4 and 5 GHz bands

- In applications where the antenna isolation is limited, the transmit power level for the Bluetooth radio may need to be reduced. The transmit power level depends on various system design factors such as antenna gain and isolation.

Figure 18 shows the typical front-end topology for a single-antenna application. An external SPDT switch is required to combine the 2.4 GHz Wi-Fi and Bluetooth transmit/ receive paths. Use discrete low pass filters (LPF) to ensure the rejection of out-of-band emissions. LPF components also act as impedance matching circuits between the wireless SoC pin and the diplexer part on the PCB. For maximum power transfer in RF, the input/output impedance needs to match 50  $\Omega$ . Refer to Figure 16 for the filter circuit on Wi-Fi 2.4 GHz path.

#### <u>Table 5</u> lists the recommended RF front-end components.

| RF component                       | Manufacturer | Part number                                                        |

|------------------------------------|--------------|--------------------------------------------------------------------|

| Diplexer                           | TDK          | DPX166000DT-8093A1                                                 |

| SPDT switch                        | SKYWORKS     | SKY13323-378LF                                                     |

| Discrete LPF on Wi-Fi 2.4 GHz path | —            | L = 2.1 nH ± 0.1 nH (0201), C = 0.6 pF (0201)                      |

| Discrete LPF on Bluetooth path     | —            | C= 1.6 pF (0201), L = 3.3 nH ± 0.1 nH (0201), C<br>= 1.6 pF (0201) |

AN13125 Application note

### 6.2 RF front-end for WLCSP package

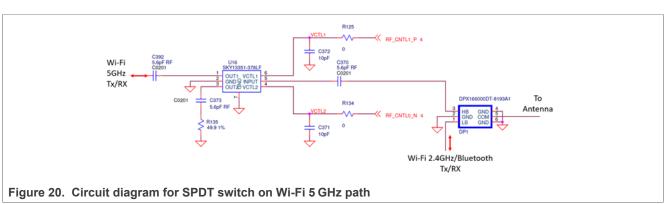

Similar to QFN package, WLCSP package can also be configured as single or dual antenna front-end application. WLCSP package requires an external RF SPDT switch on 5 GHz Wi-Fi path to provide additional rejection to out-of-band emissions. The following RF front-end components must be used to reduce out-of-band emissions.

- RF SPDT switch on Wi-Fi 5 GHz path

- Bandpass-bandpass structure diplexer

Figure 19 shows a typical front-end topology for dual antenna applications.

Figure 19. RF front-end with dual antenna applications

Use discrete low pass filters (LPF) to ensure the rejection of out-of-band emissions. LPF components also act as impedance matching circuits between the wireless SoC pin and the diplexer part on the PCB. For maximum power transfer in RF, the input/output impedance needs to match 50  $\Omega$ . Refer to Figure 16 for filter circuit on Wi-Fi 2.4 GHz path and Figure 17 for the filter circuit on Bluetooth path.

#### Figure 20 shows the circuit diagram for SPDT switch on Wi-Fi 5 GHz path.

Table 6 shows the list of recommended RF front-end components.

Table 6. Recommended RF front-end components

| RF component                       | Manufacturer | Part number                                                        |

|------------------------------------|--------------|--------------------------------------------------------------------|

| Diplexer                           | TDK          | DPX166000DT-8193A1                                                 |

| SPDT switch                        | SKYWORKS     | SKY13323-378LF                                                     |

| Discrete LPF on Wi-Fi 2.4 GHz path |              | L = 2.1 nH ± 0.1 nH (0201), C = 0.6 pF (0201)                      |

| Discrete LPF on Bluetooth path     | _            | C= 1.6 pF (0201), L = 3.3 nH ± 0.1 nH (0201), C<br>= 1.6 pF (0201) |

AN13125

IW416 Design Guide

IW416 Design Guide

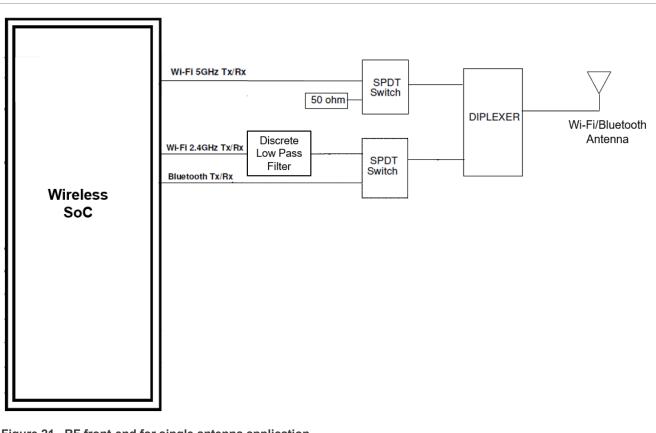

For single antenna designs, use the second SPDT switch to combine Wi-Fi 2.4 GHz and Bluetooth transmit/receive paths.

Figure 21 shows a typical front-end topology for single antenna applications.

Figure 21. RF front-end for single antenna application

Use discrete low pass filters (LPF) to ensure the rejection of out-of-band emissions. LPF components also act as impedance matching circuits between the wireless SoC pin and the diplexer part on the PCB. For maximum power transfer in RF, the input/output impedance needs to match 50  $\Omega$ . Refer to Figure 16 for the filter circuit on Wi-Fi 2.4 GHz path.

Keep the antenna gain to a minimum, outside the 2.4 GHz and 5 GHz bands. An RF shield is recommended to minimize radiated emissions and any RF interference.

### 6.3 PCB layout guidelines

Refer to the following PCB layout guidelines for RF interface:

- Route the RF signals on the top layer (micro strip) with 50 ohm impedance.

- Reference the RF signals to a solid ground plane.

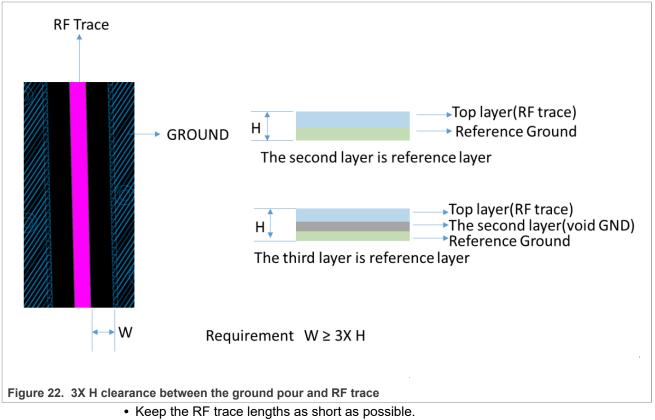

- Use at least a 3X H clearance between the ground pour and RF micro strip to minimize the impact on the micro strip impedance. Maintain this gap around any RF signal via, as shown in Figure 22.

• The bend trace routing should be smooth with a large radius rather than of 90 degree with a sharp edge.

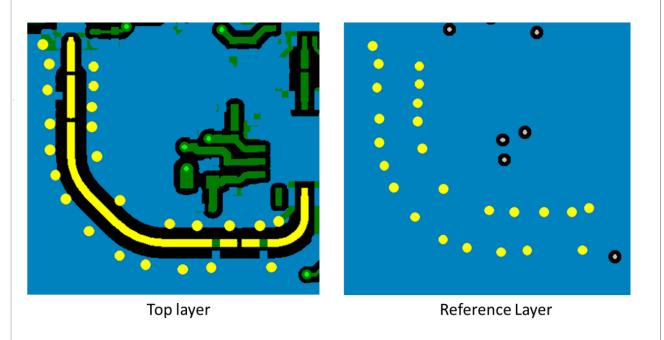

• Place stitching vias between the top and reference ground layers to increase isolation as shown in Figure 23.

Figure 23. Ground pour with stitching vias

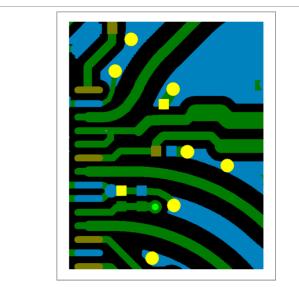

• Extend the ground plane between paths as much as possible. Extend the ground to the point where a ground via can be placed at the end, as shown in Figure 24.

Figure 24. Ground pour along with RF trace end with a ground via

- Keep the RF control signal traces as far away as possible from the RF traces.

- Follow the manufacturer's recommendations for RF front-end parts that require matching networks.

- RF ground via along the RF shield must be less than 100 mil interval.

- Ground via must be close to the matching capacitor ground pin.

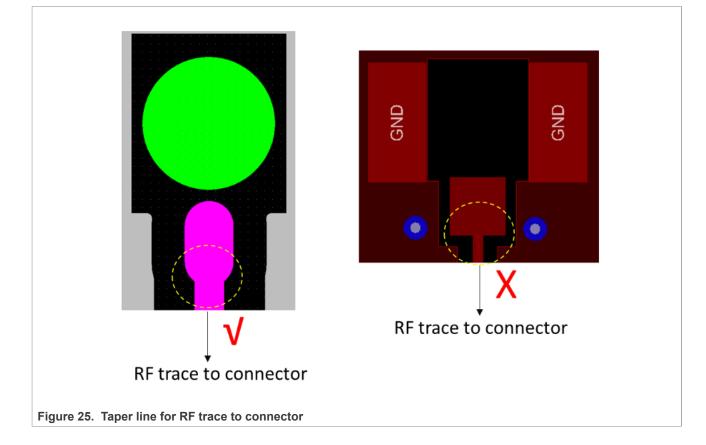

• RF trace to RF connector pad transition must be tapered to avoid discontinuity and high insertion loss, especially at 5 GHz band. An example is shown in Figure 25.

• We recommend to place a non-plated through hole under the RF connector to minimize the insertion loss as shown in <u>Figure 26</u>.

Figure 26. Non-plated through hole under the RF connector

- Add a ground via on each side of RF via near the RF trace layer transition, the distance between the via and RF trace edge to edge is about 20 mil.

- Add ground vias close to the diplexer ground pins for a good return path.

- If an ESD protection inductor is required, place the inductor close to the RF connector or close to the ESD sensitive front-end component.

- An RF shield is recommended to minimize radiated emissions and any RF interference.

- Avoid clock signal routes (system clock, SDIO\_CLK, SLP\_CLK) crossing the power supply traces or vice-versa.

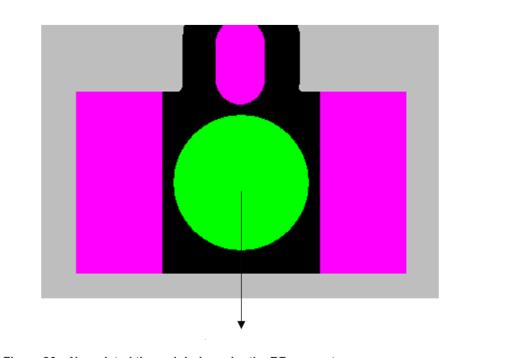

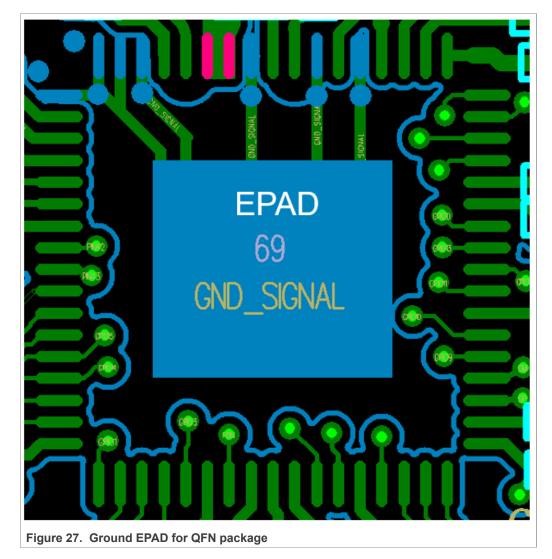

- For QFN package only, add a ground EPAD under the package for thermal relief as shown in Figure 27.

- Make sure the GND EPAD has a good number of thermal vias for the thermal path to be effective.

• For the WLCSP package only, do not route any signal traces, power planes, ground planes over the on-chip inductor keep-out areas. The on-chip inductor keep-out areas are highlighted in Figure 28.

For additional details, refer to DXF drawing layer included in Wireless SoC WLCSP reference design PCB layout file on NXP website.

# 7 Miscellaneous

# 7.1 Unused interfaces and pins

Table 7 shows the PCB connection for unused pins.

| Table 7. Unused pins          |                                       |

|-------------------------------|---------------------------------------|

| Pin name                      | PCB connection when not used          |

| LDO_VIN                       | Connect to ground                     |

| LDO_VOUT                      | Keep floating/No connect              |

| SLP_CLK_IN                    | Keep floating/No connect              |

| XTAL_OUT                      | Connect a 100 Ω resistor to ground    |

| RF_TR_2 or RF_TR_5 or BRF_ANT | Connect a 50 Ω resistor to ground     |

| RF_CNTL                       | Keep floating/No connect              |

| VPA                           | Connect to 2.2 V supply rail          |

| VIO_SD                        | Connect to 1.8 V supply rail          |

| VIO_RF                        | Connect to 1.8 V or 3.3 V supply rail |

#### Table 8 shows the PCB connection for unused interfaces.

| Table 8. Unused interfaces |                              |

|----------------------------|------------------------------|

| Interface                  | PCB connection when not used |

| SDIO interface             | Keep floating/No connect     |

| UART interface             | Keep floating/No connect     |

| PCM interface              | Keep floating/No connect     |

| WCI-2 interface            | Keep floating/No connect     |

## 7.2 GPIOs

Refer to IW416 data sheet for the typical function assigned to the GPIO pins.

### 7.3 PCB stackup

- Ensure the stackup is symmetrical.

- Ensure all layers meet specified thickness.

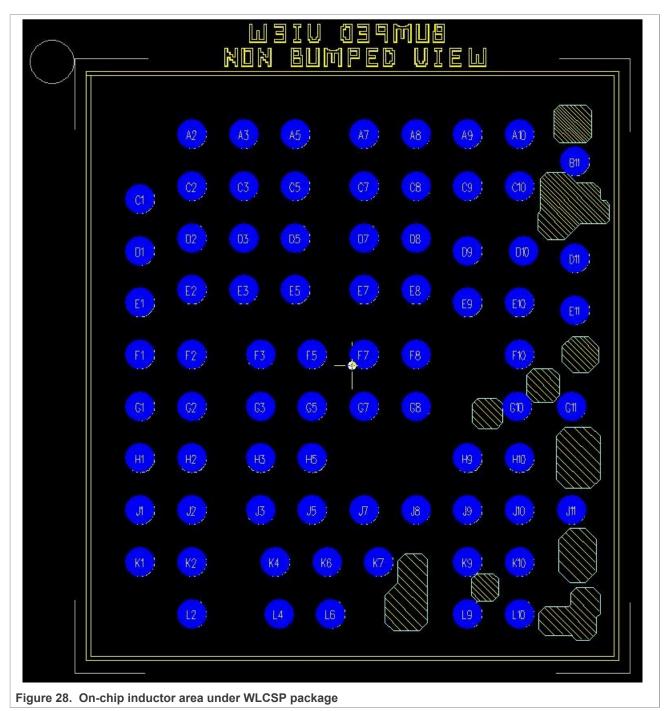

- For WLCSP package, NXP reference design PCB typically consists of six layers with FR-4 material and blind buried vias.

Figure 29 shows the typical 6 layer PCB stack up for WLCSP package

|                                                                | 3.                               | 6 LAYER STACKUP<br>(FOR REFERENCE ONLY)            |                 |

|----------------------------------------------------------------|----------------------------------|----------------------------------------------------|-----------------|

| SILKSCREEN (TOP SIDE)<br>SOLDERMASK (TOP SIDE)                 | 0.70 mil                         |                                                    |                 |

| LAYER 1 (TOP) 1/2 OZ + PLATING<br>LAYER 2 1 OZ<br>LAYER 3 1 OZ | 1.30 mil<br>1.30 mil             | PREPREG 5.697 mil CORE 5.910 mil PREPREG 6.542 mil | <br>]<br>40 mil |

| LAYER 4 1 OZ<br>LAYER 5 1 OZ<br>LAYER 6 (BOT) 1/2 OZ + PLATING | 1.30 mil<br>1.30 mil<br>1.50 mil | CORE 5.910 mil                                     | ]               |

| SOLDERMASK (BOTTOM SIDE)<br>SILKSCREEN (BOTTOM SIDE)           | 0.70 mil ——<br>——                |                                                    |                 |

| Figure 29. PCB stackup for WLCSP pack                          | age                              |                                                    |                 |

IW416 Design Guide

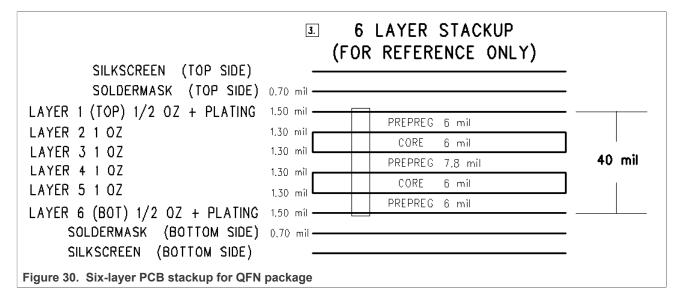

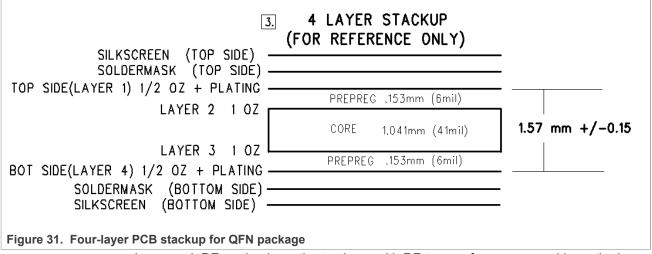

For QFN package, NXP reference design PCB can be of four to six layers with FR-4 material and plated through hole vias

Figure 30 shows the typical six-layer PCB stack up for QFN package.

Figure 31 shows the typical four-layer PCB stackup for QFN package.

In general, RF routing is on the top layer with RF trace reference ground is on the layer 2

# 8 Legal information

## 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 8.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or

the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security - Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

## 8.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

# **Tables**

| Tab. 1. | Power supplies4                     |  |

|---------|-------------------------------------|--|

|         | MPS PMICs part numbers5             |  |

| Tab. 3. | Marvell and NXP PMICs part numbers  |  |

| Tab. 4. | Wi-Fi and Bluetooth host interfaces |  |

# **Figures**

| ower supply by MPS PMICs5                  |

|--------------------------------------------|

| ower supply by 88PG823 (QFN)6              |

| ower vias and ground vias7                 |

| kample of power trace outing to power pin7 |

| ecoupling capacitor and bulk capacitor     |

| acements8                                  |

| ower plane without loop8                   |

| /pical crystal circuit9                    |

| rystal PCB layout10                        |

| ternal oscillator circuit11                |

| On signal trace routing12                  |

| DIO interface connection to host           |

| ocessor13                                  |

| ace ground between SDIO signals with       |

| ound stitch vias14                         |

| end trace routing14                        |

| ART host interface connections15           |

| F front-end for two antenna application 16 |

| screte LPF on Wi-Fi 2.4GHz RF path 17      |

| screte LPF on Bluetooth RF path 17         |

|                                            |

| Tab. 5. | Recommended RF front-end components18 |

|---------|---------------------------------------|

| Tab. 6. | Recommended RF front-end components20 |

| Tab. 7. | Unused pins                           |

| Tab. 8. | Unused interfaces28                   |

| Fig. 18. | RF Front-end for single antenna application | 18 |

|----------|---------------------------------------------|----|

| Fig. 19. | RF front-end with dual antenna applications | 19 |

| Fig. 20. | Circuit diagram for SPDT switch on Wi-Fi    |    |

|          | 5 GHz path                                  | 20 |

| Fig. 21. | RF front-end for single antenna application | 21 |

| Fig. 22. | 3X H clearance between the ground pour      |    |

|          | and RF trace                                | 22 |

| Fig. 23. | Ground pour with stitching vias             | 23 |

| Fig. 24. | Ground pour along with RF trace end with    |    |

|          | a ground via                                | 23 |

| Fig. 25. | Taper line for RF trace to connector        | 24 |

| Fig. 26. | Non-plated through hole under the RF        |    |

|          | connector                                   | 25 |

| Fig. 27. | Ground EPAD for QFN package                 | 26 |

| Fig. 28. | On-chip inductor area under WLCSP           |    |

|          | package                                     | 27 |

| Fig. 29. | PCB stackup for WLCSP package               | 29 |

| Fig. 30. | Six-layer PCB stackup for QFN package       | 30 |

| Fig. 31. | Four-layer PCB stackup for QFN package      | 30 |

# Contents

| 1   | Overview                                | 3  |

|-----|-----------------------------------------|----|

| 2   | Power supply                            | 4  |

| 2.1 | Power supply overview                   | 4  |

| 2.2 | Power supply using MPS PMICs            |    |

| 2.3 | Power supply using NXP PM823 or Marvell |    |

|     | 88PG823                                 | 6  |

| 2.4 | Power-up sequence requirements          | 6  |

| 2.5 | PCB layout guidelines                   | 7  |

| 3   | Clock source                            |    |

| 3.1 | Crystal                                 | 9  |

| 3.2 | External oscillator                     |    |

| 3.3 | Sleep clock                             | 11 |

| 4   | Reset                                   | 12 |

| 4.1 | Reset overview                          | 12 |

| 4.2 | Reset strap configuration               | 12 |

| 4.3 | PCB layout guidelines                   | 12 |

| 5   | Host interface                          |    |

| 5.1 | SDIO interface                          | 13 |

| 5.2 | UART interface                          | 15 |

| 6   | RF interface                            | 16 |

| 6.1 | RF front-end for QFN package            | 16 |

| 6.2 | RF front-end for WLCSP package          |    |

| 6.3 | PCB layout guidelines                   |    |

| 7   | Miscellaneous                           | 28 |

| 7.1 | Unused interfaces and pins              |    |

| 7.2 | GPIOs                                   | 28 |

| 7.3 | PCB stackup                             | 29 |

| 8   | Legal information                       |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 26 May 2021 Document identifier: AN13125