# Relion 2840e

Versatile enterprise servers featuring the latest AMD technology

Technical Guide Rev. 1.0

www.penguincomputing.com | 1-888-PENGUIN (736-4846) | twitter:@PenguinHPC

# Intel<sup>®</sup> Server System H2000JF Family

**Technical Product Specification**

Intel order number: G39462-007

Revision 1.6 October, 2012 Enterprise Platforms and Services Division

# **Revision History**

| Date           | Revision Number | Modifications                                                                                                                                                                                                                                                |  |

|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| January, 2012  | 1.0             | Initial release.                                                                                                                                                                                                                                             |  |

| February, 2012 | 1.1             | Added environmental data.                                                                                                                                                                                                                                    |  |

| March, 2012    | 1.2             | Updated environmental specifications.                                                                                                                                                                                                                        |  |

| May, 2012      | 1.3             | <ul> <li>Updated environmental specifications with ASHRAE specification.</li> <li>Updated Processor TDP to conditional support 135W.</li> <li>Added new bridge board for 6G SAS support.</li> <li>Added riser support for non-transparent bridge.</li> </ul> |  |

| July, 2012     | 1.4             | <ul> <li>Updated safety notice to rail kit installation.</li> <li>Updated InfiniBand* usage recommendation.</li> </ul>                                                                                                                                       |  |

| August, 2012   | 1.5             | <ul> <li>Corrected typo in USB device beep in POST.</li> <li>Added new 6G SAS module solution.</li> <li>Updated power redundant scheme.</li> </ul>                                                                                                           |  |

| O, 2012        | 1.6             | <ul><li>Updated link to Rail specification.</li><li>Updated system specification.</li></ul>                                                                                                                                                                  |  |

## Disclaimers

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel<sup>®</sup>'s Terms and Conditions of Sale for such products, Intel<sup>®</sup> assumes no liability whatsoever, and Intel<sup>®</sup> disclaims any express or implied warranty, relating to sale and/or use of Intel<sup>®</sup> products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel<sup>®</sup> products are not intended for use in medical, lifesaving, or life sustaining applications. Intel<sup>®</sup> may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel<sup>®</sup> reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> Server System H2000JF Family may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This document and the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the express written consent of Intel Corporation.

Intel, Pentium and Xeon are trademarks or registered trademarks of Intel Corporation.

\*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2012. Portions Copyright © 2012 by LSI\* Corporation and Mellanox\* Corporation.

# Table of Contents

| 1. | Introduc | stion                                      | 1  |

|----|----------|--------------------------------------------|----|

| 1  | .1       | Chapter Outline                            | 1  |

| 1  | .2       | Server Board Use Disclaimer                | 2  |

| 2. | Product  | Overview                                   | 3  |

| 2  | .1       | System Views                               | 5  |

| 2  | .2       | System Dimensions                          | 5  |

| 2  | .3       | System Level Environmental Limits          | 6  |

| 2  | .4       | System Parts                               | 13 |

| 2  | .5       | Hard Drive and Peripheral Bays             | 14 |

| 2  | .6       | Server Board Overview                      | 15 |

| 2  | .7       | Front Bezel Support                        | 17 |

| 2  | .8       | Rack and Cabinet Mounting Options          | 17 |

| 3. | Power S  | Sub-System                                 | 19 |

| 3  | .1       | Mechanical Overview                        | 19 |

|    | 3.1.1    | AC Power Supply Unit Dimension Overview    | 19 |

|    | 3.1.2    | AC Power Supply Unit General Data          | 19 |

|    | 3.1.3    | AC input connector                         | 20 |

|    | 3.1.4    | AC Power Cord Specification Requirements   | 20 |

|    | 3.1.5    | Power Supply Unit DC Output Connector      | 20 |

|    | 3.1.6    | Handle Retention                           | 21 |

|    | 3.1.7    | LED Marking and Identification             | 21 |

|    | 3.1.8    | Power Cage with Power Distribution Board   | 21 |

|    | 3.1.9    | Power Cage Output Pin Assignment           | 22 |

| 3  | .2       | AC Input Specification                     | 24 |

|    | 3.2.1    | Input Voltage And Frequency                | 24 |

|    | 3.2.2    | AC input Power Factor                      | 24 |

|    | 3.2.3    | Efficiency                                 | 24 |

|    | 3.2.4    | AC Line Fuse                               | 25 |

|    | 3.2.5    | AC Line Inrush                             | 25 |

|    | 3.2.6    | AC Line Dropout/Holdup                     | 25 |

|    | 3.2.7    | AC Line Fast Transient (EFT) Specification | 25 |

|    | 3.2.8    | Hot Plug                                   | 26 |

|    | 3.2.9    | Susceptibility Requirements                | 26 |

|    | 3.2.10   | Electrostatic Discharge Susceptibility     | 26 |

|    | 3.2.11   | Fast Transient/Burst                       | 26 |

|    | 3.2.12   | Radiated Immunity                          | 26 |

|    | 3.2.13   | Surge Immunity                             | 26 |

|    | 3.2.14   | AC Line Transient Specification            |    |

|    | 3.2.15   | Power recovery                             | 27 |

| 3.2.16     | Voltage Interruptions                     | 27 |

|------------|-------------------------------------------|----|

| 3.2.17     | AC Line Isolation                         | 27 |

| 3.2.18     | AC Power Inlet                            | 27 |

| 3.3        | DC Ouput Specification                    | 28 |

| 3.3.1      | Output Power/Currents                     | 28 |

| 3.3.2      | Standby Output                            | 28 |

| 3.3.3      | Voltage Regulation                        | 28 |

| 3.3.4      | Dynamic Loading                           | 29 |

| 3.3.5      | Capacitive Loading                        | 29 |

| 3.3.6      | Ripple/Noise                              | 29 |

| 3.3.7      | Grounding                                 | 30 |

| 3.3.8      | Closed Loop Stability                     | 30 |

| 3.3.9      | Residual Voltage Immunity in Standby Mode | 30 |

| 3.3.10     | Common Mode Noise                         | 30 |

| 3.3.11     | Soft Starting                             | 30 |

| 3.3.12     | Zero Load Stability Requirement           | 31 |

| 3.3.13     | Hot Swap Requirement                      | 31 |

| 3.3.14     | Forced Load Sharing                       | 31 |

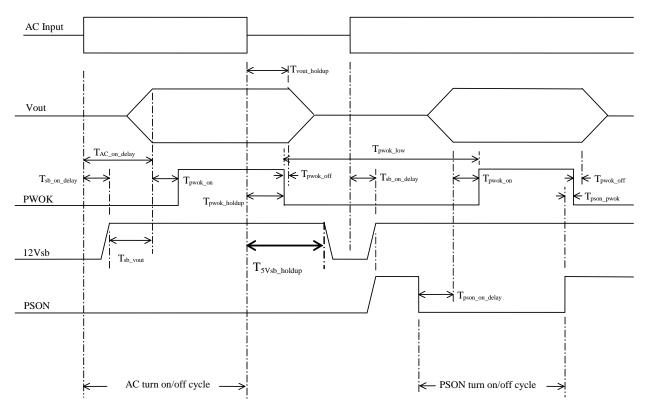

| 3.3.15     | Timing Requirement                        | 31 |

| 3.4        | Power Supply Cold Redundancy Support      | 32 |

| 3.4.1      | 1200W CRPS Cold Redundancy                | 33 |

| 3.4.2      | 1600W CRPS Cold Redundancy                | 33 |

| 3.5        | Control And Indicator Functions           | 33 |

| 3.5.1      | PSON# Input Signal                        | 33 |

| 3.5.2      | PWOK (power good) Output Signal           | 34 |

| 3.5.3      | SMBAlert# Signal                          | 34 |

| 3.6        | Protection circuits                       | 35 |

| 3.6.1      | Current Limit (OCP)                       | 35 |

| 3.6.2      | Over Voltage Protection (OVP)             | 35 |

| 3.6.3      | Over Thermal Protection (OTP)             | 36 |

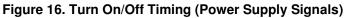

| 3.7        | PMBus*                                    | 36 |

| 3.7.1      | PSU Address Lines A0                      | 36 |

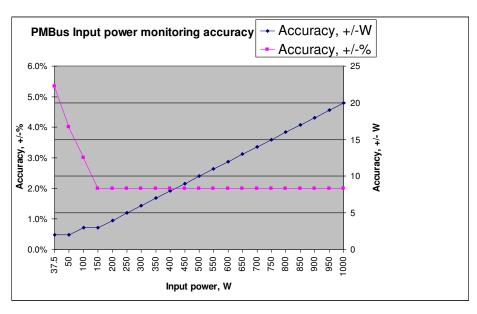

| 3.7.2      | Accuracy                                  |    |

| 3.8        | Power Management Policy                   |    |

| 4. Cooling | Sub-System                                |    |

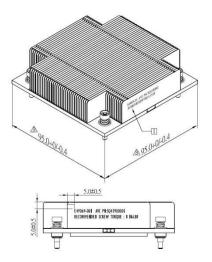

| 4.1        | Processor Heatsink                        | 39 |

| 4.2        | Node cooling Fans                         | 40 |

| 4.3        | Power Supply Fan                          |    |

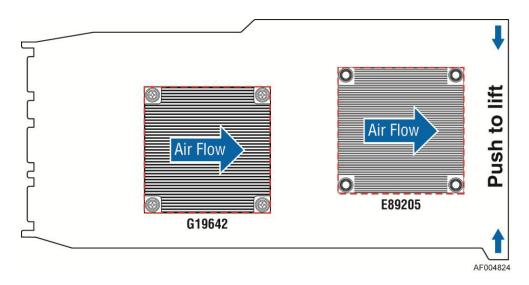

| 4.4        | Air Duct Module                           |    |

| 4.5        | Drive Bay Population Requirement          |    |

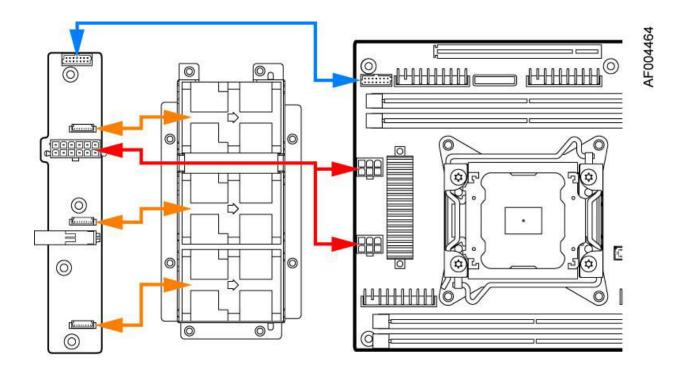

| 5. System  | Boards in the Node Tray                   | 43 |

| 5.1        | Node Docking Board                                        | 43 |

|------------|-----------------------------------------------------------|----|

| 5.1.1      | Overview of Node Docking Board                            | 43 |

| 5.1.2      | Pinout definition on Node Docking Board                   | 44 |

| 5.2        | Bridge Board                                              | 45 |

| 5.2.1      | Overview of Bridge Board                                  | 45 |

| 5.2.2      | Pinout definition on Bridge Board                         | 47 |

| 5.3        | 6Gbs SAS Support Option 1                                 |    |

| 5.3.1      | Overview of Bridge Board                                  | 48 |

| 5.3.2      | Pinout definition on SAS 6Gbs Bridge Board                | 50 |

| 5.4        | 6Gbs SAS Support Option 2                                 | 51 |

| 5.4.1      | Bridge Board                                              | 51 |

| 5.4.2      | Riser Card                                                | 53 |

| 5.4.3      | SAS Controller Module                                     | 55 |

| 6. Hard D  | isk Drive Support                                         | 57 |

| 6.1        | Hard Disk Drive Bays Scheme                               | 57 |

| 6.2        | Hard Drive Carrier                                        | 57 |

| 6.3        | Hot-Swap Hard Drive Support                               | 58 |

| 6.3.1      | Backplane Feature set:                                    | 59 |

| 6.3.2      | Backplane Block Diagram                                   | 60 |

| 6.3.3      | 3.5" Hot Swap Backplane Connector scheme                  | 60 |

| 6.3.4      | 2.5" Hot Swap Backplane Connector scheme                  | 61 |

| 6.3.5      | Backplane LED Support                                     | 62 |

| 6.3.6      | Backplane Connector Definition                            | 63 |

| 7. Front F | Panel Control and Indicators                              | 67 |

| 7.1        | Control Panel Button                                      | 68 |

| 7.2        | Control Panel LED Indicators                              | 68 |

| 7.2.1      | Power/Sleep LED                                           | 69 |

| 7.2.2      | System Status LED                                         | 69 |

| 7.2.3      | System Status LED – BMC Initialization                    | 70 |

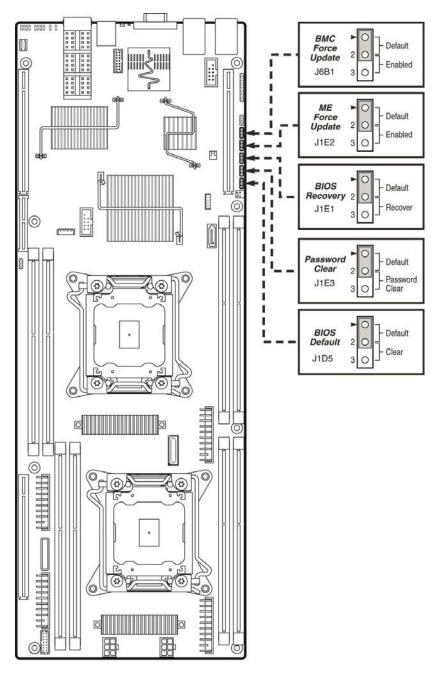

| 8. Config  | uration Jumpers                                           | 71 |

| 8.1        | Force Integrated BMC Update (J6B1)                        | 72 |

| 8.2        | Force ME Update (J1E2)                                    | 73 |

| 8.3        | Password Clear (J1E3)                                     | 74 |

| 8.4        | BIOS Recovery Mode (J1E1)                                 | 74 |

| 8.5        | Reset BIOS Settings (J1D5)                                | 75 |

| 9. PCI Ex  | press* Riser Card and Assembly                            | 77 |

| 9.1        | PCI Express* Riser for Slot 1                             | 77 |

| 9.1.1      | Overview of PCI-Express* Riser                            | 77 |

| 9.1.2      | Pinout definition on Slot 1 Riser                         | 77 |

| 9.2        | PCI Express* Riser with IOM Carrier for Slot 2 (Optional) | 82 |

| 9.2.1      | Overview of PCI-E* Riser with IOM Carrier                 | 82 |

|            |                                                           |    |

| 9.2.2 Pinout definition on Slot 2 Riser and IOM Carrier | 83  |

|---------------------------------------------------------|-----|

| Appendix A: Integration and Usage Tips                  |     |

| Appendix B: POST Code LED Decoder                       | 90  |

| Appendix C: Video POST Code Errors                      | 95  |

| Glossary                                                |     |

| Reference Documents                                     | 103 |

# List of Figures

| Figure 1. System Overview (Air Duct removed)                    | 5   |

|-----------------------------------------------------------------|-----|

| Figure 2. Compute Node Scheme (Rear View)                       | 5   |

| Figure 3. Fan Control Model                                     | .13 |

| Figure 4. Major System Parts                                    | .13 |

| Figure 5. Intel® Server System H2312JF Drive Bay Overview       | .14 |

| Figure 6. Intel® Server System H2216JF Drive Bay Overview       | .14 |

| Figure 7. Intel <sup>®</sup> Server Board S2600JFQ/S2600JFF     | .15 |

| Figure 8. Intel® Server Board S2600JF Components                | .16 |

| Figure 9. Back Panel Feature Overview                           | .16 |

| Figure 10. Light-Guided Diagnostic LED Locations                | .17 |

| Figure 11. System Bezel Front View                              | .17 |

| Figure 12. AC Power Supply Unit Dimension Overview              | .19 |

| Figure 13. Power Cage Overview                                  |     |

| Figure 14. Power distribution board                             | .23 |

| Figure 15. AC Power Cord Specification                          | 28  |

| Figure 16. Turn On/Off Timing (Power Supply Signals)            | .32 |

| Figure 17. Power Supply Device Address                          | 36  |

| Figure 18. PMBus* Monitoring Accuracy                           | 37  |

| Figure 19. Processor Heatsink Overview                          | 39  |

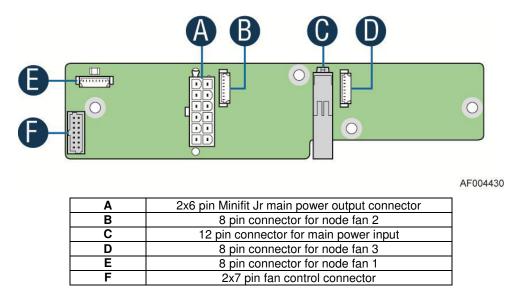

| Figure 20. Node Fan Set and power/control Connection            |     |

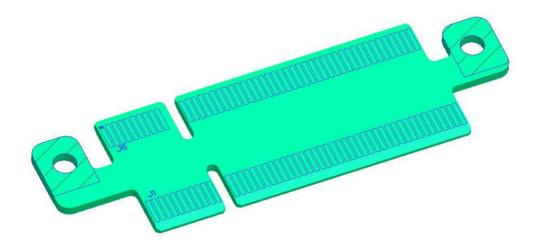

| Figure 21. Compute Node Air Duct (Top view)                     | .42 |

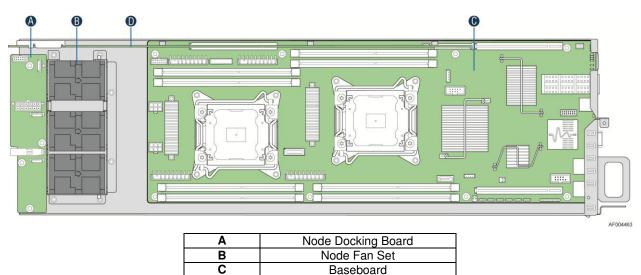

| Figure 22. Compute Node Tray Overview                           | .43 |

| Figure 23. Node Docking Board                                   | .43 |

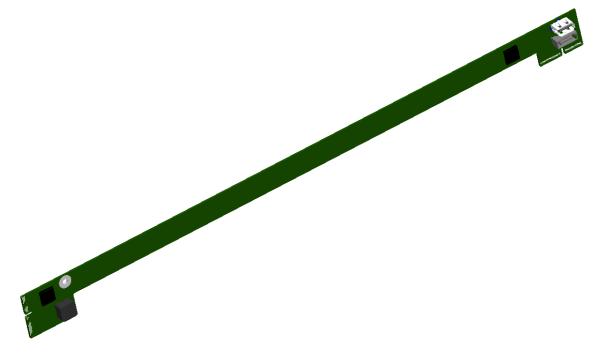

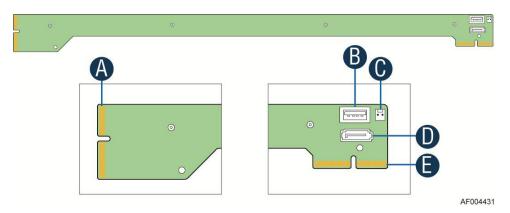

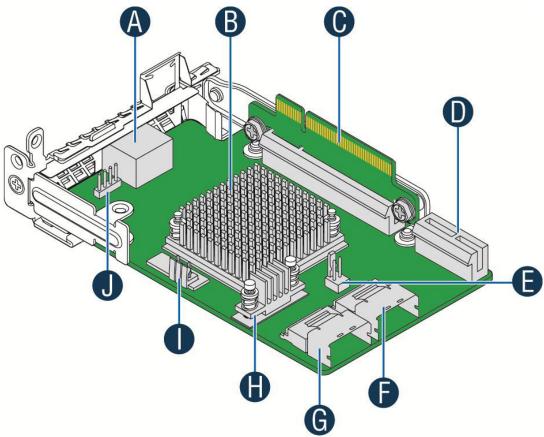

| Figure 24. Bridge Board Overview                                | .45 |

| Figure 25. Connectors on Bridge Board                           |     |

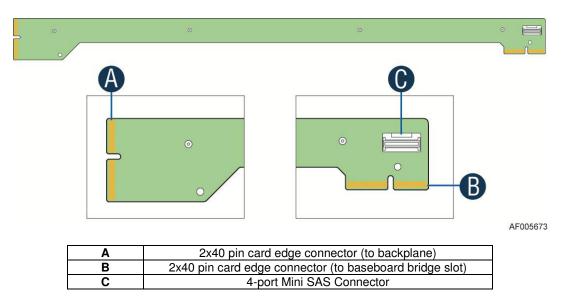

| Figure 26. SAS 6Gbs Bridge Board Overview                       | 49  |

| Figure 27. Connectors and components on Spare Bridge Board      | .50 |

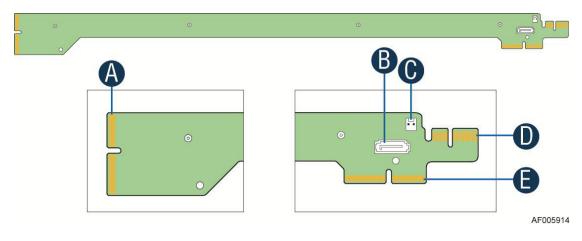

| Figure 28. Overview of the Bridge Board                         | .52 |

| Figure 29. Connectors on Bridge Board                           | .52 |

| Figure 30. Overview of the Riser Card                           | 53  |

| Figure 31. SAS Controller Module Overview                       | 56  |

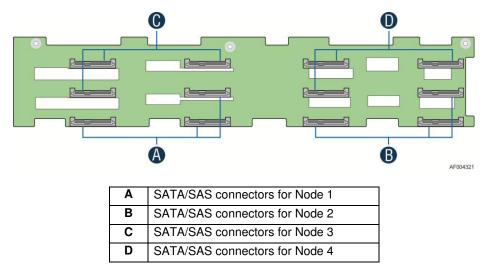

| Figure 32. HDD Scheme for H2312JF                               | 57  |

| Figure 33. HDD Scheme for H2216JF                               | 57  |

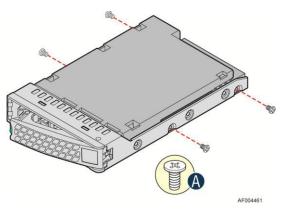

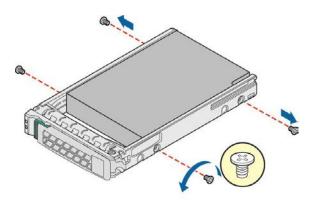

| Figure 34. 3.5-inch HDD Assembly Overview                       | 58  |

| Figure 35. 2.5-inch HDD Assembly Overview                       | 58  |

| Figure 36. Passive Backplane Block Diagram (for one node)       | .60 |

| Figure 37. 3.5" Backplane Component and Connectors (Front View) | 60  |

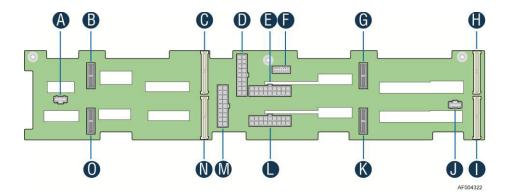

| Figure 38. 3.5" Backplane Component and Connectors (Back View)  | .61 |

|                                                                 |     |

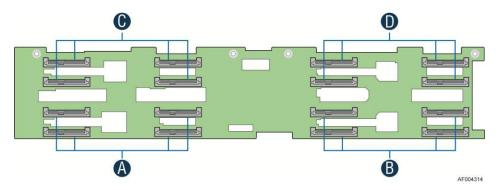

| Figure 39. 2.5" Backplane Component and Connectors (Front View) | 62 |

|-----------------------------------------------------------------|----|

| Figure 40. 2.5" Backplane Component and Connectors (Back View)  | 62 |

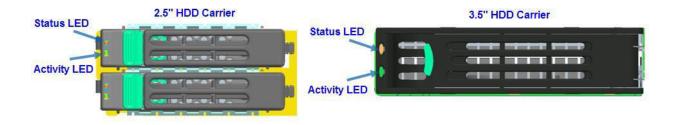

| Figure 41. Hard Drive Carrier LED                               | 63 |

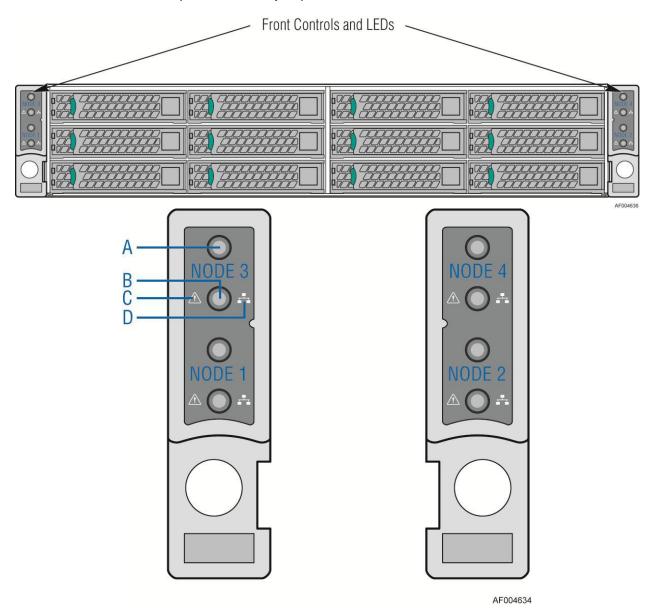

| Figure 42. Front Control Panel                                  | 67 |

| Figure 43. Jumper Locations and Functions                       | 71 |

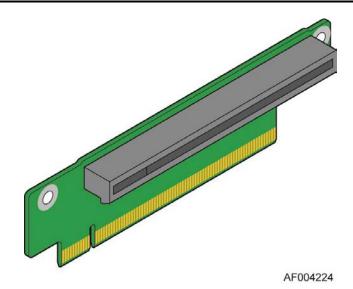

| Figure 44. PCI Express* Riser for Riser Slot 1                  | 77 |

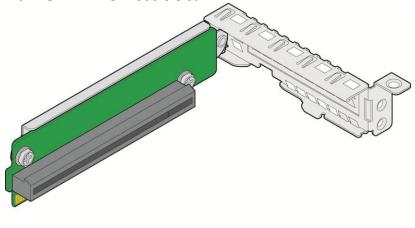

| Figure 45. PCI Express* Riser with bracket for Riser Slot 2     | 82 |

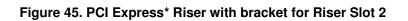

| Figure 46. IOM Carrier                                          | 82 |

| Figure 47. Diagnostic LED location                              | 90 |

# List of Tables

| Table 1. System Feature Set                                |    |

|------------------------------------------------------------|----|

| Table 2. System SKU matrix                                 |    |

| Table 3. Chassis Dimension (SKU: H2312JF)                  | 5  |

| Table 4. Chassis Dimension (SKU: H2216JF)                  | 6  |

| Table 5. System Environmental Limits Summary               |    |

| Table 6. Ambient Temperature versus System Configuration   | 9  |

| Table 7. Specification Data for AC Power Supply Unit       | 20 |

| Table 8. AC power cord specification                       | 20 |

| Table 9. DC Output Power Connector                         | 20 |

| Table 10. Power Supply Status LED                          | 21 |

| Table 11. Pin assignment of power ouput connector          | 23 |

| Table 12. Pin assignment of control signal connector       | 23 |

| Table 13. AC input rating                                  |    |

| Table 14. Typical power factor                             |    |

| Table 15. Platinum Efficiency Requirement                  | 25 |

| Table 16. AC Power Holdup Requirement                      |    |

| Table 17. Performance Criteria                             | 26 |

| Table 18. AC Line Sag Transient Performance                |    |

| Table 19. AC Line Surge Transient Performance              | 27 |

| Table 20. Load Ratings for single power supply unit        | 28 |

| Table 21. Voltage Regulation Limits                        |    |

| Table 22. Transient Load Requirements                      | 29 |

| Table 23. Capacitive Loading Conditions                    |    |

| Table 24. Ripple and Noise                                 | 29 |

| Table 25. Timing Requirement                               |    |

| Table 26. 1200W CRPS Cold Redundancy Threshold.            |    |

| Table 27. 1600W CRPS Cold Redundancy Threshold.            |    |

| Table 28. PSON# Signal Characteristics                     |    |

| Table 29. PWOK Signal Characteristics                      | 34 |

| Table 30. SMBAlert# Signal Characteristics                 |    |

| Table 31. Over Current Protection                          |    |

| Table 32. Over Voltage Protection (OVP) Limits             |    |

| Table 33. PSU addressing                                   |    |

| Table 34. PMBus* Accuracy                                  |    |

| Table 35. Power Management Policy                          |    |

| Table 36. 8-pin Connector Pin-Out for Node Dual Rotor Fans |    |

| Table 37. Main Power Input Connector                       | 44 |

| Table 38. | Fan Control Signal Connector                              | 44 |

|-----------|-----------------------------------------------------------|----|

| Table 39. | Node Fan Connector                                        | 44 |

| Table 40. | Main Power Output Connector                               | 45 |

| Table 41. | Card Edge Connector Pinout                                | 47 |

| Table 42. | AHCI SATA0 DOM Connector Pinout                           | 48 |

| Table 43. | USB 2.0 Type-A Connector Pinout                           | 48 |

| Table 44. | 5V_AUX Power Connector Pinout                             | 48 |

| Table 45. | Pinout of Card Edge to Base Board                         | 50 |

| Table 46. | Pinout of Card Edge to Hot Swap Back Plane                | 50 |

| Table 47. | Pinout of Mini SAS Connector                              | 51 |

| Table 48. | Card Edge Pinout of Bridge Board to SAS Controller        | 52 |

| Table 49. | Card Edge Pinout of Riser card to SAS Controller          | 53 |

| Table 50. | Card Edge Pinout of Riser card to PCIe Slot2 of Baseboard | 54 |

| Table 51. | Hard Drive Carrier Status LED Functions                   | 63 |

| Table 52. | Hard Drive Carrier Activity LED Functions                 | 63 |

| Table 53. | Backplane Input Power Connector Pin-out                   | 63 |

| Table 54. | 2-Blade Compute Node Power Connector Pin-out              | 64 |

| Table 55. | 2x40 Pin Connector Pin-out for Node Bridge Board          | 64 |

| Table 56. | Front Panel Connector Pin-out                             | 65 |

| Table 57. | Power Supply Control Connector Pin-out                    | 66 |

| Table 58. | Front Control Button Function                             | 68 |

| Table 59. | Front LED Indicator Functions                             | 68 |

| Table 60. | Power LED Operation                                       | 69 |

| Table 61. | System Status LED Operation                               | 69 |

| Table 62. | Force Integrated BMC Update Jumper                        | 72 |

| Table 63. | Force Integrated BMC Update Jumper                        | 72 |

| Table 64. | Force ME Update Jumper                                    | 73 |

| Table 65. | BIOS Password Clear Jumper                                | 74 |

| Table 66. | BIOS Recovery Mode Jumper                                 | 74 |

|           | Reset BIOS Jumper                                         |    |

| Table 68. | Riser Card Edge Pinout                                    | 77 |

| Table 69. | PCI Express* Slot Pinout on Riser Card                    | 80 |

| Table 70. | Dedicated NIC Port LED Functionality                      | 83 |

|           | Riser Card Edge Pinout                                    |    |

|           | PCI Express* Slot Pinout on Riser Card                    |    |

|           | IO Module Slot on Carrier                                 |    |

| Table 74. | POST Code Diagnostic LED Location                         | 90 |

|           | POST Progress Code LED Example                            |    |

|           | Diagnostic LED POST Code Decoder                          |    |

|           | POST Error Message and Handling                           |    |

| Table 78. | POST Error Beep Codes                                     | 99 |

<This page is intentionally left blank.>

## 1. Introduction

This Technical Product Specification (TPS) provides system specific information detailing the features, functionality, and high-level architecture of the Intel<sup>®</sup> Server System H2000JF family. You should also refer to the *Intel<sup>®</sup> Server Board S2600JF Family Technical Product Specification* to obtain greater detail of functionality and architecture of the server board integrated in this server system.

In addition, you can obtain design-level information for specific sub-systems by ordering the External Product Specifications (EPS) or External Design Specifications (EDS) for a given sub-system. EPS and EDS documents are not publicly available. They are only made available under NDA with Intel<sup>®</sup> and must be ordered through your local Intel<sup>®</sup> representative. For a complete list of available documents, refer to the *Reference Documents* section at the end of this document.

The Intel<sup>®</sup> Server System H2000JF may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Refer to the *Intel<sup>®</sup> Server Board S2600JF/Intel<sup>®</sup> Server System H2000JF Specification Update* for published errata.

### 1.1 Chapter Outline

This document is divided into the following chapters:

- Chapter 1 Introduction

- Chapter 2 Product Overview

- Chapter 3 Power Sub-System

- Chapter 4 Cooling Sub-System

- Chapter 5 System Boards in the Node Tray

- Chapter 6 Hard Disk Drive Support

- Chapter 7 Front Panel Control and Indicators

- Chapter 8 Configuration Jumpers

- Chapter 9 PCI Express\* Riser Card and Assembly

- Appendix A Integration and Usage Tips

- Appendix B POST code LED Decoder

- Appendix C Video POST Code Errors

- Glossary

- Reference Documents

### **1.2 Server Board Use Disclaimer**

Intel Corporation server boards support add-in peripherals and contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel<sup>®</sup> ensures through its own chassis development and testing that when Intel<sup>®</sup> server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel<sup>®</sup> developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of air flow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of their published operating or non-operating limits.

# 2. Product Overview

The Intel<sup>®</sup> Server System H2000JF family includes two major SKUs: H2312JF and H2216JF, which are rack mount 2U 4-node server systems, purpose-built for high-density and lowest total cost of ownership in dense computing applications, such as HPC and IPDC. The system is integrated with four units of Intel<sup>®</sup> Server Board S2600JF, supports up to twelve 3.5" or sixteen 2.5" hot-swap SAS or SATA hard drives, with Common Redundant Power Supply (CRPS) capability.

This chapter provides a high-level overview of the system features. The following chapters provide greater detail for each major system component or feature:

| Feature         Description  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor                    | <ul> <li>Support Intel<sup>®</sup> Xeon<sup>®</sup> Processor E5-2600 series processors.</li> <li>Up to eight GT/s Intel<sup>®</sup> QuickPath Interconnect (Intel<sup>®</sup> QPI).</li> <li>LGA 2011 Socket R</li> <li>Thermal Design Power (TDP) up to 135W with conditional ambient temperature, 130 Watt (6-core or 8-core) and below, or 80 Watt (4-core) and below.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Memory                       | <ul> <li>Unbuffered DDR3 and registered DDR3 with ECC DIMMs.</li> <li>Memory DDR3 data transfer rates of 800/1066/1333/1600/1867 MT/s.</li> <li>Load Reduced DDR3 DIMM.</li> <li>DDR3 standard I/O voltage of 1.5V (all speed) and DDR3 Low Voltage of 1.35V (1600MT/s or below)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chipset                      | Intel <sup>®</sup> C600 Platform Controller Hub (PCH) with support for optional Storage Upgrade Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| System<br>Connectors/Headers | <ul> <li>External I/O connectors:</li> <li>DB-15 Video connectors.</li> <li>Two RJ-45 Network Interface for 10/100/1000 LAN.</li> <li>One stacked two port USB 2.0 (Port 0/1) connectors.</li> <li>One dedicated 1GbE management port on rIOM carrier (Optional).</li> <li>One InfiniBand* QDR QSFP port (Board SKU: S2600JFQ) or</li> <li>One InfiniBand* FDR QSFP port (Board SKU: S2600JFF)</li> <li>Internal connectors/headers:</li> <li>Bridge Slot to extend board I/O with common bridge board <ul> <li>SCU0 (Four SAS 3Gb/s ports) to backplane</li> <li>Front control panel signals</li> <li>One SATA (Port 0) 6Gb/s port for DOM</li> </ul> </li> <li>Bridge Slot to extend board I/O with spare bridge board <ul> <li>Front control panel signals</li> <li>One SATA (Bot O) and SAS 6Gb/s ports) from add-in RAID card to backplane</li> <li>Front control panel signals</li> </ul> </li> <li>One Type-A USB 2.0 connector (USB port 2)</li> <li>One Zx7pin header for system FAN module</li> <li>One DH-10 serial Port A connector</li> <li>One SATA 6Gb/s (Port 1)</li> <li>One 2x4 pin header for Intel<sup>®</sup> RMM4 Lite</li> <li>One 1x4 pin header for Storage Upgrade Key</li> </ul> |

| System Fan Support           | Three sets of dual rotor fan for each node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Add-in Adapter Support       | <ul> <li>Three PCIe Gen III x16 riser slots:</li> <li>Riser slot 1 support PCIe Gen III x16 Riser with LP PCIe add-in card</li> <li>Riser slot 2 supports PCIe Gen III x8 Riser (Intel<sup>®</sup> rIOM)</li> <li>Riser slot 3 cannot be used with bridge board covered</li> <li>One Bridge Slot for board I/O expansion.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Table 1. System Feature Set

| Feature           | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| On-board Video    | On-board Server Engines* LLC Pilot III Controller  Integrated 2D Video Controller  128MB DDR2 Memory                                                                                                                                                                                                                                                                                                                  |  |  |

| Hard Disk Drive   | 12x 3.5-inch SATA/SAS HDD bays (SKU: H2312JF)                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Supported         | 16x 2.5-inch SATA/SAS HDD bays (SKU: H2216JF)                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RAID Support      | <ul> <li>Intel<sup>®</sup> RSTe SW RAID 0/1/10/5 for SATA mode</li> <li>LSI* SW RAID 0/1/10/5</li> </ul>                                                                                                                                                                                                                                                                                                              |  |  |

| LAN               | <ul> <li>For each node:</li> <li>One Gigabit Ethernet device i350 connect to PCI-E x4interfaces on the PCH, providing 2GbE ports for each node.</li> <li>One QSFP port from Mellanox* ConnectX-3* to support QDR/FDR Infiniband* based on board SKU.</li> <li>One dedicated 1GbE management port with RMM4 Lite installed</li> </ul>                                                                                  |  |  |

| System Power      | 1200w AC Common Redundant Power Supply (CRPS), 80 plus Platinum with PFC,<br>supporting CRPS configuration. Chassis SKU: <b>H2312JFJR, H2216JFJR</b><br>1600w AC Common Redundant Power Supply (CRPS), 80 plus Platinum with PFC,<br>supporting CRPS configuration. Chassis SKU: <b>H2312JFKR, H2216JFKR</b>                                                                                                          |  |  |

| Server Management | <ul> <li>Onboard ServerEngines* LLC Pilot III* Controller</li> <li>Support for Intel<sup>®</sup> Remote Management Module 4 Lite solutions.</li> <li>Intel<sup>®</sup> Light-Guided Diagnostics on field replaceable units.</li> <li>Support for Intel<sup>®</sup> System Management Software.</li> <li>Support for Intel<sup>®</sup> Intelligent Power Node Manager (Need PMBus*-compliant power supply).</li> </ul> |  |  |

#### Table 2. System SKU matrix

| Board SKU vs Chassis | 3.5" HDD with 1200W<br>CRPS | 2.5" HDD with 1200W<br>CRPS | 3.5" HDD with 1600W<br>CRPS | 2.5" HDD with 1600W<br>CRPS |

|----------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| S2600JF              | H2312JFJR                   | H2216JFJR                   | H2312JFKR                   | H2216JFKR                   |

| S2600JFQ             | H2312JFQJR                  | H2216JFQJR                  | H2312JFQKR                  | H2216JFQKR                  |

| S2600JFF             | H2312JFFJR                  | H2216JFFJR                  | H2312JFFKR                  | H2216JFFKR                  |

The Intel<sup>®</sup> Server System H2000JF family are supporting all Intel<sup>®</sup> Xeon<sup>®</sup> processor E5-2600 series with TDP 135W (8-core, 6-core) and below, or 80W (4-core) and below. You can find a full list of supported processors at the Intel<sup>®</sup> Support Website: <u>http://www.intel.com/p/en\_US/support/highlights/server/ss-h2000jf</u>.

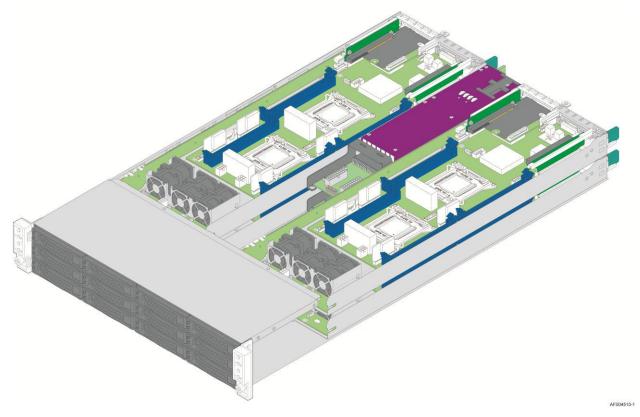

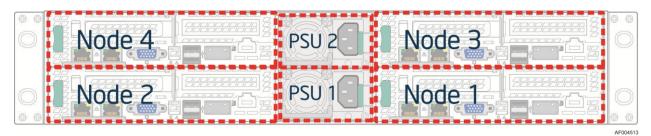

### 2.1 System Views

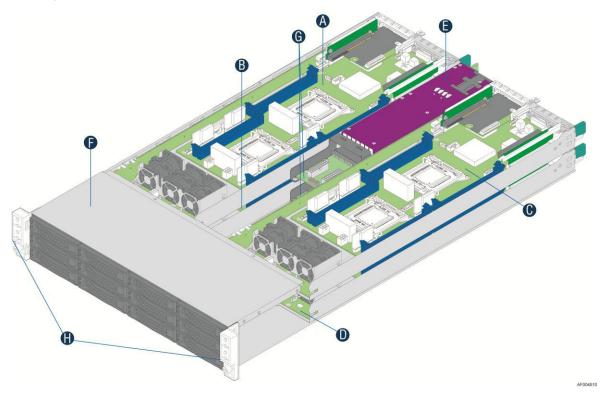

Figure 1. System Overview (Air Duct removed)

Figure 2. Compute Node Scheme (Rear View)

### 2.2 System Dimensions

| Table 3. | Chassis | Dimension | (SKU: H23 | 12JF) |

|----------|---------|-----------|-----------|-------|

|----------|---------|-----------|-----------|-------|

| Height |                                               | 87.9mm | 3.46"  |

|--------|-----------------------------------------------|--------|--------|

| Width  |                                               | 438mm  | 17.24" |

| Depth  |                                               | 771mm  | 30.35" |

| Weight |                                               | kg     | lbs    |

| -      | Chassis – basic configured (2 PSU, 0 drives)  | 30     | 66.14  |

|        | Chassis - fully configured (2 PSU, 12 drives) | 38     | 83.78  |

| Height |                                               | 87.9mm | 3.46"  |

|--------|-----------------------------------------------|--------|--------|

| Width  |                                               | 438mm  | 17.24" |

| Depth  |                                               | 733mm  | 28.86" |

| Weight |                                               | kg     | lbs    |

| -      | Chassis – basic configured (2 PSU, 0 drives)  | 29     | 63.93  |

|        | Chassis – fully configured (2 PSU, 16 drives) | 32     | 70.55  |

### Table 4. Chassis Dimension (SKU: H2216JF)

### 2.3 System Level Environmental Limits

The following table defines the system level operating and non-operating environmental limits:

| Parameter   |                                          | Limits                                                                                                                           |  |  |  |  |  |  |

|-------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Temperature |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             |                                          | ASHRAE Class A2 – Continuous Operation. 10°C to 35°C (50°F to 95°F) with the maximum rate of change not to exceed 10°C per hour  |  |  |  |  |  |  |

|             | Operating                                | ASHRAE Class A3 – Includes operation up to 40°C for up to 900 hours per year.                                                    |  |  |  |  |  |  |

|             |                                          | ASHRAE Class A4 – Includes operation up to 45°C for up to 90 hours per year.                                                     |  |  |  |  |  |  |

|             | Shipping                                 | -40°C to 70°C (-40°F to 158°F)                                                                                                   |  |  |  |  |  |  |

| Humidity    |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             | Non-Operating                            | 50% to 90%, non-condensing with a maximum wet bulb of 28°C (at temperatures from 25°C to 35°C)                                   |  |  |  |  |  |  |

| Shock       |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             | Operating                                | Half sine, <u>2g</u> , 11 mSec                                                                                                   |  |  |  |  |  |  |

|             | Unpackaged                               | Trapezoidal, <u>25g</u> , velocity change is based on packaged weight                                                            |  |  |  |  |  |  |

|             | Packaged                                 | Product Weight: ≥ 40 to < 80<br>Non-palletized Free Fall Height = 18 inches<br>Palletized (single product) Free Fall Height = NA |  |  |  |  |  |  |

| Vibration   |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             | Unpackaged                               | 5 Hz to 500 Hz 2.20 g RMS random                                                                                                 |  |  |  |  |  |  |

|             | Packaged                                 | 5 Hz to 500 Hz 1.09 g RMS random                                                                                                 |  |  |  |  |  |  |

| AC-DC       |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             | Voltage                                  | 90V to 132V and 180V to 264                                                                                                      |  |  |  |  |  |  |

|             | Frequency                                | 47Hz to 63Hz                                                                                                                     |  |  |  |  |  |  |

|             | Source<br>Interrupt                      | No loss of data for power line drop-out of 12 mSec                                                                               |  |  |  |  |  |  |

|             | Surge Non-<br>operating and<br>operating | Unidirectional                                                                                                                   |  |  |  |  |  |  |

|             | Line to earth<br>Only                    | AC Leads2.0 kVI/O Leads1.0 kVDC Leads0.5 kV                                                                                      |  |  |  |  |  |  |

| ESD         |                                          |                                                                                                                                  |  |  |  |  |  |  |

|             | Air Discharged                           | 8.0 kV                                                                                                                           |  |  |  |  |  |  |

Table 5. System Environmental Limits Summary

| Parameter                               |                          | Limits                                                                                                             |

|-----------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------|

|                                         | Contact<br>Discharge     | 8.0 kV                                                                                                             |

| Altitude                                |                          |                                                                                                                    |

|                                         | Operating                | -16 to 3048 m (-50 to 10,000 ft)                                                                                   |

|                                         |                          | <b>Note</b> : For altitudes above 2950 feet, the maximum operating temperature is derated 1°F/550 ft.              |

|                                         | Storage                  | -16 to 10,600 m (-50 to 35,000 ft)                                                                                 |

| Acoustics<br>Sound<br>Power<br>Measured | _                        | _                                                                                                                  |

|                                         | Power in<br>Watts        | All range                                                                                                          |

|                                         | Servers/Rack<br>Mount BA | - 3.5" HDD SKU: 6.9BA at idle and 7.4BA at active mode<br>- 2.5" HDD SKU: 6.5BA at idle and 7.07BA at active mode. |

#### Note:

Intel Corporation server boards contain a number of high-density VLSI and power delivery components that need adequate airflow to cool. Intel<sup>®</sup> ensures through its own chassis development and testing that when Intel<sup>®</sup> server building blocks are used together, the fully integrated system will meet the intended thermal requirements of these components. It is the responsibility of the system integrator who chooses not to use Intel<sup>®</sup> developed server building blocks to consult vendor datasheets and operating parameters to determine the amount of airflow required for their specific application and environmental conditions. Intel Corporation cannot be held responsible, if components fail or the server board does not operate correctly when used outside any of its published operating or non-operating limits.

**Disclaimer Note:** Intel<sup>®</sup> ensures the unpackaged server board and system meet the shock requirement mentioned above through its own chassis development and system configuration. It is the responsibility of the system integrator to determine the proper shock level of the board and system if the system integrator chooses different system configuration or different chassis. Intel Corporation cannot be held responsible if components fail or the server board does not operate correctly when used outside any of its published operating or non-operating limits.

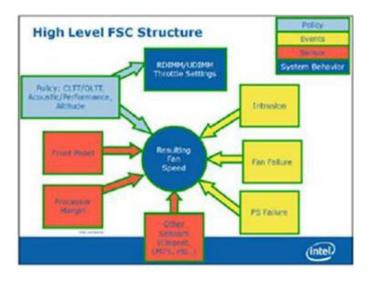

In order to maintain comprehensive thermal protection, deliver the best system acoustics, and fan power efficiency, an intelligent Fan Speed Control (FSC) and thermal management technology (mechanism) is used. Options in <F2> BIOS Setup (**BIOS** > **Advanced** > **System Acoustic and Performance Configuration**) allow for parameter adjustments based on the actual system configuration and usage. Refer to the following sections for a description of each setting.

### 2.3.1 High Temperature Ambience (HTA) Support

To keep the system operating within supported maximum thermal limits, the system must meet the following operating and configuration guidelines:

- The system operating ambient is designed for sustained operation up to 35°C (ASHRAE Class A2) with short term excursion based operation up to 45°C (ASHRAE Class A4).

- The system can operate up to 40°C (ASHRAE Class A3) for up to 900 hours per year

- The system can operate up to 45<sup>o</sup>C (ASHRAE Class A4) for up to 90 hours per year

- System performance may be impacted when operating within the extended operating temperature range

- There is no long term system reliability impact when operating at the extended temperature range within the approved limits.

- Specific configuration requirements and limitations are documented in the configuration matrix found in the Intel<sup>®</sup> Server Board S2600JF Product Family Power Budget and Thermal Configuration Guidelines Tool, available as a download tool online at <u>http://www.intel.com/p/en\_US/support/</u>.

- The CPU-1 processor + CPU heat sink must be installed first. The CPU-2 heat sink must be installed at all times, with or without a processor installed.

- Memory Slot population requirements:

**Note:** Specified memory slots can be populated with a DIMM or supplied DIMM Blank. Memory population rules apply when installing DIMMs.

- **DIMM Population Rules on CPU-1** Install DIMMs in order; Channels A, B, C, and D.

- **DIMM Population on CPU-2** Install DIMMs in order; Channels E, F, G, and H.

- The following system configurations require that specific memory slots be populated at all times using either a DIMM or supplied DIMM Blank

- System Configuration 16x 2.5" hard drive bay or 12x 3.5" hard drive bay configuration + Intel<sup>®</sup> Server Board S2600JF (8-DIMM server board)

- All hard drive bays must be populated. Hard drive carriers can be populated with a hard drive or supplied drive blank.

- With the system operating, the air duct must be installed at all times

- In single power supply configurations, the second power supply bay must have the supplied filler blank installed at all times.

- Thermally, the system can support the following PCI add-in cards.

- Add-in cards with a minimum 100 LFM (0.5 m/s) air flow requirement can be installed in any available add-in card slot in both Riser Card #1 and Riser Card for IO Module carrier

- $\circ~$  Add-in cards with a >200 LFM air flow requirement cannot be supported.

**Note:** Most PCI add-in cards have minimum air flow requirements of 100 LFM (0.5m/s). Some high power add-in cards have minimum air flow requirements of 200 LFM (1 m/s). System integrators should verify PCI add-in card air flow requirements from vendor specifications when integrating add-in cards into the system.

- The system top-cover must be installed at all times when the system is in operation.

- Supported ambient temperature versus processor TDP is as follows:

| No  | tes:                                                                                                                          |                                                                                                                                       |     |                           |                |     |         |                        |         |               |

|-----|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|----------------|-----|---------|------------------------|---------|---------------|

| 1.  | 25°C is limited                                                                                                               | to elevations of 900m or less                                                                                                         |     |                           |                |     |         |                        |         |               |

| 2.  |                                                                                                                               | Modules cannot be installed<br>y with PCI Cards.                                                                                      |     |                           |                |     |         |                        |         |               |

| 3.  | Processor - 13<br>some perform                                                                                                | 30W-4C and 135W-8C may have ance impact.                                                                                              |     |                           |                |     |         |                        |         |               |

| 4.  | Processors - T<br>impact during                                                                                               | There may be some performance<br>fan failures.                                                                                        |     |                           |                |     |         |                        |         |               |

| 5.  | For A3/A4 ind                                                                                                                 | ividual PS selection:                                                                                                                 |     |                           |                |     |         |                        |         |               |

|     | powe                                                                                                                          | lual power supply configuration,<br>er budget must fit within single<br>er supply rated load and be<br>lled in dual configuration, or |     | System<br><b>H2216J</b> I |                | Ва  |         | tem SKl<br><b>12JF</b> | Js:     |               |

|     | powe                                                                                                                          | ingle power supply configuration,<br>or budget must be sized with 30%<br>in to single power supply rated                              |     |                           |                |     |         |                        |         |               |

| 6.  | LV refers to lo                                                                                                               | w voltage DIMMs (1.35V)                                                                                                               |     |                           |                |     |         |                        |         |               |

| 7.  | <ol> <li>When identifying memory in the table, only<br/>Rank and Width are required. Capacity is not<br/>required.</li> </ol> |                                                                                                                                       |     |                           |                |     |         |                        |         |               |

| 8.  | fail. "Fan Fail                                                                                                               | al-rotor fans refers to one rotor<br>Support" indicates if fan fail can<br>with specified configuration in                            |     |                           |                |     |         |                        |         |               |

| ASI | HRAE (See                                                                                                                     | Classifications                                                                                                                       | A2  | A3                        | A4             | 25C | A2      | A3                     | A4      |               |

|     | e 1)                                                                                                                          | Max Ambient                                                                                                                           | 35C | 40C                       | 45C            | 25C | 35C     | 40C                    | 45C     | See<br>note 1 |

|     | oling (See                                                                                                                    | Redundant Fan Configuration                                                                                                           | •   | •                         | •              | •   | •       | •                      | •       |               |

| not | note 8) Fan Fail Support                                                                                                      |                                                                                                                                       | •   |                           |                | •   | •       |                        |         |               |

| PS  | PS (See note 5) Power Supplies                                                                                                |                                                                                                                                       | See | Power                     | Budget<br>Tool | S   | See Pow | er Budg                | et Tool | See<br>note 5 |

|     | Processors<br>e notes 3 and                                                                                                   | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2630L, 60w, 6C                                                                  | •   | •                         |                | •   | •       | •                      |         | See<br>note 4 |

| 4)  |                                                                                                                               | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2650L, 70w, 8C                                                                  | •   | •                         | •              | •   | •       | •                      |         | See<br>note 4 |

### Table 6. Ambient Temperature versus System Configuration

|                                      | (P)                                                                                       | 1 | 1 |   |   |   | 1 | T | 1             |

|--------------------------------------|-------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|---------------|

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2620 , E5-2630, E5-2640, 95w,<br>6C | • | • | • | • | • | • | • | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2650, E5-2660, 95w, 8C              | • | • | • | • | • | • | • | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2665, E5-2670, 115w, 8C             | • | • | • | • | • | • |   | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2667, 130w, 6C                      | • | • | • | • | • |   |   | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2680, 130w, 8C                      | • |   |   | • | • |   |   | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2690, 135w, 8C                      | • |   |   | • |   |   |   |               |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2637, 80w, 2C                       | • | • | • | • | • | • | • | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2603, E5-2609, 80w, 4C              | • | • | • | • | • | • | • | See<br>note 4 |

|                                      | Intel <sup>®</sup> Xeon <sup>®</sup> processor E5-<br>2643, 130w, 4C                      | • |   |   | • |   |   |   |               |

|                                      | Dual Rank x8                                                                              | • | • | • | • | • | • | • |               |

| м <del>т</del>                       | Dual Rank x4                                                                              | • | • |   | • | • | • |   |               |

| Memory Type<br>(See note 6 and<br>7) | Quad Rank x8                                                                              | • | • |   | • | • | • |   |               |

|                                      | Quad Rank x4                                                                              | • |   |   | • | • |   |   |               |

|                                      | Load Reduced DIMM                                                                         | • |   |   | • | • |   |   |               |

| Add-in Cards<br>(See note 2)         | PCI Cards                                                                                 | • | • | • | • | • | • | • | See<br>note 2 |

|                                      | AXX10GBTWLIOM - Dual<br>10GBASE-T IO Module                                               | • | • | • | • | • | • | • |               |

|                                      | AXX10GBNIAIOM - Dual SFP+<br>port 10GbE IO Module                                         | • | • | • | • | • | • | • |               |

| Module (See<br>note 2)               | AXX1FDRIBIOM - Single Port<br>FDR Infiniband* IO Module                                   | • | • | • | • | • | • | • |               |

|                                      | AXX2FDRIBIOM - Dual Port<br>FDR Infiniband* IO Module                                     | • | • | • | • | • | • | • |               |

|                                      | AXX4P1GBPWLIOM - Quad<br>Port 1GbE IO Module                                              | • | • | • | • | • | • | • | See<br>note 2 |

### 2.3.2 Set Throttling Mode

This option is used to select the desired memory thermal throttling mechanism. Available settings include:

[Auto], [DCLTT], [SCLTT], and [SOLTT].

- [Auto] Factory Default Setting BIOS automatically detects and identifies the appropriate thermal throttling mechanism based on DIMM type, airflow input, and DIMM sensor availability.

- [DCLTT] Dynamic Closed Loop Thermal Throttling: for the SOD DIMM with system airflow input

- [SCLTT] Static Close Loop Thermal Throttling: for the SOD DIMM without system airflow input

- [SOLTT] Static Open Loop Thermal Throttling: for the DIMMs without sensor on DIMM (SOD)

### 2.3.3 Altitude

This option is used to select the proper altitude that the system will be used in. Available settings include: [300m or less], **[301m-900m]**, [901m-1500m], [Above 1500m].

Selecting an altitude range that is lower than the actual altitude the system will be operating at, can cause the fan control system to operate less efficiently, leading to higher system thermals and lower system performance. If the altitude range selected is higher than the actual altitude the system will be operating at, the fan control system may provide better cooling but with higher acoustics and higher fan power consumption. If the altitude is not known, selecting a higher altitude is recommended in order to provide sufficient cooling.

### 2.3.4 Set Fan Profile

This option is used to set the desired Fan Profile. Available settings include: [Performance] and [Acoustic].

The Acoustic mode offers the best acoustic experience and appropriate cooling capability covering the mainstream and the majority of the add-in cards used. Performance mode is designed to provide sufficient cooling capability covering all kinds of add-in cards on the market.

### 2.3.5 Fan PWM Offset

This option is reserved for manual adjustment to the minimum fan speed curves. The valid range is from [0 to 100] which stands for 0% to 100% PWM adding to the minimum fan speed. This feature is valid when Quiet Fan Idle Mode is at Enabled state. The default setting is [0]

### 2.3.6 Quiet Fan Idle Mode

This feature can be [Enabled] or [Disabled]. If enabled, the fans will either shift to a lower speed or stop when the aggregate sensor temperatures are satisfied, indicating the system is at ideal thermal/light loading conditions. When the aggregate sensor temperatures are not satisfied, the fans will shift back to normal control curves. If disabled, the fans will never shift into lower fan speeds or stop, regardless of whether the aggregate sensor temperatures are satisfied or not. The default setting is [Disabled]. **Note:** The above feature may or may not be in effect and depends on the actual thermal characteristics of the specified system.

### 2.3.7 Thermal Sensor Input for Fan Speed Control

The BMC uses various IPMI sensors as inputs to fan speed control. Some of the sensors are actual physical sensors and some are "virtual" sensors derived from calculations.

The following IPMI thermal sensors are used as input to fan speed control:

- Front Panel Temperature Sensor<sup>1</sup>

- Server board Temperature Sensor<sup>2</sup>

- Processor Margin Sensors<sup>3,5,6</sup>

- DIMM Thermal Margin Sensors<sup>3,5</sup>

- Exit Air Temperature Sensor<sup>1, 4, 8</sup>

- Chipset Temperature Sensor <sup>4,6</sup>

- On-board Ethernet Controller Temperature Sensors <sup>4, 6</sup>

- Add-In Intel SAS/IO Module Temperature Sensors <sup>4, 6</sup>

- Power Supply Thermal Sensor<sup>4, 9</sup>

- Processor VR Temperature Sensors<sup>4, 7</sup>

- DIMM VR Temperature Sensors<sup>4, 7</sup>

- BMC Temperature Sensor<sup>4, 7</sup>

- Global Aggregate Thermal Margin Sensors<sup>8</sup>

#### Notes:

- 1. For fan speed control in Intel chassis

- 2. For fan speed control in 3rd party chassis

- 3. Temperature margin from throttling threshold

- 4. Absolute temperature

- 5. PECI value or margin value

- 6. On-die sensor

- 7. On-board sensor

- 8. Virtual sensor

- 9. Available only when PSU has PMBus\*

The following diagram illustrates the fan speed control structure:

Figure 3. Fan Control Model

### 2.4 System Parts

| Α | Compute Node 3 Tray | Е | Common Redundant Power Supply             |

|---|---------------------|---|-------------------------------------------|

| В | Compute Node 1 Tray | F | HDD bays with Hot Swap Backplane          |

| С | Compute Node 4 Tray | G | Upper and Lower Power Distribution Boards |

| D | Compute Node 2 Tray | н | Front Control Panel                       |

Note: Not shown - Rack slide rail, and top cover.

### Figure 4. Major System Parts

### 2.5 Hard Drive and Peripheral Bays

|                                          | Intel <sup>®</sup> Server System H2312JF | Intel <sup>®</sup> Server System H2216JF |

|------------------------------------------|------------------------------------------|------------------------------------------|

| Slim-line SATA Optical Drive             | Not Supported                            | Not Supported                            |

| Internal USB Floppy Drive                | Not Supported                            | Not Supported                            |

| SATA/SAS Hard Disk Drives (3.5-<br>inch) | Up to Twelve                             | Not Supported                            |

| SATA/SAS Hard Disk Drives (2.5-<br>inch) | Not Supported                            | Up to Sixteen                            |

| SATA DOM                                 | Support                                  | Support                                  |

AF004635

### Figure 5. Intel<sup>®</sup> Server System H2312JF Drive Bay Overview

AF004637

Figure 6. Intel<sup>®</sup> Server System H2216JF Drive Bay Overview

### 2.6 Server Board Overview

The chassis is mechanically and functionally designed to support half-width server board, including Intel<sup>®</sup> Server Board S2600JF. The following sections provide an overview of the server board feature sets:

Figure 7. Intel<sup>®</sup> Server Board S2600JFQ/S2600JFF

The following figure shows the layout of the server board. Each connector and major component is identified by a number or letter, and a description is given in the following figure.

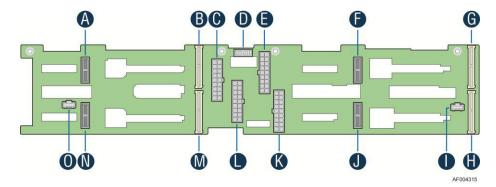

| A | 2x7 fan control<br>connector | I | Slot2 (PCle<br>Gen3x16) | Q | VGA out               | Y  | SATA port 1 |

|---|------------------------------|---|-------------------------|---|-----------------------|----|-------------|

| в | VRS (4 total)                | J | Infiniband*<br>QDR/FDR  | R | Dual port 1Gbe<br>NIC | z  | PCH C600    |

| с | Slot3 (PCle<br>Gen3x16)      | к | RMM4 lite               | S | NIC Port 2            | AA | CPU 1       |

| D | CPU2 DIMM<br>(4 total) | L | POST and<br>InfiniBand* Status<br>LED | т | Serial Port A           | AB | XDP connector                  |

|---|------------------------|---|---------------------------------------|---|-------------------------|----|--------------------------------|

| Е | CPU1 DIMM<br>(4 total) | М | QSFP                                  | U | NIC Port 1              | AC | CPU 2                          |

| F | Bridge board connector | Ν | USB x2                                | v | Slot1 (PCle<br>Gen3x16) | AD | 2x3 PWR<br>connector (2 total) |

| G | IPMB                   | 0 | Debug connector                       | w | Integrated BMC          |    |                                |

| н | 2x5 USB                | Ρ | Status and ID<br>LED                  | x | Storage Upgrade<br>key  |    |                                |

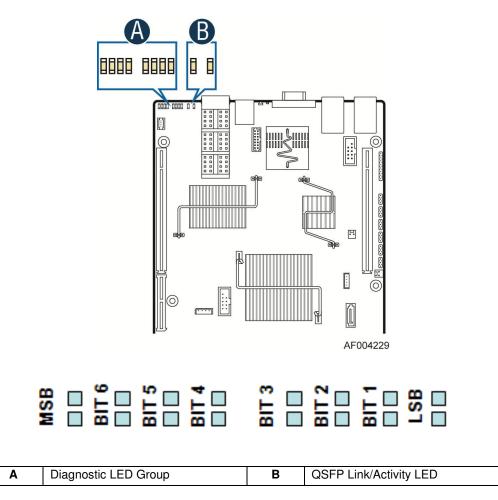

### Figure 8. Intel<sup>®</sup> Server Board S2600JF Components

|   | Description                    |   | Description                       |

|---|--------------------------------|---|-----------------------------------|

| Α | NIC port 1 (RJ45) <sup>1</sup> | Е | Status LED                        |

| В | NIC port 2 (RJ45) <sup>1</sup> | F | Dual port USB connector           |

| С | DB15 video out                 | G | QSFP Connector <sup>2</sup>       |

| D | ID LED                         | н | QSFP status and Diagnostic<br>LED |

#### Figure 9. Back Panel Feature Overview

**Note 1:** The Intel<sup>®</sup> Server System H2312JF and H2216JF requires the use of shielded LAN cable to comply with Emission/Immunity regulatory requirements. Use of non shield cables **may result in** product non-compliance.

**Note 2:** The Intel<sup>®</sup> Server System H2312JFF and H2216JFF are recommended to use two meters or three meter length cables for better EMI performance.

Figure 10. Light-Guided Diagnostic LED Locations

### 2.7 Front Bezel Support

Intel<sup>®</sup> Server System H2000JF family provides front panel bezel. The bezel provides protection to system HDD bays with a lock to chassis. The front view of the bezel is as below.

### 2.8 Rack and Cabinet Mounting Options

The chassis was designed to support 19 inches wide by up to 30 inches deep server cabinets. The system bundles with the following  $Intel^{®}$  rack mount option:

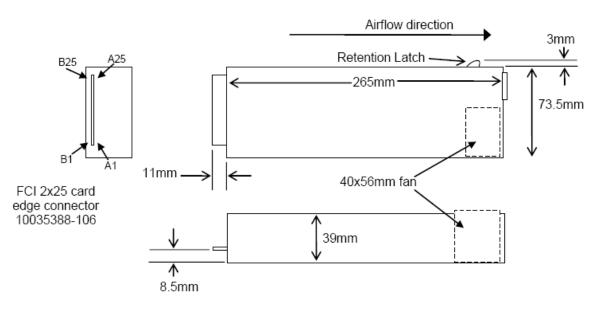

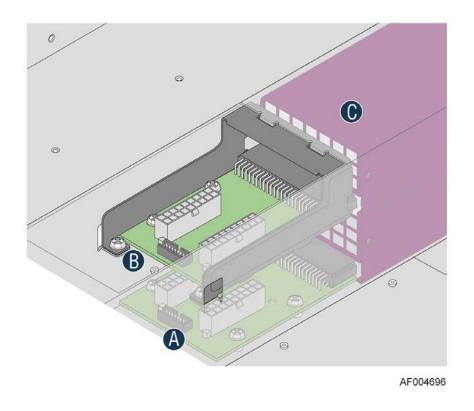

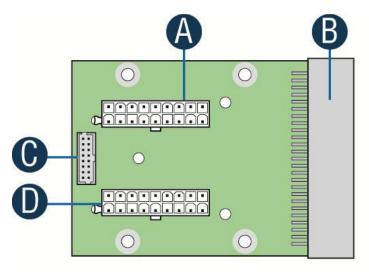

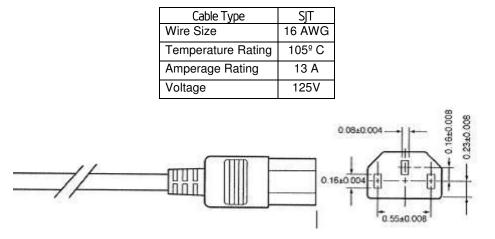

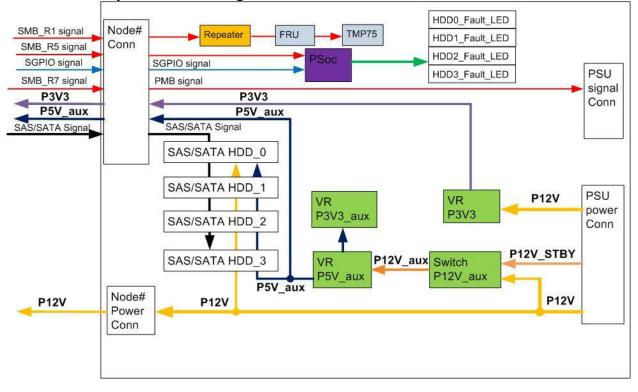

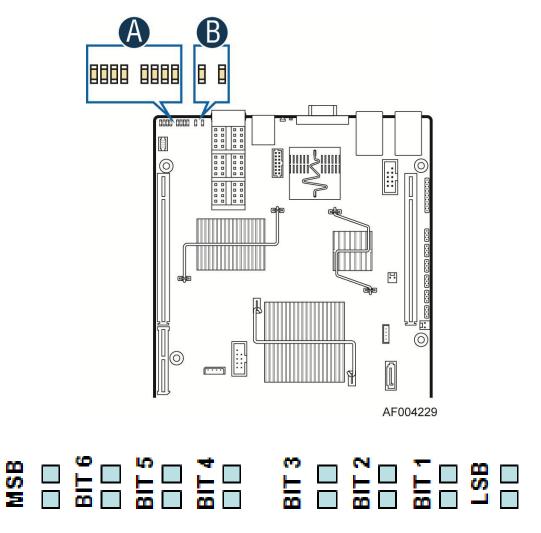

A basic slide rail kit (Product order code – AXXELVRAIL) is designed to mount the chassis into a standard (19 inches by up to 30 inches deep) EIA-310D compatible server cabinet.