# **Command Line Tools User Guide**

(Formerly the Development System Reference Guide)

UG628 (v 13.4) January 18, 2012

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© Copyright 2002-2012 Xilinx Inc. All Rights Reserved. XILINX, the Xilinx logo, the Brand Window and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners. The PowerPC name and logo are registered trademarks of IBM Corp., and used under license. All other trademarks are the property of their respective owners.

## **Revision History**

| Date       | Version          |                                                                                                                                                   |  |

|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 03/01/2011 | 13.1 download    | Adding information for Xilinx® 7 series FPGA devices.                                                                                             |  |

| 03/02/2011 | 13.1 Web release | Additional updates for Xilinx 7 series FPGA devices.                                                                                              |  |

| 07/06/2011 | 13.2 download    | Updated information on Xilinx 7 series FPGA supported devices (CR #610690 and edit requests)                                                      |  |

|            |                  | Updated all Processes and Properties tables to match the GUI. Added Static Timing Process Properties table based on GUI                           |  |

|            |                  | Additional detail to Tclk set_family option (CR #604108)                                                                                          |  |

|            |                  | Added USR_ACCESS option to BitGen chapter (edit request)                                                                                          |  |

|            |                  | Removed CLT documentation options that are obsoleted by change to map<br>-global_opt flow (CR #604740)                                            |  |

|            |                  | Misc. other corrections to match document with how the software works (CR #590750, #593738, #594127, #595446, #596310, #596916, #604740, #609259) |  |

| 10/19/2011 | 13.3 download    | Documented bitgen options EssentialBits, RevisionSelect, and RevisionSelect_tristate                                                              |  |

|            |                  | Added Tcl command information for EssentialBits, RevisionSelect, and RevisionSelect_tristate                                                      |  |

|            |                  | Updated BitGen output file table to add EssentialBits files                                                                                       |  |

|            |                  | Updated BitGen flow diagram to include all current input and output files                                                                         |  |

|            |                  | Final characterization for bitgen -g ConfigRate for 7 series devices                                                                              |  |

|            |                  | Added links from Bitgen options table to options                                                                                                  |  |

The following table shows the revision history for this document.

| Date      | Version       |                                                                                     |

|-----------|---------------|-------------------------------------------------------------------------------------|

| 1/18/2012 | 13.4 download | Reorganized SmartXplorer chapter to better expose how to run strategies in parallel |

|           |               | Addr bitgen -g next_config_reboot option                                            |

|           |               | par -activityfile switch is not supported in newer architectures                    |

# Table of Contents

| Revision History2                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 Introduction9                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Command Line Program Overview9                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Command Line Syntax10                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Command Line Options10                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Invoking Command Line Programs14                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Chapter 2 Design Flow15                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Design Flow Overview15                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Design Entry and Synthesis18                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Design Implementation22                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Design Verification25                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FPGA Design Tips31                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 3 PARTGen                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PARTGen Overview33                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PARTGen Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PARTGen Command Line Options                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 4 NetGen43                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 4 NetGen       43         NetGen Overview       43                                                                                                                                                                                                                                                                                                                                                                                               |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43<br>NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43<br>NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 43<br>NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 43<br>NetGen Overview                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| NetGen Overview43NetGen Simulation Flow45NetGen Equivalence Checking Flow55NetGen Static Timing Analysis Flow59Preserving and Writing Hierarchy Files63Dedicated Global Signals in Back-Annotation Simulation65Chapter 5Logical Design Rule Check (DRC)67                                                                                                                                                                                                |

| NetGen Overview43NetGen Simulation Flow45NetGen Equivalence Checking Flow55NetGen Static Timing Analysis Flow59Preserving and Writing Hierarchy Files63Dedicated Global Signals in Back-Annotation Simulation65Chapter 5Logical Design Rule Check (DRC)67Logical DRC Overview67                                                                                                                                                                          |

| NetGen Overview43NetGen Simulation Flow45NetGen Equivalence Checking Flow55NetGen Static Timing Analysis Flow59Preserving and Writing Hierarchy Files63Dedicated Global Signals in Back-Annotation Simulation65Chapter 5 Logical Design Rule Check (DRC)67Logical DRC Overview67Logical DRC Checks67                                                                                                                                                     |

| <ul> <li>NetGen Overview</li> <li>MetGen Simulation Flow</li> <li>NetGen Simulation Flow</li> <li>NetGen Equivalence Checking Flow</li> <li>Soution Static Timing Analysis Flow</li> <li>Preserving and Writing Hierarchy Files</li> <li>Dedicated Global Signals in Back-Annotation Simulation</li> <li>Chapter 5 Logical Design Rule Check (DRC)</li> <li>Chapter 5 Logical Design Rule Check (DRC)</li> <li>Chapter 6 NGDBuild</li> <li>71</li> </ul> |

| NetGen Overview43NetGen Simulation Flow45NetGen Equivalence Checking Flow55NetGen Static Timing Analysis Flow59Preserving and Writing Hierarchy Files63Dedicated Global Signals in Back-Annotation Simulation65Chapter 5Logical Design Rule Check (DRC)67Logical DRC Overview67Logical DRC Checks67Chapter 6NGDBuild71NGDBuild Overview71                                                                                                                |

| NetGen Overview43NetGen Simulation Flow45NetGen Equivalence Checking Flow55NetGen Static Timing Analysis Flow59Preserving and Writing Hierarchy Files63Dedicated Global Signals in Back-Annotation Simulation65Chapter 5Logical Design Rule Check (DRC)67Logical DRC Overview67Logical DRC Checks67Chapter 6NGDBuild71NGDBuild Overview71NGDBuild Syntax74                                                                                               |

| MAP Process                                      |

|--------------------------------------------------|

| MAP Syntax84                                     |

| MAP Options                                      |

| Resynthesis and Physical Synthesis Optimizations |

| Guided Mapping97                                 |

| Simulating Map Results98                         |

| MAP Report (MRP) File99                          |

| Physical Synthesis Report (PSR) File105          |

| Halting MAP 107                                  |

| Chapter 8 Physical Design Rule Check109          |

| DRC Overview 109                                 |

| DRC Syntax                                       |

| DRC Options 110                                  |

| DRC Checks 111                                   |

| DRC Errors and Warnings111                       |

| Chapter 9 Place and Route (PAR)113               |

| PAR Overview113                                  |

| PAR Process 115                                  |

| PAR Syntax 116                                   |

| Detailed Listing of Options117                   |

| PAR Reports 123                                  |

| ReportGen131                                     |

| Halting PAR133                                   |

| Chapter 10 SmartXplorer135                       |

| SmartXplorer Overview135                         |

| Using SmartXplorer Strategies135                 |

| Running SmartXplorer Strategies in Parallel      |

| Using Synthesis with SmartXplorer146             |

| SmartXplorer Reports148                          |

| Setting Up SmartXplorer to Run on SSH151         |

| SmartXplorer Command Line Reference151           |

| Chapter 11 XPWR163                               |

| XPWR Overview                                    |

| XPWR Syntax164                                   |

| XPWR Command Line Options165                     |

| XPWR Command Line Examples167                    |

| Using XPWR 16                     | 57                         |

|-----------------------------------|----------------------------|

| Power Reports 16                  | <u>;9</u>                  |

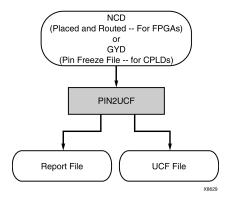

| Chapter 12 PIN2UCF17              | '1                         |

| PIN2UCF Overview17                | 71                         |

| PIN2UCF Syntax17                  | 74                         |

| PIN2UCF Command Line Options17    | 75                         |

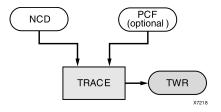

| Chapter 13 TRACE17                | 7                          |

| TRACE Overview17                  | 77                         |

| TRACE Syntax17                    | 78                         |

| TRACE Options17                   | 79                         |

| TRACE Command Line Examples18     | 34                         |

| TRACE Reports 18                  | 34                         |

| OFFSET Constraints20              | )0                         |

| PERIOD Constraints 20             | )8                         |

| Halting TRACE21                   | 12                         |

| Chapter 14 Speedprint21           | 3                          |

| Speedprint Overview21             | 13                         |

| Speedprint Command Line Syntax21  | l7                         |

| Speedprint Command Line Options21 | 17                         |

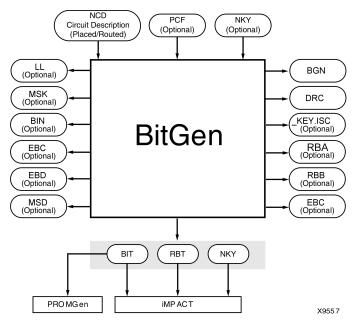

| Chapter 15 BitGen21               | 9                          |

| BitGen Overview21                 | 9                          |

| BitGen Command Line Syntax22      | 22                         |

| BitGen Command Line Options22     | 23                         |

| Chapter 16 BSDLAnno24             | 9                          |

| BSDLAnno Overview24               | 19                         |

| BSDLAnno Command Line Syntax25    | 50                         |

| BSDLAnno Command Line Options     |                            |

|                                   | 50                         |

| BSDLAnno File Composition25       |                            |

| -                                 | 51                         |

| BSDLAnno File Composition         | 51<br>57                   |

| BSDLAnno File Composition         | 51<br>57<br>59             |

| BSDLAnno File Composition         | 51<br>57<br>59<br>59       |

| BSDLAnno File Composition         | 51<br>57<br>59<br>59       |

| BSDLAnno File Composition         | 51<br>57<br>59<br>50<br>51 |

## **E** XILINX®

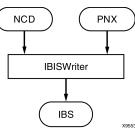

| Chapter 18 IBI | ISWriter                | 269 |

|----------------|-------------------------|-----|

| IBISWrite      | er Overview             | 269 |

| IBISWrite      | er Syntax               | 270 |

| IBISWrite      | er Options              | 271 |

| Chapter 19 CP  | PLDFit                  | 273 |

| CPLDFit        | Overview                | 273 |

| CPLDFit        | Syntax                  | 274 |

| CPLDFit        | Options                 | 275 |

| Chapter 20 TS  | SIM                     | 283 |

| TSIM Ov        | verview                 | 283 |

| TSIM Sy        | ntax                    | 283 |

| Chapter 21 TA  | Engine                  | 285 |

| TAEngin        | e Overview              | 285 |

| TAEngin        | e Syntax                | 286 |

| TAEngin        | e Options               | 286 |

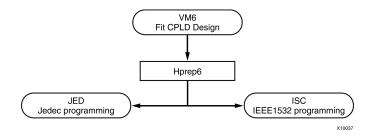

| Chapter 22 Hp  | orep6                   | 287 |

| Hprep6 C       | Overview                | 287 |

| Hprep6 C       | Options                 | 288 |

| Chapter 23 XF  | EOW                     | 291 |

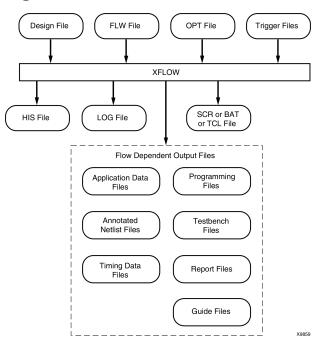

| XFLOW (        | Overview                | 291 |

| XFLOW S        | Syntax                  | 295 |

| XFLOW I        | Flow Types              | 296 |

| Flow File      | 25                      | 301 |

| XFLOW (        | Option Files            | 303 |

| XFLOW (        | Options                 | 305 |

| Running        | XFLOW                   | 309 |

| Chapter 24 NG  | GCBuild                 | 311 |

| NGCBuil        | ld Overview             | 311 |

| NGCBuil        | ld Syntax               | 312 |

| NGCBuil        | ld Options              | 313 |

| Chapter 25 Co  | ompxlib                 | 319 |

| Compxlil       | b Overview              | 319 |

| Compxlil       | b Syntax                | 320 |

| Compxlil       | b Options               | 321 |

| Compxlil       | b Command Line Examples | 326 |

| Specif     | ying Runtime Options                   |     |

|------------|----------------------------------------|-----|

| Samp       | e Configuration File (Windows Version) |     |

| Chapter 26 | XWebTalk                               | 335 |

| WebTa      | ılk Overview                           |     |

| XWeb       | Talk Syntax                            |     |

| XWeb       | Talk Options                           |     |

| Chapter 27 | Tcl Reference                          |     |

| Tcl Ov     | erview                                 |     |

| Tcl Fu     | ndamentals                             |     |

| Projec     | t and Process Properties               |     |

| Xilinx     | Tcl Commands for General Use           |     |

| Xilinx     | Tcl Commands for Advanced Scripting    |     |

| Examp      | ole Tcl Scripts                        |     |

| Appendix A | ISE Design Suite Files                 |     |

| Appendix B | EDIF2NGD and NGDBuild                  | 405 |

| EDIF2      | NGD Overview                           |     |

| EDIF2      | NGD Options                            |     |

| NGDI       | Build                                  |     |

| Appendix C | Additional Resources                   | 419 |

## Chapter 1

# Introduction

This chapter describes the command line programs for the ISE® Design Suite. This guide was formerly known as the *Development System Reference Guide*, but has been renamed to *Command Line Tools User Guide*.

## **Command Line Program Overview**

Xilinx® software command line programs allow you to implement and verify your design. The following table lists the programs you can use for each step in the design flow. For detailed information, see the Design Flow chapter in this guide.

| Design Flow Step                                                                            | Command Line Program                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Implementation                                                                       | NGDBuild, MAP, PAR, SmartXplorer, BitGen                                                                                                                                                                                          |

| Timing-driven Placement and Routing,<br>Re-synthesis, & Physical Synthesis<br>Optimizations | MAP<br><b>Note</b> MAP uses specified options to enable<br>timing-driven placement and routing<br>(-timing), and re-synthesis and physical<br>synthesis optimizations that can transform a<br>design to meet timing requirements. |

| Timing Simulation and Back Annotation<br>(Design Verification)                              | NetGen                                                                                                                                                                                                                            |

| Static Timing Analysis<br>(Design Verification)                                             | TRACE                                                                                                                                                                                                                             |

#### **Command Line Programs in the Design Flow**

You can run these programs in the standard design flow or use special options to run the programs for design preservation. Each command line program has multiple options, which allow you to control how a program executes. For example, you can set options to change output file names, to set a part number for your design, or to specify files to read in when executing the program. You can also use options to create guide files and run guide mode to maintain the performance of a previously implemented design.

Some of the command line programs described in this guide underlie many of the Xilinx Graphical User Interfaces (GUIs). The GUIs can be used with the command line programs or alone. For information on the GUIs, see the online Help provided with each Xilinx tool.

## **Command Line Syntax**

Command line syntax always begins with the command line program name. The program name is followed by any options and then by file names. Use the following rules when specifying command line options:

- Enter options in any order, preceded them with a dash (minus sign on the keyboard) and separate them with spaces.

- Be consistent with upper case and lower case.

- When an option requires a parameter, separate the parameter from the option by spaces or tabs. For example, the following shows the command line syntax for running PAR with the effort level set to high:

- Correct: par -ol high

- Incorrect: par -olhigh

- When using options that can be specified multiple times, precede each parameter with the option letter. In this example, the -l option shows the list of libraries to search:

- Correct: -1 xilinxun -1 synopsys

- Incorrect: -1 xilinxun synopsys

- Enter parameters that are bound to an option after the option.

- Correct: -f command\_file

- Incorrect: command\_file -f

Use the following rules when specifying file names:

- Enter file names in the order specified in the chapter that describes the command line program. In this example the correct order is program, input file, output file, and then physical constraints file.

- Correct: par input.ncd output.ncd freq.pcf

- Incorrect: par input.ncd freq.pcf output.ncd

- Use lower case for all file extensions (for example, .ncd).

## **Command Line Options**

The following options are common to many of the command line programs provided with the ISE® Design Suite.

- -f (Execute Commands File)

- -h (Help)

- -intstyle (Integration Style)

- -p (Part Number)

#### -f (Execute Commands File)

With any Xilinx® command line program for use with FPGA designs, you can store command line program options and file names in a command file. You can then execute the arguments by entering the program name with the **-f** option followed by the name of the command file. This is useful if you frequently execute the same arguments each time you execute a program or if the command line command becomes too long.

#### **Syntax**

-f command\_file

You can use the file in the following ways:

• To supply all of the command options and file names for the program, as in the following example:

par -f command\_file

*command\_file* is the name of the file that contains the command options and file names.

• To insert certain command options and file names within the command line, as in the following example:

**par** -f placeoptions -f routeoptions design\_i.ncd design\_o.ncd

- placeoptions is the name of a file containing placement command parameters.

- routeoptions is the name of a file containing routing command parameters.

You create the command file in ASCII format. Use the following rules when creating the command file:

- Separate program options and file names with spaces.

- Precede comments with the pound sign (#).

- Put new lines or tabs anywhere white space is allowed on the Linux or DOS command line.

- Put all arguments on the same line, one argument per line, or a combination of these.

- All carriage returns and other non-printable characters are treated as spaces and ignored.

- No line length limitation exists within the file.

#### Example

Following is an example of a command file:

```

#command line options for par for design mine.ncd

-w

Ol 5

/home/yourname/designs/xilinx/mine.ncd

#directory for output designs

/home/yourname/designs/xilinx/output.dir

#use timing constraints file

/home/yourname/designs/xilinx/mine.pcf

```

## -h (Help)

When you enter the program name followed by this option, you will get a message listing all options for the program and their parameters, as well as the file types used by the program. The message also explains each of the options.

#### **Syntax**

-h -help

| Symbol  | Description                                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| []      | Encloses items that are optional.                                                                                                 |

| {}      | Encloses items that may be repeated.                                                                                              |

| italics | Indicates a variable name or number for which you must substitute information.                                                    |

| ,       | Shows a range for an integer variable.                                                                                            |

| -       | Shows the start of an option name.                                                                                                |

| :       | Binds a variable name to a range.                                                                                                 |

| 1       | Logical OR to show a choice of one out of<br>many items. The OR operator may only<br>separate logical groups or literal keywords. |

| ()      | Encloses a logical grouping for a choice between sub-formats.                                                                     |

#### Example

Following are examples of syntax used for file names:

- *infile*[.ncd] shows that typing the .ncd extension is optional but that the extension must be .ncd.

- *infile.edn* shows that the .edn extension is optional and is appended only if there is no other extension in the file name.

For architecture-specific programs, such as BitGen, you can enter the following to get a verbose help message for the specified architecture:

program\_name **-h** architecture\_name

You can redirect the help message to a file to read later or to print out by entering the following:

program\_name -h > filename

On the Linux command line, enter the following to redirect the help message to a file and return to the command prompt.

program\_name **-h** > & filename

#### -intstyle (Integration Style)

This option limits screen output, based on the integration style that you are running, to warning and error messages only.

#### Syntax

-intstyle ise |xflow|silent

When using **-intstyle**, one of three modes must be specified:

- -intstyle ise indicates the program is being run as part of an integrated design environment.

- **-intstyle xflow** indicates the program is being run as part of an integrated batch flow.

- -intstyle silent limits screen output to warning and error messages only.

**Note** -intstyle is automatically invoked when running in an integrated environment such as Project Navigator or XFLOW.

## -p (Part Number)

This option specifies the part into which your design is implemented.

#### Syntax

**-p** part\_number

This option can specify an architecture only, a complete part specification (device, package, and speed), or a partial specification (for example, device and package only). The part number or device name must be from a device library you have installed on your system.

A complete Xilinx<sup>®</sup> part number consists of the following elements:

- Architecture (for example, spartan3e)

- Device (for example, xc3s100e)

- Package (for example, vq100)

- Speed (for example, -4)

**Note** The Speedprint program lists block delays for device speed grades. The **-s** option lets you specify a speed grade. If you do not specify a speed grade, Speedprint reports the default speed grade for the device you are targeting.

#### **Specifying Part Numbers**

You can specify a part number at various points in the design flow, not all of which require the **-p** option.

- In the input netlist (does not require the -p option)

- In a Netlist Constraints File (NCF) (does not require the **-p** option)

- With the **-p** option when you run a netlist reader (EDIF2NGD)

- In the User Constraints File (UCF) (does not require the **-p** option)

- With the **-p** option when you run NGDBuild

By the time you run NGDBuild, you must have already specified a device architecture.

• With the **-p** option when you run MAP

When you run MAP you must specify an architecture, device, and package, either on the MAP command line or earlier in the design flow. If you do not specify a speed, MAP selects a default speed. You can only run MAP using a part number from the architecture you specified when you ran NGCBuild.

- With the **-p** option when you run SmartXplorer (FPGA designs only)

- With the **-p** option when you run CPLDFit (CPLD designs only)

**Note** Part numbers specified in a later step of the design flow override a part number specified in an earlier step. For example, a part specified when you run MAP overrides a part specified in the input netlist.

#### **Examples**

The following examples show how to specify parts on the command line.

| Specification        | Examples                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------|

| Architecture only    | virtex4<br>virtex5<br>spartan3<br>spartan3a<br>xc9500<br>xpla3 (CoolRunner™ XPLA3 devices) |

| Device only          | xc4vfx12<br>xc3s100e                                                                       |

| DevicePackage        | xc4fx12sf363<br>xc3s100evq100                                                              |

| Device-Package       | xc4vfx12-sf363<br>xc3s100e-vq100                                                           |

| DeviceSpeed-Package  | xc4vfx1210-sf363<br>xc3s100e4-vq100                                                        |

| DevicePackage-Speed  | xc4fx12sf363-10<br>xc3s100evq100-4                                                         |

| Device-Speed-Package | xc4vfx12-10-sf363<br>xc3s100e-4-vq100                                                      |

| Device-SpeedPackage  | xc4vfx12-10sf363<br>xc3s100e-4vq100                                                        |

## **Invoking Command Line Programs**

You start Xilinx® command line programs by entering a command at the Linux or DOS command line. See the program-specific chapters in this book for the appropriate syntax

Xilinx also offers the XFLOW program, which lets you automate the running of several programs at one time. See the XFLOW chapter for more information.

## Chapter 2

# Design Flow

This chapter describes the process for creating, implementing, verifying, and downloading designs for Xilinx® FPGA and CPLD devices. For a complete description of Xilinx FPGA and CPLDs devices, refer to the Xilinx Data Sheets at: <a href="http://www.xilinx.com/support/">http://www.xilinx.com/support/</a>

## **Design Flow Overview**

The standard design flow comprises the following steps:

- 1. **Design Entry and Synthesis -** Create your design using a Xilinx®-supported schematic editor, a Hardware Description Language (HDL) for text-based entry, or both. If you use an HDL for text-based entry, you must synthesize the HDL file into an EDIF file or, if you are using the Xilinx Synthesis Technology (XST) GUI, you must synthesize the HDL file into an NGC file.

- 2. **Design Implementation -** Convert the logical design file format, such as EDIF, that you created in the design entry and synthesis stage into a physical file format by implementing to a specific Xilinx architecture. The physical information is contained in the Native Circuit Description (NCD) file for FPGAs and the VM6 file for CPLDs. Then create a bitstream file from these files and optionally program a PROM or EPROM for subsequent programming of your Xilinx device.

- 3. **Design Verification -** Using a gate-level simulator or cable, ensure that your design meets timing requirements and functions properly. See the iMPACT online help for information about Xilinx download cables and demonstration boards.

The full design flow is an iterative process of entering, implementing, and verifying your design until it is correct and complete. The command line tools provided with the ISE® Design Suite allow quick design iterations through the design flow cycle. Xilinx devices permit unlimited reprogramming. You do not need to discard devices when debugging your design in circuit.

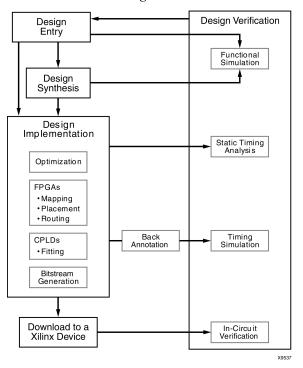

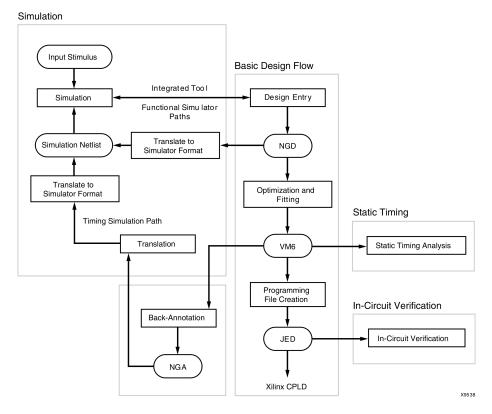

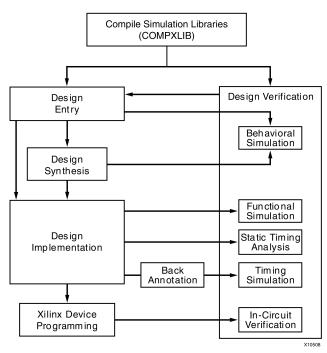

#### **Xilinx Design Flow**

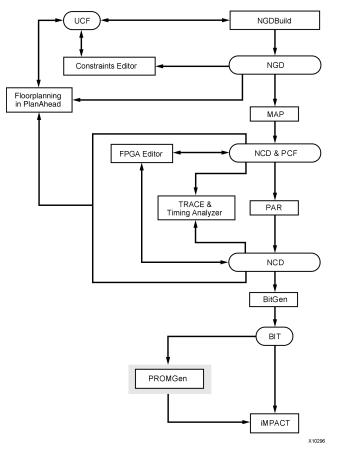

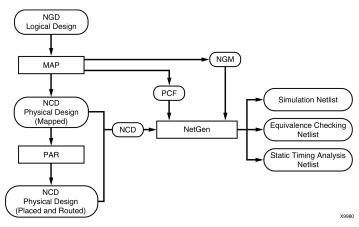

This figure shows the standard Xilinx design flow.

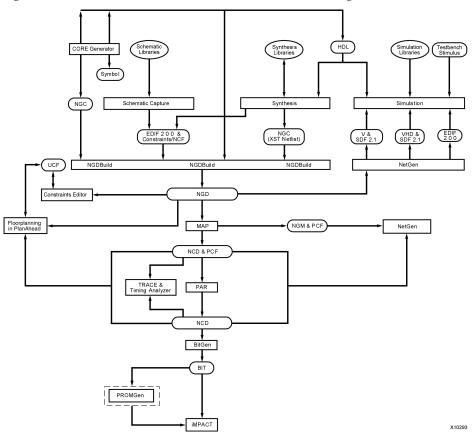

#### Xilinx Software Design Flow (FPGAs)

This figure shows the Xilinx software flow chart for FPGA designs.

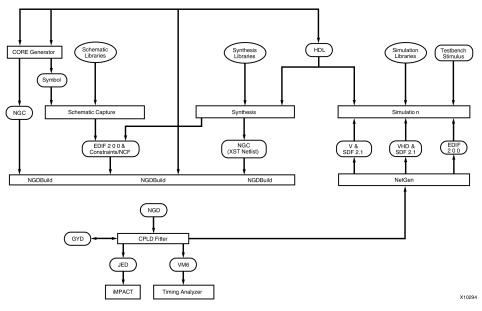

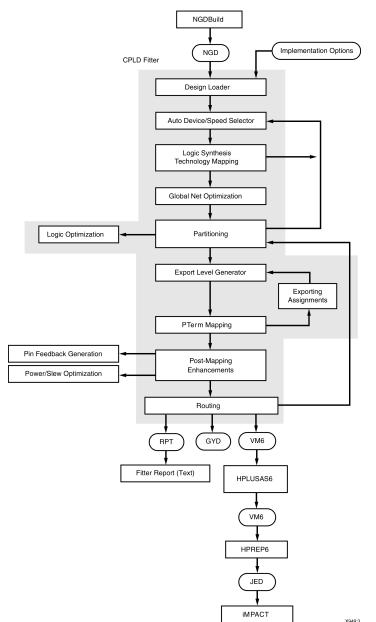

Xilinx Software Design Flow (CPLDs)

This figure shows the Xilinx software flow chart for CPLD designs.

## **Design Entry and Synthesis**

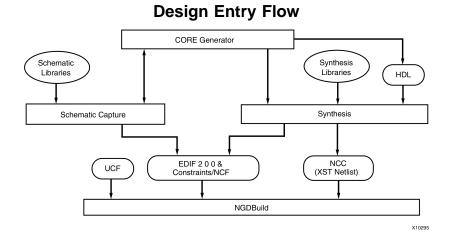

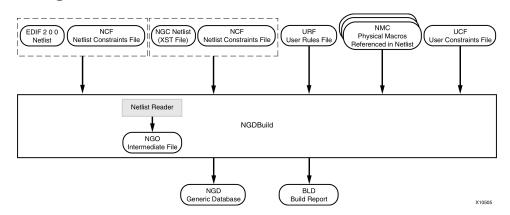

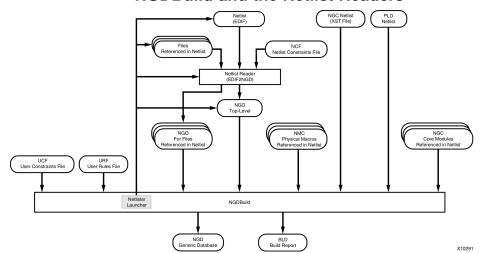

You can enter a design with a schematic editor or a text-based tool. Design entry begins with a design concept, expressed as a drawing or functional description. From the original design, a netlist is created, then synthesized and translated into a native generic object (NGO) file. This file is fed into the Xilinx® software program called NGDBuild, which produces a logical Native Generic Database (NGD) file.

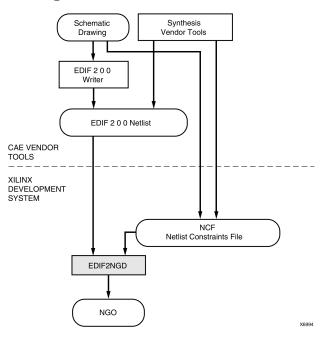

The following figure shows the design entry and synthesis process.

### **Hierarchical Design**

Design hierarchy is important in both schematic and HDL entry for the following reasons:

- Helps you conceptualize your design

- Adds structure to your design

- Promotes easier design debugging

- Makes it easier to combine different design entry methods (schematic, HDL, or state editor) for different parts of your design

- Makes it easier to design incrementally, which consists of designing, implementing, and verifying individual parts of a design in stages

- Reduces optimization time

- Facilitates concurrent design, which is the process of dividing a design among a number of people who develop different parts of the design in parallel.

In hierarchical designing, a specific hierarchical name identifies each library element, unique block, and instance you create. The following example shows a hierarchical name with a 2-input OR gate in the first instance of a multiplexer in a 4-bit counter:

/Acc/alu\_1/mult\_4/8count\_3/4bit\_0/mux\_1/or2

Xilinx® strongly recommends that you name the components and nets in your design. These names are preserved and used by FPGA Editor. These names are also used for back-annotation and appear in the debug and analysis tools. If you do not name your components and nets, the Schematic Editor automatically generates the names. For example, if left unnamed, the software might name the previous example, as follows:

/\$1a123/\$1b942/\$1c23/\$1d235/\$1e121/\$1g123/\$1h57

**Note** It is difficult to analyze circuits with automatically generated names, because the names only have meaning for Xilinx software.

#### Partitions

In hierarchical design flows, such as Design Preservation and Partial Reconfiguration, partitions are used to define hierarchical boundaries so that a complex design can be broken up into smaller blocks. Partitions create a boundary or insulation around the hierarchical module, which isolates the module from other parts of the design. A partition that has been implemented and exported can be re-inserted into the design using a simple cut-and-paste type function, which preserves the placement and routing results for the isolated module. All of the partition definitions and controls are done in a file called xpartition.pxml. For more information on using hierarchical design flows and implementing partitions, see the *Hierarchical Design Methodology Guide (UG748)*.

#### **PXML** File

Partition definitions are contained in the xpartition.pxml file. The PXML file name is case-sensitive, and must be named xpartition.pxml. The top level module of the design must be defined as a partition in addition to any optional lower level partitions. The PXML file can be created by hand, from scripts, or from a tool such as the PlanAhead<sup>TM</sup> software. The PXML will be picked up automatically by the ISE® Design Suite implementation tools when located in the current working directory. For more information about using the xpartition.pxml file, see the *Hierarchical Design Methodology Guide* (*UG748*). An example xpartition.pxml file is available at %XILINX%/PlanAhead/testcases/templates (where %XILINX% is your installation directory) if you wish to create a PXML file by hand.

**Note** All paths in the PXML file must be absolute paths.

<?xml version="1.0" encoding="UTF-8" ?>

```

<project FileVersion="1.2" Name="Example" ProjectVersion="2.0">

<Partition Name="/top" State="implement" ImportLocation="NONE">

<Partition Name="/top/module_A" State="import" ImportLocation="/home/user/Example/import" Preserve="routing">

</Partition>

<Partition Name="/top/module_B" State="import" ImportLocation="/home/user/Example/import" Preserve="routing">

</Partition>

<Partition Name="/top/module_B" State="import" ImportLocation="/home/user/Example/import" Preserve="routing">

</Partition>

</Partition>

```

```

</Project>

```

|                |              | •                                                            |

|----------------|--------------|--------------------------------------------------------------|

| Attribute name | Value        | Description                                                  |

| FileVersion    | 1.2          | Used for internal purposes. Do <i>not</i> change this value. |

| Name           | Project_Name | <i>Project_Name</i> is user defined.                         |

| ProjectVersion | 2.0          | Used for internal purposes. Do <i>not</i> change this value. |

#### **PXML** attributes for Project definition

| Attribute name | Value          | Description                                                                                                                                                                                                                                              |

|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name           | Partition_Name | Hierarchical instance name of module in which the partition should be applied.                                                                                                                                                                           |

| State          | "implement"    | Partition is implemented from scratch.                                                                                                                                                                                                                   |

|                | "import"       | Partition is imported and preserved according to the level set by <b>Preserve</b> .                                                                                                                                                                      |

| ImportLocation | path           | Ignored if <b>State</b> does not equal "import."<br>The path can be relative or absolute, but the<br>location specified must contain a valid "export"<br>directory when <b>State=import</b> . "NONE" is a<br>predefined keyword for no import directory. |

| ImportTag      | Partition_Name | Allows a partition to be imported into a different level of hierarchy than it was initially implemented in. Set the value to the hierarchical instance name of the partition where it was implemented.                                                   |

| Preserve       | "routing"      | 100% placement and routing is preserved. This is the default for the top level Partition.                                                                                                                                                                |

|                | "placement"    | Placement is preserved but routing can be modified.                                                                                                                                                                                                      |

|                | "synthesis"    | Placement and routing can be modified.                                                                                                                                                                                                                   |

|                | "inherit"      | Inherit value from the parent partition. This is<br>the default for all partitions except the top level<br>partition.                                                                                                                                    |

| BoundaryOpt    | "all"          | Enables the implementation tools to do<br>optimization on partition ports connected to<br>constraints as well as unused partition ports.                                                                                                                 |

|                | "none"         | Normal partition optimization rules apply.<br>Optimization is allowed only within partition<br>boundaries. This is the default value.                                                                                                                    |

## **Schematic Entry Overview**

Schematic tools provide a graphic interface for design entry. You can use these tools to connect symbols representing the logic components in your design. You can build your design with individual gates, or you can combine gates to create functional blocks. This section focuses on ways to enter functional blocks using library elements and the CORE Generator<sup>TM</sup> tool.

#### **Library Elements**

Primitives and macros are the "building blocks" of component libraries. Xilinx® libraries provide primitives, as well as common high-level macro functions. Primitives are basic circuit elements, such as AND and OR gates. Each primitive has a unique library name, symbol, and description. Macros contain multiple library elements, which can include primitives and other macros.

You can use the following types of macros with Xilinx FPGAs:

- Soft macros have pre-defined functionality but have flexible mapping, placement, and routing. Soft macros are available for all FPGAs.

- Relationally placed macros (RPMs) have fixed mapping and relative placement. RPMs are available for all device families, except the XC9500 family.

Macros are not available for synthesis because synthesis tools have their own module generators and do not require RPMs. If you wish to override the module generation, you can instantiate modules created using CORE Generator. For most leading-edge synthesis tools, this does not offer an advantage unless it is for a module that cannot be inferred.

#### **CORE Generator Tool (FPGAs Only)**

The Xilinx CORE Generator tool delivers parameterizable cores that are optimized for Xilinx FPGAs. The library includes cores ranging from simple delay elements to complex DSP (Digital Signal Processing) filters and multiplexers. For details, refer to the CORE Generator Help (part of ISE Help). You can also refer to the Xilinx IP (Intellectual Property) Center Web site at <u>http://www.xilinx.com/ipcenter</u>, which offers the latest IP solutions. These solutions include design reuse tools, free reference designs, Digital Signal Processing (DSP), PCI<sup>TM</sup> solutions, IP implementation tools, cores, specialized system level services, and vertical application IP solutions.

## **HDL Entry and Synthesis**

A typical Hardware Description Language (HDL) supports a mixed-level description in which gate and netlist constructs are used with functional descriptions. This mixed-level capability lets you describe system architectures at a high level of abstraction and then incrementally refine the detailed gate-level implementation of a design.

HDL descriptions offer the following advantages:

- You can verify design functionality early in the design process. A design written as an HDL description can be simulated immediately. Design simulation at this high level, at the gate-level before implementation, allows you to evaluate architectural and design decisions.

- An HDL description is more easily read and understood than a netlist or schematic description. HDL descriptions provide technology-independent documentation of a design and its functionality. Because the initial HDL design description is technology independent, you can use it again to generate the design in a different technology, without having to translate it from the original technology.

- Large designs are easier to handle with HDL tools than schematic tools.

After you create your HDL design, you must synthesize it. During synthesis, behavioral information in the HDL file is translated into a structural netlist, and the design is optimized for a Xilinx® device. Xilinx supports HDL synthesis tools for several third-party synthesis vendors. In addition, Xilinx offers its own synthesis tool, Xilinx Synthesis Technology (XST). For more information, see the *XST User Guide for Virtex-4*, *Virtex-5*, *Spartan-3*, and Newer CPLD Devices (UG627) or the XST User Guide for Virtex-6, *Spartan-6*, and 7 Series Devices (UG687). For detailed information on synthesis, see the Synthesis and Simulation Design Guide (UG626).

## **Functional Simulation**

After you create your design, you can simulate it. Functional simulation tests the logic in your design to determine if it works properly. You can save time during subsequent design steps if you perform functional simulation early in the design flow. See Simulation for more information.

#### Constraints

You may want to constrain your design within certain timing or placement parameters. You can specify mapping, block placement, and timing specifications.

You can enter constraints manually or use the Constraints Editor or FPGA Editor, which are graphical user interface (GUI) tools provided by Xilinx®. You can use the Timing Analyzer GUI or TRACE command line program to evaluate the circuit against these constraints by generating a static timing analysis of your design. See the TRACE chapter and the online Help provided with the ISE® Design Suite for more information. For more information on constraints, see the *Constraints Guide (UG625)*.

#### Mapping Constraints (FPGAs Only)

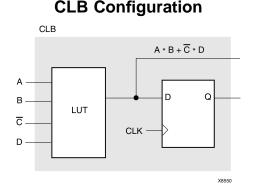

You can specify how a block of logic is mapped into CLBs using an FMAP for all Spartan® and Virtex® FPGA architectures. These mapping symbols can be used in your schematic. However, if you overuse these specifications, it may be difficult to route your design.

#### **Block Placement**

Block placement can be constrained to a specific location, to one of multiple locations, or to a location range. Locations can be specified in the schematic, with synthesis tools, or in the User Constraints File (UCF). Poor block placement can adversely affect both the placement and the routing of a design. Only I/O blocks require placement to meet external pin requirements.

#### **Timing Specifications**

You can specify timing requirements for paths in your design. PAR uses these timing specifications to achieve optimum performance when placing and routing your design.

#### **Netlist Translation Programs**

Netlist translation programs let you read netlists into the Xilinx® software tools. EDIF2NGD lets you read an Electronic Data Interchange Format (EDIF) 2 0 0 file. The NGDBuild program automatically invokes these programs as needed to convert your EDIF file to an NGD file, the required format for the Xilinx software tools. NGC files output from the Xilinx XST synthesis tool are read in by NGDBuild directly.

You can find detailed descriptions of the EDIF2NGD, and NGDBuild programs in the NGDBuild chapter and the EDIF2NGD and NGDBuild Appendix.

## **Design Implementation**

Design Implementation begins with the mapping or fitting of a logical design file to a specific device and is complete when the physical design is successfully routed and a bitstream is generated. You can alter constraints during implementation just as you did during the Design Entry step. See Constraints for information.

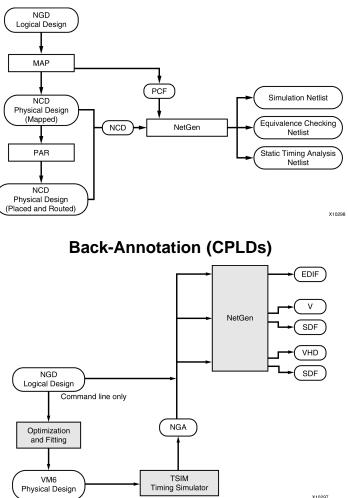

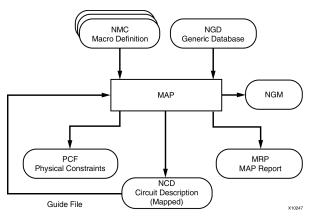

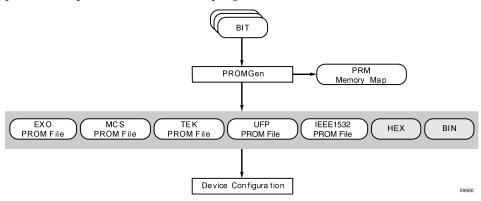

The following figure shows the design implementation process for FPGA designs:

## **Design Implementation Flow (FPGAs)**

The following figure shows the design implementation process for CPLD designs:

#### **Design Implementation Flow (CPLDs)**

## Mapping (FPGAs Only)

For FPGAs, the MAP command line program maps a logical design to a Xilinx® FPGA. The input to MAP is an NGD file, which contains a logical description of the design in terms of both the hierarchical components used to develop the design and the lower-level Xilinx primitives, and any number of NMC (hard placed-and-routed macro) files, each of which contains the definition of a physical macro. MAP then maps the logic to the components (logic cells, I/O cells, and other components) in the target Xilinx FPGA.

The output design from MAP is an NCD file, which is a physical representation of the design mapped to the components in the Xilinx FPGA. The NCD file can then be placed and routed, using the PAR command line program. See the MAP chapter for detailed information.

**Note** MAP provides options that enable advanced optimizations that are capable of improving timing results beyond standard implementations. These advanced optimizations can transform a design prior to or after placement. Optimizations can be applied at two different stages in the Xilinx design flow. The first stage happens right after the initial mapping of the logic to the architecture slices; the second stage if after placement. See Re-Synthesis and Physical Synthesis Optimizations in the MAP chapter for more information.

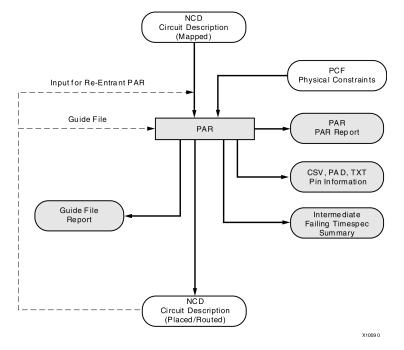

## Placing and Routing (FPGAs Only)

For FPGAs, the PAR command line program takes a mapped NCD file as input, places and routes the design, and outputs a placed and routed Native Circuit Description (NCD) file, which is used by the bitstream generator, BitGen. The output NCD file can also act as a guide file when you reiterate placement and routing for a design to which minor changes have been made after the previous iteration. See the PAR chapter for detailed information.

You can also use FPGA Editor to do the following:

- Place and route critical components before running automatic place and route tools on an entire design.

- Modify placement and routing manually. The editor allows both automatic and manual component placement and routing.

**Note** For more information, see the online Help provided with FPGA Editor.

## **Bitstream Generation (FPGAs Only)**

For FPGAs, the BitGen command line program produces a bitstream for Xilinx® device configuration. BitGen takes a fully routed NCD file as its input and produces a configuration bitstream, which is a binary file with a .bit extension. The BIT file contains all of the configuration information from the NCD file defining the internal logic and interconnections of the FPGA, plus device-specific information from other files associated with the target device. See the BitGen chapter for detailed information.

After you generate your BIT file, you can download it to a device using the iMPACT GUI. You can also format the BIT file into a PROM file using the PROMGen command line program and then download it to a device using the iMPACT GUI. See the PROMGen chapter of this guide or the iMPACT online help for more information.

## **Design Verification**

Design verification is testing the functionality and performance of your design. You can verify Xilinx® designs in the following ways:

- Simulation (functional and timing)

- Static timing analysis

- In-circuit verification

The following table lists the different design tools used for each verification type.

| Verification Type       | Tools                                                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Simulation              | Third-party simulators (integrated and non-integrated)                                                                      |

| Static Timing Analysis  | TRACE (command line program)                                                                                                |

|                         | Timing Analyzer (GUI)                                                                                                       |

|                         | Mentor Graphics TAU and Innoveda BLAST<br>software for use with the STAMP file format<br>(for I/O timing verification only) |

| In-Circuit Verification | Design Rule Checker (command line program)                                                                                  |

|                         | Download cable                                                                                                              |

#### **Verification Tools**

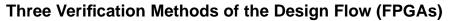

Design verification procedures should occur throughout your design process, as shown in the following figures.

Simulation

The following figure shows the verification methods of the design flow for CPLDs.

#### Three Verification Methods of the Design Flow (CPLDs)

#### Simulation

You can run functional or timing simulation to verify your design. This section describes the back-annotation process that must occur prior to timing simulation. It also describes the functional and timing simulation methods for both schematic and HDL-based designs.

#### **Back-Annotation**

Before timing simulation can occur, the physical design information must be translated and distributed back to the logical design. For FPGAs, this back-annotation process is done with a program called NetGen. For CPLDs, back-annotation is performed with the TSim Timing Simulator. These programs create a database, which translates the back-annotated information into a netlist format that can be used for timing simulation.

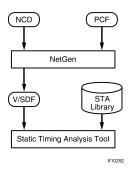

#### **Back-Annotation Flow for FPGAs**

#### NetGen

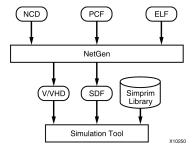

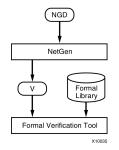

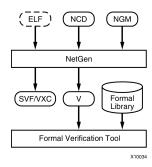

NetGen is a command line program that distributes information about delays, setup and hold times, clock to out, and pulse widths found in the physical Native Circuit Description (NCD) design file back to the logical Native Generic Database (NGD) file and generates a Verilog or VHDL netlist for use with supported timing simulation, equivalence checking, and static timing analysis tools.

NetGen reads an NCD as input. The NCD file can be a mapped-only design, or a partially or fully placed and routed design. An NGM file, created by MAP, is an optional source of input. NetGen merges mapping information from the optional NGM file with placement, routing, and timing information from the NCD file.

**Note** NetGen reads an NGA file as input to generate a timing simulation netlist for CPLD designs.

See the NetGen chapter for detailed information.

#### **Functional Simulation**

Functional simulation determines if the logic in your design is correct before you implement it in a device. Functional simulation can take place at the earliest stages of the design flow. Because timing information for the implemented design is not available at this stage, the simulator tests the logic in the design using unit delays.

**Note** It is usually faster and easier to correct design errors if you perform functional simulation early in the design flow.

#### **Timing Simulation**

Timing simulation verifies that your design runs at the desired speed for your device under worst-case conditions. This process is performed after your design is mapped, placed, and routed for FPGAs or fitted for CPLDs. At this time, all design delays are known.

Timing simulation is valuable because it can verify timing relationships and determine the critical paths for the design under worst-case conditions. It can also determine whether or not the design contains set-up or hold violations.

Before you can simulate your design, you must go through the back-annotation process, above. During this process, NetGen creates suitable formats for various simulators.

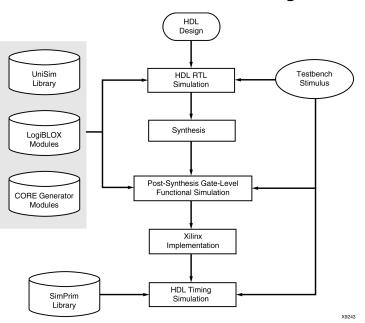

#### **HDL-Based Simulation**

Xilinx® supports functional and timing simulation of HDL designs at the following points:

- Register Transfer Level (RTL) simulation, which may include the following:

- Instantiated UNISIM library components

- − CORE Generator<sup>TM</sup> models

- Dedicated blocks (SecureIP)

- Post-synthesis functional simulation with one of the following:

- Gate-level UNISIM library components

- CORE Generator models

- Hard IP (SecureIP)

- Post-implementation back-annotated timing simulation with the following:

- SIMPRIM library components

- Hard IP (SecureIP)

- Standard Delay Format (SDF) file

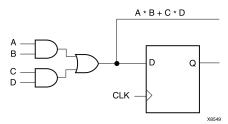

The following figure shows when you can perform functional and timing simulation:

**Simulation Points for HDL Designs**

The three primary simulation points can be expanded to allow for two post-synthesis simulations. These points can be used if the synthesis tool cannot write VHDL or Verilog, or if the netlist is not in terms of UNISIM components. The following table lists all the simulation points available in the HDL design flow.

| Simulation                                | UNISIM | SIMPRIM | SDF |

|-------------------------------------------|--------|---------|-----|

| RTL                                       | Х      |         |     |

| Post-Synthesis                            | Х      |         |     |

| Functional<br>Post-NGDBuild<br>(Optional) |        | X       |     |

| Functional Post-MAP<br>(Optional)         |        | X       | Х   |

| Post-Route Timing                         |        | Х       | Х   |

**Five Simulation Points in HDL Design Flow**

These simulation points are described in the "Simulation Points" section of the *Synthesis* and *Simulation Design Guide* (UG626).

The libraries required to support the simulation flows are described in detail in the "VHDL/Verilog Libraries and Models" section of the *Synthesis and Simulation Design Guide* (*UG626*). The flows and libraries support close functional equivalence of initialization behavior between functional and timing simulations. This is due to the addition of methodologies and library cells to simulate Global Set/Reset (GSR) and Global 3-State (GTS) behavior.

Xilinx VHDL simulation supports the VITAL standard. This standard allows you to simulate with any VITAL-compliant simulator. Built-in Verilog support allows you to simulate with the Cadence Verilog-XL and compatible simulators. Xilinx HDL simulation supports all current Xilinx FPGA and CPLD devices. Refer to the *Synthesis and Simulation Design Guide* (UG626) for the list of supported VHDL and Verilog standards.

## Static Timing Analysis (FPGAs Only)

Static timing allows you to determine path delays in your design. Following are the two major goals of static timing analysis:

Timing verification

This is verifying that the design meets your timing constraints.

Reporting

This is enumerating input constraint violations and placing them into an accessible file. You can analyze partially or completely placed and routed designs. The timing information depends on the placement and routing of the input design.

You can run static timing analysis using the Timing Reporter And Circuit Evaluator (TRACE) command line program. See the TRACE chapter for detailed information. You can also use the Timing Analyzer to perform this function. See the Help that comes with Timing Analyzer for additional information. Use either tool to evaluate how well the place and route tools met the input timing constraints.

#### **In-Circuit Verification**

As a final test, you can verify how your design performs in the target application. In-circuit verification tests the circuit under typical operating conditions. Because you can program your FPGA devices repeatedly, you can easily load different iterations of your design into your device and test it in-circuit. To verify your design in-circuit, download your design bitstream into a device with the appropriate Xilinx® cable.

**Note** For information about Xilinx cables and hardware, see the iMPACT online help.

#### Design Rule Checker (FPGAs Only)

Before generating the final bitstream, it is important to use the DRC option in BitGen to evaluate the NCD file for problems that could prevent the design from functioning properly. DRC is invoked automatically unless you use the **-d** option. See the Physical Design Rule Check chapter and the BitGen chapter for detailed information.

#### Probe

The Xilinx PROBE function in FPGA Editor provides real-time debug capability good for analyzing a few signals at a time. Using PROBE a designer can quickly identify and route any internal signals to available I/O pins without having to replace and route the design. The real-time activity of the signal can then be monitored using normal lab test equipment such as logic/state analyzers and oscilloscopes.

#### ChipScope<sup>™</sup> ILA and ChipScope Pro

The ChipScope toolset was developed to assist engineers working at the PCB level. ChipScope ILA actually embeds logic analyzer cores into your design. These logic cores allow the user to view all the internal signals and nodes within an FPGA. Triggers are changeable in real-time without affecting the user logic or requiring recompilation of the user design.

## **FPGA** Design Tips

The Xilinx® FPGA architecture is best suited for synchronous design. Strict synchronous design ensures that all registers are driven from the same time base with no clock skew. This section describes several tips for producing high-performance synchronous designs.

### **Design Size and Performance**

Information about design size and performance can help you to optimize your design. When you place and route your design, the resulting report files list the number of CLBs, IOBs, and other device resources available. A first pass estimate can be obtained by processing the design through the MAP program.

If you want to determine the design size and performance without running automatic implementation software, you can quickly obtain an estimate from a rough calculation based on the Xilinx FPGA architecture.

## Chapter 3

# PARTGen

This chapter describes PARTGen.

## **PARTGen Overview**

PARTGen is a Xilinx® command line tool that displays architectural details about supported Xilinx devices.

#### **Device Support**

This program is compatible with the following device families:

- 7 series

- Spartan®-3, Spartan-3A, Spartan-3E, and Spartan-6

- Virtex<sup>®</sup>-4, Virtex-5, and Virtex-6

- CoolRunner<sup>™</sup> XPLA3 and CoolRunner-II

- XC9500 and XC9500XL

## **PARTGen Input Files**

PARTGen does not have any user input files.

## **PARTGen Output Files**

PARTGen outputs two file types:

- PARTGen Partlist Files (ASCII and XML)

- PARTGen Package Files (ASCII)

#### **PARTGen Partlist Files**

PARTGen partlist files contain detailed information about architectures and devices, including supported synthesis tools. Partlist files are generated in both ASCII (.xct) and XML (.xml) formats.

The partlist file is automatically generated in XML format whenever a partlist file is created with the PARTGen -p (Generate Partlist and Package Files) or PARTGen -v (Generate Partlist and Package Files) options. No separate command line option is required.

The partlist file is a series of part entries. There is one entry for every part supported in the installed software. The following sections describe the information contained in the partlist file.

- PARTGen Partlist File Header

- PARTGen Partlist File Device Attributes for Both -p and -v Options

- PARTGen Partlist File Device Attributes for -v Option Only

#### PARTGen Partlist File Header

The first part of a PARTGen partlist file is a header for the entry.

part architecture family partname diename packagefilename

#### PARTGen Partlist File Header Example for XC6VLX550TFF1759 Device

partVIRTEX XC6VLX550Tff1759 NA.die xc6vlx550tff1759.pkg

#### PARTGen Partlist File Device Attributes for both -p and -v Options

The following PARTGen partlist file device attributes display for both the **-p** and **-v** command line options.

- CLB row and column sizes NCLBROWS=# NCLBCOLS=#

- Sub-family designation

STYLE=sub\_family (For example, STYLE = Virtex6)

- Input registers

IN\_FF\_PER\_IOB=#

- Output registers OUT\_FF\_PER\_IOB=#

- Number of pads per row and per column NPADS\_PER\_ROW=# NPADS\_PER\_COL=#

- Bitstream information

- Number of frames: NFRAMES=#

- Number bits/frame: NBITSPERFRAME=#

- Stepping levels supported: STEP=#

- I/O Standards

For each I/O standard, PARTGen now reports all properties in a parsable format. This allows third party tools to perform complete I/O banking design rules checking (DRC).

The following information has been added to the partlist.xct and partlist.xml output for each available I/O standard:

```

IOSTD_NAME: LVTTL \

IOSTD_DRIVE: 12 2 4 6 8 16 24 \

IOSTD_SLEW: SLOW FAST \

IOSTD_DIRECTION: INPUT=1 OUTPUT=1 BIDIR=1 \

IOSTD_INPUTTERM: NONE \

IOSTD_OUTPUTTERM: NONE \

IOSTD_VCCO: 3.300000 \

IOSTD_VREF: 100.000000 \

IOSTD_VREF: 100.000000 \

IOSTD_VREQUIRED: 0 \

IOSTD_DIFFTERMREQUIRED: 0 \

```

For IOSTD\_DRIVE and IOSTD\_SLEW, the default values are reported first in the list. For true/false values:

- 1 indicates true

- 0 indicates false

A value of 100.000000 for IOSTD\_VREF indicates that this keyword is undefined for this standard.

SO and WASSO Calculations