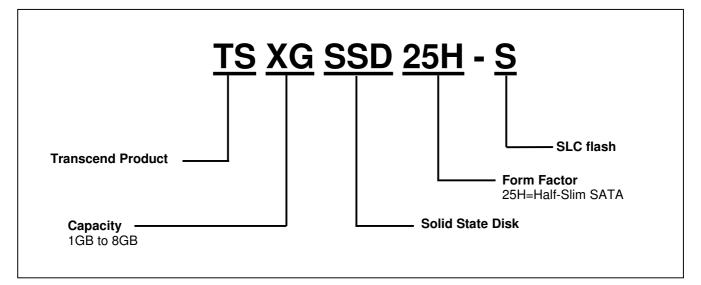

# TS2GSSD25H-S TS8GSSD25H-S

### Description

Compatible with SATA II 3.0Gb/s standard, due to smaller size, high speed, low power consumption, and great reliability, Transcend's Half-Slim SATA Solid State Disk is the perfect storage device for tablet PC, laptop, and industrial PC.

### Placement

### Features

- Fully compatible with devices and OS that support the SATA II 3.0Gb/s standard

- Non-Volatile Flash Memory (SLC) for outstanding data retention and reliability

- Global Wear-Leveling and Block management for reliability

- Built-in ECC (Error Correction Code) functionality

- Shock resistance

- Power Shield to prevent data loss when sudden power

off

- Support Security Command

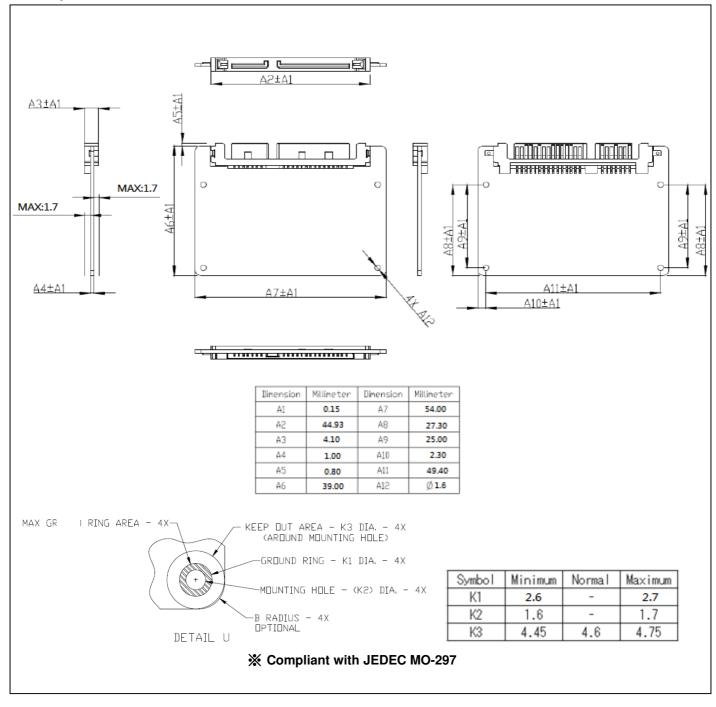

- Compliant with JEDEC MO-297

- RoHS compliant

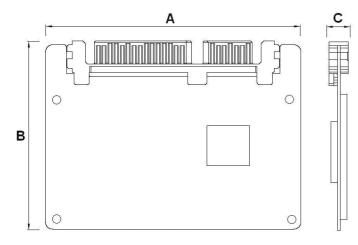

### **Dimensions**

1

| Side | Millimeters  | Inches            |

|------|--------------|-------------------|

| A    | 54.00 ± 0.15 | $2.130 \pm 0.006$ |

| В    | 39.80 ± 0.30 | 1.570 ± 0.012     |

| С    | 4.10 ± 0.15  | 0.160 ± 0.006     |

### TS2GSSD25H-S TS8GSSD25H-S

### **Specifications**

| Physical Specification |        |                                    |  |  |

|------------------------|--------|------------------------------------|--|--|

| Form Factor            |        | 2.5" Half-Slim SATA (JEDEC MO-297) |  |  |

| Storage Capacities     |        | 1GB / 2GB / 4GB / 8GB              |  |  |

|                        | Length | $54.00 \pm 0.15$                   |  |  |

| Dimensions (mm)        | Width  | $39.80\pm0.30$                     |  |  |

|                        | Height | $4.10 \pm 0.15$                    |  |  |

| Input Voltage          |        | 5V ± 5%                            |  |  |

| Weight                 |        | 10 g                               |  |  |

| Connector              |        | SATA 7+15 pins combo connector     |  |  |

| Environmental Specifications         |  |                            |

|--------------------------------------|--|----------------------------|

| Operating Temperature  0 °C to 70 °C |  | 0 °C to 70 °C              |

| Storage Temperature                  |  | - 40 ℃ to 85 ℃             |

| Operating                            |  | 0% to 95% (Non-condensing) |

| Humidity Non-Operating               |  | 0% to 95% (Non-condensing) |

| Performance  |                   |                    |                           |                            |                                     |                                      |                                           |                                            |

|--------------|-------------------|--------------------|---------------------------|----------------------------|-------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------------------|

| АТТО         |                   |                    | CrystalDiskMark           |                            |                                     |                                      | IOmeter                                   |                                            |

| Model P/N    | Max.<br>Read<br>* | Max.<br>Write<br>* | Sequential<br>Read<br>*** | Sequential<br>Write<br>*** | Random<br>Read<br>(4KB QD32)<br>*** | Random<br>Write<br>(4KB QD32)<br>*** | IOPS<br>Random Read<br>(4KB QD32)<br>**** | IOPS<br>Random Write<br>(4KB QD32)<br>**** |

| TS1GSSD25H-S | 50                | 15                 | 50                        | 15                         | 13                                  | 0.2                                  | 4000                                      | 270                                        |

| TS2GSSD25H-S | 95                | 30                 | 95                        | 30                         | 15                                  | 0.7                                  | 4000                                      | 260                                        |

| TS4GSSD25H-S | 95                | 60                 | 95                        | 55                         | 15                                  | 1.9                                  | 4000                                      | 510                                        |

| TS8GSSD25H-S | 95                | 85                 | 95                        | 80                         | 16                                  | 2.1                                  | 4000                                      | 470                                        |

Note: Maximum transfer speed recorded

\* 25 C, test on ASUS Z87-Pro , 4GB, Windows<sup>®</sup> 7 with AHCI mode, benchmark utility ATTO (version 2.41), unit MB/s

\*\* 25 C, test on ASUS Z87-Pro, 4GB, Windows<sup>®</sup> 7 with AHCI mode, benchmark utility CrystalDiskMark (version 3.0), copied file 1000MB, unit MB/s \*\*\* Random read/write performance based on IOmeter2008 with 4K file size and queue depth of 32, unit IOPs

\*\*\*\* The recorded performance is obtained while the SSD is not operating as an OS disk

### TS2GSSD25H-S TS8GSSD25H-S

| Actual Capacity |            |  |  |

|-----------------|------------|--|--|

| Model P/N       | LBA        |  |  |

| TS1GSSD25H-S    | 1,974,672  |  |  |

| TS2GSSD25H-S    | 3,928,176  |  |  |

| TS4GSSD25H-S    | 7,835,184  |  |  |

| TS8GSSD25H-S    | 15,649,200 |  |  |

| Power Consumption       |        |              |  |  |

|-------------------------|--------|--------------|--|--|

| Input Voltage           |        | 5V ± 5%      |  |  |

| Model P/N / Power Consu | mption | Typical (mA) |  |  |

|                         | Read   | 80           |  |  |

| TS1GSSD25H-S            | Write  | 79           |  |  |

|                         | Idle   | 68           |  |  |

|                         | Read   | 105          |  |  |

| TS2GSSD25H-S            | Write  | 106          |  |  |

|                         | Idle   | 69           |  |  |

|                         | Read   | 115          |  |  |

| TS4GSSD25H-S            | Write  | 146          |  |  |

|                         | Idle   | 70           |  |  |

|                         | Read   | 119          |  |  |

| TS8GSSD25H-S            | Write  | 184          |  |  |

|                         | Idle   | 72           |  |  |

\*Tested with IOmeter running sequential reads/writes and idle mode

| Reliability                   |              |                                     |  |  |

|-------------------------------|--------------|-------------------------------------|--|--|

| Data Reliability              | Supports BC  | Supports BCH ECC 1 bit per 528-byte |  |  |

| Data Retention                | 10 years     | 10 years                            |  |  |

| MTBF                          | 1,000,000 ho | 1,000,000 hours                     |  |  |

|                               | 1GB          | 30 TBW                              |  |  |

| Endurance (Terabytes Written) | 2GB          | 65 TBW                              |  |  |

|                               | 4GB          | 120 TBW                             |  |  |

|                               | 8GB          | 215 TBW                             |  |  |

## TS2GSSD25H-S TS8GSSD25H-S

| Vibration     |                 |

|---------------|-----------------|

| Operating     | 3.0G, 5 - 800Hz |

| Non-Operating | 5.0G, 5 - 800Hz |

\* Reference to IEC 60068-2-6 Testing procedures; Operating-Sine wave, 5-800Hz/1 oct., 1.5mm, 3g, 0.5 hr./axis, total 1.5 hrs.

| Shock                                                                                                                   |              |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------|--|

| Operating                                                                                                               | 1500G, 0.5ms |  |

| Non-Operating                                                                                                           | 1500G, 0.5ms |  |

| * Reference to IEC 60068-2-27 Testing procedures; Operating-Half-sine wave, 1500g, 0.5ms, 3 times/dir., total 18 times. |              |  |

| Regulations |                  |

|-------------|------------------|

| Compliance  | CE, FCC and BSMI |

### Reliability

#### Global Wear Leveling – Advanced algorithm to enhance the Wear-Leveling Efficiency

There are 3 main processes in global wear leveling approaches:

- (1) Record the block erase count and save in the wear-leveling table.

- (2) Find the static-block and save it in wear-leveling pointer.

- (3) Check the erase count when the block popped from spare pool. If the block erase count is bigger than WEARCNT, then swapped the static-block and over-count-block. After actual test, global wear leveling successfully even the erase count of every block; hence, it can extend the life expectancy of Flash product.

#### **Bad-block management**

When the flash encounters ECC failed, program fail or erase fail, the controller will mark the block as bad block to prevent the used of this block and caused data lost later on.

### **Power Shield**

The controller uses intelligent internal power shield logic to prevent data loss when sudden power off or power failure.

### **Package Dimensions**

Below figure illustrates the Transcend Half-Slim Solid State Disk. All dimensions are in mm.

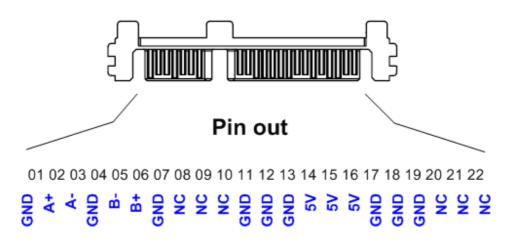

### **Pin Assignments**

| Pin No. | Pin Name | Pin No. | Pin Name |

|---------|----------|---------|----------|

| 01      | GND      | 02      | A+       |

| 03      | A-       | 04      | GND      |

| 05      | B-       | 06      | B+       |

| 07      | GND      | 08      | NC       |

| 09      | NC       | 10      | NC       |

| 11      | GND      | 12      | GND      |

| 13      | GND      | 14      | 5V       |

| 15      | 5V       | 16      | 5V       |

| 17      | GND      | 18      | GND      |

| 19      | GND      | 20      | NC       |

| 21      | NC       | 22      | NC       |

### **Pin Layout**

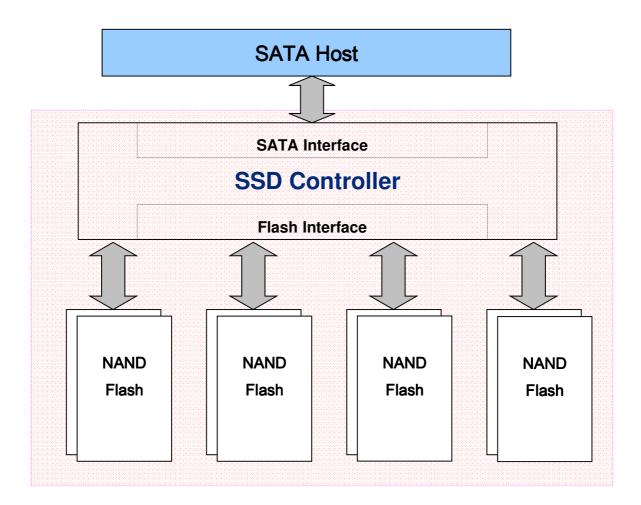

### **Block Diagram**

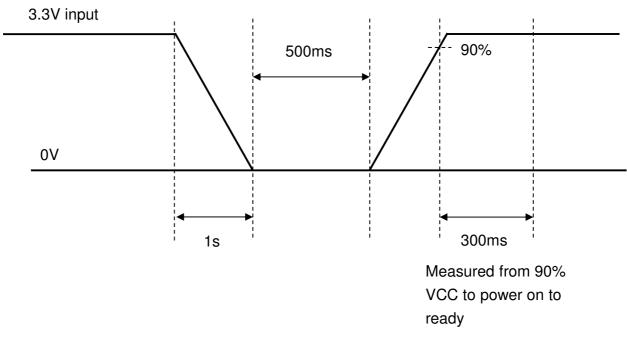

### **Power Sequence**

Below figure illustrates the Transcend Half-Slim SSD power sequence.

- 1. Shut down the input power.

- 2. Power on reset pull low.

- 3. Wait for the drive to static state.

- 4. Turn on the input power.

- 5. Power on to ready pull high.

\*The actual value may vary depend on device capacity and system environment.

8

### ATA command register

This table with the following paragraphs summarizes the ATA command set.

| Support ATA/ATAPI Command        | Code       | Protocol          |

|----------------------------------|------------|-------------------|

| General Feature Set              |            |                   |

| EXECUTE DIAGNOSTICS              | 90h        | Device diagnostic |

| FLUSH CACHE                      | E7h        | Non-data          |

| IDENTIFY DEVICE                  | ECh        | PIO data-In       |

| READ DMA                         | C8h        | DMA               |

| READ MULTIPLE                    | C4h        | PIO data-In       |

| READ SECTOR(S)                   | 20h        | PIO data-In       |

| READ VERIFY SECTOR(S)            | 40h or 41h | Non-data          |

| SET FEATURES                     | EFh        | Non-data          |

| SET MULTIPLE MODE                | C6h        | Non-data          |

| WRITE DMA                        | CAh        | DMA               |

| WRITE MULTIPLE                   | C5h        | PIO data-out      |

| WRITE SECTOR(S)                  | 30h        | PIO data-out      |

| NOP                              | 00h        | Non-data          |

| READ BUFFER                      | E4h        | PIO data-In       |

| WRITE BUFFER                     | E8h        | PIO data-out      |

| Power Management Feature Set     |            |                   |

| CHECK POWER MODE                 | E5h or 98h | Non-data          |

| IDLE                             | E3h or 97h | Non-data          |

| IDLE IMMEDIATE                   | E1h or 95h | Non-data          |

| SLEEP                            | E6h or 99h | Non-data          |

| STANDBY                          | E2h or 96h | Non-data          |

| STANDBY IMMEDIATE                | E0h or 94h | Non-data          |

| Security Mode Feature Set        |            |                   |

| SECURITY SET PASSWORD            | F1h        | PIO data-out      |

| SECURITY UNLOCK                  | F2h        | PIO data-out      |

| SECURITY ERASE PREPARE           | F3h        | Non-data          |

| SECURITY ERASE UNIT              | F4h        | PIO data-out      |

| SECURITY FREEZE LOCK             | F5h        | Non-data          |

| SECURITY DISABLE PASSWORD        | F6h        | PIO data-out      |

| SMART Feature Set                |            |                   |

| SMART Disable Operations         | B0h        | Non-data          |

| SMART Enable/Disable Autosave    | B0h        | Non-data          |

| SMART Enable Operations          | B0h        | Non-data          |

| SMART Return Status              | B0h        | Non-data          |

| SMART Execute Off-Line Immediate | B0h        | Non-data          |

| SMART Read Data                  | B0h        | PIO data-In       |

| Host Protected Area Feature Set  |            |                   |

| Read Native Max Address          | F8h        | Non-data          |

| Set Max Address                  | F9h        | Non-data          |

| Set Max Set Password             | F9h        | PIO data-out      |

| Set Max Lock                     | F9h        | Non-data          |

| Set Max Freeze Lock              | F9h        | Non-data          |

| Set Max Unlock              | F9h | PIO data-out |  |  |  |  |  |

|-----------------------------|-----|--------------|--|--|--|--|--|

| 48-bit Address Feature Set  |     |              |  |  |  |  |  |

| Flush Cache Ext             | EAh | Non-data     |  |  |  |  |  |

| Read Sector(s) EXt          | 24h | PIO data-In  |  |  |  |  |  |

| Read DMA Ext                | 25h | DMA          |  |  |  |  |  |

| Read Multiple Ext           | 29h | PIO data-In  |  |  |  |  |  |

| Read Native Max Address Ext | 27h | Non-data     |  |  |  |  |  |

| Read Verify Sector(s) Ext   | 42h | Non-data     |  |  |  |  |  |

| Set Max Address Ext         | 37h | Non-data     |  |  |  |  |  |

| Write DMA Ext               | 35h | DMA          |  |  |  |  |  |

| Write DMA FUA Ext           | 3Dh | DMA          |  |  |  |  |  |

| Write Multiple Ext          | 39h | PIO data-out |  |  |  |  |  |

| Write Multiple FUA Ext      | CEh | PIO data-out |  |  |  |  |  |

| Write Sector(s) Ext         | 34h | PIO data-out |  |  |  |  |  |

### ATA Command Specifications

#### FLUSH CACHE (E7h)

This command is used by the host to request the device to flush the write cache. If there is data in the write cache, that data shall be written to the media. The BSY bit shall remain set to one until all data has been successfully written or an error occurs.

#### IDENTIFY DEVICE (ECh)

This commands read out 512Bytes of drive parameter information. Parameter Information consists of the arrangement and value as shown in the following table. This command enables the host to receive the Identify Drive Information from the device.

#### READ DMA (C8h)

Read data from sectors during Ultra DMA and Multiword DMA transfer. Use the SET FEATURES command to specify the mode value. A sector count of zero requests 256 sectors.

#### READ MULTIPLE (C4h)

This command performs similarly to the Read Sectors command. Interrupts are not generated on each sector, but on the transfer of a block which contains the number of sectors defined by a Set Multiple command.

#### READ SECTOR(S) (20h)

This command reads 1 to 256 sectors as specified in the Sector Count register from sectors which is set by Sector number register. A sector count of 0 requests 256 sectors. The transfer beings specified in the Sector Number register.

#### READ VERIFY SECTOR(S) (40h/41h)

This command verifies one or more sectors on the drive by transferring data from the flash media to the data buffer in the drive and verifying that the ECC is correct. This command is identical to the Read Sectors command, except that DRQ is never set and no data is transferred to the host.

#### SET FEATURES (EFh)

This command set parameter to Features register and set drive's operation. For transfer mode, parameter is set to Sector Count register. This command is used by the host to establish or select certain features.

#### SET MULTIPLE MODE (C6h)

This command enables the device to perform READ MULTIPLE and WRITE MULTIPLE operations and establishes the block count for these commands.

#### WRITE DMA (CAh)

Write data to sectors during Ultra DMA and Multiword DMA transfer. Use the SET FEATURES command to specify the mode value.

#### WRITE MULTIPLE (C5h)

This command is similar to the Write Sectors command. Interrupts are not presented on each sector, but on the transfer of a block which contains the number of sectors defined by Set Multiple command.

#### WRITE SECTOR(S) (30h)

Write data to a specified number of sectors (1 to 256, as specified with the Sector Count register) from the specified address. Specify "00h" to write 256 sectors.

### NOP (00h)

The device shall respond with command aborted. For devices implementing the Overlapped feature set, subcommand code 00h in the Features register shall abort any outstanding queue. Subcommand codes 01h through FFh in the Features register shall not affect the status of any outstanding queue.

#### READ BUFFER (E4h)

The READ BUFFER command enables the host to read a 512-byte block of data.

#### WRITE BUFFER (E8h)

This command enables the host to write the contents of one 512-byte block of data to the device's buffer.

### **Power Management Feature Set**

#### CHECK POWER MODE (E5h or 98h)

The host can use this command to determine the current power management mode.

#### IDLE (E3h or 97h)

This command causes the device to set BSY, enter the Idle mode, clear BSY and generate an interrupt. If sector count is non-zero, the automatic power down mode is enabled. If the sector count is zero, the automatic power mode is disabled.

#### IDLE IMMEDIATE (E1h or 95h)

This command causes the device to set BSY, enter the Idle(Read) mode, clear BSY and generate an interrupt.

#### SLEEP (E6h or 99h)

This command causes the device to set BSY, enter the Sleep mode, clear BSY and generate an interrupt.

#### STANDBY (E2h or 96h)

This command causes the device to set BSY, enter the Sleep mode (which corresponds to the ATA "Standby" Mode), clear BSY and return the interrupt immediately.

#### STANDBY IMMEDIATE (E0h or 94h)

This command causes the drive to set BSY, enter the Sleep mode (which corresponds to the ATA "Standby" Mode), clear BSY and return the interrupt immediately.

### Security Mode Feature Set

#### SECURITY SET PASSWORD (F1h)

This command set user password or master password. The host outputs sector data with PIO data-out protocol to indicate the information defined in the following table.

#### Security set Password data content1

| Word   | Content             |                |                       |  |  |  |

|--------|---------------------|----------------|-----------------------|--|--|--|

| 0      | Control word        |                |                       |  |  |  |

|        | Bit 0               | Identifier     | 0=set user password   |  |  |  |

|        |                     |                | 1=set master password |  |  |  |

|        | Bits 1-7            | Reserved       |                       |  |  |  |

|        | Bit 8               | Security level | 0=High                |  |  |  |

|        |                     |                | 1=Maximum             |  |  |  |

|        | Bits 9-15           | Reserved       |                       |  |  |  |

| 1-16   | Password (32 bytes) |                |                       |  |  |  |

| 17-255 | Reserved            |                |                       |  |  |  |

#### SECURITY UNLOCK (F2h)

This command disables LOCKED MODE of the device. This command transfers 512 bytes of data from the host with PIO data-out protocol. The following table defines the content of this information

### Security Unlock information2

| Word   | Content             |            |                           |  |  |  |

|--------|---------------------|------------|---------------------------|--|--|--|

| 0      | Control word        |            |                           |  |  |  |

|        | Bit 0               | Identifier | 0=compare user password   |  |  |  |

|        |                     |            | 1=compare master password |  |  |  |

|        | Bits 1-15           | Reserved   |                           |  |  |  |

| 1-16   | Password (32 bytes) |            |                           |  |  |  |

| 17-255 | Reserved            |            |                           |  |  |  |

#### SECURITY DISABLE PASSWORD (F6h)

Disables any previously set user password and cancels the lock. The host transfers 512 bytes of data, as shown in the following table, to the drive. The transferred data contains a user or master password, which the drive compares with the saved password. If they match, the drive cancels the lock. The master password is still saved. It is re-enabled by issuing the SECURITY SET PASSWORD command to re-set a user password.

#### SECURITY ERASE PREPARE (F3h)

This command shall be issued immediately before the Security Erase Unit command to enable erasing and unlocking. This command prevents accidental loss of data on the drive.

#### SECURITY ERASE UNIT (F4h)

The host uses this command to transfer 512 bytes of data, as shown in the following table, to the drive. The transferred data contains a user or master password, which the drive compares with the saved password. If they match, the drive deletes user data, disables the user password, and cancels the lock. The master password is still saved. It is re-enabled by issuing the SECURITY SET PASSWORD command to re-set a user password.

#### SECURITY FREEZE LOCK (F5h)

Causes the drive to enter Frozen mode. Once this command has been executed, the following commands to update a lock result in the Aborted Command error:

- SECURITY SET PASSWORD

- SECURITY UNLOCK

- SECURITY DISABLE PASSWORD

- SECURITY ERASE PREPARE

- SECURITY ERASE UNIT

The drive exits from Frozen mode upon a power-off or hard reset. If the SECURITY FREEZE LOCK command is issued when the drive is placed in Frozen mode, the drive executes the command, staying in Frozen mode.

# TS2GSSD25H-S TS8GSSD25H-S

| Word<br>Address | Default<br>Value | Total<br>Bytes | Data Field Type Information                                                                 |  |

|-----------------|------------------|----------------|---------------------------------------------------------------------------------------------|--|

| 0               | 044Ah            | 2              | General configuration                                                                       |  |

| 1               | XXXXh            | 2              | Default number of cylinders                                                                 |  |

| 2               | 0000h            | 2              | Reserved                                                                                    |  |

| 3               | 00XXh            | 2              | Default number of heads                                                                     |  |

| 4               | 0000h            | 2              | Obsolete                                                                                    |  |

| 5               | 0240h            | 2              | Obsolete                                                                                    |  |

| 6               | XXXXh            | 2              | Default number of sectors per track                                                         |  |

| 7-8             | XXXXh            | 4              | Number of sectors per card (Word 7 = MSW, Word 8 = LSW)                                     |  |

| 9               | 0000h            | 2              | Obsolete                                                                                    |  |

| 10-19           | XXXXh            | 20             | Serial number in ASCII (Right Justified)                                                    |  |

| 20              | 0002h            | 2              | Obsolete                                                                                    |  |

| 21              | 0002h            | 2              | Obsolete                                                                                    |  |

| 22              | 0004h            | 2              | Obsolete                                                                                    |  |

| 23-26           | XXXXh            | 8              | Firmware revision in ASCII. Big Endian Byte Order in Word                                   |  |

| 27-46           | XXXXh            | 40             | Model number in ASCII (Left Justified) Big Endian Byte Order in Word                        |  |

| 47              | 8001h            | 2              | Maximum number of sectors on Read/Write Multiple command                                    |  |

| 48              | 0000h            | 2              | Reserved                                                                                    |  |

| 49              | 0F00h            | 2              | Capabilities                                                                                |  |

| 50              | 4000h            | 2              | Capabilities                                                                                |  |

| 51              | 0200h            | 2              | PIO data transfer cycle timing mode                                                         |  |

| 52              | 0000h            | 2              | Obsolete                                                                                    |  |

| 53              | 0007h            | 2              | Field Validity                                                                              |  |

| 54              | XXXXh            | 2              | Current numbers of cylinders                                                                |  |

| 55              | 00XXh            | 2              | Current numbers of heads                                                                    |  |

| 56              | XXXXh            | 2              | Current sectors per track                                                                   |  |

| 57-58           | XXXXh            | 4              | Current capacity in sectors (LBAs)(Word 57 = LSW, Word 58 = MSW)                            |  |

| 59              | 01XXh            | 2              | Multiple sector setting                                                                     |  |

| 60-61           | XXXXh            | 4              | Total number of sectors addressable in LBA Mode                                             |  |

| 62              | 0000h            | 2              | Reserved                                                                                    |  |

| 63              | 0007h            | 2              | Multiword DMA transfer. Supports MDMA Mode 0,1,and 2                                        |  |

| 64              | 0003h            | 2              | Advanced PIO modes supported                                                                |  |

| 65              | 0078h            | 2              | Minimum Multiword DMA transfer cycle time per word. In PC Card modes this value shall be 0h |  |

| 66              | 0078h            | 2              | Recommended Multiword DMA transfer cycle time. In PC Card modes this value shall be 0h      |  |

| 67              | 0078h            | 2              | Minimum PIO transfer cycle time without flow control                                        |  |

# TS2GSSD25H-S TS8GSSD25H-S

Solid State Disk

| Word<br>Address | Default<br>Value | Total<br>Bytes | Data Field Type Information                                                     |  |

|-----------------|------------------|----------------|---------------------------------------------------------------------------------|--|

| 68              | 0078h            | 2              | Minimum PIO transfer cycle time with IORDY flow control                         |  |

| 69-74           | 0000h            | 12             | Reserved                                                                        |  |

| 75              | 0000h            | 2              | Queue depth                                                                     |  |

| 76              | 0006h            | 2              | Serial ATA capacities<br>· Support Serial ATA Gen1<br>· Support Serial ATA Gen2 |  |

| 77              | 0000h            | 2              | Reserved                                                                        |  |

| 78              | 0008h            | 2              | Device supports initiating interface power management                           |  |

| 79              | 0000h            | 2              | Reserved                                                                        |  |

| 80              | 0080h            | 2              | Major version number (ATA8-ACS)                                                 |  |

| 81              | 0000h            | 2              | Minor version number                                                            |  |

| 82              | 742Bh            | 2              | Command sets supported 0                                                        |  |

| 83              | 5500h            | 2              | Command sets supported 1                                                        |  |

| 84              | 4002h            | 2              | Command sets supported 2                                                        |  |

| 85-87           | XXXXh            | 6              | Features/command sets enabled                                                   |  |

| 88              | 407Fh            | 2              | Ultra DMA Mode Supported and Selected                                           |  |

| 89              | 0003h            | 2              | Time required for Security erase unit completion                                |  |

| 90              | 0000h            | 2              | Time required for Enhanced security erase unit completion                       |  |

| 91              | 0000h            | 2              | Current Advanced power management value                                         |  |

| 92              | FFFEh            | 2              | Master Password Revision Code                                                   |  |

| 93-127          | 0000h            | 70             | Reserved                                                                        |  |

| 128             | 0001h            | 2              | Security status                                                                 |  |

| 129-159         | 0000h            | 64             | Vendor unique bytes                                                             |  |

| 160             | 0000h            | 2              | Power requirement description                                                   |  |

| 161             | 0000h            | 2              | Reserved                                                                        |  |

| 162             | 0000h            | 2              | Key management schemes supported                                                |  |

| 163             | 0000h            | 2              | CF Advanced True IDE Timing Mode Capability and Setting                         |  |

| 164-216         | 0000h            | 106            | Reserved                                                                        |  |

| 217             | 0001h            | 2              | Non-rotating media (SSD)                                                        |  |

| 218-255         | 0000h            | 140            | Reserved                                                                        |  |

### SMART Command Support

| Value | Command                    | Value | Command                  |

|-------|----------------------------|-------|--------------------------|

| D0h   | Read Data                  | D5h   | Reserved                 |

| D1h   | Read Attribute Threshold   | D6h   | Reserved                 |

| D2h   | Enable/Disable Autosave    | D8h   | Enable SMART Operations  |

| D3h   | Save Attribute Values      | D9h   | Disable SMART Operations |

| D4h   | Execute OFF-Line Immediate | DAh   | Return Status            |

If the reserved size is below a threshold, status can be read from the Cylinder Register using the Return Status command (DAh).

### **SMART DATA Structure**

| ВҮТЕ    | F / V | Description                                                                    |

|---------|-------|--------------------------------------------------------------------------------|

| 0-1     | X     | Revision code                                                                  |

| 2-361   | X     | Vendor specific                                                                |

| 362     | V     | Off-line data collection status                                                |

| 363     | X     | Self-test execution status byte                                                |

| 364-365 | V     | Total time in seconds to complete off-line data collection activity            |

| 366     | X     | Vendor specific                                                                |

| 367     | F     | Off-line data collection capability                                            |

| 368-369 | F     | SMART capability                                                               |

| 370     | F     | Error logging capability<br>7-1 Reserved<br>0 1=Device error logging supported |

| 371     | X     | Vendor specific                                                                |

| 372     | F     | Short self-test routine recommended polling time (in minutes)                  |

| 373     | F     | Extended self-test routine recommended polling time (in minutes)               |

| 374     | F     | Conveyance self-test routine recommended polling time (in minutes)             |

| 375-385 | R     | Reserved                                                                       |

| 386-395 | F     | Firmware Version/Date Code                                                     |

| 396-397 | F     | Reserved                                                                       |

| 398-399 | F     | Reserved                                                                       |

| 400-406 | F     | 'SMI2244LT'                                                                    |

# TS2GSSD25H-S TS8GSSD25H-S

Solid State Disk

407-415 Х Vendor specific F 416 Reserved 417 F Program/write the strong page only 418-419 V Number of spare block 420-423 V Average Erase Count 424-510 Х Vendor specific V 511 Data structure checksum F=the content of the byte is fixed and does not change. V=the content of the byte is variable and may change depending on the state of the device or the commands executed by the device. X=the content of the byte is vendor specific and may be fixed or variable. R=the content of the byte is reserved and shall be zero. \* 4 Byte value : [MSB] [2] [1] [LSB]

# TS2GSSD25H-S TS8GSSD25H-S

| Attribute ID<br>(hex) | Raw Attribute Value |     |    | Attribute Name |    |    |                                             |  |

|-----------------------|---------------------|-----|----|----------------|----|----|---------------------------------------------|--|

| 01                    | MSB                 | 00  | 00 | 00             | 00 | 00 | Read Error Rate                             |  |

| 05                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Reallocated sectors count                   |  |

| 09                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Reserved                                    |  |

| 0C                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Power Cycle Count                           |  |

| A0                    | LSB                 |     |    | MSB            | 00 | 00 | Uncorrectable sectors count when read/write |  |

| A1                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Number of valid spare blocks                |  |

| A2                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Number of Child pair                        |  |

| A3                    | LSB                 | MSB | 00 | 00             | 00 | 00 | Number of initial invalid blocks            |  |

| A4                    | LSB                 |     |    | MSB            | 00 | 00 | Total erase count                           |  |

| A5                    | LSB                 |     |    | MSB            | 00 | 00 | Maximum erase count                         |  |

| A6                    | LSB                 |     |    | MSB            | 00 | 00 | Minimum erase count                         |  |

| A7                    | LSB                 |     |    | MSB            | 00 | 00 | Average erase count                         |  |

| C0                    | LSB                 |     |    | MSB            | 00 | 00 | Power-off retract Count                     |  |

| C2                    | MSB                 | 00  | 00 | 00             | 00 | 00 | Controlled temperature                      |  |

| C3                    | LSB                 |     |    | MSB            | 00 | 00 | Hardware ECC recovered                      |  |

| C4                    | LSB                 |     |    | MSB            | 00 | 00 | Reallocation event count                    |  |

| C6                    | LSB                 |     |    | MSB            | 00 | 00 | Reserved                                    |  |

| C7                    | LSB                 | MSB | 00 | 00             | 00 | 00 | UltraDMA CRC Error Count                    |  |

| F1                    | LSB                 |     |    | MSB            | 00 | 00 | Total LBA written (each write unit = 32MB)  |  |

| F2                    | LSB                 |     |    | MSB            | 00 | 00 | Total LBA read (each read unit = 32MB)      |  |

### TS2GSSD25H-S TS8GSSD25H-S

### **Ordering Information**

The above technical information is based on industry standard data and has been tested to be reliable. However, Transcend makes no warranty, either expressed or implied, as to its accuracy and assumes no liability in connection with the use of this product. Transcend reserves the right to make changes to the specifications at any time without prior notice.

Beijing: E-mail: sales-cn@transcendchina.com Shenzhen: E-mail:sales-cn@transcendchina.com http://cn.transcend-info.com GERMANY E-mail:vertrieb-de@transcend-info.com http://de.transcend-info.com HONG KONG E-mail: sales-hk@transcend-info.com http://hk.transcend-info.com JAPAN E-mail: sales-jp@transcend-info.com http://jp.transcend-info.com THE NETHERLANDS E-mail: sales-nl@transcend-info.com http://nl.transcend-info.com **United Kingdom** E-mail: sales-uk@transcend-info.com

E-mail: sales-kr@transcend-info.com http://kr.transcend-info.com

| Revision History |            |                                                                                       |                |  |  |  |

|------------------|------------|---------------------------------------------------------------------------------------|----------------|--|--|--|

| Version          | Date       | Modification Content                                                                  | Modified Page  |  |  |  |

| V2.0             | 2014/06/06 | Initial release                                                                       |                |  |  |  |

| V2.1             | 2015/06/04 | 1.Change SMART DATA structure byte400-406 to<br>'SMI2244LT'<br>2.Add SMART attributes | P17<br>P18~P19 |  |  |  |

| V2.2             | 2015/06/10 | 1.Update ID table/SMART table<br>2.Modify ECC bits                                    | P4~P19         |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |

|                  |            |                                                                                       |                |  |  |  |