Issue 50

## XCEI journal

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

### PARTNERSHIP —

20 Years of Partnership Author! Author! Programmable World 2004

### SOFTWARE

Algorithmic C Synthesis

The Need for Speed

### MANUFACTURING

Lower PCB Mfg. Costs

Optimize PCB Routability

**COVER STORY** FPGAs on Mars

XILINX®

## OHS ERCAS

## The New SPARTAN-3 Make It Your ASIC

### The world's lowest-cost FPGAs

Spartan-3 Platform FPGAs deliver everything you need at the price you want. Leading the way in 90nm process technology, the new Spartan-3 devices are driving down costs in a huge range of high-capability, cost-sensitive applications. With the industry's widest density range in its class — 50K to 5 Million gates — the Spartan-3 family gives you unbeatable value and flexibility.

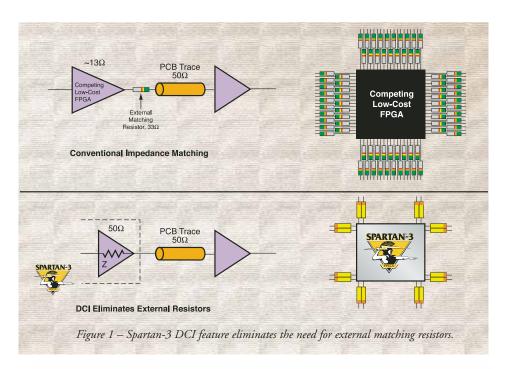

### Lots of features ... without compromising on price

Check it out. You get 18x18 embedded multipliers for XtremeDSP<sup>™</sup> processing in a low-cost FPGA. Our unique staggered pad technology delivers a ton of I/Os for total connectivity solutions. Plus our XCITE technology improves signal integrity, while eliminating hundreds of resistors to simplify board layout and reduce your bill of materials.

With the lowest cost per I/O and lowest cost per logic cell, Spartan-3 Platform FPGAs are the perfect fit for any design ... and any budget.

### **→ MAKE IT YOUR ASIC**

For more information visit www.xilinx.com/spartan3

Easiest to use

## Thank You for Making Xilinx Number One

Carlis Collins editor@xilinx.com 408-879-4519

MANAGING EDITOR Forrest Couch forrest.couch@xilinx.com 408-879-5770

EDITOR IN CHIEF

ASSISTANT MANAGING EDITOR Charmaine Cooper Hussain

XCELL ONLINE EDITOR Tom Pyles

tom.pyles@xilinx.com 720-652-3883

ADVERTISING SALES Dan Teie

1-800-493-5551

ART DIRECTOR Scott Blair

Xcelljournal

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

Phone: 408-559-7778

FAX: 408-879-4780

©2004 Xilinx, Inc.

All rights reserved

The Xcell Journal is published quarterly, XILINX, the XilinX logo. CoolRunner, RocketChips, Rocket IP, Spartan, SurteBENCH, StateCAD, Virtex, Virtex-II, and XACT are registered trademarks of Xilinx, Inc. ACE Controller, ACE Flesh, Alliannes Series, Alliannes CORE, Bencher, ChipScope. Configuration Logic Cell, CORE Generator, CoreLINX, Delock, EZOg., Fast CLK, Fast CONNECT, Foundation, Gigabit Speeds... and Beyond!, HardWire, HDL Bencher, IRL, J Drive, Jbits, LCA, LogiBLOX, Logic Cell, Logic Professor, MicroBlaze, MircoVia, MultiLINX, NanoBlaze, FivoBlaze, PLUSASM, PowerGuride, PowerMarze, OPro, Real-PCI, RocketlO, RocketPHY, SelectIO, SelectRAM, Select

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xlim makes no warranties, express; implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim it might have against

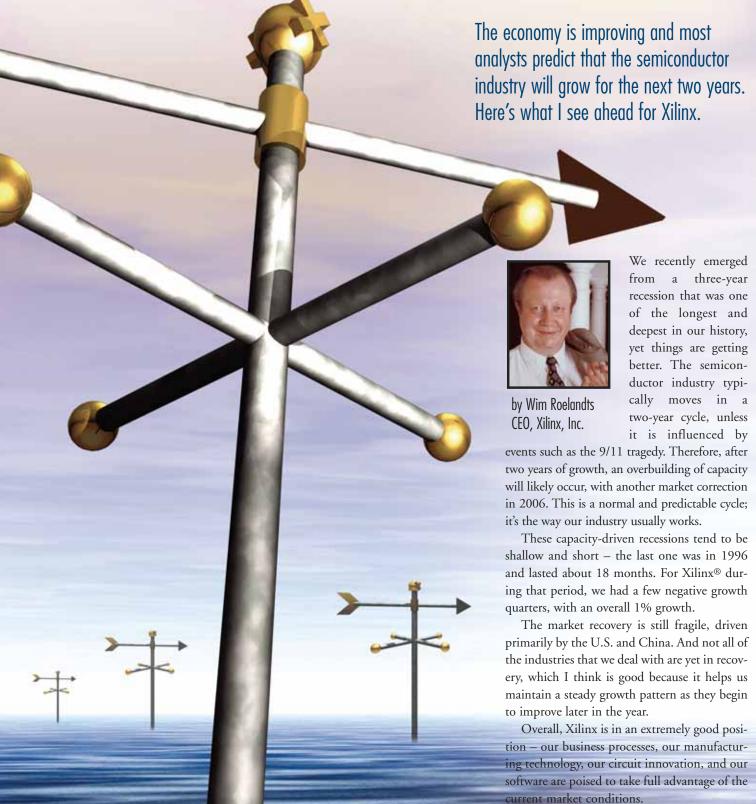

Ever have one of those days where you're working hard, nose to the grindstone, striving to make sure your latest project is on time and on target; and then suddenly out of nowhere, you overhear someone complimenting your efforts? It's not a comment that you solicited, but independently you find out that all of your hard work is recognized as the best among your peers and you're headed in the right direction.

CMP Media LLC, the parent company of *EETimes*, just dropped quite a few kudos on the Xilinx doorstep. Most of you know that every year CMP conducts a PCB and IC electronic design tool industry survey to sample the engineering community's view on design tool providers. This year, at the 2004 Design Automation Conference, CMP announced the results of their first FPGA vendor survey.

The ratings are striking. In 21 out of 22 categories measuring everything from best pre-sales support to brand and tool awareness, from most ethical company to customer loyalty, FPGA designers chose Xilinx as the top FPGA vendor. We received the highest rankings in best after-sales support, best documentation, current technology leader, technology leader in three years, clear vision of the future, best integration with other vendors' tools, well-managed company, and more.

We were also able to hear the industry concerns. Respondents cited the accuracy and integrity of FPGA tools as their biggest design issue, followed closely by functional verification, timing closure, and the ability of those tools to easily handle complex designs. They also said that the majority of their design time was spent in place and route, synthesis, and HDL simulation, followed by timing analysis and floorplanning. One-third of the respondents also use formal verification, while almost half regularly use signal integrity and C language system-level tools.

On behalf of all of the employees at Xilinx, thank you. We hear you loud and clear. Our primary goal is to put a programmable device in every piece of electronic equipment over the next 10 years. It's nice to hear that we're on the right path to get there.

Forest Couch

Forrest Couch Managing Editor

COVER STORY

### FPGAs on Mars

Xilinx FPGAs have transitioned from a flight ASIC prototyping platform to playing integral roles in the Mars Exploration Rover Mission.

8

### Streaming Data at 10 Gbps

Using a Virtex-II FPGA to stream data from DDR-SDRAM to OC-192 serializers.

13

### Celebrating 20 Years of Partnership

Turning an industry cliché into a successful business model.

21

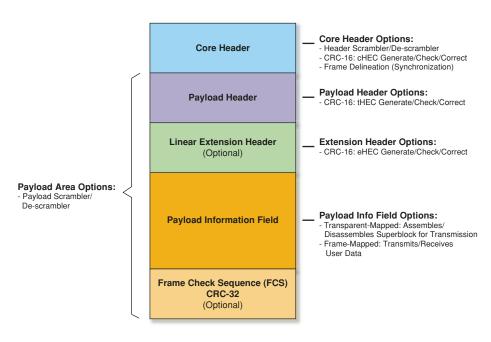

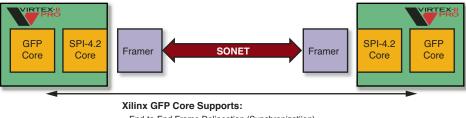

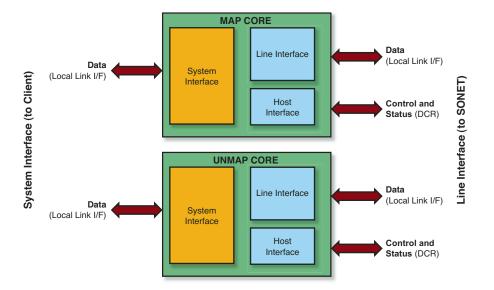

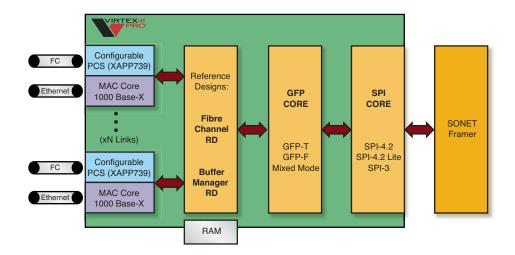

### Next-Generation Data Transport over Metro Area Networks

The Xilinx GFP core enables efficient transport of LAN/SAN over SONET-based networks.

### Xcelljournal

| View from the Top                          | 5   |

|--------------------------------------------|-----|

| FPGAs on Mars                              | 8   |

| Streaming Data at 10 Gbps                  | .13 |

| Control Your QDR Designs                   | .16 |

| Celebrating 20 Years of Partnership        | .21 |

| Author! Author!                            | .25 |

| Experience Programmable World 2004         | .30 |

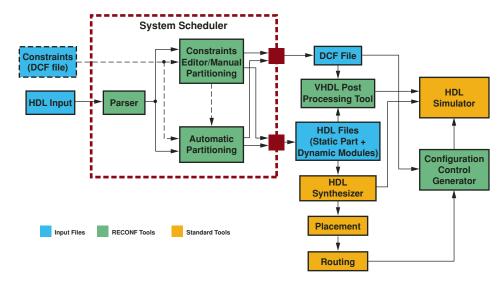

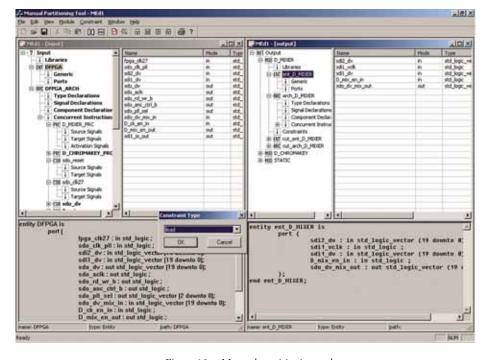

| Managing Partial Dynamic Reconfiguration   | .32 |

| Nucleus RTOS for Xilinx FPGAs              | .38 |

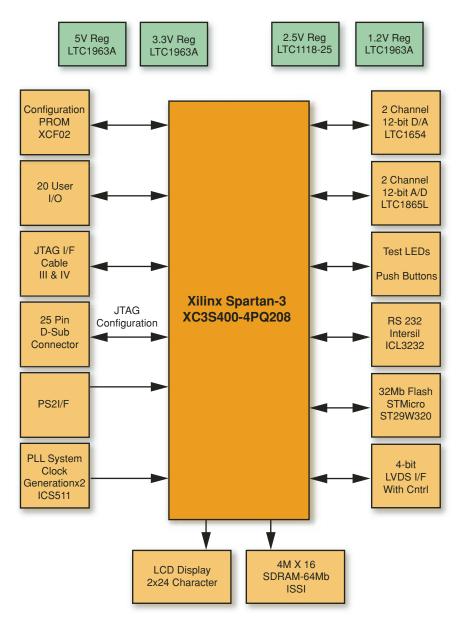

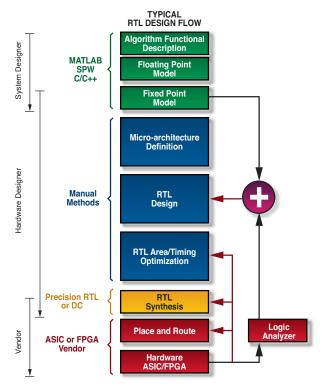

| Implement an Embedded System with FPGAs    | .43 |

| Algorithmic C Synthesis                    | .46 |

| Design Tool Performance Lowers Costs       | .52 |

| The Need for Speed                         | .54 |

| Lower Your PCB Manufacturing Costs         | .57 |

| Plan FPGA Signal Assignments               | .60 |

| Next-Generation Data Transport             | .64 |

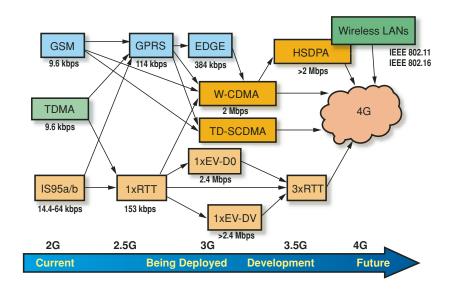

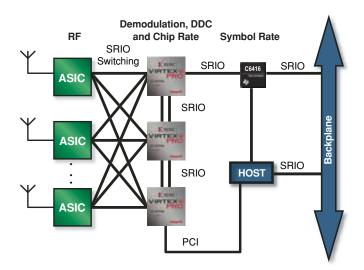

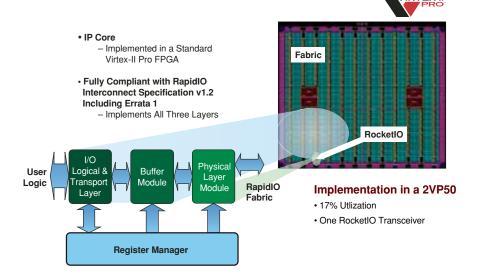

| Designing Next-Generation Wireless Systems | .68 |

| Meeting Interoperability Standards         | .70 |

| Xilinx Partner Yellow Pages                | .74 |

| Reference Pages                            | .82 |

To receive a free subscription to the printed *Xcell Journal*, or to view the Web-based *Xcell Online*, visit www.xilinx.com/xcell/.

Fall 2004

### The Growing Asian Markets

A significant and quickly growing segment of our business comes from the Japanese and Asia-Pacific markets – our business there is now more than three times higher than it was just four years ago. This comes both from systems that are designed and manufactured there as well as from manufacturing outsourced from other countries. Plus, Japanese business is starting to expand and is beginning to help drive the world economy forward.

I believe our business in Asia will continue to grow over the years to come. We see a big shift taking place, driven primarily by the next big trend in our industry – digital consumer electronics. The core of this business will be in Asia, and we are putting a lot of our resources there to help meet the demand. We recently began staffing a facility in Singapore that will eventually house more than 200 employees.

### **Beating Moore's Law**

Semiconductor technology typically follows Moore's Law, which states that every two years the number of transistors that can be fabricated on a chip will double this law has held true for many years. As we approach finer and finer process geometries, moving from 130 nm to 90 nm and down to 65 nm, it becomes increasingly difficult to manufacture devices. Xilinx is leading the industry in the development and use of these advanced technologies, which means that we are often the first to solve difficult process problems - that's both the good and the bad news. We usually get to market first with the most advanced manufacturing processes, but we also put a lot of effort into getting it right.

We also have a strategy for significantly improving performance through innovative architectural designs – the best example is our new Virtex- $4^{TM}$  family. In fact,

Because cores allow us to provide a more complete solution, our customers have to do less work to produce more and better designs. And they want to buy cores from Xilinx because they want to have the assurance of ongoing long-term support. We are in fact increasing our investments in IP and cores to meet the increasing demand. We already have many more cores than our competitors, and thus we are very well positioned to take advantage of these trends.

### Xilinx Strategy for the Future

Here are some of the long-term objectives that define our strategy for the next five to 10 years.

### Setting the Standard

We will continue to set the standard for how to manage a high-tech company. I think we have already done a phenomenal

### Programmable logic is indeed taking over; it is becoming mainstream and finding new markets where it's never been used before.

### **Going Mainstream**

Eight years ago, when I joined Xilinx, I said that we will put a programmable chip in every system, and it's now becoming a reality. Our ability to shrink our products into smaller and smaller geometries at lower costs, coupled with the recession (which means that many of our customers can no longer afford the high costs of designing and building ASICs) is moving more and more of our customers to take full advantage of the many benefits of programmable logic.

Market forces, combined with our low-cost technology advances, are driving programmable logic into the mainstream – our devices are now used in all types of products and the trend continues to grow. Over the next two or three years, when these new designs go into production, our business will expand significantly. Programmable logic is indeed taking over; it is becoming mainstream and finding new markets where it's never been used before.

most of our performance improvements in the Virtex-4 family come from circuit enhancements. The Virtex-4 ASMBL architecture allows us to create devices that are optimized for specific applications, providing just the features and performance that are needed at the lowest possible cost. As you can see, our innovation is not just in CMOS technology – we are way ahead of our competition in both device manufacturing technology and architecture.

### Reducing Design Costs with IP

Our marketplace is changing rapidly, and our customers must operate differently today than they did four years ago. Their own customers are much more cost-conscious, and thus they are much more worried about return on investments. Our customers have fewer engineers because of the recession, so they demand more from us — it's one of the reasons why we are increasing our investments in IP and cores.

job – we're admired as a company that manages its people well, treats its people well, and at the same time is innovative and wins in the market. And of course, the core of our culture is innovation. We want to continue to bring new technologies, new circuitries, new innovative marketing programs, and new channels of distribution. This will continue to be the core of our strategy because it's what makes Xilinx excel in everything we do.

### Leading Manufacturing Technology

We will continue to reduce our manufacturing costs. We made a lot of progress in the last year and now we need to move on to the next step. My intention is to make sure that all of our organizations are focused on low-cost, high-volume capabilities. The consumer electronics and automotive industries require us to reduce costs and ramp production faster than ever before. We will continue to innovate with-

### For the next 10 years, we want to extend our brand and establish Xilinx as a global leader, recognized not only by the engineering community but also by the financial community.

in all of our organizations to achieve this ongoing objective. For programmable logic to achieve its full potential in mainstream electronics, we must become even more efficient and productive – and we will.

Yet, while we continue to develop more high-volume strategies and products, we will continue to lead the high-end, high-performance market that has traditionally been the core of our business. We are doing a phenomenal job with our Virtex product line, with 70% to 80% market share, and that will continue as well.

### Creating Partnerships

Partnerships are a key strategy that allow us to focus on what we do best while allowing other companies to provide the products and services they do best – we call it our Partner Ecosystem. We will continue to build strong partnerships not only with our suppliers but with our customers as well.

We want to engage our customers early in their design process so that we can provide the best possible service and support throughout their entire design and manufacturing cycle. This requires a broad range of services from a number of ecosystem partners, and that requires a well coordinated and comprehensive approach. We have been successful with our partnership program in the past and we intend to strengthen it by making it easier for our customer partners — and our technology partners — to work more closely together for the benefit of all.

### **Expanding Our Markets**

We are already the leader in programmable logic technology, and now it's time for us to become a leader in all programmable technology, including DSP and embedded processing. Our technology already provides significant advantages in these areas, and it's time for us to capitalize on these strengths. We want to be the champion of programmability because we

are the only company that can provide the advantages of programmable logic, high-performance DSP, and embedded processing all on one device.

We are the largest company in program-

mable logic, with 50% market segment share. However, the embedded processor market and the DSP markets also offer significant market opportunity.

### **Brand Recognition**

Xilinx is already well respected and recognized in our marketplace, and we will continue to build our brand worldwide. Our success in the first 10 years was based on two innovations: FPGAs and fabless manufacturing. When we started in 1985, neither of these ideas was credible. Only the Xilinx founders believed they

would work. Yet we made them possible and we made them credible.

Our second 10 years were based on two things: becoming the technology leader in our industry and establishing a unique

business culture that fosters innovation. In that we have also been very successful.

For the next 10 years, we want to extend our brand and establish Xilinx as a global leader, recognized not only by the engineering community but also by the financial community. We want to be recognized not only for our innovative culture but also for our financial stability, management depth, the global reach and diversity of our products, and by the brand name we create.

### Going Global

We will continue to expand globally and place our resources close to the markets they serve. If 20% of our business is in Asia, we will strive to place 20% of our resources there because we want to be close to our customers and understand their needs. That's why we opened up a new factory headquarters in Singapore

and a new design center in India. We want to have a presence in Asia just like we have in Europe and the United States.

### Conclusion

Innovation remains the core of Xilinx. I believe innovation is the only thing that matters because if you innovate, there is no competition. That's the reason why we have gained market share every single year in the last six years.

As you can see I'm very excited about our current situation, and I'm even more excited about our future.

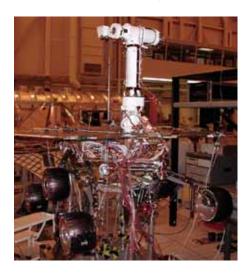

## FPGAS on Mars

Xilinx FPGAs have transitioned from a flight ASIC prototyping platform to playing integral roles in the Mars Exploration Rover Mission.

by David Ratter Field Applications Engineer Nu Horizons Electronics dratter@nuhorizons.com

Selecting the correct components for any engineering project can be a critical and difficult choice. This is clearly true for engineers at the Jet Propulsion Laboratory (JPL) when they must select components used on high-stakes flight projects, and especially important on high-profile missions like the Mars Exploration Rover Mission.

On Mars there are no tow trucks or auto clubs to call if something stops working. So how did Xilinx FPGAs go from performing a predominantly flight ASIC prototyping role to being designed into and flown in projects like the Mars lander and rovers? And what does the future hold for Xilinx and JPL space missions?

The needs of JPL's design engineers were the main driving force behind the paradigm shift from ASIC prototype to flight-qualified part, as were the Xilinx testing, processing, and manufacturing flows for its radiation-tolerant FPGAs. Engineering needs demand meeting mission requirements, both from a functional/performance viewpoint and a time-to-working-product viewpoint. Xilinx FPGAs provide inherent design advantages to meet those needs: high gate densities, rich on-board architectural features, large I/O counts with multiple I/O standards, and the ability to be reprogrammed at any time.

The second reason for the transition was JPL's qualification of Xilinx radiation-tolerant FPGAs into more and more flight situations.

The net results of these efforts can easily be seen on the Mars Exploration Rovers. Inside of each rover (named Discovery and Spirit), two Virtex TM XQVR1000s served as the main brains that controlled the motors. Four Xilinx XQR4062XL devices in the 4000XL family controlled the Mars lander pyrotechnics, crucial to the successful multi-phase descent and landing procedure. Also evident, although not as visible, are the increasing number of future flight missions that JPL engineers are designing with Xilinx radiation-tolerant FPGAs.

In this article, we'll briefly document the parts qualification and design steps, along with the past, present, and future of FPGA-based flight opportunities at JPL.

### **Flight Considerations**

There are three steps that must be accomplished before any part can be used in a flight application for JPL. The first is a general flight approval for a part. The second can be referred to as mission-specific approval. The third is additional design requirements for flight-based semiconductors.

### General Flight Approvals

JPL must give general flight approval before any part can be used for a flight application. This process requires that the manufacturer perform numerous additional processing, testing, and quality steps over and above the normal commercial processing steps.

JPL also meticulously examines device statistical and quality data that is constantly updated by the semiconductor manufacturers. They also examine additional parameters in this phase, including temperature considerations and packaging materials as well as semiconductor characteristics (for example, are there voids or contaminants that in zero gravity could migrate and cause failures?). Only after JPL engineers have conducted exhaustive research and analysis do they approve parts for flight use.

JPL Radiation Effects Group scientists work directly with Xilinx to unify and continually improve the testing, processing, and manufacturing steps used for Xilinx radiation-tolerant parts. This close customer/manufacturer relationship has resulted in a much superior radiation-tolerant product from Xilinx, and for JPL, a high-reliability manufacturing process gives them the utmost confidence.

### Specific Flight Approvals

Even after a part or parts has general flight approval, it still must receive mission-specific flight approval. Mission-specific approval is exactly what the term implies: JPL scientists and engineers review the mission-specific environments that the parts will encounter. This includes a detailed risk assessment.

JPL takes into account all aspects of the flight to predict what the part(s) will face during the mission's lifetime. Some of these parameters might include the number of temperature cycles, total ionizing dose, and predicted rate of radiation exposure. It is possible that parts with general flight approval will not get mission-specific flight approval.

### Specific Flight Design Considerations

Only after a part has met the above two criteria can it be used in a flight mission. The design process entails incorporating space-specific flight design requirements that include, but are not limited to, the following single-event phenomena:

- Single-event latch-up (SEL)

- Single-event upsets (SEU)

- Single-event transients (SET)

- Single-event functional interrupts (SEFIs)

In the case of Xilinx radiation-tolerant FPGAs, all single-event phenomena are taken into account either through the radiation-tolerant manufacturing and processing steps or through well-documented design practices:

- The epitaxial layer of Xilinx radiationtolerant FPGAs eliminates SELs.

- Triple-mode redundancy (commonly referred to as TMR) mitigates SEUs and SETs.

- "Scrubbing," or reprogramming the FGPA, takes care of SEFIs and the accumulation of SEUs.

Let's discuss the latter two design features in more detail.

In simple terms, a design with TMR requires three sets of key logic elements, with a voting structure that allows only the majority decision to propagate through the circuit. The theory is that statistically you are going to get an SEU over some time period. When this upset occurs, it will disrupt a single element (net, route, or bit). When this happens and the element it disrupts is being used, the other two "correct" elements will have the correct value; thus, the correct value will be passed out of the circuit. This is especially important in circuits that use feedback, such as counters and state machines.

9

Numerous approaches can be taken with respect to scrubbing, from simply reprogramming the FPGA to partial reconfiguration. The simplest method of scrubbing is to completely reprogram the FPGA at some periodic rate (typically 1/10 the calculated upset rate).

For example, if an SEU will occur once every 10 days, then you would reprogram the FPGA every day. However, when you reprogram the FPGA it is not operational during that reprogram time (on the order of micro to milliseconds). For situations that cannot tolerate that type of interruption, partial reconfiguration is available. This technique allows the FPGA to be reprogrammed while still operational.

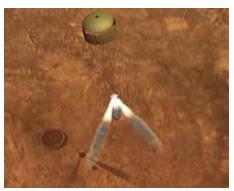

### The Past

Although the both the Discovery and Spirit rovers are still on the surface of Mars and active, they were launched in June and July 2003 and landed on Mars in January 2004. This means, obviously, that the engineering was completed in the past.

As stated earlier, the Mars Exploration Rovers used XQVR1000 devices and the lander used XQR4062XLs. The XQR4062XLs were used during the descent and landing of the rovers on the surface of Mars, while the XQVR1000s were used to control all of the brushed DC and stepper motors for the wheels, steering, antennas, camera, and other instruments on the rovers themselves.

Both the XQR4062XL and XQVR1000 designs used TMR for SEU and SET mitigation as well as scrubbing. JPL engineers achieved TMR in their designs by analyzing the design for feedback nets and other low-level design details (as detailed in Xilinx application note XAPP197), and then inserted or replaced logic with TMR library elements. After the designs were functionally implemented, the engineers went back through the design and inserted the TMR logic where necessary and made other space-specific design changes.

Due to the critical nature of the XQR4062XL's role, FPGA redundancy was utilized to mitigate all single-event phenomena. The scrubbing technique employed was a complete reconfiguration.

Animation by Dan Maas, Maas Digital LLC (c) 2002 Cornell University. All rights reserved. This work was performed for the Jet Propulsion Laboratory, California Institute of Technology, sponsored by the United States Government under Prime Contract # NAS7-1407 between the California Institute of Technology and NASA. Copyright and other rights in the design drawings of the Mars Exploration Rover are held by the California Institute of Technology (Caltech)/ Jet Propulsion Laboratory (JPL). Use of the MER design has been provided to Cornell courtesy of NASA, JPL, and Caltech.

When an upset condition was detected, the FPGA in question was completely reprogrammed, while the redundant FPGAs remained functional. On the other hand, because of its non-time critical nature, when a fault condition was detected on one of the XQVR1000s, the rover was temporarily halted, the FPGA was reprogrammed, and the rover went back on its merry way.

All of the mitigation techniques on the Mars Exploration Rovers worked exactly as designed by JPL engineers. During the seven-month voyage from Earth to Mars, the Xilinx radiation-tolerant FPGAs on the lander were "left on." During that time JPL collected data of interest, including the upset rate. The upset rates predicted for the FPGAs by JPL matched almost exactly the actual upset rates observed. Also, the upset detection and mitigation techniques implemented on the FPGAs performed their functions flawlessly and allowed for robust and reliable operation.

### The Present

JPL is currently working on flight designs with both Virtex-II<sup>TM</sup>, the latest Xilinx radiation-tolerant family, as well as Virtex radiation-tolerant FPGAs. These new missions will fly in the next two to five years and are becoming more and more sophisticated in both mission electronic requirements and design implementation. These current projects more fully utilize the FPGA's inherent benefits.

JPL is particularly interested in the ability to update or revise designs while the spacecraft is either in flight to its final destination or already there. This will allow engineers to implement algorithm enhancements after the spacecraft has left Earth, enabling them to constantly improve design performance during a long mission timeline. This, coupled with partial reconfiguration, will allow an FPGA-based design to have one portion of its design upgraded while the rest of the design remains completely operational.

There have been some breakthroughs in the area of single event mitigation and correction. Xilinx, in partnership with Sandia Labs, recently produced a TMR tool that

will XTMR a design. The XTMR tool takes in a synthesized netlist, analyzes it, and applies the appropriate TMR measures and space-specific design modifications to produce a final XTMR netlist. Not only does this guarantee a much more robust TMR design, it also takes what used to take an engineer days or weeks to perform and reduces the process to a matter of minutes.

### The Future

Who knows that the future has in store? The new missions have more demanding requirements: more speed and more integration, with an ongoing goal of less space and less weight. On the Xilinx front, each subsequent family of radiation-tolerant FPGAs (like Virtex-II Pro<sup>TM</sup> devices) will provide more integration, more architectural features, and more capabilities.

The need for more integration, speed, and reduced space and weight goes hand in hand with continually improving radiation-tolerant FPGAs. Xilinx advances in FPGA technology and the improvements in radiation testing and processing made possible by their relationship with JPL come together to spell success.

### **Conclusion**

The collaborative efforts between JPL, the Xilinx aerospace and defense team, and local support (provided by the manufacturer's representative, Norcomp SC, and Nu Horizons Electronics Distribution) helped pave the way for Xilinx to go from a predominantly ASIC prototyping role to become key components in the successful design and implementation of the Mars Exploration Rovers.

Current JPL flight projects that will launch in the years to come are already being designed using the latest Virtex and Virtex-II Xilinx high-reliability FPGAs. And the continual release of bigger, faster, and better Xilinx radiation-tolerant families means that with Xilinx and JPL, not even the sky is the limit.

For more information, please visit http://marsrovers.jpl.nasa.gov/home/, www.xilinx.com/esp/mil\_aero/index.htm, www.norcompsc.com, and www.nuhorizons.com.

## At your Service. From start to finish.

### www.xilinx.com/services

Xilinx offers the industry's broadest portfolio of education, support and design services to extend your technical capabilities, accelerate your time to market, and build a competitive advantage.

- Reduce the learning curve

- Speed your design time

- Jump-start your product development cycle

- Lower your overall development costs

### **Finish Faster**

Xilinx delivers industry-leading service and support through every step of the design process—around the clock and around the world—to help you get to market faster. From technical support, consultative services, and dedicated design assistance to online support and training, you can find it all at www.xilinx.com/services.

## Streaming Data at 10 Gbps

Using a Virtex-II/Pro FPGA to stream data from DDR-SDRAM to OC-192 serializers.

by David Banas President Tao of Digital, Inc. dbanas@taoofdigital.com

You'd like to use DDR-SDRAM as the storage medium for OC-192 test pattern generation to dramatically increase the length of patterns available to you. However, when you take the standard approach to architecting this interface and attempt implementation in a FPGA, you find that the FIFO read clock enable signals don't meet the timing requirements. Your project budget can't afford an ASIC. How can you get around this issue and make the FPGA work as the needed interface?

Fortunately, the Xilinx® digital clock manager (DCM) provides the answer. As long as you've got sufficient global clock resources available, you can use the DCM's quadrature-phase outputs to clock the outputs of the four FIFO groups directly. This eliminates the need for clock

enable signals in the 320 MHz clock domain and yields a design that will achieve timing closure at that speed.

### Standard Architecture

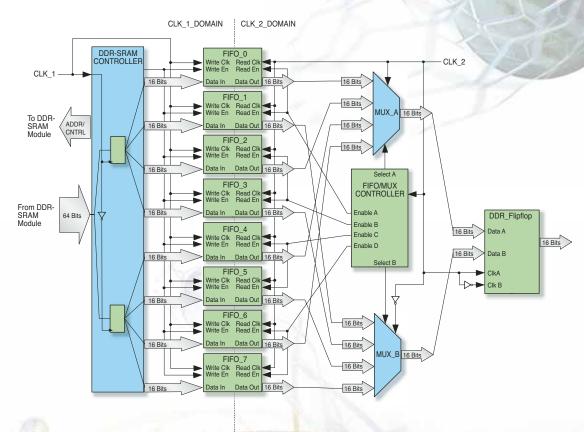

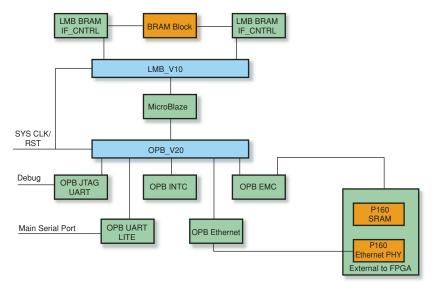

Figure 1 shows the standard architecture used to design a streaming data interface between DDR-SDRAM and OC-192 serializers. All of the design blocks shown in this figure, with the exception of the FIFO/MUX controller, are available as directly instantiated elements (the DDR flip-flop), Xilinx CORE Generator<sup>TM</sup> modules (MUX x and FIFO n), or Xilinx-provided reference designs (DDR-SDRAM controller).

### **DDR-SDRAM Controller**

The DDR-SDRAM controller is a modified Xilinx-provided reference design. I modified it to provide a continuously streaming mode of operation. The controller provides the necessary address and control signals for driving a standard PC-1600/2100 DDR-

SDRAM module and also converts the data bus from a 64-bit DDR mode to a 128-bit SDR mode to facilitate a simpler clocking scheme inside the FPGA.

The controller stops fetching data from memory and disables the write enable signal to the FIFOs when it detects that FIFO\_0's high watermark signal has gone active (not shown in Figure 1).

The frequency of clock 1 is 100 MHz, yielding a burst data rate of 12.8 Gbps. This data rate is 28% higher than that required by the serializer, leaving room for overhead tasks such as DRAM refresh.

### **FIFOs**

The eight FIFO blocks represent standard, asynchronous FIFO elements generated using the CORE Generator tool. The FIFOs serve a dual purpose. First, they provide elastic buffering between two asynchronous clock domains. Second, they work in conjunction with the MUX *x* and FIFO/MUX controller blocks to provide

the data bus width reduction. This is necessary to convert from the 128-bit data bus presented by the DDR-SDRAM controller to the 16-bit data bus required by typical OC-192 serializers. I will explain this functionality in more detail.

### **MUXs**

The two multiplexer blocks represent standard 4-to-1 synchronous 16-bit bus multiplexers also generated using the CORE Generator tool.

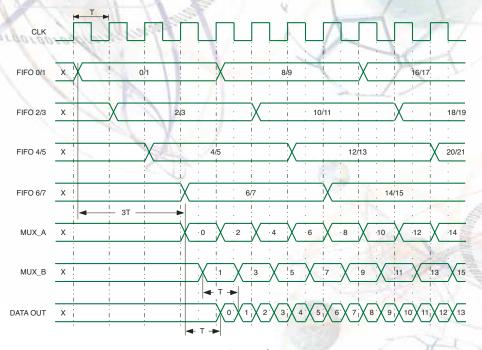

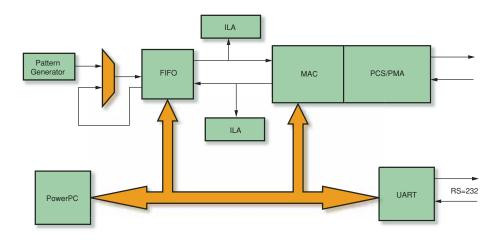

(also shown in Figure 1). Its operation is straightforward and you can easily understand it by looking at the timing diagram of Figure 2.

Note that while the signals generated by the FIFO/MUX controller are not explicitly shown in the timing diagram, their behavior is implicitly depicted there. For instance, the outputs of FIFOs 0 and 1 only change when the enable A signal from the FIFO/MUX controller is active.

Likewise, whenever a multiplexer out-

(1/[320 MHz]). The numbers identifying the various data intervals correspond to the index of a particular 16-bit word in a sequence of data, which is at least 24 16-bit words in length. The FIFO outputs are updated once every four clock cycles in quadrature succession, as shown in the timing diagram.

The two multiplexers select from among the four FIFO groups in the same succession. However, a delay is imposed on the multiplexer selection sequence such that the

> FIFO outputs are allowed three clock cycles to propagate to the multiplexer inputs before being selected, as shown.

By designing this way, I can apply a multi-cycle delay constraint to the FIFO outputs and thus ease the task of the place and route engine. This is very helpful when designing in a 320 MHz clock domain. The DDR flipflop selects from among its two inputs in standard fashion, as shown. The result is a 640 Mword/s data stream at the output, yielding a data rate to the serializer of 10.24 Gbps.

### Implementation Results

Up to this point, the proposed architecture appears to satisfy the design requirements. However, when I tried to implement

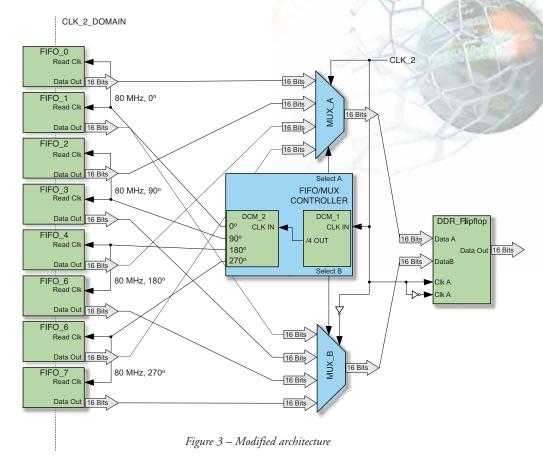

this approach in a XC2V1000-6BG575 part, I couldn't get the propagation delays of the FIFO read clock enable signals under the 3.125 ns period constraint imposed by the 320 MHz clock. Therefore, I came up with the following modification to the basic architecture (Figure 3), which resulted in successful timing closure.

### **Modification Description**

In the modified architecture shown in Figure 3, I eliminated the clock 1 domain section of the design, as it is irrelevant to

Figure 1 – Standard architecture

### DDR Flip-flop

The DDR flip-flop is a directly instantiated element of the Virtex-II<sup>TM</sup>/Pro<sup>TM</sup> architecture. Its two inputs are multiplexed onto its single output through successive clocking at both clock edges. In this way, the data A input is clocked through to data out at the rising edge of the clock, while data B is clocked through at the falling edge.

### FIFO/MUX Controller

The FIFO/MUX controller is the only fully custom element in the architecture

put changes, it is the respective select X signal from the FIFO/MUX controller that dictates which of the multiplexer's four inputs gets clocked through to its output.

### **Timing Discussion**

As mentioned previously, Figure 2 depicts a timing diagram that describes the dynamic behavior of the architecture shown in Figure 1. The clock signal shown is clock 2 from Figure 1. (The clock 1 domain does not contain any novel design features.)

The clock period "T" is 3.125 ns

14 Xcell Journal

the discussion. The only design block that changed in the modified architecture is the FIFO/MUX controller; all other design blocks remain unchanged.

Instead of generating clock-enable sig-

nals, the controller block generates four 80 MHz clocks in a quadrature phase arrangement. This is very easy to accomplish when designing for the Xilinx Virtex-II/Pro architecture, as the DCMs in that architecture

have quadrature phase outputs. All I had to do was divide down the 320 MHz clock by a factor of four, using an additional DCM, to generate the original 80 MHz clock signal.

When I apply these quadrature-phased 80 MHz clocks directly to the four FIFO groups, respectively – without using any clock enable signals – the data at all FIFO outputs is exactly as required by the original architecture. You can see this fairly easily by envisioning these four clocks overlaid atop the four FIFO *nln* signals in the timing diagram of Figure 2.

Notice that the rising edges of the four clocks line up perfectly with the changes in the outputs of the four FIFO groups. You no longer need to use clock enables to govern the FIFO read clocking and have, therefore, eliminated the one group of signals that failed to achieve timing closure. Of course, you must have two additional DCMs and five additional global clock buffers available to make use of this approach.

Figure 2 – Output data timing

### Conclusion

By taking advantage of the design technique presented here, OC-192 test pattern generation hardware designers can avail themselves of the low cost and large capacity of standard DDR-SDRAM modules, thereby making possible the use of extremely long test patterns or automated testing with many shorter patterns, all without incurring the cost of ASIC design and production.

The technique presented here will also find applicability in the area of direct digital synthesis (DDS) of arbitrary waveforms, where a high-speed digital waveform is used, in conjunction with PWM or Sigma/Delta modulation and subsequent low-pass filtering, to produce arbitrary waveforms with great precision and repeatability.

If you have any questions or suggestions, please contact me, David Banas, at (415) 846-5837, or e-mail at *dbanas@taoofdigital.com*.

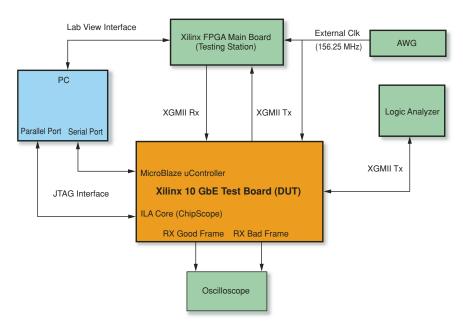

A step-by-step guide to solving QDR memory data capture challenges with Virtex-II FPGAs.

by Jerry A. Long Technical Marketing Manager, Chronology Division Forte Design Systems jlong@forteds.com

As design requirements push memory interfaces to operate at 200 MHz and beyond, a new set of timing challenges enters the design arena. Timing analysis plays an increasingly prominent role in the identification and resolution of system operation issues.

It's likely that you will use double data rate (DDR) or Quad Data Rate (QDR<sup>TM</sup>) memory devices in your next high-speed design, which brings the added need to design signal skew into the memory controller to ensure proper clock/data relationships.

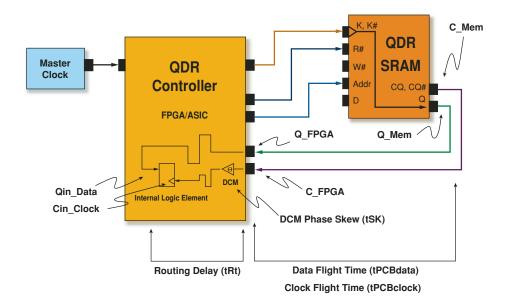

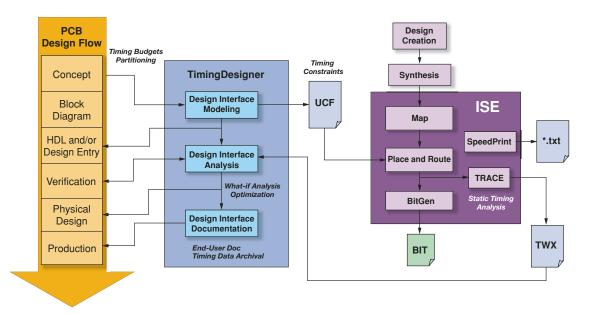

Xilinx® has simplified the use of these devices by providing high-performance external memory interfaces directly from their Virtex-II<sup>TM</sup> FPGAs. And to clearly understand interface timing and potential issues, Chronology has added features to its TimingDesigner® tool to streamline the exchange of critical timing data with the Xilinx ISE software suite.

TimingDesigner generates place and route constraints, allowing direct use of post-place-and-route timing information to verify desired FPGA interface operation. You can accurately determine the proper clock/data relationship for your DDR/QDR memory interface design, export the information as constraint data into ISE, and automatically get visual verification of design success.

For the purposes of this design guide, we'll use a QDR SRAM device to illustrate a source-synchronous interface design. Stepping through the design flow, we implemented a QDR memory controller in a Xilinx X2V50 Virtex-II Pro<sup>TM</sup> FPGA with a focus on the interface signals required for a read operation, utilizing a 133 MHz master clock. The memory device is a Micron<sup>TM</sup> 18 Mb QDR II four-word burst SRAM (MT54W1MH18J).

The features and principles outlined here are not necessarily unique to high-speed memory design. TimingDesigner's robust timing diagram-based analysis features, coupled with its Xilinx-specific import/export capabilities, allow a level of integration that can be applied to any timing-critical design interface for Xilinx FPGAs.

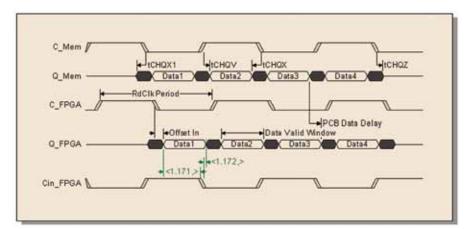

### **QDR Interface Timing Requirements**

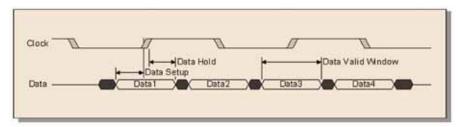

QDR SRAM devices have unique timing requirements for successful read operations. In order to guarantee accurate data capture, QDR devices require the capture clock to be center-aligned within the valid data window. For source-synchronous designs, this means shifting the optional-use echo data clock supplied by the QDR device.

### Center Alignment of Capture Clock Edges

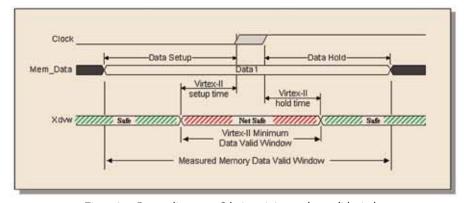

Proper timing for read operations of QDR SRAM interface designs requires you to center-align the edges of the capture clock within the valid window of the data bus for accurate data capture, as shown in Figure 1. This is because most SRAM devices typically have a positive setup and a positive hold requirement, and both are roughly the same value. So it makes sense to center the clock edge within the data valid window to maximize the safety margin for latching data. To accomplish this, the memory con-

troller must skew the capture clock.

For source-synchronous capture of read data from a QDR device, you must use the optional echo clock signals (typically CQ and CQ#) provided from the QDR device. With the Virtex-II Pro family of FPGAs, skewing this clock is easily accomplished using one of the digital clock managers (DCM). However, the amount of phase shift necessary to achieve a safe margin is an unknown, given the external PCB skew

clock/data relationship to ensure that various temperature effects the design may encounter (or other unforeseen influences) won't cause an excessive amount of drift in signal position during the read operation and result in a violation of the setup or hold time requirement of the receiving register. In theory, a center-aligned clock edge will maximize the setup and hold times for most devices, allowing sufficient safety margins for signal drift.

Figure 1 – Illustration of center-aligned clock/data relationship

Figure 2 – Center alignment of device minimum data valid window

effects on both the incoming data and its associated clock, as well as the associated routing delays encountered within the FPGA fabric. TimingDesigner will help us to accurately determine this phase shift value.

### Capturing Read Data in Virtex-II Pro Devices

You can skew (or delay) the clock signal by using PCB trace delay techniques, or by designing clock delay into the memory controller design. Because PCB trace delay techniques aren't very flexible, it makes more sense to use the incidental PCB trace delay coupled with internal FPGA routing delay and use the Virtex-II Pro DCM element as the "adjustable" component for phase shift within the FPGA memory controller design.

Typically, memory manufacturers recommend center alignment of the However, some devices, like the Virtex II-Pro device, have a negative hold time requirement, which simply means that data can transition to the next value before the clock edge that latches it. In effect, this characteristic places the clock edge to the right (delayed) of the data transition. So for these devices, if you center-align the capture clock within the actual data valid window, you may be satisfying the setup/hold requirements of the device, but the safety margin achieved will be greater for the hold requirement than for setup.

The ideal solution is to provide a maximum safety margin for both the setup and hold requirements of a device, which translates to "balancing" these margins. This provides equal amounts of safety for both, as illustrated in Figure 2.

17

Figure 3 – Illustration of signal delay paths for QDR read operation

To accomplish this balance, you must determine the minimum data valid window for the receiving device, and center that window within the actual data valid window provided from the memory device, given your design parameters. Using the minimum setup and hold characteristics of the receiving device, determine a minimum "safe" data valid window with the following formula:

### Min Data Valid Window = Min Setup + Min Hold

Because the placement of the resulting minimum data valid window is tied to the placement of the clock signal, skewing the clock will effectively skew the minimum data valid window. As indicated in Figure 2, as long as the data bus transitions outside of the receiver's minimum data valid window, safe data capture is ensured.

### Determining the Clock/Data Relationship

To determine the required clock skew, you create a timing diagram illustrating the clock/data relationship of a read operation for the QDR device based on the actual read timing diagrams acquired directly from the memory device's data sheet. To be more descriptive of the signal relationships in the diagram, name the read data clock signal *C\_Mem* and the data bus signal *Q\_Mem* to reflect the signals as they appear at the pins of the memory device.

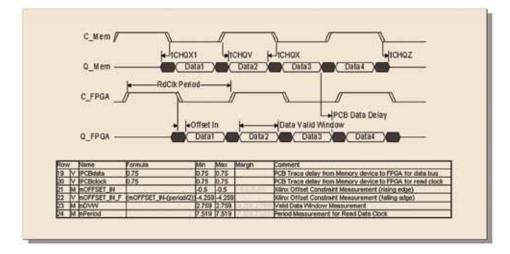

Figure 4 – Clock/data timing diagram of QDR read operation

To model those same signals as they appear at the pins of the FPGA, after their accumulated flight path delay from the QDR device, create the signals *C\_FPGA* and *Q\_FPGA*. Figure 3 is a block diagram illustrating the signal path relationships just described.

The resulting QDR memory read diagram is displayed in Figure 4. The data bus represents the transition period necessary for all elements of the data bus between valid data words. The PCB trace delay accumulated by both data and clock is represented with separate variables: *tPCBdata* for the delay associated with the data signal and *tPCBclock* for the delay associated with the clock. This allows you to easily vary the values and see the effect on the design results.

### Creating Constraints with TimingDesigner

Knowing the timing relationship of an external clock and its associated data as it arrives at the pins of the FPGA provides a unique advantage for accurate data capture and design success. The Xilinx timing constraint *OFFSET* is used along with its associated keywords to provide initial timing information to ISE, so that proper placement of data capture elements and their associated routing delays will be adequate for the design. As illustrated in Figure 5, TimingDesigner provides direct dynamic access to any measurement within a timing diagram for generation of a place and route constraint file (UCF).

For this design example, you need to measure the offset for the data (*Q\_FPGA*) and clock (*C\_FPGA*) signals, and the duration of the valid data window at the pins of the FPGA controller. This can be done directly from the timing diagram using TimingDesigner measurements, as indicated in Figure 4. You'll also need the read data clock period measurement.

### Generating Constraint Information

TimingDesigner's Dynamic Text dialog box offers a way to reference timing diagram measurements from within a vendor's specific timing constraint syntax. Using ISE's *OFFSET* timing constraint syntax, you reference the measured offset values in

the Dynamic Text dialog box to assemble constraints for transfer into the ISE constraints file. The syntax for this design example is illustrated below:

OFFSET = IN %mOFFSET\_IN.min VALID %mDVW.min ns BEFORE "rd\_clk" TIMEGRP RdClkRisingFFs;

OFFSET = IN %mOFFSET\_IN\_F.min VALID %mDVW.min ns BEFORE "rd\_clk" TIMEGRP RdClkFallingFFs;

The VALID keyword is for specifying the duration of the incoming data valid window, and is used for hold time calculations in ISE. The signal rd\_clk is the pin name in the design code associated with the C\_FPGA clock signal in the timing diagram. Notice that two offset specifications must be declared – one for the rising clock edge and one for the falling clock edge – because this is a dual-data rate read operation. Also notice the "%" syntax that indicates dynamic text access of measured values in the timing diagram.

The Dynamic Text dialog box will resolve the dynamically referenced measurements and allow direct transfer of the information into the UCF constraints file. Once the UCF file has been assembled, execute a place and route in the ISE tool set.

### Take Control of Your Design

After initial place and route is complete, you can generate a timing report using the TRACE timing analysis tool within ISE, and import that into the timing diagram. This will allow you to determine the actual routing delays so that you can specify the necessary phase shift for the read clock. You then enter the phase shift attribute into ISE, execute a final place and route, and generate a timing report. When complete, you then re-import the timing report to gauge how well the constraints were met.

### **Determining Routing Delays**

For this design example, ISE placed the read data capture registers into the I/O blocks of the Virtex-II Pro devices, because they capture data from the input pads and have a common clock and reset signal. This is a default setting for ISE's mapping process and is appropriate for this design example.

As the I/O blocks have only one routing path for input data signals, the TRACE report includes this data path delay in the setup and hold requirements of the I/O block registers. However, the clock signal has several possible paths from the input pad to the capture register, and this design example uses a path through the DCM element for phase shift control. So you must determine the routing and element delays for the clock path to achieve proper phase shifting of the clock.

A TRACE analysis report is generated in verbose mode to get the needed timing information. This report is limited to 16 paths per constraint (the data bus is 16 bits). Briefly look at the report and make note of the worst-case setup path for the data bus in preparation for import into the timing diagram.

To import the desired TRACE analysis report information (saved as a TWX file)

into TimingDesigner, map the worst-case setup path identified earlier to the associated waveform in the diagram (*Q\_FPGA*), and then import the information to create variables for the routing and element delays. Mapping the FPGA ports guides TimingDesigner to the desired signal information, and allows for automatic updates of existing variables if successive place and route executions are necessary.

### Visualization at the Capture Register

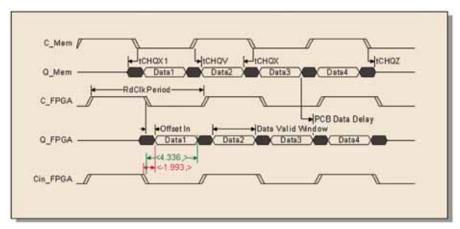

After importing the timing results, create another clock signal (*Cin\_FPGA*) to represent the clock characteristics at the data capture register. You then add the setup and hold requirements obtained in the TRACE report import as TimingDesigner constraints on the data signal relative to the register clock, as shown in Figure 6.

Notice that the indicated setup and hold margin results from the diagram match the slack values from the initial TRACE timing report, and indicate that the setup paths are failing by about 2 ns, but the hold time paths have more than enough margin. You need to shift the clock so that both the setup and hold time measurements are met with roughly the same margin.

Figure 5 – TimingDesigner offers an intuitive interface to ISE's design flow.

Figure 6 – Setup and hold of data capture register after initial placement

Figure 7 – Balanced setup and hold of data capture register

### Making Adjustments

Using the imported information obtained from the TRACE timing analysis report and the measured values from our timing diagram, you can obtain the attribute value for the necessary DCM phase shift (see sidebar, "Balancing the Data Valid Window"). For this example, the attribute value was determined to be 108, for a shift of 3.165 ns. You then enter this value into the ISE tool flow, and execute a second place and route to shift the clock and properly balance the setup/hold margins.

### Verifying the Results

Re-importing the new post-place-and-route timing report using the previous import settings will automatically update all of the necessary values, and correctly re-position the register clock signal (*Cin\_FPGA*). This is illustrated in Figure 7. Examination of these timing results shows that the setup and hold

requirements for a read data capture in the design are now balanced with respect to margin (slack), giving the safest possible result for any unforeseen signal drift.

### Conclusion

Using TimingDesigner together with Xilinx Virtex-II Pro devices allows optimal safety margins for setup and hold requirements, which are necessary for accurate data exchange with a QDR SRAM memory controller.

By following a design process that combines the use of TimingDesigner timing diagrams and ISE's post-place-and-route timing reports, you can create an accurate analysis of your design's critical timing relationships. Using timing diagrams, you can account for PCB trace delays and other external factors that will affect the signal relationship at the pins of your FPGA device.

ISE's TRACE timing analyzer provides timing reports that give you details on the route delays and constraint requirements of your FGPA device. Together, these tools allow you to accurately capture and exchange critical interface timing information, and allow visual verification that your design will perform as desired.

To learn more about TimingDesigner and the Chronology Division of Forte Design Systems, please visit www.timingdesigner.com.

### **Balancing the Data Valid Window**

You can determine the amount of DCM-generated phase shift needed for the clock signal to balance the data window using the following procedure:

1. Subtract the minimum data valid window for the Virtex-II Pro device from the design's actual data valid window, and divide that result by two. This accounts for the difference between the two valid data windows (DlyDVW).

### DlyDVW = (DVWactual - DVW VIImin) / 2

2. Subtract the offset measurement made at the pins of the FPGA device from the required setup time for the capture registers, to account for device setup requirements (DlyRelSU).

### DlyRelSU = IOBsu - OFFSET

3. Determine total clock path delay from the TRACE timing report (Xtcd).

### Xtcd = <from TRACE report>

4. Add up the necessary delays (values obtained in 1 and 2 above), and subtract the total clock path delay (value from 3 above).

### Clk offset = (DlyDVW + DlyRelSU) - Xtcd

5. Finally, determine the correct ISE attribute value to control DCM phase shift with the formula:

phase shift attribute = (Clk offset/Clk period)\*256

### Celebrating 20 Years of Partnership

Turning an industry cliché into a successful business model.

by Xilinx Staff

"Partnership" might possibly be the most overused word in the high-technology industry. But at Xilinx®, it transcends cliché as a foundation principle behind the company's highly successful business model since its inception.

Today, the Xilinx way of thinking reflects a rare mindset about the value of an interconnected ecosystem of like-minded companies and the benefits such an approach can bring to Xilinx, its customers, and to the partners themselves.

To say that Xilinx was founded on the Spirit of Partnership is no overstatement. In the original 1984 business plan, the second bullet under the "strategy" section (after the primary strategy point of "maximizing our strength in product architecture and design") articulated the idea to partner with complementary suppliers. The Xilinx founders thought that through an extreme focus on a few core competencies, Xilinx could deliver highly differentiated products and drive technology innovation forward.

Most notably at the outset was the need for a manufacturing partner. The founders fundamentally believed that there was no need to fund such a capability in-house – a radical concept in the era of "real men own fabs." (The average price tag for a fab at the time was \$300 million, about one-tenth of today's going rate, but still a hefty investment for a startup company in 1984.)

### ...Programmable logic technology is an excellent means for manufacturers to characterize new processes...

Company founder Bernie Vonderschmitt leveraged past relationships and his solid reputation for fair play to negotiate a manufacturing deal with Japanese giant Seiko, which agreed to allow Xilinx-designed chips to be produced in its fabs. Sealed with only a handshake, Xilinx had its first partner and the industry had a new model – the fabless semiconductor company.

In short order Xilinx signed up another critical partner as its first distributor, because the founders viewed the sales process as they did manufacturing: essential, yes, but not necessarily something the company needed to "own." As with Seiko, the distribution agreement was built on mutual trust and a benefit to both sides – a benefit that could be measured beyond just dollars and cents.

Since then, Xilinx has formed partnerships with a wide range of other suppliers in the semiconductor supply chain, all guided by a consistent principle.

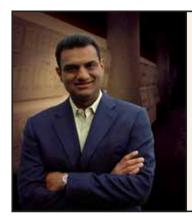

"When we look at forming a partnership, the first question we ask is 'what's in it for you?" Xilinx CEO Wim Roelandts says, explaining a philosophy that may seem counterintuitive to the traditional approach. "It really should be weighted 51-49 in the partner's favor. They need to get something out of it, as much – if not more – than we do."

Such an approach has helped Xilinx assemble critical components to fill the "solution gap" in its offerings, allowing it to focus on developing the core technology for which it has gained the deserved reputation of a world-class innovator. It has also made Xilinx one of the most respected companies in all of high technology and a favorite among complementary suppliers both large and small.

"For us, a partnership is more than a financial transaction or relationship. It really is about shared goals and ways of thinking," says Sandeep Vij, vice president of worldwide marketing at Xilinx. "Yes, we use partnerships to maintain our own focus and we know it doesn't make sense economically for us to invest in all areas. But it comes down to results – our partnerships are aimed at making breakthroughs that allow our customers to scale new heights."

### **Manufacturing Partnerships**

Manufacturing still represents the most substantial of the Xilinx partnering strategies, if only because of the cost of today's modern fabrication facility. Xilinx has emerged as one of only a small handful of semiconductor companies that truly "pushes the envelope" when it comes to implementing new technology processes. Recently, it became the first company to ship a production device based on 90 nm process geometries, considered the leading edge of expertise. It also is among the leaders in the use of 300 mm wafers to produce its chips. Both manufacturing achievements allow Xilinx to reach new price/performance milestones with its products and further distance itself from its competitors.

Although such advances are enabled by choosing the right type of company to partner with (for manufacturing, Xilinx partners with UMC<sup>TM</sup> and IBM<sup>TM</sup>), Xilinx itself is a key contributor to driving manufacturing advancements. The company has more than 100 engineers on-site at UMC, for example, working in tandem with their R&D teams. And because of the "regular" nature of its structure, programmable logic technology is an excellent means for manufacturers to characterize new processes, as UMC has done with its last several generations of new process nodes. But perhaps the secret ingredient is mindset.

"Our partners must share our view on risk-taking. They must be willing to engage in joint risk-taking and be willing to try new things. It is the only way to stay on top of leading-edge technology, to truly innovate," says B.C. Ooi, Xilinx vice president of operations and the man responsible for seeing that Xilinx products stay on the leading edge.

"Programmable technology requires the smallest geometries and advanced processes – and we must be a leader in those areas. We are willing to invest to be able to achieve such things as producing the world's largest dies, to be first to 90 nm. And our partners must be, too."

Ooi also points out that because Xilinx is a mission-critical supplier to its customers, its partners must share that sense of urgency and flexibility. "They have to be able to scale with us," he says of an increasingly valuable asset in the cyclical semiconductor industry.

Vincent Tong, vice president of product technology, agrees, adding that the number-one criterion for a Xilinx partner is to be a "technology leader.

"We can't afford to partner with companies that aren't leaders in what they are doing. Three or four years ago, when it came to manufacturing, you could kind of throw a design over the wall. Today we need to be engaged tightly with our partners to drive technology forward. We have more than 80 process engineers and we don't even own a fab," he says, underscoring the commitment level of Xilinx even in areas in which it chooses to partner.

Through its partnership strategy in manufacturing, Xilinx is already pushing into areas beyond the current state-of-theart, including joint development work in 75 and 65 nm process geometries.

### The Link to the Customer

As with manufacturing, Xilinx made the decision early on that it would work with partners to sell and distribute its products (notably, field support of those products was always viewed as a critical internal function).

"It was a decision borne out of necessity and practicality," explains Vice President of Sales Steve Haynes, who's been with the company for nearly 20 years. "We knew that as a company we needed to focus on what we do best – design, technology, innovation. We needed a ready-made channel to

## Today, Xilinx counts some 250 complementary technology and service providers in its "ecosystem" of companies that help it deliver the most robust solutions in the industry.

get our technology in the hands of the customers. There were, and still are, firms that bring an expertise and reach that we couldn't or didn't want to develop ourselves."

Today Xilinx uses a network of close to 30 partners to deliver its products to customers around the world. Some are broadline distributors who sell complementary technology to round out the use of programmable logic. Others are regional or vertical market specialists. In most cases, Xilinx is the most significant product line they represent, and in all cases the relationship is based on mutual trust and shared values.

"When a customer looks at a rep [resentative], they are looking at Xilinx. We have to be on the same page in all facets of the relationship. We have to know them as well as we know ourselves," says Haynes.

Haynes and his team meet regularly with sales partners to align their goals and strategies, and make sure the company's products are being represented consistently with the "Xilinx Way."

The formula is surely working, as Xilinx sales and customer satisfaction metrics show. But it's a constantly evolving process, as Haynes well knows. "Good partnerships evolve. Our channel looks a lot different than it did 20 years ago. It's like being in a marriage – you have to work at it."

### **Comprehensive Solutions**

The design and use of programmable logic has become an increasingly complex process. In the early days of Xilinx, third-party design tools were just coming to market as the EDA industry took shape, and commercial IP cores were almost non-existent. Today, they, along with a set of other capabilities, are essential to developing multi-million gate, multi-function systems on chip (SoCs). Thus, the Xilinx partnership model has expanded significantly to include technology partners who can round out the core offering.

"Today's markets call for a complete solution, which includes the FPGA and a full set of components and tools," says Senior Manager Strategic Relationships Jasbinder Bhoot, who oversees all of the partnership programs at Xilinx. "Xilinx has been successfully delivering for years the best FPGA products in the industry. Now, together with our partners, we have a focused emphasis on providing comprehensive solutions to our customers. We seek out and collaborate with best-in-class companies to complement our product offerings with EDA tools, IP, design services, reference designs and manufacturing kits."

Xilinx partners must share our sense of business integrity and win-win philosophy. "We are fairly selective in who we work with. Yes,

who we work with. Yes, they must bring a best-of-breed offering, and yes, it must make economic sense for

both sides. But these are the companies with whom we will be on the front lines with our customers, so we have to be in synch on many different levels," explains Bhoot.

Bhoot and his team use well-defined metrics to gauge how effective each and every partnership is for Xilinx and its customers. And they are constantly on the lookout for new areas to develop partnerships and make Xilinx technology more accessible and complete.

the lookout for new areas to develop partnerships and make Xilinx technology more accessible and complete. Today, Xilinx counts some 250 complementary technology and service providers in its "ecosystem" of companies that help it deliver the most robust solu-

tions in the industry. From industry leaders such as IBM<sup>TM</sup>, Cadence<sup>TM</sup>, Mentor

Graphics®, Synopsys<sup>TM</sup>, Synplicity<sup>TM</sup> and Wind River<sup>TM</sup> to specialized experts in key areas, Xilinx partnerships provide maximum breadth and depth of technology offerings.

23

Xcell Journal

Among the areas in which Xilinx partners are:

- Intellectual property cores. Xilinx works closely with independent thirdparty core developers to produce a broad selection of industry-standard solutions, deemed AllianceCORE™, dedicated for use in and optimized for Xilinx programmable logic.

- Design tools. Xilinx's AllianceEDA partners are among the tool leaders for each step in the design process, including such critical areas as highlevel design, synthesis, logic verification, and complete PCB design. Xilinx and its partners develop the methodologies and tool flows that help make programmable logic users productive and well positioned to take full advantage of Xilinx devices.

- Design services. Xperts are a global network of certified design experts trained to take full advantage of the features present in the Xilinx Platform FPGAs, software, and IP cores. When customers need design expertise, they can access a sophisticated resource database and quickly identify design consultants in their own regions.

Embedded development tools.

Xilinx AllianceEmbedded partners are experts in the field of embedded systems – inclusive of compiler, debugger, IDE, and trace/visibility

### The Spirit of Partnership

Xilinx has developed a successful formula for delivering a steady stream of innovation and technology firsts to the market in its first 20 years. Its partnership approach is an essential element of that formula, and although no one intends to alter the basic strategy, the technology industry mandates that change is a constant.

"Xilinx is in a much different position as a company now than when we first started 20 years ago," Roelandts says. "Resource-wise we could consider doing more things ourselves. But we know that the key to our success has been our focus. That has enabled our innovation, which is why we are a leader. In that respect, part-

nerships make even more sense, especially as the world gets more complicated. Our challenge is to continue to develop the right set of relationships with companies that share our vision and make sure we all

## Xilinx has developed a successful formula for delivering a steady stream of innovation and technology firsts to the market in its first 20 years.

tools – as well as RTOS requirements. They support the Xilinx commitment to deliver high-performance, cost-effective embedded processor-based solutions.

Reference designs. Xilinx teams up with industry-leading semiconductor vendors to develop reference designs for accelerating its customers' product and system time to market. derive a benefit. We will not waver on the basic principles that guide our partnership strategy, but we will keep the process dynamic to address new market needs and conditions."

So don't expect to see Xilinx building its own fab in the next 20 years. But thanks to is unique Spirit of Partnership, it's a safe bet that Xilinx and its partners will continue to set the standard for innovation and best business practices in the semiconductor industry.

## Author! Author!

Turn your terrific idea into a technical tome through the Xcell Publishing Alliance.

by Clive "Max" Maxfield

President

TechBites Interactive

max@techbites.com

When reading a technical book, you may sometimes find yourself muttering, "Ha! The author is a complete and utter idiot! I could have done a better job than that!"

Or you may be working on an interesting project – or have just developed a novel solution to some problem – when you suddenly think, "I could write a really cool book about this!"

That initial flush of enthusiasm soon cools, however, when you start to mull over things in a little more detail, realizing that you don't actually have a clue where to start. Is there a market for such a book? What should it cover? Who will create the graphics? How will you find a publisher for your masterpiece?

Given these imponderables, it usually doesn't take long before you've talked yourself out of becoming an author. This is unfortunate, because there may be a lot of potential readers out there who could really benefit from your expertise. And of course, being known as an author can only enhance your career prospects and make your family and friends very proud.

## The Xcell Publishing Alliance is designed to help you take your magnum opus from initial concept, through planning and implementation, all the way to publication, fame, and glory.

To assist authors-to-be (like yourself?), Xilinx® has created an innovative new program called the Xcell Publishing Alliance. The program is designed to help you take your magnum opus from initial concept, through planning and implementation, all the way to publication, fame, and glory.

In fact, as I pen these words, I'm basking in the glow of having just received the author copies of my latest book, "The Design Warrior's Guide to FPGAs: Devices, Tools, and Flows." This book was made possible in large part by Xilinx and Mentor Graphics®, both of whom provided me with access to a wide variety of experts and information sources. Thus, in this article I thought I'd walk you through the process of creating a book – using "The Design Warrior's Guide" as an example – and then discuss what Xilinx can do to help you create your very own tour de force.

### **Topical Questions**

The very first thing you have to decide on is a topic. What exactly would you like to write about? There's little point in spending vast amounts of precious time and effort creating a book that no one actually wants to read.

I've been fortunate in this regard, because I've tended to write books on topics that interest me and that I would like to read myself. Happily, the folks who read my books seem to enjoy them also. For example, my very first effort – "Bebop to the Boolean Boogie: An Unconventional Guide to Electronics" – was recently re-released in its second edition due to popular demand.

Looking back, I realized that most of my tomes were introductory in nature, so the time seemed right to focus on a particular topic in more depth. FPGAs have become phenomenally powerful and sophisticated in recent years. Today's FPGA devices can be used to implement extremely large and complex functions that previously could be realized only using ASICs, and thus an increasing number of design engineers are starting to use the little rascals. When I began to look around, however, there seemed to be a dearth of useful material in this arena.

### **Readership to Shore**

Once you've decided on your topic, you will have to flesh it out into an outline, and eventually grow it into a full-blown proposed contents list. An integral part of this process is to decide who your audience is, because the type of information you will cover will typically vary depending on whether you are talking to engineering gurus or novices.

I personally dislike reading books that talk down to me as though I am the village idiot. But equally, I'm less than enamored by books that try to impress me with the author's brilliance, or those that require me to return to college just to wend my weary way through the first chapter.

In the case of "The Design Warrior's Guide to FPGAs," I wanted to address the needs of an unusually wide audience, including students, sales and marketing professionals in the EDA arena, and full-blown engineers. For this reason, I devoted the first section of the book to fundamental concepts such as:

- What are FPGAs and why are they of interest?

- Underlying technologies, such as antifuses, flash memory, and SRAM cells

- Alternative architectures and concepts

- Different programming techniques

- Who are the various players in the FPGA space?

I felt that this background information would be useful to less-technical readers, while techno-weenies could leap directly into the more challenging middle section of the book. Among many other topics, this section takes an in-depth look at:

- FPGA versus ASIC design styles

- Schematic-based design flows (yes, they are still used to support legacy designs)

- HDL-based design flows

- Silicon virtual prototyping for FPGAs

- C/C++-based design flows

- DSP-based design flows

- Embedded processor-based design flows

- Modular and incremental design

- High-speed design

- Migrating ASIC designs to FPGAs, and vice versa

One thing I recall from my college days is that despite having scores of text-books, I was unable to find the fact I was looking for in any of them. For this reason, "The Design Warrior's Guide" includes a third section boasting a host of peripheral topics, including:

- Choosing the right device

- Gigabit serial interfaces

- Reconfigurable computing

- Field programmable node arrays (FPNAs)

- Independent design tools

- Creating a design flow based on opensource tools

Just looking at the above lists makes my eyes water, because I well remember the research and effort that went into fleshing

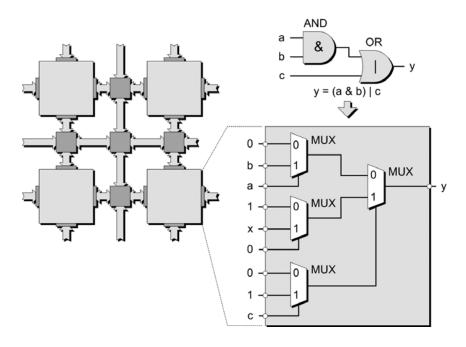

Figure 1 – An example figure created in Visio.

out these topics when I finally got around to writing the book.

### In Style

Yet another point to ponder before you leap into the fray is the style you intend to use. To a large extent this will be determined by your target audience, but it will also be strongly influenced by your personality.

I soon become disgruntled when reading boring books. Unfortunately, this seems to cover the vast majority of technical books out there (although there are a few notable exceptions). It's almost as though someone sent out a memo saying, "Whatever you do, don't make engineering books interesting – otherwise all sorts of folks might decide to read them."

Fortunately, I didn't receive this memo, so I don't feel bound to follow it. As a simple rule of thumb, I tend to write the sort of book that I personally would like to read. Thus, I use a somewhat informal, chatty style – much like this article – and I also like to include nuggets of trivia and tidbits of information, such as "Where did this come from?" or "Why do we do things this way rather than that?"

Furthermore, in my later books I've started to include little pronunciation notes as sidebar items for technical acronyms and terms. I do this because if you mispronounce a word when talking to someone in the industry, you immediately brand yourself as an outsider. Some engineers have been known to scoff at me for this, but I've received many e-mails from less-technical readers that say, "Only the other day you saved me from a potentially embarrassing situation."

### Yes, There's More

At some stage, of course, you are going to have to actually put pen to paper (or fingers to keyboard). Writing a book-length project isn't easy. You may start off full of vim and enthusiasm, but as you approach the middle of the project things seem to slow down and become increasingly difficult — much like wading through molasses. And then, suddenly, you'll find that you've crested the brow of the hill and are racing down the other side towards the finish line.

Another consideration is creating graphics. I personally go by the adage that "a picture is worth a thousand words," so

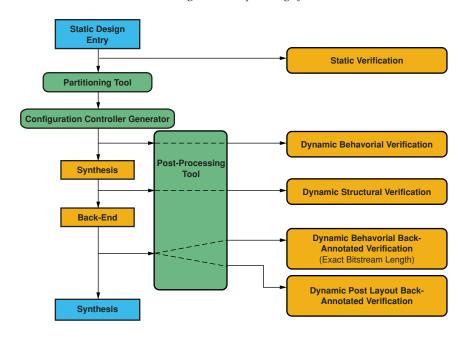

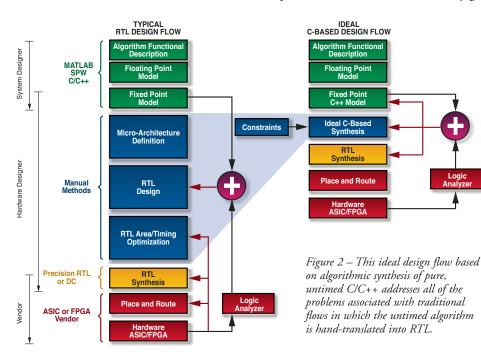

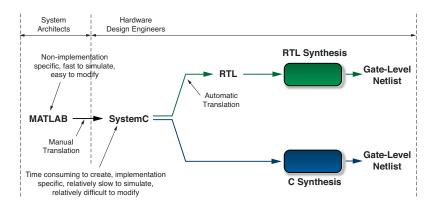

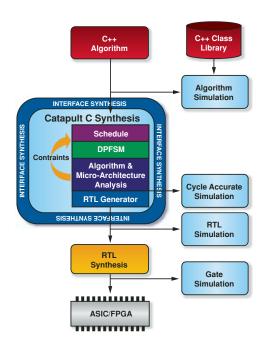

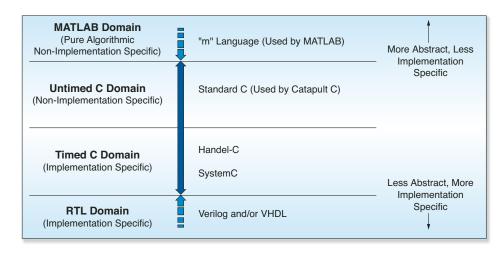

I festoon my writings with graphics wherever I can. For technical books and white papers, I tend to use line art created in Microsoft<sup>TM</sup> Visio<sup>TM</sup>, an incredibly useful and easy-to-use tool. As an example, consider a sample illustration from "The Design Warrior's Guide" (Figure 1), which reflects a simple multiplexer-based FPGA architecture. Logic gates are not usually shown with gray fills and shadows, but I think it looks more interesting – and it's my book.