### ROGRAMME

35th European Solid-State Device Research Conference

12 - 16 September 2005 - Grenoble, France

Organized by

Technical Co-Sponsorship

www.essderc2005.com

## **SPONSORS**

Thank you to our generous sponsors:

|               |                                                                                                  | TUE                                                | SDAY, 13 S                                                                       | EPTEMBER 2005                                                   |                                                     |                                                               |  |

|---------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|--|

| 08:45         | Introduction and Paper Award 2004 (Dauphine)                                                     |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 09:15-09:55   | Joint Plenary Session - R. Cavin (Dauphine)                                                      |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 10:00         | ESSDERC Plenary Session - A. Auberton-Hervé, C. Mazuré (Dauphine)                                |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 10:40         |                                                                                                  | Cof                                                | fee Break (Alpes C                                                               | ongrès - exhibtion area)                                        |                                                     |                                                               |  |

| 11:05         | SESSION 1.A. : Multi-Gate Devices<br>(Dauphine)                                                  | SESSION 1.B. : Ga<br>(Oisans)                      | ION 1.B. : Gate Stack SESSION 1.C. : RF Devices (Oisans) (Sept Laux)             |                                                                 | evices                                              | SESSION 1.D.: Compact Modeling<br>(Stendhal)                  |  |

| 12:45         |                                                                                                  | Lunch Break (Salon les Ecrins)                     |                                                                                  |                                                                 |                                                     |                                                               |  |

| 14:15 - 14:55 |                                                                                                  | Joint Plenary Session - E. Yablonovitch (Dauphine) |                                                                                  |                                                                 |                                                     |                                                               |  |

| 15:00         | 2.A.: Nano-Scaled Devices<br>(Chartreuse)                                                        |                                                    | ic Random Access Memories 2.C. : High- and Medium-K Ch<br>(Belle Etoile) (Meije) |                                                                 | naracterisation                                     | SESSION 2.D.: Nanowires<br>(Sept Laux)                        |  |

| 16:40         | Coffee Break (Salle de Réception)                                                                |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 17:00         | RUMP SESSION: Where Will the Revolutionary Solutions Come from: Technology or Design? (Dauphine) |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 18:30         | End of conference day                                                                            |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 19:00         | Welcome Reception (Musée de Grenoble)                                                            |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

|               |                                                                                                  |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

|               |                                                                                                  | WEDN                                               | IESDAY, 14                                                                       | SEPTEMBER 2005                                                  |                                                     |                                                               |  |

| 09:00 - 09:40 |                                                                                                  | Jo                                                 | oint Plenary Session                                                             | n - M. Shur (Dauphine)                                          |                                                     |                                                               |  |

| 09:45         | SESSION 3.A. : RF and Power SOI<br>(Chartreuse)                                                  | SSION 3.B. : Nanoscale an<br>(Sept Laux            |                                                                                  | SESSION 3.C.: Back-End Characterisation and Reliability (Meije) |                                                     | SESSION 3.D. : Transport in Novel Materials<br>(Belle étoile) |  |

| 11:05         |                                                                                                  |                                                    | Coffee Break (S                                                                  | alle de Réception)                                              |                                                     |                                                               |  |

| 11:25         | SESSION 4.A. : Strain Engineering (Chartreuse)                                                   |                                                    | SESSION 4.B. : Non-Volatile Memories I<br>(Belle étoile)                         |                                                                 | SESSION 4.C.:                                       | Noise and Fluctuations in Nanometer MOSFETs<br>(Meije)        |  |

| 12:45         |                                                                                                  |                                                    | Lunch Break (                                                                    | Salon les Ecrins)                                               |                                                     |                                                               |  |

| 14:15 - 14:55 |                                                                                                  | Joint                                              | Plenary Session -                                                                | M. Thompson (Dauphine)                                          |                                                     |                                                               |  |

| 15:00         |                                                                                                  | ESSDEI                                             | RC Plenary Session                                                               | - HS. P. Wong (Dauphine)                                        |                                                     |                                                               |  |

| 15:40         |                                                                                                  | Cof                                                | fee Break <i>(Alpes C</i>                                                        | ongrès - exhibtion area)                                        |                                                     |                                                               |  |

| 16:00         | SESSION 5.A.: Biological and Optical Devic<br>(Stendhal)                                         | es                                                 | SESSION 5.B. : High-K Dielectrics<br>(Oisans)                                    |                                                                 | SESSION 5.C. : Oxide Reliability and ESD (Dauphine) |                                                               |  |

| 18:00         |                                                                                                  |                                                    | End of con                                                                       | ference day                                                     |                                                     |                                                               |  |

| 19:00         |                                                                                                  |                                                    | Gala I                                                                           | Dinner                                                          |                                                     |                                                               |  |

|               |                                                                                                  | THUI                                               | RSDAY, 15 S                                                                      | EPTEMBER 2005                                                   |                                                     |                                                               |  |

| 09:00 - 09:40 |                                                                                                  | Joir                                               | nt Plenary Session                                                               | C. Joachim (Dauphine)                                           |                                                     |                                                               |  |

| 09:45         | ESSDERC Plenary Session - L. Risch (Dauphine)                                                    |                                                    |                                                                                  |                                                                 |                                                     |                                                               |  |

| 10:25         |                                                                                                  |                                                    | •                                                                                | ongrès - exhibtion area)                                        |                                                     |                                                               |  |

| 10:45         | SESSION 6.A. : CMOS Technology<br>(Dauphine)                                                     | SESSI                                              | SESSION 6.B.: Advanced Process Steps Integration (Oisans)                        |                                                                 | SE                                                  | SSION 6.C. : Power and HV Devices<br>(Stendhal)               |  |

| 12:45         |                                                                                                  |                                                    | Lunch Break (                                                                    | Salon les Ecrins)                                               |                                                     |                                                               |  |

| 14:15         |                                                                                                  | Prese                                              | entation ESSDERC-I                                                               | SSCIRC 2006 (Dauphine)                                          |                                                     |                                                               |  |

| 14:25 - 15:05 |                                                                                                  |                                                    | •                                                                                | - H. Stormer (Dauphine)                                         |                                                     |                                                               |  |

| 15:10         | SESSION 7.A. : Advanced Numerical Metho<br>(Chartreuse)                                          | ds                                                 | (Belle                                                                           | Volatile Memories II<br>étoile)                                 | SESSION 7.C.                                        | : Strained Si Characterisation and Reliability<br>(Meije)     |  |

| 16:30         |                                                                                                  |                                                    |                                                                                  | ille de Réception)                                              |                                                     |                                                               |  |

| 16:40         | SESSION 8.A. : Carbon Nanotube Devices<br>(Chartreuse)                                           | <b>3</b>                                           | (Belle                                                                           | h-Speed Memories<br>étoile)                                     | S                                                   | SESSION 8.C. : Mobility Extraction<br>(Meije)                 |  |

| 17:40         |                                                                                                  |                                                    | •                                                                                | on (Dauphine)                                                   |                                                     |                                                               |  |

| 18:00         |                                                                                                  |                                                    |                                                                                  | ference day                                                     |                                                     |                                                               |  |

| 19:30         |                                                                                                  |                                                    | Farewe                                                                           | ell Party                                                       |                                                     |                                                               |  |

## WELCOME

The 35th European Solid-State Device Research Conference takes place in Grenoble from Tuesday 13 September to Thursday 15 September 2005. The aim of the conference is to provide an annual European forum for the presentation and discussion of recent advances in semiconductor devices and technologies. ESSDERC 2005 is jointly organized with the 31st European Solid-State Circuits Conference (ESSCIRC). The initiative to merge the two sister conferences was started in 2002, as an incentive to foster the necessary interaction among technologists, device experts, and circuit & system designers. While keeping separate Technical Programme Committees, ESSDERC and ESSCIRC are governed by a single Steering Committee and share plenary keynote presentations, tutorials (September 12) and satellite workshops (September 16) bridging both communities. Participants registered for either conference are encouraged to attend any of the scheduled parallel sessions.

ESSDERC-ESSCIRC is the largest and best quality European meeting related to micro and nano electronics. In order to guarantee the excellence of the scientific level, the Steering Committee has abolished posters and half-time presentations, while imposing a very strict acceptance rate (40%). The evaluation of submitted papers has been improved; enlarged Technical Programme Committee, redesigned sub-committee topics, increased number of reports per paper, new functionalities enabled in the web submission system. A total number of 308 papers were submitted to ESSDERC, representing a tremendous increase (+ 85 papers) compared to 2004 and a record for the last decade. More than 30 countries, from all continents, were represented with substantial participations from Europe, USA, Japan and Korea. Most of the papers originated from strong national (55%) and international (16%) co-operations. Only 123 contributions could be included in the final programme of ESSDERC 2005 which also features outstanding plenary and session invited talks. ESSDERC'05 will especially focus on advanced device concepts, revolutionary transistor architectures, new technologies and process steps related to ITRS road blocks, nanotechnologies, quantum and molecular devices, sensors and displays, etc.

Several innovations are tested or reintroduced this year: a joint panel session, session invited talks, an exhibit, a farewell party and technical visits (Friday September 16). Our conference has a new logo. A Special Issue of Solid-State Electronics will contain selected full-length papers. Grenoble will not miss the opportunity to preserve and develop the tradition of a warm Social Programme: the Welcome Reception at the Museum of Grenoble (Tuesday evening), the Gala Dinner and Show on Wednesday evening and, finally, the Farewell Party (Thursday evening) at the scenic Bastille location which overlooks Grenoble area and mountains. The accompanying persons will enjoy several excursions. Grenoble is a high-tech city, with wonderful surroundings in the heart of the Alps, offering attractive opportunities for an extended stay over the weekend.

We would like to thank the authors for their contributions, the members of the Technical Programme Committee, Steering Committee and Local Organizing Committee for their hard work, Mrs Iris Mazuré our omnipresent conference secretary, and our generous sponsors.

We are looking forward to a successful conference, with exciting scientific contents and rich human interactions. We warmly welcome you and your colleagues to Grenoble.

Sorin Cristoloveanu, Conference Chair Michel Brillouët, Conference Co-Chair Thomas Skotnicki, ESSDERC Technical Programme Chair

## TABLE OF CONTENTS ESSDERC

|                                              | paģe(s) |

|----------------------------------------------|---------|

| CONFERENCE ORGANISATION                      | 3       |

| COMMITTEES                                   | 4 - 6   |

| GENERAL INFORMATION                          | 7 - 8   |

| CONFERENCE SITE                              | 9 - 10  |

| MAP CONFERENCE FACILITIES                    | 11 - 12 |

| CONFERENCE REGISTRATION                      | 13 - 14 |

| CONFERENCE INFORMATION                       | 15      |

| SOCIAL PROGRAMME                             | 16      |

| ACCOMPANYING PERSONS PROGRAMME               | 17      |

| ESSDERC-ESSCIRC JOINT PLENARY TALKS          | 18      |

| ESSDERC-INVITED PLENARY TALKS                | 19 - 20 |

| EXHIBITORS                                   | 21 - 22 |

| MONDAY, 12 SEPTEMBER SHORT COURSES           | 23 - 24 |

| TUESDAY, 13 SEPTEMBER SCIENTIFIC PROGRAMME   | 25 - 31 |

| WEDNESDAY, 14 SEPTEMBER SCIENTIFIC PROGRAMME | 32 - 39 |

| THURSDAY, 15 SEPTEMBER SCIENTIFIC PROGRAMME  | 40 - 47 |

| FRIDAY, 16 SEPTEMBER WORKSHOPS               | 47      |

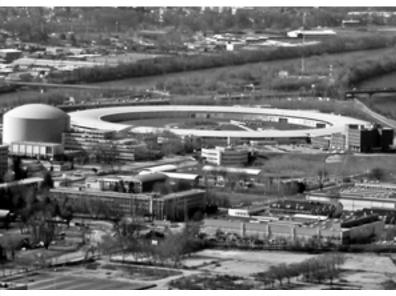

FRIDAY, 16 SEPTEMBER TECHNICAL VISITS

ESRF in Grenoble.

## **CONFERENCE ORGANISATION**

#### Chairs

#### Sorin Cristoloveanu

General Chair sorin@enserg.fr Tel. +33 (0) 476 85 60 40

#### Michel Brillouët

Co-General Chair michel.brillouet@cea.fr Tel. +33 (0) 438 78 43 02

#### **Thomas Skotnicki**

ESSDERC Technical Programme Chair Thomas.Skotnicki@st.com Tel. +33 (0) 476 92 68 29

#### **Further information**

For further information about the conference please contact the conference secretariat:

#### Iris Mazuré Espejo

IMEP/ENSERG

23 rue des Martyrs, BP 257,

38016 Grenoble cedex 1, France

essderc-esscirc@enserg.fr

Tel. +33 (0) 476 85 60 76

Fax +33 (0) 476 85 60 70

Or visit the web page: http://www.essderc2005.com

2005 mm silicon wafers.

## COMMITTEES

#### **Technical programme committee**

G.A.J. Cambridge University (UK) Amaratunga Franck STMicroelectronics Crolles (F) Arnaud University of Glasgow (UK) Asen Asenov

University of Southampton (UK) Peter Ashburn

**Emmanuel** Augendre IMEC (B)

Jean-Luc Autran Université d'Aix-Marseille (F) University of Bologna (I) Giorgio Baccarani

STMicroelectronics Agrate (I) Livio Baldi

IMEP (F) Francis Balestra FhG, Erlangen (D) Anton Bauer

Romuald Warsaw University of Technology (PL) Beck

Chalmers University (S) Stefan

Bengtsson Roberto STMicroelectronics Agrate (I) Bez

Josef Boeck Infineon (D)

Frederic Boeuf STMicroelectronics Crolles (F)

Bork Ingo Synopsys (US) Ralf Brederlow Infineon (D)

STMicroelectronics Crolles (F) Hugues Brut

Joachim Burghartz DIMES (NL)

Eugenio Cantatore Philips Leuven (B)

STMicroelectronics Crolles (F) Alain Chantre

Cesare Clementi STMicroelectronics Agrate (I) Raphael Clerc IMEP (F)

STMicroelectronics Crolles (F) Philippe Coronel

Gilles **Dambrine** IEMN (F)

Αn De Keersgieter IMEC (B)

Kristin De Meyer IMEC (B) Christian De Prost Atmel (F)

Barbara De Salvo CEA-LETI (F) Stefaan IMEC (B) Decoutere Simon Deleonibus CEA-LETI (F)

Dubois

IEMN (F) Eisele Universität der Bundeswehr München (D) Ignaz

Olof Engström Chalmers University (SE)

CEA-LETI (F) Thomas Ernst

STMicroelectronics Agrate (I) Pietro Erratico

University Catholique de Louvain (B) Denis Flandre

University of Granada (SP) Francisco Gamiz

CEA-LETI (F) Gautier Jacques Gérard Ghibaudo IMEP (F)

John Grant Freescale Crolles (US)

Guido Groeseneken IMEC (B)

Hall University of Liverpool (UK) Steven

Paul IMEC (B) Heremans

Jacob Hooker Philips Leuven (B)

Giuseppe University of Pisa (I) lannacconne Adrian EPFL (CH) - TPC Vice-Chair Ionescu

**Emmanuel**

## COMMITTEES

Rvoichi Ishihara Tu Delft (NL) Toshiba (JP) Kazunari Ishimaru

Hiroshi Ishiwara Tokyo Institute of Technology (JP) Hiroshi lwai Tokyo Institute of Technology (JP) STMicroelectronics Crolles (F) Hervé Jaouen

Casper Juffermans Philips Leuven (B)

Malgorzata Jurczak IMEC (B)

Erich University of Stuttgart (D) Kasper

Steven J. Koester IBM (US)

Heinrich Kurz RWTH Aachen/ AMO (D) Andrea University of Milano (I) Lacaita Analog Devices (IR) William Lane

Gilles CEA(F) Le Blevennec CEA-LETI (F) Gilles Le Carval FhG, IISB (D) Jürgen Lorenz

Lidia Lukasiak Warsaw University of Technology (PL)

Massimo University of Pisa (I) Macucci

Pascal Masson Université d'Aix-Marseille (F) Alfonso Maurelli STMicroelectronics Agrate (I)

Carlos Mazuré SOITEC (F)

Kevin McCarthy University College Cork (IR) Bernd Meinerzhagen TU Braunschweig (D)

Robert Mertens IMEC (B)

Ultimate Junction Technology Lab, (JP) Bunii Mizuno

Philips Leuven (B) André Montree Judith Mueller Freescale Crolles (USA)

University of Technology Lodz (PL) Malgorzata Napieralski

Alexiei Nazarov University of Kiev (UA) Olivier Noblanc STMicroelectronics Crolles (F) Serguei Okhonin Innovative Silicon (CH)

Mikael Östling KTH (S) Alain Poncet INSA Lyon (F) Henryk Przewlocki ITE Warsow (PL) Lothar Risch Infineon (D)

Massimo Rudan University of Bologna (I)

Techical University of Bucharest (Ro) Adrian Rusu Sakalas University of Technology Dresden (D), Paulius Semiconductor Physics Institute, Lithuania

EPFL (CH)

Jean-Michel Sallese

Sangiorgi University of Bologna (I) Enrico Marc Sanquer

Andreas Schenk

Integrated Systems Laboratory (CH) Jurriaan Schmitz

University of Twente (NL)

Schoenmaker MAGWEL (B) Wim Hermann Schumacher Universität Ulm (D) Siegfried Selberherr TU Wien, (A) Luca Selmi University of Udine (I)

University of Erlangen (D) Michael Stoisiek

Philips Crolles (F) Peter Stolk

## COMMITTEES

Eiichi Suzuki National Institute of Advanced

Industrial Science and Technology (JP)

Roland Thewes Infineon (D)

Dimitris Tsoukalas IMEL/NCRS (GR)

Mateo Valenza University of Montpellier (F)

Jan Van Houdt IMEC (B) Marc Van Rossum IMEC (B)

Günter Weimann (FhG / IAF Freiburg (D) Terence Whall Warwick University (UK)

Andreas Wild Freescale (USA)

Hans-Dieter Wohlmuth Infineon (D)

Reinout Woltjer Philips Leuven (NL)

Jason Woo UCLA (US)

Katsunobu Yoshimura NEC Electronics Corporation (JP)

Bin Yu NASA (US)

Alex Zaslavsky Brown University (USA)

#### **ESSDERC-ESSCIRC Steering committee**

Werner Weber (Chair) Infineon Corporate Research (D)

Giorgio Baccarani (Vice-Chair) University of Bologna (I)

Peter Ashburn University of Southampton (UK)

Cor Claeys IMEC (B)

Sorin Cristoloveanu IMEP (F)

Franz Dielacher Infineon Technologies Austria (A)

Christian Enz CSEM (CH)

José Epifanio da Franca Chipidea Microelectrónica (POR)

Ernesto Perea STMicroelectronics (F)

Hans-Jörg Pfleiderer University of Ulm (D)

William Redman-White Philips Semiconductors (UK)

Christer Svensson University of Lingköping (S)

Reinout Woltjer Philips Research (NL)

#### **ESSDERC-ESSCIRC Local organising committee**

Raphaël Clerc IMEP-INPG (F)

Simon Deleonibus CEA LETI (F)

Denis Duret CEA LETI (F)

Laurent Fesquet TIMA - INPG (F)

Gérard Ghibaudo IMEP - INPG (F)

Jalal Jomaah IMEP - INPG (F)

Laurent Montes IMEP - INPG (F)

Mehdi Moussavi CEA LETI (F)

Frédéric Petrot TIMA/SLS - INPG (F) Marc Renaudin TIMA - INPG (F)

Thomas Repellin AEPI (F)

Patrice Senn France Telecom R&D (F)

Gilles Sicard TIMA - INPG (F)

## **GENERAL INFORMATION**

#### **GRENOBLE - An Attractive Destination**

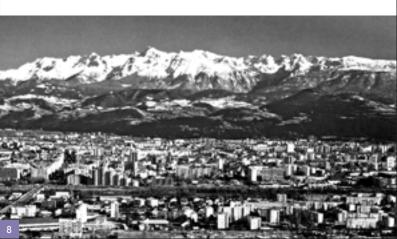

Grenoble is the capital of the French Alpes, located in a valley surrounded by beautiful mountains. On the touristic side, Grenoble is famous for alpine landscapes, sunshine and snow. Stendhal once wrote that "...there was a mountain at the end of each Grenoble street: Belledonne, Vercors and Chartreuse..."

On the scientific side, Grenoble is often referred to as the place where the Silicon and SOI Valleys merge. Stendhal would certainly write today that "...there is research lab or high-tech place at the corner of each mountain".

A number of advanced R&D centres and leading semiconductor fabs are scattered around Grenoble. Application oriented research is blooming, its roots being the dense network of laboratories dedicated to basic research. World class institutes (European Synchrotron Radiation Facility, CEA, CNRS, High Magnetic Field Laboratory, Neutron ILL reactor, etc) are surrounded by numerous smaller, yet outstanding University and CNRS laboratories.

Grenoble is one of the major university towns in France: over 60 000 students representing about 10% of the population of the greater Grenoble area. Grenoble is understandably proud of its academic and scientific environment, with a long tradition of partnership between research and industry.

#### **Climate**

September is usually a sunny month with an average temperature of 20 - 24°C. Since rain showers are possible, light clothing and a raincoat are recommended. However, the organisers have negotiated perfect weather conditions...

#### **Time Zone**

Central European summer time (GMT + 2).

### **Electricity**

Standard European type 2 pin round sockets with 220 Volts, 50Hz are used.

#### **Currency and Value Added Tax (VAT)**

The French national currency is the Euro. France has a Value Added Tax called T.V.A (19.6 %) that is included in the price of all goods and services. Visitors are entitled to claim this tax back on purchases made over a certain amount, upon or after leaving the country.

#### Tips

Tips in restaurants, hotels and taxis are not usual; they are included in the cost.

## **GENERAL INFORMATION**

#### Banks

Banks are usually open from Monday to Friday from 09h00-16h00. Some banks are closed on Monday and some are open on Saturday.

#### **Emergency calls**

In case of emergency, dial 18 for Fire/accident and 15 for Medical Help (SAMU).

#### **Visa Requirements**

All foreign participants must have a valid passport, except the European Union citizens, who need only an identification card. According to the citizenship, the duration and purpose of the stay in France, a visa may be required. For more information http://www.diplomatie.fr/venir/visas/

Invitation letters to apply for a visa will be sent by the organisers upon request. We advise you to forward your request before 15 July 2005 to:

essderc-esscirc@enserg.fr

clearly indicating the dates of arrival and departure.

#### **Hotel Reservation**

ESSDERC-ESSCIRC'05 has blocked hotel rooms for the participants until August 1, 2005. Please note that September is high season for business travellers. It is therefore strongly recommended to complete the reservation of your hotel room as soon as possible.

An updated hotel list is available on:

http://www.esscirc2005.com or http://www.esscirc2005.com

Please contact the hotel of your choice and make the reservation directly, mentioning the name of the conference.

## **CONFERENCE SITE**

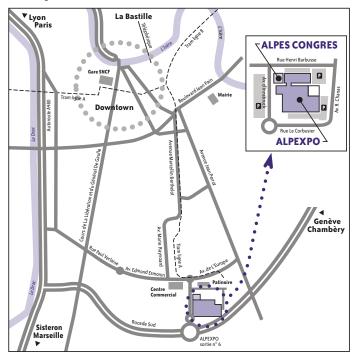

The conferences will be held at:

Alpes Congres - Alpexpo Avenue d'Innsbruck - BP 2408 38034 GRENOBLE - France

#### How to get to the conference site

#### From downtown / Grenoble train station:

- ► Tramway line A, direction Echirolles: Denis Papin, Stop: Pôle Sud.

- By car: Take Rocade Sud (coming from A48 Lyon-Grenoble or A41 Genève-Chambery-Grenoble), exit number 6: Alpexpo-Grand Place. There is a large car park in front of the Alpes Congrès - Alpexpo conference centre.

## **CONFERENCE SITE**

#### By plane:

- Lyon-St. Exupéry airport www.lyon.aeroport.fr: 1 hour drive. Taxi cost: approx. 130 - 140 EUR - Tel. + 33 (0) 826 800 826.

- Airport shuttle bus SATOBUS www.satobus.com (every hour hh.30 from 7.30 am to 21.30 pm direction Grenoble, every hour hh.00 from 5.00 am to 20.00 pm direction Lyon-St. Exupéry) -Tel. + 33 (0) 472 68 72 17

- Airport Genève-Cointrin www.gva.ch: 1.5 2 hours drive. Taxi costs: approx. 220 EUR - Tel. + 41 (0) 22 798 20 00

#### By train:

► High Speed Train (TGV)

Grenoble-Paris 3 hours - 7 trains every day

(other TGV from Lille, Nantes)

Grenoble Gare SNCF:

Tel. + 33 (0)8.92.35.35.35. (reservations) - www.sncf.fr

#### By car - distance from Grenoble:

Lyon: 100 km

■ Geneva: 145 km

► Torino: 240 km

Nice: 330 km

Paris: 570 km

■ Barcelona: 625 km

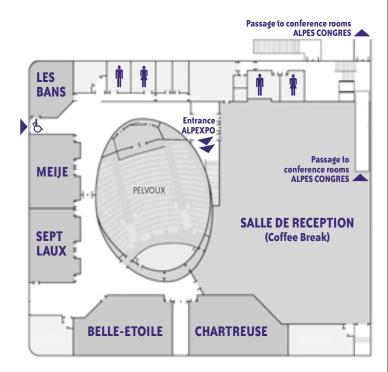

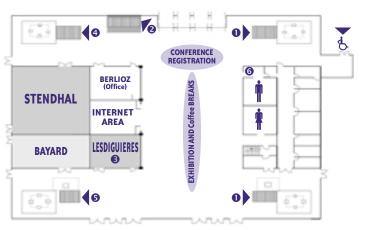

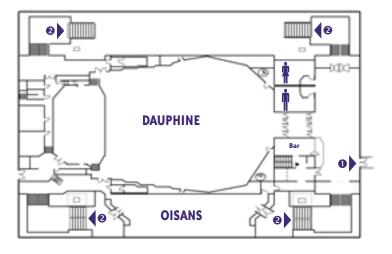

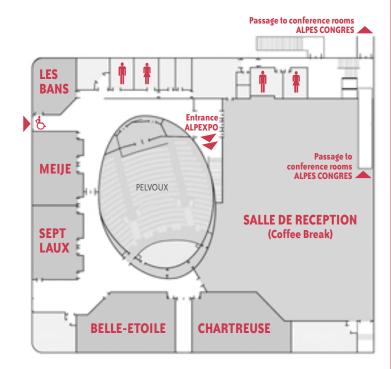

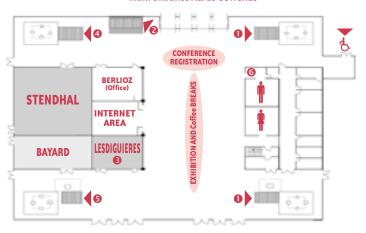

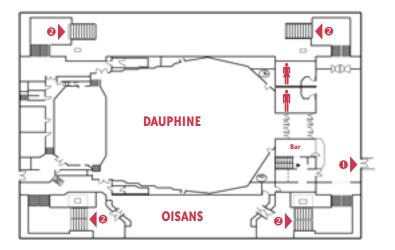

## MAP CONFERENCE FACILITIES

Alpes Congres and Alpexpo are connected by an inner passage.

## First Floor conference rooms Alpexpo

## MAP CONFERENCE FACILITIES

## **Ground Floor conference rooms Alpes Congrès**

#### **Main entrance ALPES CONGRES**

- To Dauphine and Oisans

- 2 Downstairs to lunch area (Salon Les Ecrins)

- Speakers room

- To Dauphine

- To Oisans

- Telephone

### First Floor conference rooms Alpes Congrès

- Passage to Alpexpo

- 2 Downstairs to Conference Registration, Exhibition & Coffe Break

## **CONFERENCE REGISTRATION**

Please complete the registration form (see annexed A4 sheet) and send it or fax it to:

MCI France / ESSDERC-ESSCIRC

11 rue de Solférino - 75007 Paris - Fax +33 (0)1 53 85 82 83

or register online:

#### http://www.essderc2005.com or http://www.esscirc2005.com

To take advantage of pre-registration rates, the completed registration form and fee must be received by 12 AUGUST 2005. Early registration is encouraged.

Conference registration fee covers admission to all sessions, the exhibition, the coffee breaks, the welcome reception, the gala dinner, the farewell party, three lunches, a CD and one volume of the proceedings.

Tutorial registration fee covers admission to the tutorial, the coffee breaks, the lunch, the CDROM containing all short courses, and one printed version of the selected short course.

Workshop registration fee covers admission to the workshop, the lunch buffet and the coffee breaks.

Accompanying persons fee includes the welcome reception, the gala dinner and the farewell party.

| Conference Registration Fees<br>(Tuesday, 13 – Thursday 15<br>September, 2005)      | BEFORE<br>AUGUST 12, 2005<br>(Payment must be<br>received before 12.8.2005) | AS FROM<br>August 13, 2005 |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------|

| Regular                                                                             | 590,00 EUR                                                                  | 670,00 EUR                 |

| IEEE members (IEEE N° required)                                                     | 560,00 EUR                                                                  | 640,00 EUR                 |

| Students (please provide certificate)                                               | 490,00 EUR                                                                  | 570,00 EUR                 |

| Tutorials Registration Fees<br>(Monday, 12 September)                               | BEFORE AUGUST 12, 2005 (Payment must be received before 12.8.2005)          | AS FROM<br>August 13, 2005 |

| Tutorial 1 (full day) "New process and device concepts"                             | 200,00 EUR                                                                  | 250,00 EUR                 |

| Tutorial 1 (Student)                                                                | 150,00 EUR                                                                  | 200,00 EUR                 |

| Tutorial 2 (full day) "Advanced concepts for SOC and SIP"                           | 200,00 EUR                                                                  | 250,00 EUR                 |

| Tutorial 2 (Student)                                                                | 150,00 EUR                                                                  | 200,00 EUR                 |

| Tutorials 3 + 4 (half day each) "Nanoelectronics" + "Emerging Memory Architectures" | 200,00 EUR                                                                  | 250,00 EUR                 |

| Tutorials 3 + 4 (Student)                                                           | 150,00 EUR                                                                  | 200,00 EUR                 |

|                                                                                     |                                                                             |                            |

| Workshops Registration Fees<br>(Friday, 16 September)                               | BEFORE<br>AUGUST 12, 2005<br>(Payment must be<br>received before 12.8.2005) | AS FROM<br>August 13, 2005 |

| 1) SDR / Cognitive Radio                                                            | 110,00 EUR                                                                  | 110,00 EUR                 |

| 2) MOS-AK                                                                           | free                                                                        | free                       |

| 3) SINANO                                                                           | free                                                                        | free                       |

| 4) MIMOSA                                                                           | 200,00 EUR                                                                  | 200,00 EUR                 |

| 5) ENIAC                                                                            | free                                                                        | free                       |

## **CONFERENCE REGISTRATION**

| BEFORE                     |  |  |

|----------------------------|--|--|

| <b>AUGUST 12, 2005</b>     |  |  |

| (Payment must be           |  |  |

| received before 12.9.2005) |  |  |

AS FROM August 13, 2005

| Accompanying persons                      | 110,00 EUR | 110,00 EUR |

|-------------------------------------------|------------|------------|

| Additional Proceedings of                 | 80,00 EUR  | 80,00 EUR  |

| ESSDERC or ESSCIRC                        | 00,00 2011 | 00,00 2011 |

| Technical Visits                          |            |            |

| (Registration before 15 August 2005)      |            |            |

| STMicroelectronics (Friday, 16 September) | 30,00 EUR  |            |

| SOITEC (Friday, 16 September)             | 30,00 EUR  |            |

|                                           |            |            |

| Tours                                     |            |            |

| V1 – La Chartreuse                        | 23,00 EUR  | 23,00 EUR  |

| V2 – Grenoble                             | 22,00 EUR  | 22,00 EUR  |

| V3 – Vercors region                       | 27,00 EUR  | 27,00 EUR  |

#### **Payment**

- By cheque payable in France to the order of ESSDERC-ESSCIRC/ MCI France.

- On line: accepted credit cards VISA, EURO/MASTER CARD or AMEX.

- Payments can also be made by bank transfer to

#### ESSDERC-ESSCIRC 2005 / MCI France,

11 rue de Solférino, 75007 Paris

Bank: Crédit Lyonnais - Bank code: 30002 - Sort code: 00424 - Account number: 0000008606P - Key: 61 - Bank agency: Paris rue du Bac (00424)

- IBAN: FR33 3000 2004 2400 0000 8606 P93 - BIC: CRLYFRPP

#### **Cancellation**

All cancellations must be notified in writing (by mail or fax BUT NOT email) to MCI France according to the following conditions. Reimbursement will be processed after the conference.

Up to August 29, 2005 : 80 EUR will be withheld for administrative fee

After August 29, 2005 : No refund

Requests for preregistration refunds must be received no later than 10 working days prior to the first day of the conference.

Name change: a processing fee of 30 EUR will be charged for changes in registration.

## Registration desk

Conference registration will be located at

Alpes Congres - Alpexpo

Avenue d'Innsbruck - BP 2408 - 38034 GRENOBLE - France

Tel. +33 (0) 476 39 66 00 (switch board Alpexo)

#### Opening hours of the registration

12 September: 8 am - 5 pm 13 - 15 September: 8 am - 6 pm 16 September: 8 am - 3 pm

## **CONFERENCE INFORMATION**

#### Internet services

Computer terminals with internet access will be available for free on the site of the conference during the opening hours.

It will also be possible to use the WIFI network (10 Mbytes/s) of the conference center using your personal laptop. WiFi cards can be purchased at the conference center (2 hours = 9.5 EUR, 24 hours = 29 EUR, 7 days = 99 EUR).

#### Conference language

The working language for the conference will be English to be used for all presentations and printed material.

#### Insurance disclaimer

Please arrange your own travel and health care insurance. The organizers will not be held liable for accidents, theft and property damage, nor for delays or any modification of the programme.

#### **Speakers briefing**

Authors should meet their chairperson in the session room 20 minutes prior to the beginning of their respective sessions.

#### **Guidelines for Presentations**

To ensure a successful presentation, without software compatibility problems, please note the following guidelines:

- Your presentation will take 20 minutes including your introduction by the session chair and a few minutes for questions from the audience.

- Electronic projection will be used for all presentations (no transparencies or 35mm slides).

- ▶ Your presentation has to be in PDF or PPT format on IBM PC versions ONLY.

- ➤ Your presentation has to be saved using a file name with the pattern "S\_author\_n.pdf" (or .ppt) where S is the session number (see the conference programme), author is the last name of the first author and n is the version number of your file. Example: 1A1 Einstein 17.ppt.

- Please prepare a SHORT vita (5 lines) so that the chairman can introduce you.

- The deadline for submission of your presentation is: September, 2nd 2005. Details regarding the exact procedure of submissions will be available on the ESSDERC & ESSCIRC web site at the beginning of July.

- ▶ No correction of your presentation will be possible after September 2.

- Computers will be available in the Speaker Preparation Room to review your file (not to make changes).

- ▶ Please bring a backup CD or USB key with your presentation just in case.

- Despite the fact that the content of electronic presentations is assumed to be placed in the public domain at the time of the conference, ESSDERC-ESSCIRC'05 will not publish or distribute the presentation files.

#### **Conference proceedings**

All participants will receive a copy of either the ESSDERC or the ESSCIRC Proceedings and a CDROM with both ESSDERC and ESSCIRC accepted papers.

### Best paper award

ESSDERC/ESSCIRC offers a "Best Paper" award (for contributed papers only) and a "Young Scientist" award, for the best paper presented by a speaker of less than 28 years old. The recipient will be the speaker himself. The selection is based on: (i) evaluation by the audience and (ii) paper ratings.

## SOCIAL PROGRAMME

#### Tuesday, 13 September at 7 pm

A welcome reception will be offered by the Mayor of Grenoble, Michel DESTOT, at the "Musée de Grenoble", 5, place de Lavalette.

City center, tramway stop "Nôtre Dame - Musée".

Shuttle busses from Alpexpo will be arranged at 6:40 pm for the participants at the Panel Session.

#### Wednesday, 14 September at 7:30 pm

The Gala dinner will take place at the PRISME Seyssins (89 avenue de Grenoble, 38180 Seyssins).

VILLE DE SEYSSINS

The shuttle buses will leave from Alpexpo at 7 pm.

- A cocktail reception before the dinner will be offered by the Mayor of Seyssins, Didier Migaud.

- ☼ The morning session on Thursday still starts at 9 am!

#### Thursday, 15 September at 7:30 pm

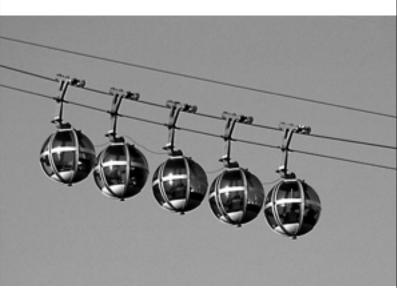

Farewell party at the Restaurant du Téléférique, Fort de la Bastille, Grenoble.

To join the restaurant, please take the cable car, the organiser will provide free tickets.

Departure: Téléférique Grenoble-Bastille, Quai Stéphane Jay

The Farewell evening is sponsored by

# ACCOMPANYING PERSONS | PROGRAMME

All tours will be conducted in English. They will depart and return from and to the Conference Center. The organisers reserve the right to cancel tours with less than 25 participants. Since the excursions have a limited number of participants, please

register as soon as possible. Reservations will be made in order of arrival; on-site availability cannot be guaranteed.

#### V1 - "La Chartreuse"

Tuesday, 13 September 2005 - 1:30pm-6:30pm Cost: 23 EUR

Saint Bruno found refuge here more than 900 years ago to meditate and found the famous Grande Chartreuse Monastery. The monastery is still dedicated to prayer and meditation and part of it can be visited. The tour includes the visit of the distillery in the greatest caves as well as the tasting of the famous Chartreuse liquor.

#### V2 - "Grenoble"

Wednesday, 14 September 2005 - 09:00am-01:00pm Cost: 22 FUR

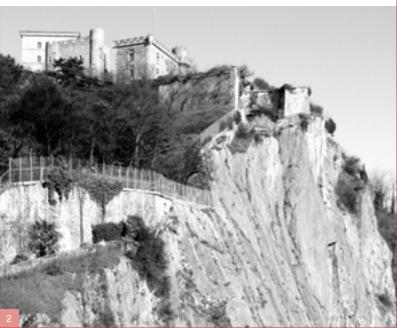

This tour is designed to reveal the city's architectural and cultural treasures such as Saint-André, Notre-Dame and Grenette squares, the palace of justice, Stendhal's home, the city gardens and old private mansions from the 15 and 16 centuries so typical with their Renaissance spiral vaulted stairways. Riding the cable car, you will get to the fortified site of the Bastille to admire an astonishing panorama overlooking Grenoble and the surrounding mountains. In clear days Mont Blanc comes nearby!

#### V3 - "Vercors region"

Thursday, 15 September 2005 - 08:30am-01h30pm Cost: 27 EUR

The Vercors seems to be an island surrounded by land. Water has cut deep gorges, magestic cirques, caves and swallow-holes, among the most famous in the Solar System.

Visit of the unforgettable Choranche Caves with its thousands of spaghetti-like stalactites reflected in the inner mountain lake. The sound and light show is

spectacular. Stop at Pont-en-Royans at the end of the Bournes Gorges: dominated by rocky edges, this very, very old village is suspended above the bed of the torrent. Picturesque houses overhang the void.

# JOINT PLENARY TALKS

For details, see Programme ESSCIRC, pages 9-12.

Horst Stormer

"Silicon Forever! Really?"

Eli Yablonovitch

"Silicon Nano-Photonics: Where the Photons Meet the Electrons"

Michael Shur

"Terahertz Electronics: Devices, Circuits, and Applications"

Ralph Cavin

"Limits of CMOS Devices and Circuits"

Mike Thompson

"Future of CMOS Technology, Manufacturing and Products"

Christian Joachim

"Towards a Molecule - Computer?"

MINATEC - Under construction.

# ESSDERC-INVITED PLENARY TALKS

#### Carlos Mazuré and André-Jacques Auberton-Hervé "Engineering Wafers for the Nanotechnology Era"

Nanotechnology starts at the substrate level. Substrate engineering is one of the most important innovations of the nanotechnology era driven by the vanishing boundary between substrate design and device architecture. SOI substrates, the first engineered substrates of its kind, have made possible an efficient optimization of MOSFET current drive while minimizing the leakage and reducing parasitic elements, thus enhancing the overall IC performance. Strained silicon, hybrid orientation SOI, germanium on insulator have added new handles to traditional scaling to further improve device and IC performance. An overview of the advances in Smart Cut engineered substrates and the impact on device performance will be given.

#### Biographies

André-Jacques Auberton-Hervé co-founded Soitec with Jean-Michel Lamure in 1992, and currently serves as President and CEO, overseeing the strategic, operational and financial activities of the company. Prior to founding Soitec, Dr. Auberton-Hervé managed joint development programs between LETI and Thomson-CSF, the ultimate target of which was the technological transfer from R&D to production. These programs included the transfer of 1.2  $\mu m$  and 0.8  $\mu m$  SOI CMOS for space applications. He was also in charge of several projects, which applied SOI to 3D integration, VLSI and ULSI. In 1999, he received the European SEMI Award in recognition of his work on the Smart Cut technology and his contribution to the semiconductor industry. Dr. Auberton-Hervé is a member of the Electrochemical Society and the IEEE. Dr. Auberton-Hervé has a Ph.D. in semiconductor physics and an M.S. in materials science from Ecole Centrale de Lyon (France).

Since 2001, Carlos Mazuré, Chief Technology Officer, has managed Soitecs's strategic Advanced Technology Development organization. He is tasked with identifying the best new breed of engineered substrates and its applications to help define the future business directions for the company. He works closely with Soitec's customers to help support and open new applications for Soitec's Smart Cut technology. Prior to Soitec, Mazuré served as director of business development at Infineon Technologies AG, and was involved with the IBM/Siemens DRAM Development Alliance. His experience also includes work on SOI and BiCMOS high performance devices and technology development at Motorola Corp. Carlos Mazuré holds two doctorates in physics, one from the University of Grenoble, France, and the other from the Technical University of Munich, Germany. Carlos Mazuré is the author of more than 150 technical papers and holds more than 70 patents worldwide.

#### **Lothar Risch**

#### "Pushing CMOS beyond the Roadmap"

The end of CMOS and of Moore's law was already discussed at feature sizes of about  $1\mu m$  in the eighties. Today, the 90 nm generation is in production and in spite of many roadblocks, the latest ITRS expects that CMOS can be scaled at least down to the 22 nm node with minimum gate lengths of 9 nm. However, for conventional bulk CMOS serious challenges are evident and new transistors with better electrostatic channel control, lower off currents and higher on currents will be needed. Among them multi-gate devices with very thin silicon channels are most promising. Several architectures like FinFET, wafer bonded double-gate and

## **ESSDERC-INVITED**

SON have been demonstrated with good electrical characteristics at gate lengths of 25-10 nm. From quantum mechanical simulations with idealized source drain doping profiles it is predicted that silicon MOSFETs will be functional down to 2 nm gate length with off currents in the  $\mu$ A/ $\mu$ m range. Multi-gate transistors have also been implemented in high density Flash memory cells down to 20 nm. They achieve large Vt shifts, suitable for multi-level storage. Even single electrons can be detected on the storage node. To summarize, it seems very realistic that the device roadmap will not end at the 22 nm node. Provided that manufacturing and cost issues can be fulfilled. CMOS will dominate also in the nanoelectronics era.

#### Biography

Lothar Risch received the diploma degree in physics from the Technical University of Berlin in 1974 and the doctor degree from the Technical University of Karlsruhe in 1976. He joined Siemens Corporate Research in Munich in 1977. Since then, he has been engaged in Silicon microelectronics especially in DRAM memory cell development from 4 to 256 Mbit, CMOS logic, and Silicon based nanoelectronics. In 1999 he moved to Infineon Technologies, the former Siemens Semiconductor Group. Now, he is a senior director of the department Corporate Research Nano Devices with the main activity on 30 to 10nm CMOS and memory cells. He filed more than 50 patents and he is also a member of several advisory boards and technical program committees.

#### H.-S. Philip Wong

#### "Nanoelectronics: Nanotubes, Nanowires, Molecules and Novel Concepts"

As device sizes approach the nanoscale, new opportunities arise from harnessing the physical and chemical properties at the nanoscale. Chemical synthesis, self-assembly, and templated self-assembly promise the precise fabrication of device structures or even the entire functional entity. Quantum phenomena and one-dimensional transport may lead to new functional devices with very different power/performance tradeoffs. New materials with novel electronic, optical, and mechanical properties emerge as a result of the ability to manipulate matter on a nanoscale. It is now feasible to contemplate new nanoelectronic systems based on new devices with completely new system architectures. This paper will give an overview of the materials, technology, and device opportunities in the nanoscale era. The focus of discussion will be on nanotubes, nanowires, molecular devices, and novel device concepts for nanoelectronics.

#### Biography

H.-S. Philip Wong joined the IBM T. J. Watson Research Center, Yorktown Heights, New York, in 1988. In September, 2004, he joined Stanford University as Professor of Electrical Engineering. While at IBM, he was Senior Manager of the 60-member Department of Nanoscale Materials, Processes, and Devices. He has the responsibility of shaping and executing IBM's strategy on nanoscale science and technology, Prior to this appointment, he was Senior Manager of the Exploratory Devices and Integration Technology Department, His 54-member department was responsible for defining and executing IBM's exploratory devices and technology roadmap for silicon technology. His research interests are in nanoscale science and technology, semiconductor technology, solid state devices, and electronic imaging. He is interested in exploring new materials, novel fabrication techniques, and novel device concepts for future nanoelectronics systems. Novel devices often require new concepts in circuit and system designs. His research also includes explorations into circuits and systems that are device-driven. He is a Fellow of the IEEE. He is a member of the Emerging Research Devices Working Group of the International Technology Roadmap for Semiconductors (ITRS).

## **EXHIBITORS**

The exhibition includes major scientific publishers as well as suppliers of equipments for characterisation, CAD software, test tools and equipment, etc.

Opening hours:

Tuesday 13 September: 12 am - 5 pm

Wednesday 14 September: 9 am - 5 pm

Thursday 15 September: 9 am - 3 pm

#### ... Agilent Technologies

. Innovating the HP Way

Agilent Advanced Design System (ADS) is the industry leader in high-frequency design. It supports system and RF design engineers developing all types of RF designs, from simple to the most complex, from RF/microwave modules to integrated MMICs for communications and aerospace/defense applications.

## **KEITHLEY**

Keithley Instruments provides leading and cost effective solutions for DC to RF test and measurements for high tech industries in semiconductor, wireless telecom and nanotechnology domains. For more than 50 years, we have demonstrated our excellence in electrical characterization of materials, reliability test, failure analysis, data acquisition and process control.

## SILVACO

Silvaco delivers to semiconductor technologists TCAD products to develop and optimize their semiconductor processes; to IC designers CAD products to design and simulate analog circuits and "field solvers" products for accurate parasitics extraction. Interaction between manufacturing and design depends on accurately extracted device models and reliable simulation.

a division of

### **AMETEK**

Taylor Hobson is an ultra-precision technology company operating at the highest levels of accuracy within the field of surface and form metrology. We provide contact and non-contact measurement solutions to the most demanding applications on a global basis, with a worldwide infrastructure to support our clients, wherever they may be.

#### CAMBRIDGE UNIVERSITY PRESS www.cambridge.org

Cambridge University Press is the printing and publishing house of the University of Cambridge. Visit our stand and receive a 20% discount on all displayed titles.

John Wiley & Sons Ltd are a leading international publisher of print and electronic products, specialising in scientific and technical books and journals. Visit our stand at ESSDERC-ESSCIRC'05 and view our latest range of circuits & devices publications. All books on display are available at a special conference discount. Alternatively view our publications online: www.wiley.com

Elsevier is the world's leading publisher of scientific, medical & technical information. Our publications are written and edited by internationally renowned scholars with excellent technical and scientific credentials and wide research and teaching experience in their fields. Please feel free to visit our stand and sample some of the journal content for yourself!

Welcome to the new Springer!

Since the merger of Kluwer Academic Publisher and Springer-Verlag the product range includes more than 1,200 journals and 3,500 new book titles each year, making Springer the world's second largest supplier of scientific literature. For a comprehensive overview of the Springer publishing program, please visit http://www.springeronline.com

#### **CIRCUIT EXHIBITION**

An exhibition of integrated circuits is organised during all the Conference. Three categories of circuits are considered: education, research, industry. All circuits have been fabricated, through different manufacturing services. The circuit exhibition is sponsored by CMP.

Plots of the circuits as well as information on the circuits (function, origin, etc.) are on display on Tuesday, Wednesday and Thursday at the exhibition area. The authors will be present at their posters for discussions and demonstrations during the Coffee Breaks on Tuesday. A catalogue is available.

For more information, please contact:

**Bernard Courtois** bernard.courtois@imag.fr **Hubert Delori** hubert.delori@imag.fr

#### FRINGE MEETINGS

### Lunch and Learn Seminar: Pulsed Characterization of Advanced CMOS Technologies

**Date:** Wednesday, 14 September, 12:45-14:15 (and 18:00 – 19:00)

Room: Bayard

Organised by:

Keithley

For more information please come to our booth at the exhibition area.

#### Other Fringe Meetings:

The topic and location of the fringe meetings will be announced at the conference site.

# MONDAY, 12 SEPTEMBER | SHORT COURSES

#### Registration from 8:00 am at:

Alpes Congres - Alpexpo

Avenue d'Innsbruck - BP 2408 - 38034 GRENOBLE - France

Tel. +33 (0) 476 39 66 00 (switch board Alpexo)

Organiser:

Simon Deleonibus CEA-LETI, email: sdeleonibus@cea.fr

#### Short course 1: New process and device concepts

Chair: F. Balestra, IMEP

Room: Chartreuse

8:50-9:00 Introduction - F. Balestra, IMEP

9:00-10:30 Advanced CMOS Devices on Bulk and SOI: Physics, Modeling

and Characterisation - T. Poiroux, CEA LETI

10:30-10:45 Coffee Break

10:45-12:15 Alternative CMOS Architectures and ITRS Emerging Research

**Devices** - HS Philip-Wong, University of Stanford

12:15-13:45 Lunch (Sponsored by NANOCMOS)

13:45-14:45 High-K Gate Dielectrics - H. Iwai, Tokyo Inst. of Tech

14:45-15:45 Ion Implantation Damage and Annealing in Silicon - K. Jones,

University of Florida

15:45-16:00 Coffee Break

16:00-17:00 New Interconnects Schemes: End of Copper, Optical Inter-

connects? - S. Laval, IEF, France

#### Fees:

**Regular:** 200 EUR (early), 250 EUR (late) **Students:** 150 EUR (early), 200 EUR (late)

#### **Short course 2: Advanced concepts for SOC and SIP**

Chair: S. Deleonibus, CEA-LETI

Room: Belle étoile

8:50-9:00 Introduction - S. Deleonibus CEA-LETI

9:00-10:30 SOC and SIP for Heterogeneous System Integration -

R. Mertens, IMEC

10:30-10:45 Coffee Break

10:45-12:15 System-Level Performance Analysis of Advanced CMOS

Technologies - Philip Christie, Philips

12:15-13:45 Lunch (Sponsored by NANOCMOS)

## MONDAY, 12 SEPTEMBER

13:45-14:45 Advanced SiGeC BICMOS Technology for SoC Integration -

A. Chantre, STMicroelectronics

14:45-15:45 Embedded Memories - A. Maurelli, STMicroelectronics

15:45-16:00 Coffee Break

16:00-17:00 Introducing New Devices on Chip: MEMS, Sensors, etc. -

P. Ancey, STMicroelectronics

#### Fees:

Regular: 200 EUR (early), 250 EUR (late) Students: 150 EUR (early), 200 EUR (late)

#### Short course 3: Nanoelectronics - Beyond the roadmap **Emerging research devices**

Chair: G. Baccarani, Univ. Bologna

Room: Meije

Introduction - G. Baccarani, Univ. Bologna 8:50-9:00

9:00-10:00 Molecular Electronics: Self-Assembly and Organisation,

Carbon Nanotubes - J-P. Bourgoin, CEA

10:00-11:00 Spin Electronics - C. Chappert, IEF

11:00-11:15 Coffee Break

11:15-12:15 Quantum Computing in Quantum Dots - D. Loss, U. Basel

Lunch (Sponsored by NANOCMOS) 12:15-13:45

#### Short course 4: Emerging Memory Architectures When will the UNIversal Memory be available?

Chair: R. Bouchakour, Univ. Marseille

Room: Meiie

12:15-13:45 Lunch (Sponsored by NANOCMOS)

13:50-14:00 Introduction - R. Bouchakour, Univ. Marseille

14:00-15:00 Technology and Key Design Issues for New Memory Devices

(Embedded and Stand Alone) - Kinam Kim, Samsung

15:00-16:00 FeRAM and MRAM Technologies - Y. Arimoto, Fujitsu

16:00-16:15 Coffee Break

16:15-17:15 **New Memory Concepts: from Silicon Nanocrystal Memories**

to Molecular Memories - B. De Salvo, LETI

#### Fees (short course 3 + 4):

Regular: 200 EUR (early), 250 EUR (late) Students:

150 EUR (early), 200 EUR (late)

# TUESDAY, 13 SEPTEMBER | SCIENTIFIC PROGRAMME

#### **Introduction and Paper Award 2004**

Time: 08:45 - 09:15 Location: Dauphine

#### **Joint Plenary Session**

Chairs: S. Cristoloveanu, IMEP (France); M. Brillouët, CEA-LETI (France)

Time: 09:15 - 09:55 Location: Dauphine

09:15 Future Devices for Information Processing

R. Cavin, V. Zhirnov, Semiconductor Research Corporation, USA

#### **ESSDERC Plenary Session**

Chairs: S. Cristoloveanu, IMEP (France); M. Brillouët, CEA-LETI (France)

Time: 10:00 - 10:40 Location: Dauphine

10:00 Engineering Wafers for the Nanotechnology Era

C. Mazuré, A-J. Auberton-Hervé, SOITEC, France

#### **Coffee Break**

Time: 10:40 - 11:00 Location: Alpes Congès

#### **SESSION 1.A.: Multi - Gate Devices**

Chairs: M. Jurczak, IMEC (Belgium); P. Stolk, Philips Crolles (France)

Time: 11:05 - 12:45 Location: Dauphine

1A1

11:05 3-D Thermal Modeling of FinFET

R. Joshi, IBM, USA; J. Pascual-Gutiérrez, Purdue University, USA;

K. Chuang, IBM, USA

1A2

11:25 Immunity to Substrate Effect in Advanced  $\Omega$ -FET Devices

R. Ritzenthaler, O. Faynot, C. Jahan, A. Kuriyama, L. Brévard, CEA-LETI,

France; S. Cristoloveanu, IMEP, France; S. Deleonibus, CEA-LETI, France

1A3

11:45 Specific Features of the Capacitance and Mobility Behaviors in

**FinFET Structures**

T. Rudenko, Institute of Semiconductor Physics, National Academy of Sciences, Ukraine; V. Kilchytska, Universite Catholique de Louvain, Belgium; N. Collaert, S. Gendt, R. Rooyackers, M. Jurczak, InterUniversity Microelectronics Center, Belgium; D. Flandre,

Universite Catholique de Louvain, Belgium

1**A**4

12:05 Evidence for Reduction of Noise and Radiation Effects in G<sup>4</sup>-FET

**Depletion-All-Around Operation**

K. Akarvardar, S. Cristoloveanu, IMEP, France; B. Dufrene, IBM, USA; P. Gentil, IMEP, France; R. Schrimpf, Vanderbilt University, USA; B. Blalock, University of Tennessee, USA; J. Chroboczek, IMEP, France;

M. Mojarradi, JPL, USA

**1 4 5**

12:25 Tunneling and Intersubband Coupling in Ultra-Thin Body Double-Gate MOSFETs

V. Sverdlov, Institute for Microelectronics, TU Vienna, Austria; A. Gehring, AMD Saxony LLC & Co. KG, Germany; H. Kosina, S. Selberherr, Institute for Microelectronics, TU Vienna, Austria

#### SESSION 1.B.: Gate Stack

Chairs: J. Hooker, Philips Leuven (Belgium); R. Beck, Warsaw University of

Technology (Poland)

Time: 11:05 - 12:45 Location: Oisans

1B1

Germanium/HfO2/TiN Gate Stacks for Advanced Nodes: 11:05 Influence of Surface Preparation on MOS Capacitor

**Characteristics**

C. Le Royer, X. Garros, C. Tabone, L. Clavelier, CEA-LETI, France; Y. Morand, STMicroelectronics, France; J. Hartmann, CEA-LETI, France; Y. Campidelli, O. Kermarrec, ST Microelectronics, France; V. Loup, E. Martinez, O. Renault, B. Guigues, CEA-LETI, France; V. Cosnier, ST

Microelectronics, France; S. Deleonibus, CEA-LETI, France

1B2

11:25 The Effect of Metal Thickness, Overlayer and High-k Surface Treatment on the Effective Work Function of Metal Electrode

> K. Choi, H. Wen, SEMATECH, USA; H. Alshareef, TJ. SEMATECH, USA; R. Harris, P. Lysaght, H. Luan, P. Majhi, B. Lee, SEMATECH, USA

1B3

11:45 Mixed-Signal and Noise Properties of nMOSFETs with **HfSiON/TaN Gate Stacks**

> C. Rittersma, Philips Research Leuven, Belgium; E. Simoen, P. Srinivasan, IMEC, Belgium; M. Vertregt, Philips Research, The Netherlands; C. Claeys, IMEC, Belgium

1**B**4

12:05 Work Function Control of Metal Gates by Interdiffused Ni-Ta with **High Thermal Stability**

> T. Matsukawa, Y. Liu, M. Masahara, K. Endo, K. Ishii, H. Yamauchi, E. Sugimata, H. Takashima, E. Suzuki, S. Kanemaru, Nanoeletronics

Reseach Inst., AIST, Japan

1**B**5

12:25 PLAsma Doping for S/D Extensions: Device Integration, Gate Oxide Reliability and Dynamic Behavior

B. Dumont, STMicroelectronics, France; A. Pouydebasque, Philips Semiconductors, France; F. Lallement, D. Lenoble, G. Ribes, J. Roux, STMicroelectronics, France; S. Vanbergue, Philips Semiconductors, France; T. Skotnicki, STMicroelectronics, France

#### **SESSION 1.C.: RF Devices**

Chairs: P. Ashburn, University of Southampton (United Kingdom);

S. Decoutere, IMEC (Belgium)

Time: 11:05 - 12:45 Location: Sept Laux

| 1 <b>C</b> 1 |

|--------------|

| 11:05        |

High-Performance Varactor Diodes Integrated in a Silicon-on-

Glass Technology

G. Ghibaudo, IMEP, France

K. Buisman, HiTec, Delft University of Technology, The Netherlands; L. Nanver, T. Scholtes, H. Schellevis, ECTM, Delft University of Technology, The Netherlands; L. de Vreede, HiTec, Delft University of Technology, The Netherlands

#### **1C2**

11:25 Three-dimensional 35 nF/mm<sup>2</sup> MIM Capacitors Integrated in BiCMOS Technology

A. Bajolet, ST Microelectronics / IMEP-INPG, France; J. Giraudin, C. Rossato, L. Pinzelli, S. Bruyère, S. Crémer, T. Jagueneau, P. Delpech, ST Microelectronics, France; L. Montès, IMEP-INPG, France;

#### 1**C**3

11:45 Comparison of two Types of Lateral DMOSFET Optimized for RF Power Applications

D. Muller, J. Mourier, A. Perrotin, B. Szelag, A. Monroy, STMicroelectronics. France

#### 1C4

12:05 Deep Trench Isolation Effect on Self-Heating and RF

Performances of SiGeC HBTs

B. Barbalat, T. Schwartzmann, P. Chevalier, T. Jagueneau, B. Vandelle, L. Rubaldo, F. Saguin, STMicroelectronics, France; F. Aniel, IEF, France; A. Chantre, STMicroelectronics, France

#### **1C5**

12:25 Investigation of Fully- and Partially-Depleted Self-Aligned SiGeC

**HBTs on Thin Film SOI**

G. Avenier, P. Chevalier, B. Vandelle, D. Lenoble, F. Saguin, STMicroelectronics, France; S. Frégonese, T. Zimmer, IXL Bordeaux, France; A. Chantre, STMicroelectronics, France

#### **SESSION 1.D.: Compact Modeling**

**Chairs:** H. Jaouen, STMicroelectronics Crolles (France); K. McCarthy, University

College Cork (Ireland)

Time: 11:05 - 12:45 Location: Stendhal

#### 1D1

11:05 Quantum Short-Channel Compact Modeling of Drain-Current in Double-Gate MOSFET

D. Munteanu, J. Autran, X. Loussier, L2MP-CNRS, France; S. Harrison,

R. Cerutti, T. Skotnicki, ST Microelectronics, France

#### 1D2

11:25 Compact Modeling of Anomalous High Frequency Behavior of MOSFET's Small-Signal NQS Parameters in Presence of Velocity Saturation

A. Roy, J. Sallese, EPFL, Switzerland; C. Enz, CSEM, EPFL, Switzerland

#### 1D3

11:45 Compact Modeling of Electrical, Thermal and Optical LED

**Behavior**

P. Baureis, University of Applied Sciences, Wuerzburg, Germany

1D4

12:05 A Closed-Form Charge-Based Expression for Drain Current in

Symmetric and Asymmetric Double Gate MOSFET

A. Roy, EPFL, Switzerland; J. Sallese, EFPL, Switzerland; C. Enz,

CSEM, EPFL, Switzerland

1D5

12:25 Base-Collector Junction Charge Investigation of Si/SiGe HBT on

Thin Film SOI

S. Frégonese, IXL, France; G. Avenier, STMicroelectronics, France;

C. Maneux, IXL, France; A. Chantre, STMicroelectronics, France;

T. Zimmer, IXL, France

Lunch

Time: 12:45 - 14:10

Location: Les Ecrins

**Joint Plenary Session**

Chairs: M. Steyaert, Katholieke Universiteit Leuven (Belgium); W. Redman-

White, Philips Semiconductors (UK)

Time: 14:15 - 14:55 Location: Dauphine

14:15 Silicon Nano-Photonics: Where the Photons Meet the Electrons

E. Yablonovitch, Electrical Engineering Department, University of

California, USA

**SESSION 2.A.: Nano-Scaled Devices**

Chairs: G. Iannacconne, University of Pisa (Italy); L. Risch, Infineon (Germany)

Time: 15:00 - 16:40 Location: Chartreuse

2A1

15:00 Nanotechnology: Potential Challenger to Silicon CMOS? (Invited)

B. Yu, NASA Ames Reserach Center, USA; M. Meyyappan, NASA Ames

Research Center, USA

2A2

15:20 Quantum-Mechanical Analysis of the Electrostatics in Silicon-

**Nanowire and Carbon-Nanotube FETs**

E. Gnani, A. Marchi, S. Reggiani, M. Rudan, G. Baccarani, ARCES -

University of Bologna, Italy

2A3

15:40 Trade-off between Electron Velocity and Density of States in

**Ballistic Nano-MOSFETs**

M. De Michielis, D. Esseni, F. Driussi, DIEGM, Univ. of Udine, Italy

**2A4**

16:00 Monte Carlo Simulations of Sub-100 nm InGaAs MOSFETs for

**Digital Applications**

K. Kalna, University of Glasgow, UK; L. Yang, Cadence Ltd., China; A.

Asenov, University of Glasgow, UK

**2A5**

16:20 The 65nm Tunneling Field Effect Transistor (TFET) 0.68  $\mu$ m<sup>2</sup> 6T

Memory Cell and Multi-Vth Device

T. Nirschl, Infineon Technologies, Germany; S. Henzler, J. Fischer, A. Bargagli-Stoffi, M. Fulde, M. Sterkel, Technical University Munich, Germany; U. Schaper, G. Georgakos, Infineon Technologies, Germany;

D. Schmitt-Landsiedel, Technical University Munich, Germany

#### **SESSION 2.B.: Dynamic Random Access Memories**

Chairs: P. Erratico, STMicroelectronics Agrate (Italy); S. Okhonin, Innovative

Silicon (Switzerland)

Time: 15:00 - 16:40 Location: Belle étoile

**2B1**

15:00 High-Density Low-Power-Operating DRAM Device Adopting 6F2

Cell Scheme with Novel S-RCAT Structure on 80nm Feature Size

H. Oh, J. Kim, J. Kim, S. Park, D. Kim, S. Kim, D. Woo, Y. Lee, G. Ha, J. Park, N. Kang, H. Kim, Y. Hwang, B. Kim, D. Kim, Y. Choi, J. Choi, B. Lee, S. Kim, M. Cho, Y. Kim, J. Choi, D. Shin, M. Shim, W. Choi, G. Lee, Y.

Park, W. Lee, B. Ryu, Samsung Electronics Co, Korea

2B2

15:20 Advanced Memory Concepts for DRAM and Nonvolatile

**Memories (Invited)**

F. Horiguchi, Toyo University, Japan

**2B3**

15:40 Data Retention Analysis on Individual Cells of 256Mb DRAM in

110nm Technology

A. Weber, Infineon Technologies / TU Harburg, Germany; A. Birner, Infineon Technologies, Germany; W. Krautschneider, TU Harburg,

Germany

2**B**4

16:00 Enhancement of Data Retention Time in DRAM using Step gaTed

AsymmetRic (STAR) Cell Transistors

M. Jang, M. Seo, Y. Kim, S. Cha, S. Park, S. Pyi, J. Jeong, S. Hong, S. Park,

Hynix Semiconductor Inc., Korea

**2B5**

16:20 Analysis of the NAND-type DRAM-on-SGT for High-Density and

**Low-Voltage Memory**

H. Nakamura, I. Pesic, H. Sakuraba, F. Masuoka, Research Institute of

Electrical Communication, Tohoku University, Japan

#### SESSION 2.C.: High- and Medium-K Characterisation

Chairs: S. Bengtsson, Chalmers University (Sweden); G. Groeseneken, IMEC

(Belgium)

Time: 15:00 - 16:20

Location: Meije

2C1

15:00 Polarity Dependence of Bias Temperature Instabilities in

Hf(x)Si (1-x) ON/TaN Gate Stacks

M. Aoulaiche, M. Houssa, R. Degraeve, G. Groeseneken, S. De Gendt,

M. Heyns, IMEC, Belgium

**2C2**

15:20 The Role of Nitrogen Incorporation in Hf-based High-k Dielectrics:

**Reduction in Electron Charge Traps**

N. Umezawa, National Institute for Materials Science, Japan; K. Shiraishi, Univ. of Tsukuba, Japan; K. Torii, Semiconductor Leading Edge Technology Inc., Japan; T. Chikyow, National Institute for Materials Science, Japan; H. Watanabe, Osaka Univ., Japan; K. Yamabe, Univ. of Tsukuba, Japan; T. Ohno, Institute for Materials Science, Japan; K. Yamada, Waseda Univ., Japan; Y. Nara, Semiconductor Leading Edge Technology Inc., Japan; M. Boero, Univ. of Tsukuba, Japan

2C3

15:40 Effects of Plasma Nitridation on the Electrical Properties of

**Nitrided Oxide Gate Dielectric for DRAM Application**

J. Heo, D. Kim, B. Koo, J. Kim, C. Kim, Y. Noh, S. Baek, Y. Shin, U. Chung, Samsung Electronics Co., Korea

2C4

16:00 A New Method Based on Charge Pumping Technique to Extract the Lateral Profiles of Localized Charge Trapping in Nitride

H. Pang, L. Pan, L. Sun, Y. Zeng, Z. Zhang, J. Zhu, Institute of Microelectronics, Tsinghua University, China

SESSION 2.D.: Nanowires

Chairs: M. Sanguer, CEA (France); O. Engström, Chalmers University (Sweden)

Time: 15:00 - 16:40 Location: Sept Laux

2D1

15:00 Analytical Model for Nanowire and Nanotube Transistors

**Covering both Dissipative and Ballistic Transport**

G. Mugnaini, G. Iannaccone, University of Pisa, Italy

2D2

15:20 High Performance ZnO Nanowire Field Effect Transistor

S. Cha, J. Jang, Y. Choi, G. Ho, D. Kang, D. Hasko, M. Welland, G.

Amaratunga, University of Cambridge, UK

2D3

15:40 **Impact of Point Defect Location in Nanowire Silicon MOSFETs**

> M. Bescond, University of Glasgow, UK; N. Cavassilas, K. Nehari, J. Autran, M. Lannoo, L2MP UMR CNRS 6137, France; A. Asenov,

University of Glasgow, UK

2D4

16:00 Detection of Individual Traps in Silicon Nanowire Transistors

M. Hofheinz, X. Jehl, M. Sanguer, G. Molas, M. Vinet, S. Deleonibus,

CEA Grenoble, France

2D5

16:20 Influence of Band-Structure on Electron Ballistic Transport in

Silicon Nanowire MOSFET's: an Atomistic Study

K. Nehari, N. Cavassilas, J. Autran, L2MP-CNRS, France; M. Bescond, University of Glasgow, UK; D. Munteanu, M. Lannoo, L2MP-CNRS,

France

**Coffee Break**

Time: 16:40 - 17:00 Location: Salle de Réception

## RUMP SESSION: Where will the revolutionary solutions come from: technology or design?

Time: 17:00 - 18:30 Location: Dauphine

Moderators: T. Skotnicki (STMicroelectronics, France), A. Kaiser (IEMN, France)

#### **ESSDERC Panelists:**

- Hiroshi IWAI (Tokyo Institute of Technology, Japan)

- Rainer WASER (RWTH-Aachen, Germany)

- Kazunari ISHIMARU (SoC R&D Center, TOSHIBA Corp., Japan)

- Peter ZEITZOFF (SEMATECH, USA)

#### **ESSCIRC Panelists:**

- Clive BITTLESTONE (Texas Instruments, USA)